Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 54                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1947-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

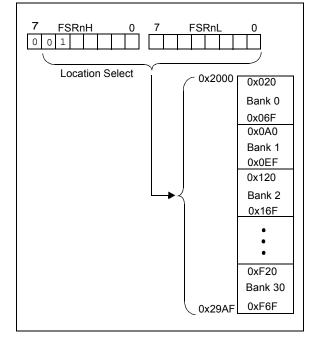

## 3.6.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-11: LINEAR DATA MEMORY MAP

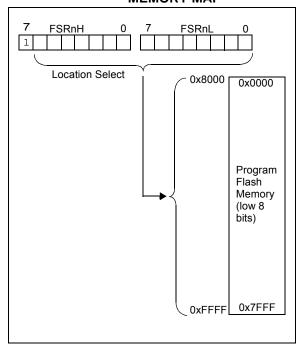

## 3.6.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire program Flash memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower eight bits of each memory location is accessible via INDF. Writing to the program Flash memory cannot be accomplished via the FSR/INDF interface. All instructions that access program Flash memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-12: PROGRAM FLASH MEMORY MAP

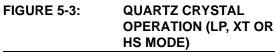

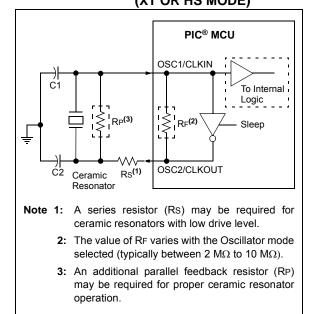

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices (DS00826)

- AN849, Basic PICmicro<sup>®</sup> Oscillator Design (DS00849)

- AN943, Practical PICmicro<sup>®</sup> Oscillator Analysis and Design (DS00943)

- AN949, Making Your Oscillator Work (DS00949)

## FIGURE 5-4:

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

## 5.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see **Section 5.4 "Two-Speed Clock Start-up Mode"**).

### 5.2.1.4 4x PLL

The oscillator module contains a 4x PLL that can be used with both external and internal clock sources to provide a system clock source. The input frequency for the 4x PLL must fall within specifications. See the PLL Clock Timing Specifications in **Section 30.0 "Electrical Specifications"**.

The 4x PLL may be enabled for use by one of two methods:

- 1. Program the PLLEN bit in Configuration Words to a '1'.

- Write the SPLLEN bit in the OSCCON register to a '1'. If the PLLEN bit in Configuration Words is programmed to a '1', then the value of SPLLEN is ignored.

### 5.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run-time. See **Section 5.3 "Clock Switching**"for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators and a dedicated Phase-Lock Loop, HFPLL that can produce one of three internal system clock sources.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase-Lock Loop, HFPLL. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 2. The **MFINTOSC** (Medium-Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 3. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

## 5.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory-calibrated 16 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of multiple frequencies derived from the HFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.7** "Internal **Oscillator Clock Switch Timing**" for more information.

The HFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'.

A fast start-up oscillator allows internal circuits to power-up and stabilize before switching to HFINTOSC.

The High-Frequency Internal Oscillator Ready bit (HFIOFR) of the OSCSTAT register indicates when the HFINTOSC is running.

The High-Frequency Internal Oscillator Status Locked bit (HFIOFL) of the OSCSTAT register indicates when the HFINTOSC is running within 2% of its final value.

The High-Frequency Internal Oscillator Stable bit (HFIOFS) of the OSCSTAT register indicates when the HFINTOSC is running within 0.5% of its final value.

### 5.2.2.2 MFINTOSC

The Medium-Frequency Internal Oscillator (MFINTOSC) is a factory calibrated 500 kHz internal clock source. The frequency of the MFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the MFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of nine frequencies derived from the MFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.7** "Internal Oscillator Clock Switch Timing" for more information.

The MFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

The Medium-Frequency Internal Oscillator Ready bit (MFIOFR) of the OSCSTAT register indicates when the MFINTOSC is running.

## 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1, PIE2, PIE3 and PIE4 registers)

The INTCON, PIR1, PIR2, PIR3 and PIR4 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 7.5 "Automatic Context Saving".")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

## 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is 3 or 4 instruction cycles. For asynchronous interrupts, the latency is 3 to 5 instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

| R/W-0/0<br>RC2IE<br>W = Writable | R/W-0/0<br>TX2IE                                            | U-0                                                     | U-0<br>—          | R/W-0/0<br>BCL2IE                                                                                                                             | R/W-0/0<br>SSP2IE<br>bit 0                                                                                                                    |

|----------------------------------|-------------------------------------------------------------|---------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| W = Writable                     | TX2IE                                                       | -                                                       | _                 | BCL2IE                                                                                                                                        |                                                                                                                                               |

|                                  |                                                             |                                                         |                   |                                                                                                                                               | bit 0                                                                                                                                         |

|                                  |                                                             |                                                         |                   |                                                                                                                                               |                                                                                                                                               |

|                                  |                                                             |                                                         |                   |                                                                                                                                               |                                                                                                                                               |

|                                  | bit                                                         | U = Unimpler                                            | mented bit, read  | as '0'                                                                                                                                        |                                                                                                                                               |

| x = Bit is unkr                  | nown                                                        | -n/n = Value a                                          | at POR and BOF    | R/Value at all o                                                                                                                              | ther Resets                                                                                                                                   |

| '0' = Bit is clea                | ared                                                        |                                                         |                   |                                                                                                                                               |                                                                                                                                               |

|                                  |                                                             |                                                         |                   |                                                                                                                                               |                                                                                                                                               |

| t <b>ed:</b> Read as '           | 0'                                                          |                                                         |                   |                                                                                                                                               |                                                                                                                                               |

| T2 Receive In                    | terrupt Enable                                              | e bit                                                   |                   |                                                                                                                                               |                                                                                                                                               |

| ne USART2 re<br>he USART2 re     | •                                                           |                                                         |                   |                                                                                                                                               |                                                                                                                                               |

| T2 Transmit In                   | terrupt Enable                                              | e bit                                                   |                   |                                                                                                                                               |                                                                                                                                               |

| ne USART2 tra<br>he USART2 tra   |                                                             |                                                         |                   |                                                                                                                                               |                                                                                                                                               |

| ted: Read as '                   | 0'                                                          |                                                         |                   |                                                                                                                                               |                                                                                                                                               |

| P2 Bus Collisi                   | on Interrupt E                                              | nable bit                                               |                   |                                                                                                                                               |                                                                                                                                               |

|                                  |                                                             |                                                         |                   |                                                                                                                                               |                                                                                                                                               |

| hronous Seria                    | I Port (MSSP2                                               | 2) Interrupt En                                         | able bit          |                                                                                                                                               |                                                                                                                                               |

|                                  |                                                             |                                                         |                   |                                                                                                                                               |                                                                                                                                               |

| ל<br>t                           | he MSSP2 Bu<br>he MSSP2 Bu<br>hronous Seria<br>e MSSP2 inte | ne MSSP2 Bus Collision Int<br>he MSSP2 Bus Collision In | e MSSP2 interrupt | ne MSSP2 Bus Collision Interrupt<br>he MSSP2 Bus Collision Interrupt<br>hronous Serial Port (MSSP2) Interrupt Enable bit<br>e MSSP2 interrupt | ne MSSP2 Bus Collision Interrupt<br>he MSSP2 Bus Collision Interrupt<br>hronous Serial Port (MSSP2) Interrupt Enable bit<br>e MSSP2 interrupt |

#### REGISTER 7-5: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

| Note: | Bit PEIE of the INTCON register must be |

|-------|-----------------------------------------|

|       | set to enable any peripheral interrupt. |

### 9.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

FIGURE 9-1:

- If the interrupt occurs **during or after** the execution of a **SLEEP** instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction is executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

|                          |                  |              |                       |         | •••••           |                   |             |             |

|--------------------------|------------------|--------------|-----------------------|---------|-----------------|-------------------|-------------|-------------|

| OSC1 <sup>(1)</sup>      | Q1 Q2 Q3 Q4      | Q1 Q2 Q3  Q4 | Q1                    |         | Q1 Q2 Q3 Q4     | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4 |             |

| CLKOUT <sup>(2)</sup>    |                  |              | ,<br>,<br>,           | Tost(3) |                 |                   |             |             |

| Interrupt flag           |                  |              | /                     |         | Interrupt Laten | <sub>CY</sub> (4) |             |             |

| GIE bit<br>(INTCON reg.) | · <u>·</u><br>·  |              | Processor in<br>Sleep | ''      |                 |                   |             |             |

| nstruction Flow<br>PC    |                  | ( PC + 1     | X PC                  | + 2     | X PC + 2        | ( PC + 2          | X 0004h     | X 0005h     |

| Instruction {<br>Fetched | Inst(PC) = Sleep | Inst(PC + 1) | 1<br>1<br>1           |         | Inst(PC + 2)    |                   | Inst(0004h) | Inst(0005h) |

| Instruction J            | Inst(PC - 1)     | Sleep        | 1<br>1                |         | Inst(PC + 1)    | Forced NOP        | Forced NOP  | Inst(0004h) |

2: CLKOUT is not available in XT, HS, or LP Oscillator modes, but shown here for timing reference.

3: TOST = 1024 TOSC (drawing not to scale). This delay applies only to XT, HS or LP Oscillator modes.

WAKE-UP FROM SLEEP THROUGH INTERRUPT

4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

#### TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name   | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|--------|---------|--------|--------|--------|------------|--------|--------|--------|---------------------|

| INTCON | GIE     | PEIE   | TMR0IE | INTE   | IOCIE      | TMR0IF | INTF   | IOCIF  | 90                  |

| IOCBF  | IOCBF7  | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3     | IOCBF2 | IOCBF1 | IOCBF0 | 148                 |

| IOCBN  | IOCBN7  | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3     | IOCBN2 | IOCBN1 | IOCBN0 | 148                 |

| IOCBP  | IOCBP7  | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3     | IOCBP2 | IOCBP1 | IOCBP0 | 148                 |

| PIE1   | TMR1GIE | ADIE   | RCIE   | TXIE   | SSPIE      | CCP1IE | TMR2IE | TMR1IE | 91                  |

| PIE2   | OSFIE   | C2IE   | C1IE   | EEIE   | BCLIE      | LCDIE  | C3IE   | CCP2IE | 92                  |

| PIE3   | —       | CCP5IE | CCP4IE | CCP3IE | TMR6IE     | _      | TMR4IE | _      | 93                  |

| PIE4   | —       | _      | RC2IE  | TX2IE  | _          | _      | BCL2IE | SSP2IE | 94                  |

| PIR1   | TMR1GIF | ADIF   | RCIF   | TXIF   | SSPIF      | CCP1IF | TMR2IF | TMR1IF | 95                  |

| PIR2   | OSFIF   | C2IF   | C1IF   | EEIF   | BCLIF      | LCDIF  | C3IF   | CCP2IF | 96                  |

| PIR3   | _       | CCP5IF | CCP4IF | CCP3IF | TMR6IF     | _      | TMR4IF | _      | 97                  |

| PIR4   | _       | —      | RC2IF  | TX2IF  | _          | _      | BCL2IF | SSP2IF | 98                  |

| STATUS | _       | _      | _      | TO     | PD         | Z      | DC     | С      | 22                  |

| WDTCON |         |        |        |        | WDTPS<4:0> |        |        | SWDTEN | 104                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

© 2010-2016 Microchip Technology Inc.

## 13.6 Register Definitions: Interrupt-on-Change Control

| u = Bit is unchanged x = Bit is unknown |         |         |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |  |

|-----------------------------------------|---------|---------|---------|-------------------------------------------------------|---------|---------|---------|--|--|--|

| R = Readable bit W = Writable bit       |         |         | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |  |

| Legend:                                 |         |         |         |                                                       |         |         |         |  |  |  |

| bit 7                                   |         |         |         |                                                       |         |         | bit 0   |  |  |  |

| IOCBP7                                  | IOCBP6  | IOCBP5  | IOCBP4  | IOCBP3                                                | IOCBP2  | IOCBP1  | IOCBP0  |  |  |  |

| R/W-0/0                                 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

#### REGISTER 13-1: IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER

bit 7-0

'1' = Bit is set

IOCBP<7:0>: Interrupt-on-Change PORTB Positive Edge Enable bits

- 1 = Interrupt-on-change enabled on the pin for a positive going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-change disabled for the associated pin.

'0' = Bit is cleared

#### REGISTER 13-2: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **IOCBN<7:0>:** Interrupt-on-Change PORTB Negative Edge Enable bits

- 1 = Interrupt-on-change enabled on the pin for a negative going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-change disabled for the associated pin.

#### REGISTER 13-3: IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | IOCBF3     | IOCBF2     | IOCBF1     | IOCBF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0 IOCBF<7:0>: Interrupt-on-Change PORTB Flag bits

- 1 = An enabled change was detected on the associated pin.

- Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.

- 0 = No change was detected, or the user cleared the detected change.

## 16.4 Register Definitions: ADC Control

| U-0                           | R/W-0/0                  | R/W-0/0                                | R/W-0/0        | R/W-0/0                      | R/W-0/0         | R/W-0/0           | R/W-0/0        |  |  |  |  |

|-------------------------------|--------------------------|----------------------------------------|----------------|------------------------------|-----------------|-------------------|----------------|--|--|--|--|

| _                             |                          |                                        | CHS<4:0>       |                              |                 | GO/DONE           | ADON           |  |  |  |  |

| oit 7                         |                          |                                        |                |                              |                 |                   | bit            |  |  |  |  |

|                               |                          |                                        |                |                              |                 |                   |                |  |  |  |  |

| L <b>egend:</b><br>R = Readat | le hit                   | W = Writable                           | hit            | II – Unimpler                | nented bit, rea | ud as 'O'         |                |  |  |  |  |

| u = Bit is un                 |                          | x = Bit is unkl                        |                |                              |                 | OR/Value at all o | other Decete   |  |  |  |  |

| "1' = Bit is s                | U                        | '0' = Bit is cle                       |                |                              |                 |                   |                |  |  |  |  |

| 1 – Dit is s                  | ει                       |                                        | areu           |                              |                 |                   |                |  |  |  |  |

| bit 7                         | Unimpleme                | nted: Read as                          | 0'             |                              |                 |                   |                |  |  |  |  |

| oit 6-2                       | CHS<4:0>:                | Analog Channe                          | I Select bits  |                              |                 |                   |                |  |  |  |  |

|                               |                          | R (Fixed Voltage                       | e Reference) E | Buffer 1 Output <sup>(</sup> | 2)              |                   |                |  |  |  |  |

|                               | 11110 <b>= DA</b>        |                                        | (3)            |                              |                 |                   |                |  |  |  |  |

|                               |                          | nperature Indica<br>served. No cha     |                | ч                            |                 |                   |                |  |  |  |  |

|                               | •                        |                                        |                | u.                           |                 |                   |                |  |  |  |  |

|                               | •                        |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               | •                        |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               |                          | 0001 = Reserved. No channel connected. |                |                              |                 |                   |                |  |  |  |  |

|                               | 10000 = AN<br>01111 = AN |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               | 01110 <b>= AN</b>        |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               | 01101 = AN               |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               | 01100 <b>= AN</b>        |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               | 01011 = AN               |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               | 01010 = AN<br>01001 = AN |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               | 01000 = AN               |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               | 00111 <b>= AN</b>        |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               | 00110 <b>= AN</b>        | 6                                      |                |                              |                 |                   |                |  |  |  |  |

|                               | 00101 <b>= AN</b>        |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               | 00100 = AN               |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               | 00011 = AN<br>00010 = AN |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               | 00001 = AN               |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               | 00000 <b>=AN</b>         | )                                      |                |                              |                 |                   |                |  |  |  |  |

| bit 1                         | GO/DONE:                 | A/D Conversion                         | Status bit     |                              |                 |                   |                |  |  |  |  |

|                               |                          | version cycle in                       |                |                              |                 |                   | od             |  |  |  |  |

|                               |                          | version complet                        |                |                              |                 | ion has complet   | . <del>.</del> |  |  |  |  |

| bit 0                         | ADON: ADC                | Enable bit                             |                |                              |                 |                   |                |  |  |  |  |

|                               | 1 = ADC is e             |                                        |                |                              |                 |                   |                |  |  |  |  |

|                               | 0 = ADC is c             | lisabled and co                        | nsumes no op   | erating current              |                 |                   |                |  |  |  |  |

| Note 1: S                     | See Section 17.0         | ) "Digital-to-Ar                       | nalog Conver   | ter (DAC) Mod                | ule" for more   | information.      |                |  |  |  |  |

| 2: 8                          | See Section 14.0         | ) "Fixed Voltag                        | e Reference    | (FVR)" for more              | e information.  |                   |                |  |  |  |  |

|                               |                          |                                        |                |                              |                 |                   |                |  |  |  |  |

## REGISTER 16-1: ADCON0: A/D CONTROL REGISTER 0

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |

|---------|--------|--------|--------|--------|--------|-----------|--------|--------|---------------------|

| ANSELF  | ANSF7  | ANSF6  | ANSF5  | ANSF4  | ANSF3  | ANSF2     | ANSF1  | ANSF0  | 141                 |

| ANSELG  | —      | —      | _      | ANSG4  | ANSG3  | ANSG2     | ANSG1  | _      | 144                 |

| CM1CON0 | C10N   | C1OUT  | C10E   | C1POL  | _      | C1SP      | C1HYS  | C1SYNC | 178                 |

| CM2CON0 | C2ON   | C2OUT  | C2OE   | C2POL  | _      | C2SP      | C2HYS  | C2SYNC | 178                 |

| CM1CON1 | C1NTP  | C1INTN | C1PCI  | H<1:0> | _      | —         | C1NCI  | H<1:0> | 179                 |

| CM2CON1 | C2NTP  | C2INTN | C2PCI  | H<1:0> | _      | _         | C2NCI  | H<1:0> | 179                 |

| CM3CON0 | C3ON   | C3OUT  | C3OE   | C3POL  | _      | C3SP      | C3HYS  | C3SYNC | 178                 |

| CM3CON1 | C3INTP | C3INTN | C3PCH1 | C3PCH0 | _      | _         | C3NCI  | H<1:0> | 179                 |

| CMOUT   | _      | _      | _      | _      | _      | MC3OUT    | MC2OUT | MC10UT | 179                 |

| FVRCON  | FVREN  | FVRRDY | TSEN   | TSRNG  | CDAFV  | ′R<1:0>   | ADFV   | R<1:0> | 151                 |

| DACCON0 | DACEN  | DACLPS | DACOE  | _      | DACPS  | SS<1:0>   | _      | DACNSS | 171                 |

| DACCON1 | _      | _      | _      |        |        | DACR<4:0> |        | •      | 171                 |

| INTCON  | GIE    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF    | INTF   | IOCIF  | 90                  |

| PIE2    | OSFIE  | C2IE   | C1IE   | EEIE   | BCLIE  | LCDIE     | C3IE   | CCP2IE | 92                  |

| PIR2    | OSFIF  | C2IF   | C1IF   | EEIF   | BCLIF  | LCDIF     | C3IF   | CCP2IF | 96                  |

| TRISF   | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2    | TRISF1 | TRISF0 | 140                 |

| TRISG   | _      | —      | TRISG5 | TRISG4 | TRISG3 | TRISG2    | TRISG1 | TRISG0 | 143                 |

#### TABLE 18-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARATOR MODULE

Legend: — = unimplemented location, read as '0'. Shaded cells are unused by the comparator module.

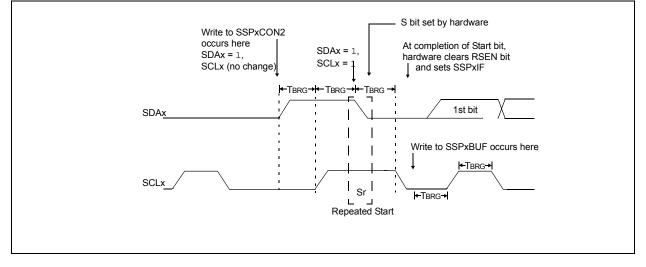

## 24.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit of the SSPxCON2 register is programmed high and the Master state machine is no longer active. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. SCLx is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- **Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

## FIGURE 24-27: REPEAT START CONDITION WAVEFORM

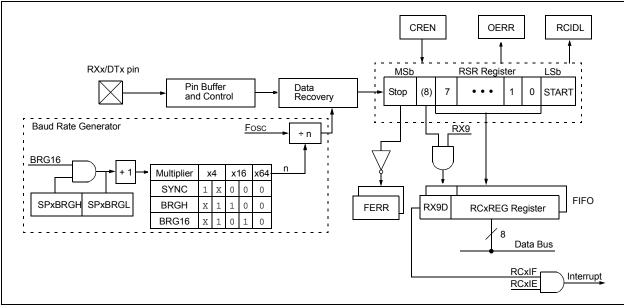

## FIGURE 25-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXxSTA)

- Receive Status and Control (RCxSTA)

- Baud Rate Control (BAUDxCON)

These registers are detailed in Register 25-1, Register 25-2 and Register 25-3, respectively.

For all modes of the EUSART operation, the TRIS control bits corresponding to the RXx/DTx and TXx/CKx pins should be set to '1'. The EUSART control will automatically reconfigure the pin from input to output, as needed.

When the receiver or transmitter section is not enabled, then the corresponding RXx/DTx or TXx/CKx pin may be used for general purpose input and output.

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                        | R/W-0                                 | R/W-0   | R/W-0                | R-0                       | R-0                | R-x   |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------|----------------------|---------------------------|--------------------|-------|--|

| SPEN          | RX9                                                                                                                                                                                                                                                                          | SREN                                  | CREN    | ADDEN                | FERR                      | OERR               | RX9D  |  |

| bit 7         |                                                                                                                                                                                                                                                                              |                                       |         |                      |                           | •                  | bit ( |  |

| Legend:       |                                                                                                                                                                                                                                                                              |                                       |         |                      |                           |                    |       |  |

| R = Readable  | e bit                                                                                                                                                                                                                                                                        | W = Writable                          | bit     | U = Unimplen         | nented bit, rea           | ad as '0'          |       |  |

| -n = Value at | POR                                                                                                                                                                                                                                                                          | '1' = Bit is set                      |         | '0' = Bit is cleared |                           | x = Bit is unknown |       |  |

| bit 7         | SPEN: Seri                                                                                                                                                                                                                                                                   | al Port Enable b                      | it      |                      |                           |                    |       |  |

|               |                                                                                                                                                                                                                                                                              | port enabled (co<br>port disabled (he |         | DTx and TXx/CI       | <pre>Kx pins as sei</pre> | rial port pins)    |       |  |

| bit 6         | RX9: 9-bit F                                                                                                                                                                                                                                                                 | Receive Enable                        | bit     |                      |                           |                    |       |  |

|               |                                                                                                                                                                                                                                                                              | 9-bit reception<br>8-bit reception    |         |                      |                           |                    |       |  |

| bit 5         | SREN: Sing                                                                                                                                                                                                                                                                   | gle Receive Ena                       | ble bit |                      |                           |                    |       |  |

|               | Asynchronous mode:                                                                                                                                                                                                                                                           |                                       |         |                      |                           |                    |       |  |

|               | Don't care                                                                                                                                                                                                                                                                   |                                       |         |                      |                           |                    |       |  |

|               | Synchronous mode – Master:                                                                                                                                                                                                                                                   |                                       |         |                      |                           |                    |       |  |

|               | 1 = Enables single receive                                                                                                                                                                                                                                                   |                                       |         |                      |                           |                    |       |  |

|               | <ul> <li>0 = Disables single receive</li> <li>This bit is cleared after reception is complete.</li> </ul>                                                                                                                                                                    |                                       |         |                      |                           |                    |       |  |

|               | Synchronous mode – Slave                                                                                                                                                                                                                                                     |                                       |         |                      |                           |                    |       |  |

|               | Don't care                                                                                                                                                                                                                                                                   |                                       |         |                      |                           |                    |       |  |

| bit 4         | CREN: Continuous Receive Enable bit                                                                                                                                                                                                                                          |                                       |         |                      |                           |                    |       |  |

|               | Asynchronous mode:                                                                                                                                                                                                                                                           |                                       |         |                      |                           |                    |       |  |

|               | 1 = Enables receiver                                                                                                                                                                                                                                                         |                                       |         |                      |                           |                    |       |  |

|               | 0 = Disables receiver                                                                                                                                                                                                                                                        |                                       |         |                      |                           |                    |       |  |

|               | Synchronous mode:                                                                                                                                                                                                                                                            |                                       |         |                      |                           |                    |       |  |

|               | <ul> <li>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</li> <li>0 = Disables continuous receive</li> </ul>                                                                                                                           |                                       |         |                      |                           |                    |       |  |

| bit 3         | ADDEN: Address Detect Enable bit                                                                                                                                                                                                                                             |                                       |         |                      |                           |                    |       |  |

|               | Asynchronous mode 9-bit (RX9 = 1):                                                                                                                                                                                                                                           |                                       |         |                      |                           |                    |       |  |

|               | <ul> <li>1 = Enables address detection, enable interrupt and load the receive buffer when RSR&lt;8&gt; is set</li> <li>0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit</li> <li>Asynchronous mode 8-bit (RX9 = 0):</li> </ul> |                                       |         |                      |                           |                    |       |  |

|               | Don't care                                                                                                                                                                                                                                                                   |                                       |         |                      |                           |                    |       |  |

| bit 2         | FERR: Frar                                                                                                                                                                                                                                                                   | ning Error bit                        |         |                      |                           |                    |       |  |

|               | <ul> <li>1 = Framing error (can be updated by reading RCxREG register and receive next valid byte)</li> <li>0 = No framing error</li> </ul>                                                                                                                                  |                                       |         |                      |                           |                    |       |  |

| bit 1         | OERR: Overrun Error bit                                                                                                                                                                                                                                                      |                                       |         |                      |                           |                    |       |  |

|               | <ul><li>1 = Overrun error (can be cleared by clearing bit CREN)</li><li>0 = No overrun error</li></ul>                                                                                                                                                                       |                                       |         |                      |                           |                    |       |  |

| bit 0         |                                                                                                                                                                                                                                                                              |                                       |         |                      |                           |                    |       |  |

| bit 0         | RX9D: Nint                                                                                                                                                                                                                                                                   | h bit of Received                     | d Data  |                      |                           |                    |       |  |

## REGISTER 25-2: RCxSTA: RECEIVE STATUS AND CONTROL REGISTER

| REGISTER 2<br>R-0/0 | R-1/1                                                                                                                                                                                          |                                                                                                                        | R/W-0/0         | R/W-0/0       | U-0               | R/W-0/0          | R/W-0/0       |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|-------------------|------------------|---------------|

| ABDOVF              | RCIDL                                                                                                                                                                                          | 0-0                                                                                                                    | SCKP            | BRG16         | 0-0               | WUE              | ABDEN         |

| bit 7               | RCIDL                                                                                                                                                                                          | —                                                                                                                      | SURP            | BRG10         | —                 | WUE              | bit 0         |

|                     |                                                                                                                                                                                                |                                                                                                                        |                 |               |                   |                  | DILU          |

| Legend:             |                                                                                                                                                                                                |                                                                                                                        |                 |               |                   |                  |               |

| R = Readable        | bit                                                                                                                                                                                            | W = Writable                                                                                                           | hit             | II = Unimple  | mented bit read   | as '0'           |               |

| u = Bit is unch     |                                                                                                                                                                                                | W = Writable bitU = Unimplemented bit, read as '0'x = Bit is unknown-n/n = Value at POR and BOR/Value at all other Res |                 |               |                   |                  | ther Resets   |

| '1' = Bit is set    | langea                                                                                                                                                                                         | '0' = Bit is cleared                                                                                                   |                 |               |                   |                  |               |

|                     |                                                                                                                                                                                                | 0 2000 000                                                                                                             |                 |               |                   |                  |               |

| bit 7               | ABDOVF: Au                                                                                                                                                                                     | to-Baud Detec                                                                                                          | t Overflow bit  |               |                   |                  |               |

|                     | Asynchronous mode:<br>1 = Auto-baud timer overflowed<br>0 = Auto-baud timer did not overflow<br>Synchronous mode:<br>Don't care                                                                |                                                                                                                        |                 |               |                   |                  |               |

| bit 6               | RCIDL: Receive Idle Flag bit<br><u>Asynchronous mode</u> :<br>1 = Receiver is Idle<br>0 = Start bit has been received and the receiver is receiving<br><u>Synchronous mode</u> :<br>Don't care |                                                                                                                        |                 |               |                   |                  |               |

| bit 5               | Unimplemen                                                                                                                                                                                     | ted: Read as '                                                                                                         | 0'              |               |                   |                  |               |

| bit 4               | SCKP: Synchronous Clock Polarity Select bit                                                                                                                                                    |                                                                                                                        |                 |               |                   |                  |               |

|                     | Asynchronous mode:                                                                                                                                                                             |                                                                                                                        |                 |               |                   |                  |               |

|                     | <ul> <li>1 = Transmit inverted data to the TXx/CKx pin</li> <li>0 = Transmit non-inverted data to the TXx/CKx pin</li> </ul>                                                                   |                                                                                                                        |                 |               |                   |                  |               |

|                     |                                                                                                                                                                                                | <u>mode</u> :<br>ocked on rising<br>ocked on falling                                                                   |                 |               |                   |                  |               |

| bit 3               | <ul> <li>BRG16: 16-bit Baud Rate Generator bit</li> <li>1 = 16-bit Baud Rate Generator is used</li> <li>0 = 8-bit Baud Rate Generator is used</li> </ul>                                       |                                                                                                                        |                 |               |                   |                  |               |

| bit 2               | Unimplemented: Read as '0'                                                                                                                                                                     |                                                                                                                        |                 |               |                   |                  |               |

| bit 1               | WUE: Wake-up Enable bit                                                                                                                                                                        |                                                                                                                        |                 |               |                   |                  |               |

|                     | will autom                                                                                                                                                                                     | is waiting for a<br>atically clear a<br>is operating no                                                                | fter RCIF is se |               | will be received, | , byte RCIF will | l be set. WUE |

| bit 0               | Asynchronous<br>1 = Auto-Bau                                                                                                                                                                   | id Detect mode<br>id Detect mode                                                                                       | e is enabled (o | lears when au | to-baud is comp   | ilete)           |               |

## 25.4.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDxCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPxBRGH:SPxBRGL register pair. After the ABDOVF bit has been set, the counter continues to count until the fifth rising edge is detected on the RXx/DTx pin. Upon detecting the fifth RXx/DTx edge, the hardware will set the RCxIF interrupt flag and clear the ABDEN bit of the BAUDxCON register. The RCxIF flag can be subsequently cleared by reading the RCxREG. The ABDOVF flag can be cleared by software directly.

To terminate the auto-baud process before the RCxIF flag is set, clear the ABDEN bit then clear the ABDOVF bit. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

#### 25.4.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RXx/DTx line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDxCON register. Once set, the normal receive sequence on RXx/DTx is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RXx/DTx line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCxIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 25-7), and asynchronously if the device is in Sleep mode (Figure 25-8). The interrupt condition is cleared by reading the RCxREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RXx line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 25.4.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Startup Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCxIF bit. The WUE bit is cleared by hardware by a rising edge on RXx/DTx. The interrupt condition is then cleared by software by reading the RCxREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

#### 25.5.1.5 Synchronous Master Reception

Data is received at the RXx/DTx pin. The RXx/DTx pin output driver must be disabled by setting the corresponding TRIS bits when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCxSTA register) or the Continuous Receive Enable bit (CREN of the RCxSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RXx/DTx pin on the trailing edge of the TXx/CKx clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCxIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCxREG. The RCxIF bit remains set as long as there are un-read characters in the receive FIFO.

#### 25.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TXx/CKx line. The TXx/CKx pin output driver must be disabled by setting the associated TRIS bit when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

### 25.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCxREG is read to access the FIFO. When this happens the OERR bit of the RCxSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCxREG.

If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

#### 25.5.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

## 25.5.1.9 Synchronous Master Reception Setup:

- 1. Initialize the SPxBRGH, SPxBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Set the RXx/DTx and TXx/CKx TRIS controls to '1'.

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC. Disable RXx/DTx and TXx/CKx output drivers by setting the corresponding TRIS bits.

- 4. Ensure bits CREN and SREN are clear.

- 5. If using interrupts, set the GIE and PEIE bits of the INTCON register and set RCxIE.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RCxIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCxIE was set.

- 9. Read the RCxSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.