Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | DMA, I²S, POR, PWM, WDT                                               |

| Number of I/O              | 37                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 8x12b; D/A 1x12b                                                  |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f301c6t6 |

|        |            | 3.15.4    | Independent watchdog (IWDG)                                   | . 24 |

|--------|------------|-----------|---------------------------------------------------------------|------|

|        |            | 3.15.5    | Window watchdog (WWDG)                                        | . 24 |

|        |            | 3.15.6    | SysTick timer                                                 | . 24 |

|        | 3.16       | Real-tim  | ne clock (RTC) and backup registers                           | . 24 |

|        | 3.17       | Inter-int | egrated circuit interfaces (I <sup>2</sup> C)                 | . 26 |

|        | 3.18       | Univers   | al synchronous/asynchronous receiver transmitter (USART)      | . 27 |

|        | 3.19       |           | eripheral interfaces (SPI)/Inter-integrated sound<br>es (I2S) | . 27 |

|        | 3.20       | Touch s   | ensing controller (TSC)                                       | . 28 |

|        | 3.21       | Infrared  | transmitter                                                   | . 30 |

|        | 3.22       | Develop   | oment support                                                 | . 31 |

|        |            | 3.22.1    | Serial wire JTAG debug port (SWJ-DP)                          |      |

| 4      | <b>D</b> ' | 4         |                                                               | 00   |

| 4      | Pinou      | its and   | pin description                                               | . 32 |

| 5      | Memo       | ory map   | ping                                                          | . 49 |

| 5<br>6 | <b>-</b>   |           |                                                               |      |

| 6      |            |           | aracteristics                                                 |      |

|        | 6.1        |           | ter conditions                                                |      |

|        |            | 6.1.1     | Minimum and maximum values                                    |      |

|        |            | 6.1.2     | Typical values                                                |      |

|        |            | 6.1.3     | Typical curves                                                |      |

|        |            | 6.1.4     | Loading capacitor                                             |      |

|        |            | 6.1.5     | Pin input voltage                                             |      |

|        |            | 6.1.6     | Power supply scheme                                           | . 53 |

|        |            | 6.1.7     | Current consumption measurement                               | . 54 |

|        | 6.2        | Absolute  | e maximum ratings                                             | . 55 |

|        | 6.3        | Operatir  | ng conditions                                                 | . 57 |

|        |            | 6.3.1     | General operating conditions                                  | . 57 |

|        |            | 6.3.2     | Operating conditions at power-up / power-down                 | . 58 |

|        |            | 6.3.3     | Embedded reset and power control block characteristics        | . 58 |

|        |            | 6.3.4     | Embedded reference voltage                                    | . 60 |

|        |            | 6.3.5     | Supply current characteristics                                | . 60 |

|        |            | 6.3.6     | Wakeup time from low-power mode                               | . 72 |

|        |            | 6.3.7     | External clock source characteristics                         |      |

|        |            |           |                                                               |      |

|        |            | 6.3.8     | Internal clock source characteristics                         | . 79 |

| Table 48. | Flash memory endurance and data retention                               |

|-----------|-------------------------------------------------------------------------|

| Table 49. | EMS characteristics                                                     |

| Table 50. | EMI characteristics                                                     |

| Table 51. | ESD absolute maximum ratings                                            |

| Table 52. | Electrical sensitivities                                                |

| Table 53. | I/O current injection susceptibility                                    |

| Table 54. | I/O static characteristics                                              |

| Table 55. | Output voltage characteristics                                          |

| Table 56. | I/O AC characteristics                                                  |

| Table 57. | NRST pin characteristics                                                |

| Table 58. | TIMx characteristics                                                    |

| Table 59. | IWDG min/max timeout period at 40 kHz (LSI)92                           |

| Table 60. | WWDG min-max timeout value @72 MHz (PCLK)92                             |

| Table 61. | I2C analog filter characteristics93                                     |

| Table 62. | SPI characteristics                                                     |

| Table 63. | I2S characteristics                                                     |

| Table 64. | ADC characteristics                                                     |

| Table 65. | Maximum ADC RAIN                                                        |

| Table 66. | ADC accuracy - limited test conditions                                  |

| Table 67. | ADC accuracy                                                            |

| Table 68. | ADC accuracy                                                            |

| Table 69. | DAC characteristics                                                     |

| Table 70. | Comparator characteristics                                              |

| Table 71. | Operational amplifier characteristics111                                |

| Table 72. | TS characteristics                                                      |

| Table 73. | Temperature sensor calibration values114                                |

| Table 74. | V <sub>BAT</sub> monitoring characteristics                             |

| Table 75. | WLCSP49 - 49-pin, 3.417 x 3.151 mm, 0.4 mm pitch wafer level chip scale |

|           | package mechanical data                                                 |

| Table 76. | WLCSP49 recommended PCB design rules (0.4 mm pitch)                     |

| Table 77. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat                       |

|           | package mechanical data                                                 |

| Table 78. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                 |

|           | mechanical data                                                         |

| Table 79. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat |

|           | package mechanical data                                                 |

| Table 80. | Package thermal characteristics                                         |

| Table 81. | Ordering information scheme                                             |

| Table 82. | Document revision history                                               |

# 2 Description

The STM32F301x6/8 family is based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 72 MHz and embedding a floating point unit (FPU). The family incorporates high-speed embedded memories (up to 64 Kbytes of Flash memory, 16 Kbytes of SRAM), and an extensive range of enhanced I/Os and peripherals connected to two APB buses.

The devices offer a fast 12-bit ADC (5 Msps), three comparators, an operational amplifier, up to 18 capacitive sensing channels, one DAC channel, a low-power RTC, one general-purpose 32-bit timer, one timer dedicated to motor control, and up to three general-purpose 16-bit timers, and one timer to drive the DAC. They also feature standard and advanced communication interfaces: three I<sup>2</sup>Cs, up to three USARTs, up to two SPIs with multiplexed full-duplex I2S, and an infrared transmitter.

The STM32F301x6/8 family operates in the –40 to +85°C and –40 to +105°C temperature ranges from at a 2.0 to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F301x6/8 family offers devices in 32-, 48-, 49- and 64-pin packages.

The set of included peripherals changes with the device chosen.

# 3.7 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example with failure of an indirectly used external oscillator).

Several prescalers allow to configure the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and the high speed APB domains is 72 MHz, while the maximum allowed frequency of the low speed APB domain is 36 MHz.

The advanced clock controller clocks the core and all peripherals using a single crystal or oscillator. To achieve audio class performance, an audio crystal can be used.

#### Inter-integrated circuit interfaces (I<sup>2</sup>C) 3.17

The devices feature three I<sup>2</sup>C bus interfaces which can operate in multimaster and slave mode. Each I2C interface can support standard (up to 100 kHz), fast (up to 400 kHz) and fast mode + (up to 1 MHz) modes.

All I<sup>2</sup>C interfaces support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask). They also include programmable analog and digital noise filters.

Table 6. Comparison of I2C analog and digital filters

|                                  | Analog filter                                         | Digital filter                                                                     |

|----------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------|

| Pulse width of suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15 I2C peripheral clocks                             |

| Benefits                         | Available in Stop mode                                | Extra filtering capability vs. standard requirements.     Stable length            |

| Drawbacks                        | Variations depending on temperature, voltage, process | Wakeup from Stop on address match is not available when digital filter is enabled. |

In addition, it provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. It also has a clock domain independent from the CPU clock, allowing the I2Cx (x=1,3) to wake up the MCU from Stop mode on address match.

The I2C interfaces can be served by the DMA controller.

Refer to Table 7 for the features available in I2C1, I2C2 and I2C3.

Table 7. STM32F301x6/8 I<sup>2</sup>C implementation

| I2C features <sup>(1)</sup>                                 | I2C1 | I2C2 | I2C3 |

|-------------------------------------------------------------|------|------|------|

| 7-bit addressing mode                                       | Х    | Х    | Х    |

| 10-bit addressing mode                                      | Х    | Х    | Х    |

| Standard mode (up to 100 kbit/s)                            | Х    | Х    | Х    |

| Fast mode (up to 400 kbit/s)                                | Х    | Х    | Х    |

| Fast Mode Plus with 20mA output drive I/Os (up to 1 Mbit/s) | Х    | Х    | Х    |

| Independent clock                                           | Х    | Х    | Х    |

| SMBus                                                       | Х    | Х    | Х    |

| Wakeup from STOP                                            | Х    | Х    | Х    |

<sup>1.</sup> X = supported.

DocID025146 Rev 6 26/135

Analog I/O group

Number of capacitive sensing channels

STM32F301Rx

STM32F301Cx

STM32F301Kx

G6

3

3

0

Number of capacitive sensing channels

18

17

13

Table 11. No. of capacitive sensing channels available on STM32F301x6/8 devices (continued)

## 3.21 Infrared transmitter

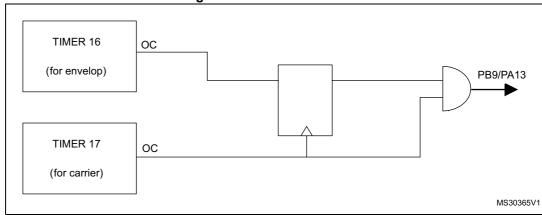

The STM32F301x6/8 devices provide an infrared transmitter solution. The solution is based on internal connections between TIM16 and TIM17 as shown in the figure below.

TIM17 is used to provide the carrier frequency and TIM16 provides the main signal to be sent. The infrared output signal is available on PB9 or PA13.

To generate the infrared remote control signals, TIM16 channel 1 and TIM17 channel 1 must be properly configured to generate correct waveforms. All standard IR pulse modulation modes can be obtained by programming the two timers output compare channels.

Figure 3. Infrared transmitter

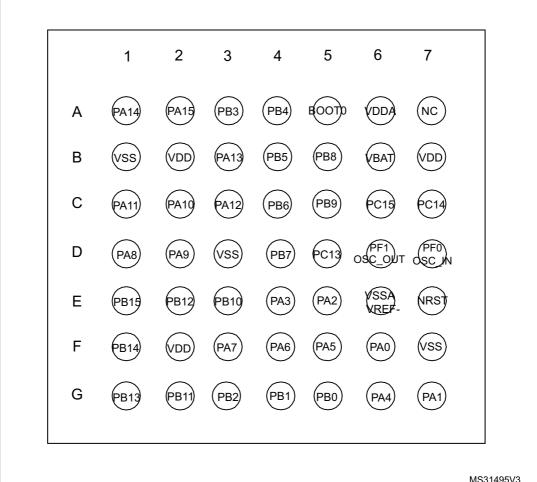

Figure 7. STM32F301x6/8 WLCSP49 ballout

MS31495V3

- 1. The above figure shows the package top view.

- 2. NC: Not connected.

Table 16. Alternate functions for Port C

|                 | AF0    | AF1                                  | AF2                      | AF3                | AF4                            | AF5                                 | AF6                                       | AF7                                      |

|-----------------|--------|--------------------------------------|--------------------------|--------------------|--------------------------------|-------------------------------------|-------------------------------------------|------------------------------------------|

| Port & pin name | SYS_AF | TIM2/TIM15/<br>TIM16/TIM17/<br>EVENT | I2C3/TIM1/TIM2<br>/TIM15 | I2C3/TIM15/<br>TSC | I2C1/I2C2/TIM1/<br>TIM16/TIM17 | SPI2/I2S2/<br>SPI3/I2S3<br>Infrared | SPI2/I2S2/SPI3/<br>I2S3/TIM1/<br>Infrared | USART1/<br>USART2/<br>USART3/<br>GPCOMP6 |

| PC0             | -      | EVENTOUT                             | TIM1_CH1                 | -                  | -                              | -                                   | -                                         | -                                        |

| PC1             | -      | EVENTOUT                             | TIM1_CH2                 | -                  | -                              | -                                   | -                                         | -                                        |

| PC2             | -      | EVENTOUT                             | TIM1_CH3                 | -                  | -                              | -                                   | -                                         | -                                        |

| PC3             | -      | EVENTOUT                             | TIM1_CH4                 | -                  | -                              | -                                   | TIM1_BKIN2                                | -                                        |

| PC4             | -      | EVENTOUT                             | TIM1_ETR                 | -                  | -                              | -                                   | -                                         | USART1_TX                                |

| PC5             | -      | EVENTOUT                             | TIM15_BKIN               | TSC_G3_IO1         | -                              | -                                   | -                                         | USART1_RX                                |

| PC6             | -      | EVENTOUT                             | -                        | -                  | -                              | -                                   | I2S2_MCK                                  | COMP6_OUT                                |

| PC7             | -      | EVENTOUT                             | -                        | -                  | -                              | -                                   | I2S3_MCK                                  | -                                        |

| PC8             | -      | EVENTOUT                             | -                        | -                  | -                              | -                                   | -                                         | -                                        |

| PC9             | -      | EVENTOUT                             | -                        | I2C3_SDA           | -                              | I2SCKIN                             | -                                         | -                                        |

| PC10            | -      | EVENTOUT                             | -                        | -                  | -                              | -                                   | SPI3_SCK/<br>I2S3_CK                      | USART3_TX                                |

| PC11            | -      | EVENTOUT                             | -                        | -                  | -                              | -                                   | SPI3_MISO/<br>I2S3ext_SD                  | USART3_RX                                |

| PC12            | -      | EVENTOUT                             | -                        | -                  | -                              | -                                   | SPI3_MOSI/<br>I2S3_SD                     | USART3_CK                                |

| PC13            | -      | -                                    | -                        | -                  | TIM1_CH1N                      | -                                   | -                                         | -                                        |

| PC14            | -      | -                                    | -                        | -                  | -                              | -                                   | -                                         | -                                        |

| PC15            | -      | -                                    | -                        | -                  | -                              | -                                   | -                                         | -                                        |

**Table 21. Current characteristics**

| Symbol                | Ratings                                                                         | Max.  | Unit |

|-----------------------|---------------------------------------------------------------------------------|-------|------|

| $\Sigma I_{VDD}$      | Total current into sum of all VDD_x power lines (source)                        | 130   |      |

| Σl <sub>VSS</sub>     | Total current out of sum of all VSS_x ground lines (sink)                       | -130  |      |

| I <sub>VDD</sub>      | Maximum current into each V <sub>DD_x</sub> power line (source) <sup>(1)</sup>  | 100   |      |

| I <sub>VSS</sub>      | Maximum current out of each V <sub>SS_x</sub> ground line (sink) <sup>(1)</sup> | -100  |      |

|                       | Output current sunk by any I/O and control pin                                  | 25    |      |

| I <sub>IO(PIN)</sub>  | Output current sourced by any I/O and control pin                               | -25   |      |

| 21                    | Total output current sunk by sum of all IOs and control pins <sup>(2)</sup>     | 80    | - mA |

| $\Sigma I_{IO(PIN)}$  | Total output current sourced by sum of all IOs and control pins <sup>(2)</sup>  | -80   |      |

|                       | Injected current on TT, FT, FTf and B pins <sup>(3)</sup>                       | -5/+0 |      |

| I <sub>INJ(PIN)</sub> | Injected current on TC and RST pin <sup>(4)</sup>                               | +/-5  |      |

|                       | Injected current on TTa pins <sup>(5)</sup>                                     | +/-5  |      |

| $\Sigma I_{INJ(PIN)}$ | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>         | +/-25 |      |

- All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub> and V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

- This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

- 3. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

- A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 20: Voltage characteristics* for the maximum allowed input voltage values.

- A positive injection is induced by V<sub>IN</sub> > V<sub>DDA</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ</sub>(PIN) must never be exceeded. Refer also to *Table 20: Voltage characteristics* for the maximum allowed input voltage values. Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 66*.

- When several inputs are submitted to a current injection, the maximum ΣI<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values).

**Table 22. Thermal characteristics**

| Symbol           | Ratings                      |             | Symbol Ratings |  | Unit |

|------------------|------------------------------|-------------|----------------|--|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C             |  |      |

| TJ               | Maximum junction temperature | 150         | °C             |  |      |

Table 34. Typical current consumption in Run mode, code with data processing running from Flash

|                                     |                                 |                                       |                   | Ту                     | /p                      |      |

|-------------------------------------|---------------------------------|---------------------------------------|-------------------|------------------------|-------------------------|------|

| Symbol                              | Parameter                       | Conditions                            | f <sub>HCLK</sub> | Peripherals<br>enabled | Peripherals<br>disabled | Unit |

|                                     |                                 |                                       | 72 MHz            | 44.8                   | 24.9                    |      |

| I <sub>DD</sub>                     |                                 |                                       | 64 MHz            | 40.0                   | 22.4                    |      |

|                                     |                                 |                                       | 48 MHz            | 30.3                   | 17.1                    |      |

|                                     |                                 |                                       | 32 MHz            | 20.7                   | 11.9                    |      |

|                                     |                                 |                                       | 24 MHz            | 15.8                   | 9.2                     |      |

|                                     | Supply current in Run mode from |                                       | 16 MHz            | 10.9                   | 6.5                     | ]    |

| IDD                                 | V <sub>DD</sub> supply          |                                       | 8 MHz             | 5.7                    | 3.55                    | mA   |

|                                     | TOD Supply                      |                                       | 4 MHz             | 3.43                   | 3.22                    | -    |

|                                     |                                 |                                       | 2 MHz             | 2.18                   | 1.53                    |      |

|                                     |                                 |                                       | 1 MHz             | 1.56                   | 1.19                    |      |

|                                     |                                 | Running from HSE crystal clock 8 MHz, | 500 kHz           | 1.25                   | 0.96                    |      |

|                                     |                                 |                                       | 125 kHz           | 0.96                   | 0.84                    |      |

|                                     |                                 | code executing from                   | 72 MHz            | 237.1                  |                         |      |

|                                     |                                 | Flash                                 | 64 MHz            | 208.3                  |                         |      |

|                                     |                                 |                                       | 48 MHz            | 154.3                  |                         |      |

|                                     |                                 |                                       | 32 MHz            | 105.0                  |                         |      |

|                                     |                                 |                                       | 24 MHz            | 81.3                   |                         | -    |

| (1)(2)                              | Supply current in Run mode from |                                       | 16 MHz            | 57.8                   |                         |      |

| I <sub>DDA</sub> <sup>(1) (2)</sup> | V <sub>DDA</sub> supply         |                                       | 8 MHz             | 1.1                    | 15                      | μA   |

|                                     | DDA cabbi                       |                                       | 4 MHz             | 1.15                   |                         |      |

|                                     |                                 |                                       | 2 MHz             | 1.15                   |                         |      |

|                                     |                                 |                                       | 1 MHz             | 1.1                    | 15                      |      |

|                                     |                                 |                                       | 500 kHz           | 1.1                    | 15                      |      |

|                                     |                                 |                                       | 125 kHz           | 1.1                    | 15                      |      |

<sup>1.</sup> V<sub>DDA</sub> supervisor is OFF.

66/135 DocID025146 Rev 6

<sup>2.</sup> When peripherals are enabled, the power consumption of the analog part of peripherals such as ADC, DAC, Comparators, OpAmp etc. is not included. Refer to the tables of characteristics in the subsequent sections.

## On-chip peripheral current consumption

The MCU is placed under the following conditions:

- all I/O pins are in analog input configuration

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature at 25°C and V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V.

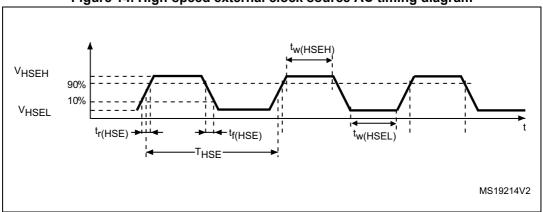

### 6.3.7 External clock source characteristics

## High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 14*.

Table 40. High-speed external user clock characteristics

| Symbol               | Parameter                                           | Conditions | Min                | Тур | Max                | Unit |

|----------------------|-----------------------------------------------------|------------|--------------------|-----|--------------------|------|

| f <sub>HSE_ext</sub> | User external clock source frequency <sup>(1)</sup> |            | 1                  | 8   | 32                 | MHz  |

| V <sub>HSEH</sub>    | OSC_IN input pin high level voltage                 |            | 0.7V <sub>DD</sub> | -   | $V_{DD}$           | V    |

| V <sub>HSEL</sub>    | OSC_IN input pin low level voltage                  | -          | $V_{SS}$           | -   | 0.3V <sub>DD</sub> | V    |

| t <sub>w(HSEH)</sub> | OSC_IN high or low time <sup>(1)</sup>              |            | 15                 | -   | -                  | ns   |

| t <sub>r(HSE)</sub>  | OSC_IN rise or fall time <sup>(1)</sup>             |            | -                  | ı   | 20                 | 10   |

<sup>1.</sup> Guaranteed by design.

Figure 14. High-speed external clock source AC timing diagram

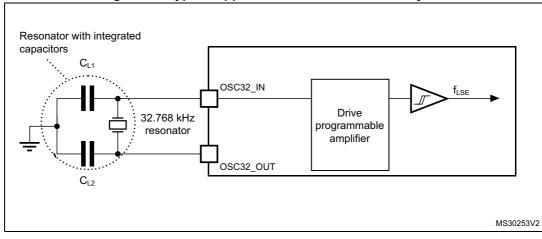

Figure 17. Typical application with a 32.768 kHz crystal

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

#### 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 49*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                                       | Conditions                                                                               | Level/<br>Class |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                  | $V_{DD}$ = 3.3 V, LQFP64, $T_{A}$ = +25°C, $f_{HCLK}$ = 72 MHz conforms to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP64, $T_A$ = +25°C, $f_{HCLK}$ = 72 MHz conforms to IEC 61000-4-4   | 4A              |

**Table 49. EMS characteristics**

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

# SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 62* for SPI or in *Table 63* for  $I^2S$  are derived from tests performed under ambient temperature,  $f_{PCLKX}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 23*.

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

Table 62. SPI characteristics<sup>(1)</sup>

| Symbol                | Parameter                | Conditions                                            | Min         | Тур   | Max    | Unit   |

|-----------------------|--------------------------|-------------------------------------------------------|-------------|-------|--------|--------|

| f <sub>SCK</sub>      | SPI clock frequency      | Master mode                                           | -           | -     | 18     | MHz    |

| 1/t <sub>c(SCK)</sub> | SPI Clock frequency      | Slave mode                                            | -           | -     | 18     | IVIIIZ |

| t <sub>su(NSS)</sub>  | NSS setup time           | Slave mode, SPI presc = 2                             | 4*Tpcl<br>k | -     | -      |        |

| t <sub>h(NSS)</sub>   | NSS hold time            | Slave mode, SPI presc = 2                             | 2*Tpcl<br>k | -     | -      |        |

| t <sub>w(SCKH)</sub>  | SCK high and low time    | Master mode, f <sub>PCLK</sub> = 36<br>MHz, presc = 4 | Tpclk-<br>2 | Tpclk | Tpclk+ |        |

| t <sub>su(MI)</sub>   |                          | Master mode                                           | 0           | -     | -      |        |

| t <sub>su(SI)</sub>   | Data input setup time    | Slave mode                                            | 1           | -     | -      |        |

| t <sub>h(MI)</sub>    | Data input hold time     | Master mode                                           | 6.5         | -     | -      |        |

| t <sub>h(SI)</sub>    | Data input hold time     | Slave mode                                            | 2.5         | -     | -      | ns     |

| t <sub>a(SO)</sub>    | Data output access time  | Slave mode                                            | 8           | -     | 40     |        |

| t <sub>dis(SO)</sub>  | Data output disable time | Slave mode                                            | 8           | -     | 14     |        |

| t <sub>v(SO)</sub>    | Data output valid time   | Slave mode                                            | -           | 12    | 27     |        |

| t <sub>v(MO)</sub>    | Data output valid tillle | Master mode                                           | -           | 1.5   | 4      |        |

| t <sub>h(SO)</sub>    | Data output hold time    | Slave mode                                            | 7.5         | -     | -      |        |

| t <sub>h(MO)</sub>    | Data output noid time    | Master mode                                           | 0           | -     | -      |        |

<sup>1.</sup> Guaranteed by characterization results.

Electrical characteristics

Table 64. ADC characteristics (continued)

| Symbol                           | Parameter                                                                                  | Conditions                                        | Min                                                                         | Тур                                       | Max                                                 | Unit               |

|----------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------|--------------------|

| C <sub>ADC</sub> <sup>(1)</sup>  | Internal sample and hold capacitor                                                         | -                                                 | -                                                                           | 5                                         | -                                                   | pF                 |

| t <sub>CAL</sub> <sup>(1)</sup>  | Calibration time                                                                           | f <sub>ADC</sub> = 72 MHz                         | 1.56                                                                        |                                           | l                                                   | μs                 |

|                                  |                                                                                            | -                                                 | 112                                                                         |                                           |                                                     | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> <sup>(1)</sup> | Trigger conversion latency<br>Regular and injected<br>channels without conversion<br>abort | CKMODE = 00                                       | 1.5                                                                         | 2                                         | 2.5                                                 | 1/f <sub>ADC</sub> |

|                                  |                                                                                            | CKMODE = 01                                       | -                                                                           | -                                         | 2                                                   | 1/f <sub>ADC</sub> |

|                                  |                                                                                            | CKMODE = 10                                       | -                                                                           | -                                         | 2.25                                                | 1/f <sub>ADC</sub> |

|                                  |                                                                                            | CKMODE = 11                                       | -                                                                           | -                                         | 2.125                                               | 1/f <sub>ADC</sub> |

|                                  | Trigger conversion latency<br>Injected channels aborting a<br>regular conversion           | CKMODE = 00                                       | 2.5                                                                         | 3                                         | 3.5                                                 | 1/f <sub>ADC</sub> |

| . (1)                            |                                                                                            | CKMODE = 01                                       | -                                                                           | -                                         | 3                                                   | 1/f <sub>ADC</sub> |

| t <sub>latrinj</sub> (1)         |                                                                                            | CKMODE = 10                                       | -                                                                           | -                                         | 3.25                                                | 1/f <sub>ADC</sub> |

|                                  |                                                                                            | CKMODE = 11                                       | -                                                                           | -                                         | 3.125                                               | 1/f <sub>ADC</sub> |

| ts <sup>(1)</sup>                | Sampling time                                                                              | f <sub>ADC</sub> = 72 MHz                         | 0.021                                                                       | -                                         | 8.35                                                | μs                 |

|                                  |                                                                                            | -                                                 | 1.5                                                                         | -                                         | 601.5                                               | 1/f <sub>ADC</sub> |

| TADCVREG_STUP <sup>(1)</sup>     | ADC Voltage Regulator<br>Start-up time                                                     | -                                                 | -                                                                           | -                                         | 10                                                  | μs                 |

| t <sub>STAB</sub> <sup>(1)</sup> | Power-up time                                                                              | -                                                 |                                                                             | conversior<br>cycle                       |                                                     |                    |

| t <sub>CONV</sub> <sup>(1)</sup> | Total conversion time (including sampling time)                                            | f <sub>ADC</sub> = 72 MHz<br>Resolution = 12 bits | 0.19                                                                        | -                                         | 8.52                                                | μs                 |

|                                  |                                                                                            | Resolution = 12 bits                              | 14 to 614 (t <sub>S</sub> for sampling + 12.5 for successive approximation) |                                           |                                                     | 1/f <sub>ADC</sub> |

| CMIR <sup>(1)</sup>              | Common mode input signal                                                                   | ADC differential mode                             | (V <sub>SSA</sub> + V <sub>REF+</sub> )/2<br>- 0.18                         | (V <sub>SSA</sub> + V <sub>REF+</sub> )/2 | (V <sub>SSA</sub> + V <sub>REF+</sub> )/2<br>+ 0.18 | V                  |

<sup>1.</sup> Data guaranteed by design.

# 6.3.19 DAC electrical specifications

Table 69. DAC characteristics

| Symbol                           | Parameter                                                                                                                              | Conditions                                                                                                                                  |                               | Min | Тур | Max                        | Unit |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----|-----|----------------------------|------|

| $V_{DDA}$                        | Analog supply voltage                                                                                                                  | DAC output buffer ON                                                                                                                        |                               | 2.4 | -   | 3.6                        | V    |

| 20/15                            | Resistive load                                                                                                                         | DAC output buffer ON                                                                                                                        | Connected to V <sub>SSA</sub> | 5   | -   | -                          | kΩ   |

|                                  | ive load                                                                                                                               | DAC datput baller ON                                                                                                                        | Connected to V <sub>DDA</sub> | 25  | -   | -                          |      |

| R <sub>O</sub> <sup>(1)</sup>    | Output impedance                                                                                                                       | DAC output buffer ON                                                                                                                        |                               | ı   | -   | 15                         | kΩ   |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                                                                        | DAC output buffer ON                                                                                                                        |                               | 1   | -   | 50                         | pF   |

| V <sub>DAC</sub> OUT             |                                                                                                                                        | Corresponds to 12-bit input code (0x0E0) to (0xF1C) at $V_{DDA}$ = 3.6 V and (0x155) and (0xEAB) at $V_{DDA}$ = 2.4 V DAC output buffer ON. |                               | 0.2 | -   | V <sub>DDA</sub> – 0.2     | ٧    |

|                                  |                                                                                                                                        | DAC output buffer OFF                                                                                                                       |                               |     | 0.5 | V <sub>DDA</sub> -<br>1LSB | mV   |

| I (3)                            |                                                                                                                                        | With no load, middle code (0x800) on the input.                                                                                             |                               | 1   | -   | 380                        | μΑ   |

|                                  | quiescent mode<br>(Standby mode) <sup>(2)</sup>                                                                                        | With no load, worst code (0xF1C) on the input.                                                                                              |                               |     | -   | 480                        | μΑ   |

|                                  | Differential non                                                                                                                       | Given for a 10-bit input code                                                                                                               |                               |     | -   | ±0.5                       | LSB  |

| DNL <sup>(3)</sup>               | linearity Difference<br>between two<br>consecutive code-<br>1LSB)                                                                      | Given for a 12-bit input code                                                                                                               |                               | -   | -   | ±2                         | LSB  |

|                                  | Integral non linearity                                                                                                                 | Given for a 10-bit input code                                                                                                               |                               |     | -   | ±1                         | LSB  |

|                                  | (difference between<br>measured value at<br>Code i and the value<br>at Code i on a line<br>drawn between Code<br>0 and last Code 4095) | Given for a 12-bit input code                                                                                                               |                               | -   | -   | ±4                         | LSB  |

|                                  | Offset error (difference                                                                                                               |                                                                                                                                             | -                             | -   | -   | ±10                        | mV   |

| Offset <sup>(3)</sup>            | VDDA/2)                                                                                                                                | Given for a 10-bit input code at V <sub>DDA</sub> = 3.6 V                                                                                   |                               |     | -   | ±3                         | LSB  |

|                                  |                                                                                                                                        | Given for a 12-bit input code at V <sub>DDA</sub> = 3.6 V                                                                                   |                               |     | -   | ±12                        | LSB  |

| Gain error <sup>(3)</sup>        | Gain error                                                                                                                             | Given for a 12-bit input code                                                                                                               |                               | -   | -   | ±0.5                       | %    |

| t <sub>SETTLING</sub> (3)        |                                                                                                                                        | C <sub>LOAD</sub> ≰50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ                                                                                       |                               |     | 3   | 4                          | μs   |

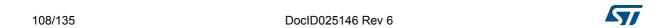

# 7.2 LQFP64 package information

Figure 39. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

1. Drawing is not to scale.

Table 77. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|--------|-------|-----------------------|--------|--------|--|

|        | Min         | Тур    | Max   | Min                   | Тур    | Max    |  |

| Α      | -           | -      | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |  |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |  |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |  |

| E      | -           | 12.000 | -     | -                     | 0.4724 | -      |  |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |  |

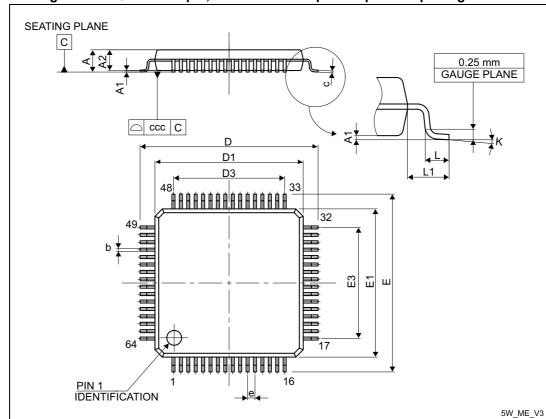

# 7.4 UFQFPN32 package information

Figure 45. UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat package outline

- 1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- There is an exposed die pad on the underside of the UFQFPN package. This pad is used for the device ground and must be connected. It is referred to as pin 0 in Table: Pin definitions.

### 7.5.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Ordering information*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F301x6 STM32F301x8 at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

#### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 82 °C (measured according to JESD51-2),  $I_{DDmax}$  = 50 mA,  $V_{DD}$  = 3.5 V, maximum 3 I/Os used at the same time in output at low level with  $I_{OL}$  = 8 mA,  $V_{OL}$ = 0.4 V and maximum 2 I/Os used at the same time in output at low level with  $I_{OL}$  = 20 mA,  $V_{OL}$ = 1.3 V

$P_{INTmax}$  = 50 mA × 3.5 V= 175 mW

$P_{IOmax} = 3 \times 8 \text{ mA} \times 0.4 \text{ V} + 2 \times 20 \text{ mA} \times 1.3 \text{ V} = 61.6 \text{ mW}$

This gives: P<sub>INTmax</sub> = 175 mW and P<sub>IOmax</sub> = 61.6 mW:

$P_{Dmax} = 175 + 61.6 = 236.6 \text{ mW}$

Thus:  $P_{Dmax} = 236.6 \text{ mW}$

Using the values obtained in *Table 80* T<sub>Jmax</sub> is calculated as follows:

For LQFP64, 45°C/W

$T_{Jmax}$  = 82 °C + (45°C/W × 236.6 mW) = 82°C + 10.65 °C = 92.65°C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105$  °C).

In this case, parts must be ordered at least with the temperature range suffix 6 (see *Section 8: Ordering information*).