Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                    |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 16K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 8x12b; D/A 1x12b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f301c6t6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of figures

| Figure 1.  | STM32F301x6/8 block diagram                                                      | 12  |

|------------|----------------------------------------------------------------------------------|-----|

| Figure 2.  | Clock tree                                                                       | 18  |

| Figure 3.  | Infrared transmitter                                                             | 30  |

| Figure 4.  | STM32F301x6/8 UFQFN32 pinout                                                     | 32  |

| Figure 5.  | STM32F301x6/8 LQFP48 pinout                                                      | 32  |

| Figure 6.  | STM32F301x6/8 LQFP64 pinout                                                      | 33  |

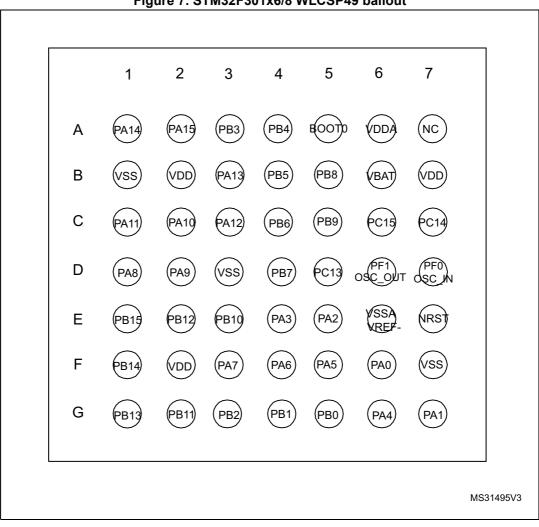

| Figure 7.  | STM32F301x6/8 WLCSP49 ballout                                                    | 34  |

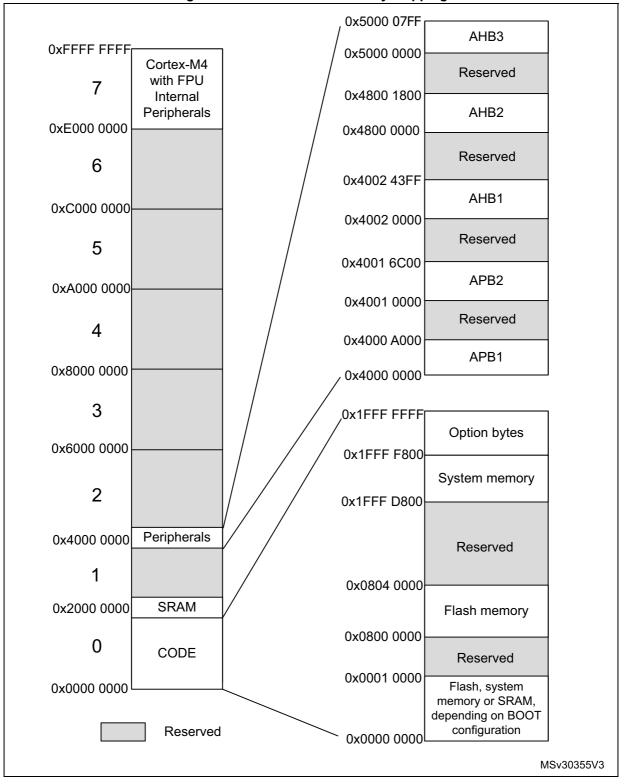

| Figure 8.  | STM32F301x6/8 memory mapping                                                     | 49  |

| Figure 9.  | Pin loading conditions                                                           |     |

| Figure 10. | Pin input voltage                                                                | 52  |

| Figure 11. | Power supply scheme.                                                             |     |

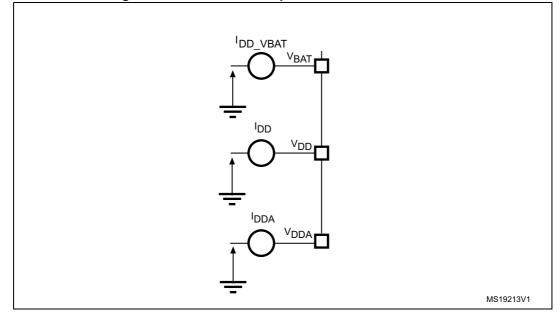

| Figure 12. | Current consumption measurement scheme                                           |     |

| Figure 13. | Typical V <sub>BAT</sub> current consumption (LSE and RTC ON/LSEDRV[1:0] = '00') |     |

| Figure 14. | High-speed external clock source AC timing diagram                               |     |

| Figure 15. | Low-speed external clock source AC timing diagram                                |     |

| Figure 16. | Typical application with an 8 MHz crystal                                        |     |

| Figure 17. | Typical application with a 32.768 kHz crystal                                    |     |

| Figure 18. | HSI oscillator accuracy characterization results for soldered parts              |     |

| Figure 19. | TC and TTa I/O input characteristics - CMOS port.                                |     |

| Figure 20. | TC and TTa I/O input characteristics - TTL port                                  |     |

| Figure 21. | Five volt tolerant (FT and FTf) I/O input characteristics - CMOS port.           |     |

| Figure 22. | Five volt tolerant (FT and FTf) I/O input characteristics - TTL port             |     |

| Figure 23. | I/O AC characteristics definition                                                |     |

| Figure 24. | Recommended NRST pin protection                                                  | 91  |

| Figure 25. | SPI timing diagram - slave mode and CPHA = 0                                     |     |

| Figure 26. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                      |     |

| Figure 27. | SPI timing diagram - master mode <sup>(1)</sup>                                  | 96  |

| Figure 28. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>          | 98  |

| Figure 29. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>         |     |

| Figure 30. | ADC typical current consumption in single-ended and differential modes           |     |

| Figure 31. | ADC accuracy characteristics                                                     |     |

| Figure 32. | Typical connection diagram using the ADC                                         |     |

| Figure 33. | 12-bit buffered /non-buffered DAC                                                |     |

| Figure 34. | Maximum V <sub>REFINT</sub> scaler startup time from power down                  | 110 |

| Figure 35. | OPAMP Voltage Noise versus Frequency                                             |     |

| Figure 36. | WLCSP49 - 49-pin, 3.417 x 3.151 mm, 0.4 mm pitch wafer level chip scale          |     |

| 0          | package outline                                                                  | 116 |

| Figure 37. | WLCSP49 - 49-pin, 3.417 x 3.151 mm, 0.4 mm pitch wafer level chip scale          |     |

| 0          | package recommended footprint                                                    | 117 |

| Figure 38. | WLCSP49 marking example (package top view)                                       |     |

| Figure 39. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline                |     |

| Figure 40. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package                        |     |

| 0          | recommended footprint.                                                           | 120 |

| Figure 41. | LQFP64 marking example (package top view).                                       |     |

| Figure 42. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline                  |     |

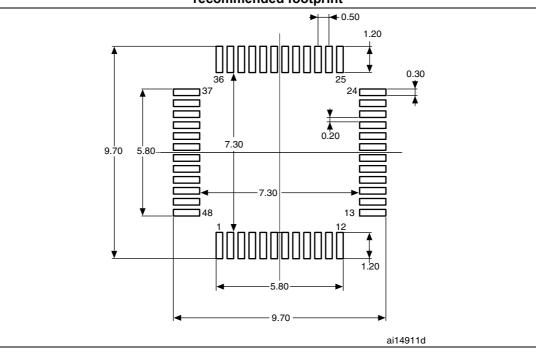

| Figure 43. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                          |     |

| <u>J</u>   | recommended footprint.                                                           | 124 |

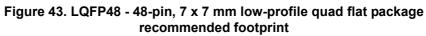

| Figure 44. | LQFP48 marking example (package top view).                                       |     |

| -          | ,                                                                                |     |

### 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F301x6/8 microcontrollers.

This datasheet should be read in conjunction with the STM32F301x6/8 and STM32F318x8 advanced ARM<sup>®</sup>-based 32-bit MCUs reference manual (RM0366). The reference manual is available from the STMicroelectronics website *www.st.com*.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core, please refer to the Cortex<sup>®</sup>-M4 Technical Reference Manual, available from ARM website www.arm.com.

### **3** Functional overview

# 3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core with FPU, embedded Flash and SRAM

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 processor with FPU is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC processor with FPU features exceptional codeefficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution. Its single-precision FPU speeds up software development by using metalanguage development tools while avoiding saturation.

With its embedded ARM core, the STM32F301x6/8 family is compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the STM32F301x6/8 family devices.

#### 3.2 Memories

#### 3.2.1 Embedded Flash memory

All STM32F301x6/8 devices feature up to 64 Kbytes of embedded Flash memory available for storing programs and data. The Flash memory access time is adjusted to the CPU clock frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states above).

#### 3.2.2 Embedded SRAM

STM32F301x6/8 devices feature 16 Kbytes of embedded SRAM.

#### 3.3 Boot modes

At startup, BOOT0 pin and BOOT1 option bit are used to select one of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART1 (PA9/PA10) and USART2 (PA2/PA3).

| Interconnect source                             | Interconnect<br>destination | Interconnect action                                            |

|-------------------------------------------------|-----------------------------|----------------------------------------------------------------|

|                                                 | TIMx                        | Timers synchronization or chaining                             |

| TIMx                                            | ADC1<br>DAC1                | Conversion triggers                                            |

|                                                 | DMA                         | Memory to memory transfer trigger                              |

|                                                 | Compx                       | Comparator output blanking                                     |

| COMPx                                           | TIMx                        | Timer input: OCREF_CLR input, input capture                    |

| ADC1                                            | TIM1                        | Timer triggered by analog watchdog                             |

| GPIO<br>RTCCLK<br>HSE/32<br>MC0                 | TIM16                       | Clock source used as input channel for HSI and LSI calibration |

| CSS<br>CPU (hard fault)<br>COMPx<br>PVD<br>GPIO | TIM1<br>TIM15, 16, 17       | Timer break                                                    |

|                                                 | TIMx                        | External trigger, timer break                                  |

| GPIO                                            | ADC1<br>DAC1                | Conversion external trigger                                    |

| DAC1                                            | COMPx                       | Comparator inverting input                                     |

*Note:* For more details about the interconnect actions, please refer to the corresponding sections in the STM32F301x6/8 and STM32F318x8 reference manual RM0366.

### 3.17 Inter-integrated circuit interfaces (I<sup>2</sup>C)

The devices feature three  $I^2C$  bus interfaces which can operate in multimaster and slave mode. Each I2C interface can support standard (up to 100 kHz), fast (up to 400 kHz) and fast mode + (up to 1 MHz) modes.

All I<sup>2</sup>C interfaces support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask). They also include programmable analog and digital noise filters.

|                                          | Analog filter                                         | Digital filter                                                                                       |  |  |

|------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|

| Pulse width of suppressed spikes ≥ 50 ns |                                                       | Programmable length from 1 to 15<br>I2C peripheral clocks                                            |  |  |

| Benefits                                 | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |  |  |

| Drawbacks                                | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.             |  |  |

In addition, it provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. It also has a clock domain independent from the CPU clock, allowing the I2Cx (x=1,3) to wake up the MCU from Stop mode on address match.

The I2C interfaces can be served by the DMA controller.

Refer to Table 7 for the features available in I2C1, I2C2 and I2C3.

#### Table 7. STM32F301x6/8 I<sup>2</sup>C implementation

| I2C features <sup>(1)</sup>                                 | I2C1 | I2C2 | I2C3 |

|-------------------------------------------------------------|------|------|------|

| 7-bit addressing mode                                       | Х    | Х    | Х    |

| 10-bit addressing mode                                      | Х    | Х    | Х    |

| Standard mode (up to 100 kbit/s)                            | Х    | Х    | Х    |

| Fast mode (up to 400 kbit/s)                                | Х    | Х    | Х    |

| Fast Mode Plus with 20mA output drive I/Os (up to 1 Mbit/s) | Х    | Х    | Х    |

| Independent clock                                           | Х    | Х    | Х    |

| SMBus                                                       | Х    | Х    | Х    |

| Wakeup from STOP                                            | Х    | Х    | Х    |

1. X = supported.

Figure 7. STM32F301x6/8 WLCSP49 ballout

1. The above figure shows the package top view.

2. NC: Not connected.

### 5 Memory mapping

Figure 8. STM32F301x6/8 memory mapping

DocID025146 Rev 6

### 6.1.7 Current consumption measurement

#### Figure 12. Current consumption measurement scheme

### 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 20: Voltage characteristics*, *Table 21: Current characteristics*, and *Table 22: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                                                                            | Min                  | Мах                   | Unit |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>  | External main supply voltage (including $V_{DDA,}$ $V_{BAT}$ and $V_{DD})$                                         | -0.3                 | 4.0                   | V    |

| V <sub>DD</sub> –V <sub>DDA</sub> | Allowed voltage difference for $V_{DD} > V_{DDA}$                                                                  | -                    | 0.4                   | V    |

|                                   | Input voltage on FT and FTf pins                                                                                   | V <sub>SS</sub> –0.3 | V <sub>DD</sub> + 4.0 |      |

|                                   | Input voltage on TTa and TT pins                                                                                   | V <sub>SS</sub> –0.3 | 4.0                   |      |

| V <sub>IN</sub> <sup>(2)</sup>    | Input voltage on any other pin                                                                                     | V <sub>SS</sub> -0.3 | 4.0                   | V    |

|                                   | Input voltage on Boot0 pin                                                                                         | 0                    | 9                     |      |

| $ \Delta V_{DDx} $                | Variations between different V <sub>DD</sub> power pins                                                            | -                    | 50                    | mV   |

| V <sub>SSX</sub> –V <sub>SS</sub> | Variations between all the different ground pins <sup>(3)</sup>                                                    | -                    | 50 mV                 |      |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body<br>model)see Section 6.3.12: Electrical<br>sensitivity characteristics |                      | V                     |      |

| Table 20 | . Voltage | characteristics <sup>(1)</sup> |

|----------|-----------|--------------------------------|

|----------|-----------|--------------------------------|

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range. The following relationship must be respected between V<sub>DDA</sub> and V<sub>DD</sub>: V<sub>DDA</sub> must power on before or at the same time as V<sub>DD</sub> in the power up sequence. V<sub>DDA</sub> must be greater than or equal to V<sub>DD</sub>.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 21: Current characteristics* for the maximum allowed injected current values.

3. Include V<sub>REF-</sub> pin.

#### 6.3.4 Embedded reference voltage

The parameters given in *Table 27* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 23*.

| Symbol                 | Parameter                                                           | Conditions                        | Min  | Тур  | Max               | Unit       |

|------------------------|---------------------------------------------------------------------|-----------------------------------|------|------|-------------------|------------|

| V <sub>REFINT</sub>    | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +105 °C | 1.20 | 1.23 | 1.25              | V          |

| T <sub>S_vrefint</sub> | ADC sampling time when<br>reading the internal<br>reference voltage | -                                 | 2.2  | -    | -                 | μs         |

| V <sub>RERINT</sub>    | Internal reference voltage<br>spread over the<br>temperature range  | V <sub>DD</sub> = 3 V ±10 mV      | -    | -    | 10 <sup>(1)</sup> | mV         |

| T <sub>Coeff</sub>     | Temperature coefficient                                             | -                                 | -    | -    | 100<br>(1)        | ppm/°<br>C |

1. Guaranteed by design.

| Calibration value name  | Description                                                              | Memory address            |  |  |

|-------------------------|--------------------------------------------------------------------------|---------------------------|--|--|

| V <sub>REFINT_CAL</sub> | Raw data acquired at<br>temperature of 30 °C<br>V <sub>DDA</sub> = 3.3 V | 0x1FFF F7BA - 0x1FFF F7BB |  |  |

#### 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 12: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

Note: The total current consumption is the sum of I<sub>DD</sub> and I<sub>DDA</sub>.

|                                                                             |                         |            |                   | All      | periphe             | erals en | abled               | All      | periphe             | erals dis | abled               |      |

|-----------------------------------------------------------------------------|-------------------------|------------|-------------------|----------|---------------------|----------|---------------------|----------|---------------------|-----------|---------------------|------|

| Symbol                                                                      | Parameter               | Conditions | f <sub>HCLK</sub> | <b>T</b> | м                   | ax @ T   | A <sup>(1)</sup>    | <b>T</b> | м                   | lax @ T   | 4 <sup>(1)</sup>    | Unit |

| Symbol                                                                      |                         |            |                   | Тур      | 25 °C               | 85 °C    | 105 °C              | Тур      | 25 °C               | 85 °C     | 105 °C              |      |

|                                                                             |                         |            | 72 MHz            | 45.8     | 49.1 <sup>(2)</sup> | 50.1     | 51.4 <sup>(2)</sup> | 25.1     | 27.3 <sup>(2)</sup> | 28.0      | 28.6 <sup>(2)</sup> |      |

|                                                                             |                         |            | 64 MHz            | 40.8     | 43.6                | 44.9     | 46.9                | 22.3     | 24.1                | 25.0      | 25.5                |      |

|                                                                             |                         | External   | 48 MHz            | 30.2     | 32.9                | 33.5     | 34.8                | 17.0     | 18.7                | 19.1      | 19.6                |      |

|                                                                             |                         | clock (HSE | 32 MHz            | 20.5     | 23.1                | 24.1     | 25.4                | 11.1     | 12.2                | 13.2      | 13.3                |      |

|                                                                             | Supply                  | bypass)    | 24 MHz            | 15.4     | 17.1                | 18.3     | 19.5                | 8.5      | 9.7                 | 10.1      | 10.2                |      |

|                                                                             | current in              |            | 8 MHz             | 5.0      | 5.9                 | 6.3      | 6.9                 | 3.1      | 3.7                 | 4.1       | 4.7                 |      |

| I <sub>DD</sub> Run mode,<br>executing<br>from RAM                          |                         | 1 MHz      | 0.8               | 1.1      | 1.9                 | 2.6      | 0.5                 | 0.8      | 1.2                 | 1.4       |                     |      |

|                                                                             | Internal<br>clock (HSI) | 64 MHz     | 37.3              | 41.1     | 41.8                | 43.3     | 22.0                | 23.8     | 24.4                | 24.9      |                     |      |

|                                                                             |                         | 48 MHz     | 28.0              | 31.1     | 31.6                | 33.2     | 16.4                | 18.0     | 18.3                | 18.6      |                     |      |

|                                                                             |                         | 32 MHz     | 18.8              | 21.3     | 22.1                | 23.1     | 10.9                | 11.9     | 12.8                | 13.1      | mA                  |      |

|                                                                             |                         | 24 MHz     | 14.2              | 15.9     | 16.8                | 17.9     | 5.5                 | 6.4      | 6.7                 | 7.3       |                     |      |

|                                                                             |                         |            | 8 MHz             | 4.8      | 5.1                 | 6.0      | 6.5                 | 2.9      | 3.5                 | 4.1       | 4.2                 |      |

|                                                                             |                         |            | 72 MHz            | 30.0     | 32.8 <sup>(2)</sup> | 33.1     | 34.1 <sup>(2)</sup> | 5.9      | 6.8 <sup>(2)</sup>  | 6.9       | 7.4 <sup>(2)</sup>  |      |

|                                                                             |                         |            | 64 MHz            | 26.7     | 29.2                | 29.6     | 30.5                | 5.3      | 5.9                 | 6.2       | 6.7                 |      |

|                                                                             | cloc                    | External   | 48 MHz            | 16.7     | 18.5                | 19.0     | 19.7                | 3.6      | 4.5                 | 4.5       | 5.3                 |      |

|                                                                             |                         | clock (HSE | 32 MHz            | 13.3     | 14.9                | 15.3     | 15.4                | 2.9      | 3.7                 | 3.8       | 4.3                 |      |

| Supply<br>current in<br>Sleep<br>mode,<br>executing<br>from Flash<br>or RAM | bypass)                 | 24 MHz     | 10.2              | 11.4     | 12.0                | 12.3     | 2.2                 | 2.7      | 2.9                 | 3.2       | 1                   |      |

|                                                                             |                         | 8 MHz      | 3.6               | 4.4      | 4.8                 | 5.3      | 0.9                 | 1.2      | 1.5                 | 2.1       |                     |      |

|                                                                             |                         | 1 MHz      | 0.5               | 0.8      | 1.1                 | 1.3      | 0.1                 | 0.4      | 0.8                 | 0.8       |                     |      |

|                                                                             |                         | 64 MHz     | 23.2              | 25.3     | 25.6                | 26.2     | 5.0                 | 5.7      | 6.1                 | 6.2       |                     |      |

|                                                                             |                         | 48 MHz     | 17.5              | 19.2     | 19.4                | 19.9     | 3.9                 | 4.7      | 4.8                 | 5.3       | 1                   |      |

|                                                                             | Internal<br>clock (HSI) | 32 MHz     | 11.7              | 12.9     | 13.2                | 13.3     | 2.6                 | 3.4      | 3.6                 | 4.2       | mA                  |      |

|                                                                             |                         | ( - ·)     | 24 MHz            | 8.9      | 10.2                | 10.6     | 10.8                | 1.4      | 2.1                 | 2.4       | 2.7                 | ]    |

|                                                                             |                         |            | 8 MHz             | 3.4      | 4.0                 | 4.6      | 5.1                 | 0.7      | 1.1                 | 1.4       | 1.9                 |      |

#### Table 29. Typical and maximum current consumption from VDD supply at VDD = 3.6V (continued)

1. Guaranteed by characterization results.

2. Data based on characterization results and tested in production with code executing from RAM.

#### Low-speed internal (LSI) RC oscillator

| Table 45. LSI oscillator characteristic | s <sup>(1)</sup> |

|-----------------------------------------|------------------|

|-----------------------------------------|------------------|

| Symbol                              | Parameter                        | Min | Тур  | Max | Unit |

|-------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                    | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup> | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μA   |

1.  $V_{DDA}$  = 3.3 V, T<sub>A</sub> = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

#### 6.3.9 PLL characteristics

The parameters given in *Table 46* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 23*.

| Symbol               | Parameter                      |                   | Unit |                    |      |  |

|----------------------|--------------------------------|-------------------|------|--------------------|------|--|

|                      | Falameter                      | Min               | Тур  | Мах                | Unit |  |

| f                    | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | -    | 24 <sup>(2)</sup>  | MHz  |  |

| f <sub>PLL_IN</sub>  | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -    | 60 <sup>(2)</sup>  | %    |  |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16 <sup>(2)</sup> | -    | 72                 | MHz  |  |

| t <sub>LOCK</sub>    | PLL lock time                  | -                 | -    | 200 <sup>(2)</sup> | μs   |  |

| Jitter               | Cycle-to-cycle jitter          | -                 | -    | 300 <sup>(2)</sup> | ps   |  |

#### Table 46. PLL characteristics

Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by f<sub>PLL\_OUT</sub>.

2. Guaranteed by design.

80/135

#### 6.3.14 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 54* are derived from tests performed under the conditions summarized in *Table 23*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                          | Conditions                                                                                         | Min                                         | Тур     | Мах                                       | Unit |

|------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------|---------|-------------------------------------------|------|

|                  |                                                    | TTa and TT I/O                                                                                     | -                                           | -       | 0.3 V <sub>DD</sub> + 0.07 <sup>(1)</sup> |      |

|                  |                                                    | FT and FTf I/O                                                                                     | -                                           | -       | $0.475  V_{DD}$ -0.2 $^{(1)}$             |      |

| VIL              | Low level input                                    | BOOT0 I/O                                                                                          | -                                           | -       | $0.3 V_{DD} - 0.3$ <sup>(1)</sup>         | v    |

| ۹L               | voltage                                            | All I/Os except BOOT0                                                                              | -                                           | -       | 0.3 V <sub>DD</sub> <sup>(2)</sup>        |      |

|                  |                                                    | TTa and TT I/O                                                                                     | 0.445 V <sub>DD</sub> +0.398 <sup>(1)</sup> | -       | -                                         |      |

|                  |                                                    | FT and FTf I/O                                                                                     | 0.5 V <sub>DD</sub> +0.2 <sup>(1)</sup>     | -       | -                                         |      |

| VIH              | High level input                                   | BOOT0                                                                                              | 0.2 V <sub>DD</sub> +0.95 <sup>(1)</sup>    | -       | -                                         | v    |

| ¥ІН              | voltage                                            | All I/Os except BOOT0                                                                              | 0.7 V <sub>DD</sub> <sup>(2)</sup>          | -       | -                                         | Ň    |

|                  |                                                    | TC and TTa I/O                                                                                     | -                                           | 200 (1) | -                                         |      |

| V <sub>hys</sub> | Schmitt trigger<br>hysteresis                      | FT and FTf I/O                                                                                     | -                                           | 100 (1) | -                                         | mV   |

|                  | hysteresis                                         | BOOT0                                                                                              | -                                           | 300 (1) | -                                         |      |

|                  |                                                    | TC, FT and FTf I/O<br>TTa I/O in digital mode<br>V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub> | -                                           | -       | ±0.1                                      |      |

|                  | Input leakage<br>current <sup>(3)</sup>            | TTa I/O in digital mode<br>V <sub>DD</sub> ≤V <sub>IN</sub> ≤V <sub>DDA</sub>                      | -                                           | -       | 1                                         |      |

| l <sub>lkg</sub> |                                                    | TTa I/O in analog mode<br>V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DDA</sub>                       | -                                           | -       | ±0.2                                      | μA   |

|                  |                                                    | FT and FTf I/O <sup>(4)</sup><br>V <sub>DD</sub> ≤V <sub>IN</sub> ≤5 V                             | -                                           | -       | 10                                        |      |

| R <sub>PU</sub>  | Weak pull-up<br>equivalent resistor <sup>(5)</sup> | $V_{IN} = V_{SS}$                                                                                  | 25                                          | 40      | 55                                        | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup>  | $V_{IN} = V_{DD}$                                                                                  | 25                                          | 40      | 55                                        | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                | -                                                                                                  | -                                           | 5       | -                                         | pF   |

| Table 54. | I/O | static | characteristics |

|-----------|-----|--------|-----------------|

|-----------|-----|--------|-----------------|

1. Data based on design simulation

2. Tested in production.

3. Leakage could be higher than the maximum value. if negative current is injected on adjacent pins. Refer to Table 53: I/O current injection susceptibility.

- 4. To sustain a voltage higher than  $V_{DD}$  +0.3 V, the internal pull-up/pull-down resistors must be disabled.

- 5. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimum (~10% order).

#### 6.3.17 Communications interfaces

#### I<sup>2</sup>C interface characteristics

The I2C interface meets the timings requirements of the I<sup>2</sup>C-bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I2C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to Reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and VDDIOx is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.14: I/O port characteristics for the I2C I/Os characteristics.

All I2C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

| Symbol          | Parameter                                                              | Min               | Мах                | Unit |

|-----------------|------------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

#### Table 61. I2C analog filter characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered

| Symbol                 | Parameter              | Conditions                             | Min | Мах | Unit |

|------------------------|------------------------|----------------------------------------|-----|-----|------|

| t <sub>v(WS)</sub>     | WS valid time          | Master mode                            | -   | 20  |      |

| t <sub>h(WS)</sub>     | WS hold time           | Master mode                            | 2   | -   |      |

| t <sub>su(WS)</sub>    | WS setup time          | Slave mode                             | 0   | -   |      |

| t <sub>h(WS)</sub>     | WS hold time           | Slave mode                             | 4   | -   |      |

| t <sub>su(SD_MR)</sub> | Data input actus tima  | Master receiver                        | 1   | -   |      |

| t <sub>su(SD_SR)</sub> | Data input setup time  | Slave receiver                         | 1   | -   |      |

| t <sub>h(SD_MR)</sub>  | Deta input hold time   | Master receiver                        | 8   | -   | ns   |

| t <sub>h(SD_SR)</sub>  | Data input hold time   | Slave receiver                         | 2.5 | -   |      |

| t <sub>v(SD_ST)</sub>  |                        | Slave transmitter (after enable edge)  | -   | 50  |      |

| t <sub>v(SD_MT)</sub>  | Data output valid time | Master transmitter (after enable edge) | -   | 22  |      |

| t <sub>h(SD_ST)</sub>  |                        | Slave transmitter (after enable edge)  | 8   | -   |      |

| t <sub>h(SD_MT)</sub>  | Data output hold time  | Master transmitter (after enable edge) | 1   | -   |      |

Table 63. I2S characteristics<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

2. 256xFs maximum is 36 MHz (APB1 Maximum frequency)

Note: Refer to RM0366 Reference Manual I2S Section for more details about the sampling frequency (Fs), fMCK, fCK, DCK values reflect only the digital peripheral behavior, source clock precision might slightly change the values DCK depends mainly on ODD bit value. Digital contribution leads to a min of (I2SDIV/(2\*I2SDIV+ODD) and a max (I2SDIV+ODD)/(2\*I2SDIV+ODD) and Fs max supported for each mode/condition.

### 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

| Cumb al           |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |

|-------------------|-------|-------------|-------|-----------------------|--------|--------|--|

| Symbol            | Min   | Тур         | Max   | Min                   | Тур    | Max    |  |

| А                 | 0.525 | 0.555       | 0.585 | 0.0207                | 0.0219 | 0.0230 |  |

| A1                | -     | 0.175       | -     | -                     | 0.0069 | -      |  |

| A2                | -     | 0.380       | -     | -                     | 0.0150 | -      |  |

| A3 <sup>(2)</sup> | -     | 0.025       | -     | -                     | 0.0010 | -      |  |

| b <sup>(3)</sup>  | 0.220 | 0.250       | 0.280 | 0.0087                | 0.0098 | 0.0110 |  |

| D                 | 3.382 | 3.417       | 3.452 | 0.1331                | 0.1345 | 0.1359 |  |

| E                 | 3.116 | 3.151       | 3.186 | 0.1227                | 0.1241 | 0.1254 |  |

| е                 | -     | 0.400       | -     | -                     | 0.0157 | -      |  |

| e1                | -     | 2.400       | -     | -                     | 0.0945 | -      |  |

| e2                | -     | 2.400       | -     | -                     | 0.0945 | -      |  |

| F                 | -     | 0.5085      | -     | -                     | 0.0200 | -      |  |

| G                 | -     | 0.3755      | -     | -                     | 0.0148 | -      |  |

| ааа               | -     | -           | 0.100 | -                     | -      | 0.0039 |  |

| bbb               | -     | -           | 0.100 | -                     | -      | 0.0039 |  |

| CCC               | -     | -           | 0.100 | -                     | -      | 0.0039 |  |

| ddd               | -     | -           | 0.050 | -                     | -      | 0.0020 |  |

| eee               | -     | -           | 0.050 | -                     | -      | 0.0020 |  |

# Table 75. WLCSP49 - 49-pin, 3.417 x 3.151 mm, 0.4 mm pitch wafer level chip scalepackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

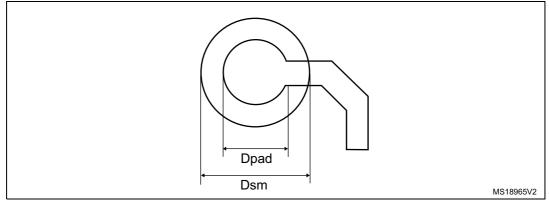

# Figure 37. WLCSP49 - 49-pin, 3.417 x 3.151 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

1. Dimensions are expressed in millimeters.

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

#### 7.5.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Ordering information*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F301x6 STM32F301x8 at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

#### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 82$  °C (measured according to JESD51-2),  $I_{DDmax} = 50$  mA,  $V_{DD} = 3.5$  V, maximum 3 I/Os used at the same time in output at low level with  $I_{OL} = 8$  mA,  $V_{OL} = 0.4$  V and maximum 2 I/Os used at the same time in output at low level with  $I_{OL} = 20$  mA,  $V_{OL} = 1.3$  V

P<sub>INTmax</sub> = 50 mA × 3.5 V= 175 mW

P<sub>IOmax</sub> = 3 × 8 mA × 0.4 V + 2 × 20 mA × 1.3 V = 61.6 mW

This gives:  $P_{INTmax}$  = 175 mW and  $P_{IOmax}$  = 61.6 mW:

$P_{Dmax} = 175 + 61.6 = 236.6 \text{ mW}$

Thus:  $P_{Dmax} = 236.6 \text{ mW}$

Using the values obtained in *Table 80* T<sub>Jmax</sub> is calculated as follows:

– For LQFP64, 45°C/W

T<sub>Jmax</sub> = 82 °C + (45°C/W × 236.6 mW) = 82°C + 10.65 °C = 92.65°C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 6 (see *Section 8: Ordering information*).