Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                    |

| Number of I/O              | 24                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 16K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 11x12b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-UFQFN Exposed Pad                                                    |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f301k6u6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Introc | luction            |                                                                                | 9    |

|---|--------|--------------------|--------------------------------------------------------------------------------|------|

| 2 | Desci  | ription .          |                                                                                | . 10 |

| 3 | Funct  | tional ov          | verview                                                                        | . 13 |

|   | 3.1    | ARM <sup>®</sup> ( | Cortex <sup>®</sup> -M4 core with FPU, embedded Flash and SRAM $\ldots \ldots$ | . 13 |

|   | 3.2    | Memori             | es                                                                             | . 13 |

|   |        | 3.2.1              | Embedded Flash memory                                                          | 13   |

|   |        | 3.2.2              | Embedded SRAM                                                                  | 13   |

|   | 3.3    | Boot mo            | odes                                                                           | . 13 |

|   | 3.4    | Cyclic re          | edundancy check calculation unit (CRC)                                         | . 14 |

|   | 3.5    | Power r            | nanagement                                                                     | . 14 |

|   |        | 3.5.1              | Power supply schemes                                                           | 14   |

|   |        | 3.5.2              | Power supply supervisor                                                        | 14   |

|   |        | 3.5.3              | Voltage regulator                                                              | 15   |

|   |        | 3.5.4              | Low-power modes                                                                | 15   |

|   | 3.6    | Intercon           | nect matrix                                                                    | . 15 |

|   | 3.7    | Clocks a           | and startup                                                                    | . 17 |

|   | 3.8    | General            | -purpose inputs/outputs (GPIOs)                                                | . 19 |

|   | 3.9    | Direct m           | nemory access (DMA)                                                            | . 19 |

|   | 3.10   | Interrup           | ts and events                                                                  | . 19 |

|   |        | 3.10.1             | Nested vectored interrupt controller (NVIC)                                    | 19   |

|   | 3.11   | Fast and           | alog-to-digital converter (ADC)                                                | . 20 |

|   |        | 3.11.1             | Temperature sensor                                                             | 20   |

|   |        | 3.11.2             | Internal voltage reference (V <sub>REFINT</sub> )                              | 20   |

|   |        | 3.11.3             | V <sub>BAT</sub> battery voltage monitoring                                    | 21   |

|   | 3.12   | Digital-te         | o-analog converter (DAC)                                                       | . 21 |

|   | 3.13   | Operatio           | onal amplifier (OPAMP)                                                         | . 21 |

|   | 3.14   | Ultra-fas          | st comparators (COMP)                                                          | . 22 |

|   | 3.15   | Timers a           | and watchdogs                                                                  | . 22 |

|   |        | 3.15.1             | Advanced timer (TIM1)                                                          |      |

|   |        | 3.15.2             | General-purpose timers (TIM2, TIM15, TIM16, TIM17)                             |      |

|   |        | 3.15.3             | Basic timer (TIM6)                                                             | 24   |

|   |        |                    |                                                                                |      |

mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

Refer to *Table 9* for the features available in SPI2 and SPI3.

| SPI features <sup>(1)</sup> | SPI2 | SPI3 |

|-----------------------------|------|------|

| Hardware CRC calculation    | Х    | Х    |

| Rx/Tx FIFO                  | Х    | Х    |

| NSS pulse mode              | Х    | Х    |

| I2S mode                    | Х    | Х    |

| TI mode                     | Х    | Х    |

| Table 9. STM3 | 2F301x6/8 | SPI/I2S | implementation |

|---------------|-----------|---------|----------------|

|---------------|-----------|---------|----------------|

1. X = supported.

# 3.20 Touch sensing controller (TSC)

The STM32F301x6/8 devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 18 capacitive sensing channels distributed over 6 analog I/O groups.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (for example glass, plastic). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. To limit the CPU bandwidth usage this acquisition is directly managed by the hardware touch sensing controller and only requires few external components to operate.

# 3.22 Development support

# 3.22.1 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

| ω       |

|---------|

| õ       |

| 1       |

| <u></u> |

| ŭĩ      |

DocID025146 Rev 6

# Pinouts and pin description

STM32F301x6 STM32F301x8

DocID025146 Rev 6

41/135

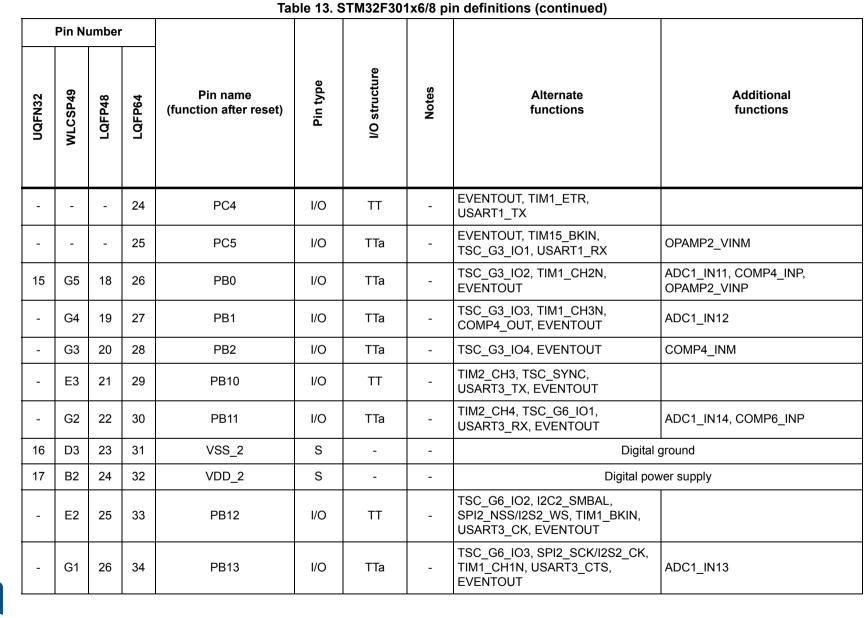

|        | Table 13. STM32F301x6/8 pin definitions (continued) |        |        |                                    |          |                                                |       |                                                                                              |                         |  |

|--------|-----------------------------------------------------|--------|--------|------------------------------------|----------|------------------------------------------------|-------|----------------------------------------------------------------------------------------------|-------------------------|--|

|        | Pin N                                               | umber  |        |                                    |          |                                                |       |                                                                                              |                         |  |

| UQFN32 | WLCSP49                                             | LQFP48 | LQFP64 | Pin name<br>(function after reset) | Pin type | I/O structure                                  | Notes | Alternate<br>functions                                                                       | Additional<br>functions |  |

| -      | -                                                   | -      | 51     | PC10                               | I/O      | FT                                             | -     | EVENTOUT, SPI3_SCK/I2S3_CK,<br>USART3_TX                                                     | -                       |  |

| -      | -                                                   | -      | 52     | PC11                               | I/O      | FT                                             | -     | EVENTOUT,<br>SPI3_MISO/I2S3ext_SD,<br>USART3_RX                                              | -                       |  |

| -      | -                                                   | -      | 53     | PC12                               | I/O      | FT - EVENTOUT, SPI3_MOSI/I2S3_SD,<br>USART3_CK |       |                                                                                              | -                       |  |

| -      | -                                                   | -      | 54     | PD2                                | I/O      | FT                                             | -     | EVENTOUT                                                                                     | -                       |  |

| 26     | A3                                                  | 39     | 55     | PB3                                | I/O      | FT                                             | -     | JTDO-TRACESWO, TIM2_CH2,<br>TSC_G5_IO1, SPI3_SCK/I2S3_CK,<br>USART2_TX, EVENTOUT             | -                       |  |

| 27     | A4                                                  | 40     | 56     | PB4                                | I/O      | FT                                             | -     | JTRST, TIM16_CH1, TSC_G5_IO2,<br>SPI3_MISO/I2S3ext_SD,<br>USART2_RX, TIM17_BKIN,<br>EVENTOUT | -                       |  |

| 28     | B4                                                  | 41     | 57     | PB5                                | I/O      | FT                                             | -     | TIM16_BKIN, I2C1_SMBAI,<br>SPI3_MOSI/I2S3_SD, USART2_CK,<br>I2C3_SDA, TIM17_CH1, EVENTOUT    | -                       |  |

| 29     | C4                                                  | 42     | 58     | PB6                                | I/O      | FTf                                            | -     | TIM16_CH1N, TSC_G5_IO3,<br>I2C1_SCL, USART1_TX,<br>EVENTOUT                                  | -                       |  |

| 30     | D4                                                  | 43     | 59     | PB7                                | I/O      | FTf                                            | -     | TIM17_CH1N, TSC_G5_IO4,<br>I2C1_SDA, USART1_RX,<br>EVENTOUT                                  | -                       |  |

STM32F301x6 STM32F301x8

Pinouts and pin description

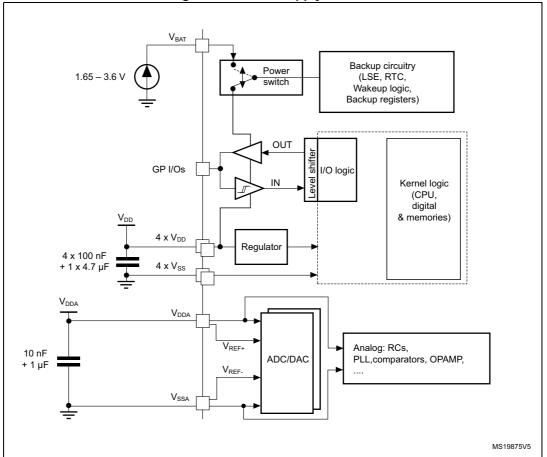

# 6.1.6 Power supply scheme

Figure 11. Power supply scheme

**Caution:** Each power supply pair (for example V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub>) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

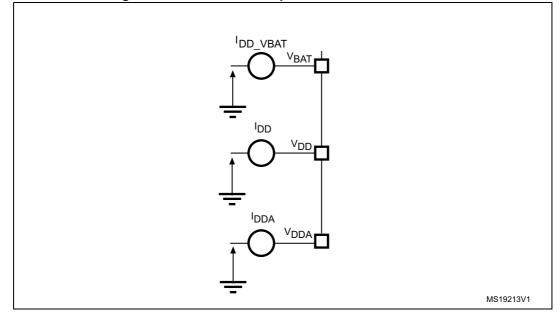

# 6.1.7 Current consumption measurement

#### Figure 12. Current consumption measurement scheme

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 54: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption (see *Table 37: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

${\rm I}_{\rm SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

V<sub>DD</sub> is the MCU supply voltage

$f_{SW}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$ + $C_S$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

# 6.3.6 Wakeup time from low-power mode

The wakeup times given in *Table 38* are measured starting from the wakeup event trigger up to the first instruction executed by the CPU:

- For Stop or Sleep mode: the wakeup event is WFE.

- WKUP1 (PA0) pin is used to wakeup from Standby, Stop and Sleep modes.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 23*.

| Symbol                        | Parameter                         | Conditions            | Typ @Vdd, V <sub>DD</sub> = V <sub>DDA</sub> |       |       |      |       |       | Мах                    | Unit |

|-------------------------------|-----------------------------------|-----------------------|----------------------------------------------|-------|-------|------|-------|-------|------------------------|------|

|                               | Farameter                         | Conditions            | 2.0 V                                        | 2.4 V | 2.7 V | 3 V  | 3.3 V | 3.6 V | wax                    | Unit |

|                               | Wakoup from                       | Regulator in run mode | 4.5                                          | 4.2   | 4.1   | 4.0  | 3.8   | 3.8   | 4.5                    |      |

| twustop Wakeup from Stop mode | Regulator in<br>low-power<br>mode | 8.2                   | 7.0                                          | 6.4   | 6.0   | 5.7  | 5.5   | 9.0   | μs                     |      |

| twustandby <sup>(1)</sup>     | Wakeup from<br>Standby mode       | LSI and<br>IWDG OFF   | 72.8                                         | 63.4  | 59.2  | 56.1 | 53.1  | 51.3  | 103                    |      |

| t <sub>WUSLEEP</sub>          | Wakeup from<br>Sleep mode         | -                     |                                              | 6     |       |      |       | -     | CPU<br>clock<br>cycles |      |

Table 38. Low-power mode wakeup timings

1. Guaranteed by characterization results.

| Symbol               | Parameter                                                                     | Conditions                                         | Тур | Мах    | Unit |

|----------------------|-------------------------------------------------------------------------------|----------------------------------------------------|-----|--------|------|

|                      | Wakeup time needed to calculate the maximum USART baud rate                   | Stop mode with main<br>regulator in low-power mode | -   | 13.125 |      |

| <sup>t</sup> wuusart | allowing to wakeup up from Stop<br>mode when the USART clock<br>source is HSI | Stop mode with main regulator in run mode          | -   | 3.125  | μs   |

1. Guaranteed by design.

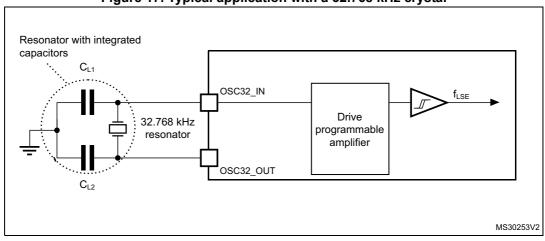

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 43*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                   | Parameter                                     | Conditions <sup>(1)</sup>                        | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |  |

|--------------------------|-----------------------------------------------|--------------------------------------------------|--------------------|-----|--------------------|------|--|

| I <sub>DD</sub> LSE curr |                                               | LSEDRV[1:0]=00<br>lower driving capability       | -                  | 0.5 | 0.9                |      |  |

|                          | LSE current consumption                       | LSEDRV[1:0]=10<br>medium low driving capability  | -                  | -   | 1                  |      |  |

| 'DD                      |                                               | LSEDRV[1:0]=01<br>medium high driving capability | -                  | -   | 1.3                | μA   |  |

|                          |                                               | LSEDRV[1:0]=11<br>higher driving capability      | -                  | -   | 1.6                |      |  |

|                          |                                               | LSEDRV[1:0]=00<br>lower driving capability       | 5                  | -   | -                  |      |  |

| a                        | Gscillator<br>g <sub>m</sub> transconductance | LSEDRV[1:0]=10<br>medium low driving capability  | 8                  | -   | -                  | μA/V |  |

| Уm                       |                                               | LSEDRV[1:0]=01<br>medium high driving capability | 15                 | -   | -                  | μΑνν |  |

|                          |                                               | LSEDRV[1:0]=11<br>higher driving capability      | 25                 | -   | -                  |      |  |

| $t_{SU(LSE)}^{(3)}$      | Startup time                                  | V <sub>DD</sub> is stabilized                    | -                  | 2   | -                  | S    |  |

#### Table 43. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz)

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design.

3. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 17. Typical application with a 32.768 kHz crystal

*Note:* An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

# 6.3.8 Internal clock source characteristics

The parameters given in *Table 44* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 23*.

# High-speed internal (HSI) RC oscillator

| Symbol                | Parameter                                | Conditions                       | Min                 | Тур | Мах                | Unit |  |  |  |

|-----------------------|------------------------------------------|----------------------------------|---------------------|-----|--------------------|------|--|--|--|

| f <sub>HSI</sub>      | Frequency                                | -                                | -                   | 8   | -                  | MHz  |  |  |  |

| TRIM                  | HSI user trimming step                   | -                                | -                   | -   | 1 <sup>(2)</sup>   | %    |  |  |  |

| DuCy <sub>(HSI)</sub> | Duty cycle                               | -                                | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |  |  |  |

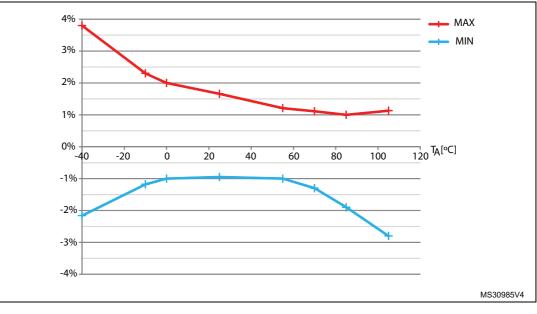

|                       | $105^{\circ}C$<br>T <sub>A</sub> = -10 t | T <sub>A</sub> = -40 to<br>105°C | -2.8 <sup>(3)</sup> | -   | 3.8 <sup>(3)</sup> |      |  |  |  |

|                       |                                          | T <sub>A</sub> = -10 to 85°C     | -1.9 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> |      |  |  |  |

| ACC <sub>HSI</sub>    |                                          | T <sub>A</sub> = 0 to 85°C       | -1.9 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   | %    |  |  |  |

|                       |                                          | $T_A = 0$ to $70^{\circ}C$       | -1.3 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |  |  |  |

|                       |                                          | T <sub>A</sub> = 0 to 55°C       | -1 <sup>(3)</sup>   | -   | 2 <sup>(3)</sup>   |      |  |  |  |

|                       |                                          | $T_A = 25^{\circ}C^{(4)}$        | -1                  | -   | 1                  |      |  |  |  |

| t <sub>su(HSI)</sub>  | HSI oscillator startup time              | -                                | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |  |  |  |

| I <sub>DDA(HSI)</sub> | HSI oscillator power<br>consumption      | -                                | -                   | 80  | 100 <sup>(2)</sup> | μA   |  |  |  |

| Table 44. | HSI | oscillator | characteristics <sup>(1)</sup> |

|-----------|-----|------------|--------------------------------|

|-----------|-----|------------|--------------------------------|

1.  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

4. Factory calibrated, parts not soldered.

#### Figure 18. HSI oscillator accuracy characterization results for soldered parts

# 6.3.10 Memory characteristics

# Flash memory

The characteristics are given at  $T_{\text{A}}$  = –40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

| Symbol                         | Parameter               | Conditions                      | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------------------|-------------------------|---------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>              | 16-bit programming time | T <sub>A</sub> = -40 to +105 °C | 40  | 53.5 | 60                 | μs   |

| t <sub>ERASE</sub>             | Page (2 KB) erase time  | $T_A = -40$ to +105 °C          | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>                | Mass erase time         | $T_A = -40$ to +105 °C          | 20  | -    | 40                 | ms   |

|                                | Supply current          | Write mode                      | -   | -    | 10                 | mA   |

| I <sub>DD</sub> Supply current | Erase mode              | -                               | -   | 12   | mA                 |      |

# Table 47. Flash memory characteristics

1. Guaranteed by design.

| 0h.e.l           | Demonster        |                                                                                         | Value              | 11      |

|------------------|------------------|-----------------------------------------------------------------------------------------|--------------------|---------|

| Symbol           | Symbol Parameter | Conditions                                                                              | Min <sup>(1)</sup> | Unit    |

| N <sub>END</sub> | Endurance        | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | kcycles |

|                  |                  | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 |         |

| t <sub>RET</sub> | Data retention   | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | Years   |

|                  |                  | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 |         |

# Table 48. Flash memory endurance and data retention

1. Guaranteed by characterization results.

2. Cycling performed over the whole temperature range.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Symbol | Parameter             | Conditions                            | Class     |

|--------|-----------------------|---------------------------------------|-----------|

| LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78A | 2 level A |

# 6.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu A/+0 \mu A$  range), or other functional failure (for example reset occurrence or oscillator frequency deviation).

The test results are given in Table 53

|                  |                                                                                                                                                                                                                | Functional s       |                    |      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                                                                                                                                    | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0                                                                                                                                                                                      | -0                 | NA                 |      |

|                  | Injected current on PC0 pin (TTa pin)                                                                                                                                                                          | -0                 | +5                 |      |

| I <sub>INJ</sub> | Injected current PC0, PC1, PC2, PC3, PA0, PA1, PA2, PA3, PA4, PA6, PA7, PC4, PB0, PB10, PB11, PB13 with induced leakage current on other pins from this group less than -100 $\mu$ A or more than +100 $\mu$ A | -5                 | +5                 | mA   |

|                  | Injected current on any other TT, FT and FTf pins                                                                                                                                                              | -5                 | NA                 |      |

|                  | Injected current on all other TC, TTa and RESET pins                                                                                                                                                           | -5                 | +5                 |      |

#### Table 53. I/O current injection susceptibility

*Note:* It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

DocID025146 Rev 6

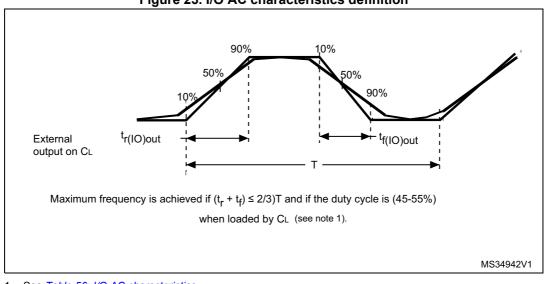

Figure 23. I/O AC characteristics definition

1. See Table 56: I/O AC characteristics.

# 6.3.15 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 54*).

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 23*.

| Symbol                               | Parameter                                       | Conditions        | Min                                            | Тур | Max                                         | Unit |

|--------------------------------------|-------------------------------------------------|-------------------|------------------------------------------------|-----|---------------------------------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST Input low level voltage                    | -                 | -                                              | -   | 0.3V <sub>DD</sub> +<br>0.07 <sup>(1)</sup> | v    |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST Input high level voltage                   | -                 | 0.445V <sub>DD</sub> +<br>0.398 <sup>(1)</sup> | -   | -                                           |      |

| V <sub>hys(NRST)</sub>               | NRST Schmitt trigger voltage hysteresis         | -                 | -                                              | 200 | -                                           | mV   |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 25                                             | 40  | 55                                          | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>  | NRST Input filtered pulse                       | -                 | -                                              | -   | 100 <sup>(1)</sup>                          | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup> | NRST Input not filtered pulse                   | -                 | 500 <sup>(1)</sup>                             | -   | -                                           | ns   |

Table 57. NRST pin characteristics

1. Guaranteed by design.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

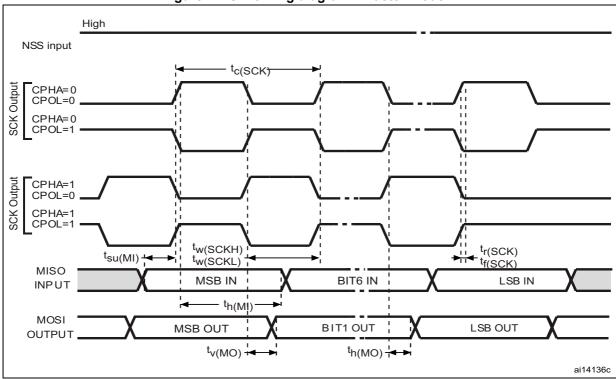

# SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 62* for SPI or in *Table 63* for I<sup>2</sup>S are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 23*.

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                       | Parameter                | Conditions                                            | Min         | Тур   | Max         | Unit |

|----------------------------------------------|--------------------------|-------------------------------------------------------|-------------|-------|-------------|------|

| f <sub>SCK</sub>                             | SPI clock frequency      | Master mode                                           | -           | -     | 18          | MHz  |

| 1/t <sub>c(SCK)</sub>                        | SFT Clock frequency      | Slave mode                                            | -           | -     | 18          |      |

| t <sub>su(NSS)</sub>                         | NSS setup time           | Slave mode, SPI presc = 2                             | 4*Tpcl<br>k | -     | -           |      |

| t <sub>h(NSS)</sub>                          | NSS hold time            | Slave mode, SPI presc = 2                             | 2*Tpcl<br>k | -     | -           |      |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time    | Master mode, f <sub>PCLK</sub> = 36<br>MHz, presc = 4 | Tpclk-<br>2 | Tpclk | Tpclk+<br>2 |      |

| t <sub>su(MI)</sub>                          | Data input setup time    | Master mode                                           | 0           | -     | -           |      |

| t <sub>su(SI)</sub>                          |                          | Slave mode                                            | 1           | -     | -           |      |

| t <sub>h(MI)</sub>                           | Data input hold time     | Master mode                                           | 6.5         | -     | -           |      |

| t <sub>h(SI)</sub>                           |                          | Slave mode                                            | 2.5         | -     | -           | ns   |

| t <sub>a(SO)</sub>                           | Data output access time  | Slave mode                                            | 8           | -     | 40          |      |

| t <sub>dis(SO)</sub>                         | Data output disable time | Slave mode                                            | 8           | -     | 14          |      |

| t <sub>v(SO)</sub>                           | Data output valid time   | Slave mode                                            | -           | 12    | 27          |      |

| t <sub>v(MO)</sub>                           |                          | Master mode                                           | -           | 1.5   | 4           |      |

| t <sub>h(SO)</sub>                           | Data output hold time    | Slave mode                                            | 7.5         | -     | -           | ]    |

| t <sub>h(MO)</sub>                           |                          | Master mode                                           | 0           | -     | -           | ]    |

1. Guaranteed by characterization results.

Figure 27. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at  $0.5V_{DD}$  and with external C<sub>L</sub> = 30 pF.

Table 63. I2S characteristics<sup>(1)</sup>

| Symbol           | Parameter                      | Conditions           | Min      | Max                   | Unit |

|------------------|--------------------------------|----------------------|----------|-----------------------|------|

| f <sub>MCK</sub> | I2S Main clock output          | -                    | 256 x 8K | 256xFs <sup>(2)</sup> | MHz  |

| f                | 125 dook froguopov             | Master data: 32 bits | -        | 64xFs                 | MHz  |

| f <sub>CK</sub>  | CK I2S clock frequency         | Slave data: 32 bits  | -        | 64xFs                 |      |

| D <sub>CK</sub>  | I2S clock frequency duty cycle | Slave receiver       | 30       | 70                    | %    |

| Dimension      | Recommended values                             |

|----------------|------------------------------------------------|

| Pitch          | 0.4                                            |

| Dood           | 260 µm max. (circular)                         |

| Dpad           | 220 µm recommended                             |

| Dsm            | 300 μm min. (for 260 μm diameter pad)          |

| PCB pad design | Non-solder mask defined via underbump allowed. |

Table 76. WLCSP49 recommended PCB design rules (0.4 mm pitch)

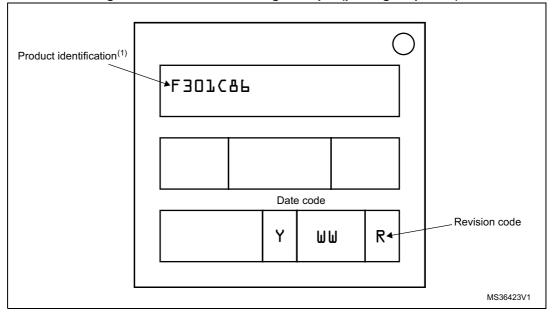

# **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 38. WLCSP49 marking example (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

1. Dimensions are expressed in millimeters.

| Table 82. Document revision history (continued) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                                            | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 04-Jun-2015                                     | 5        | <ul> <li>Updated:</li> <li>AF9 value for PA1, PA3 and PA9 in <i>Table 14: Alternate functions for Port A</i>,</li> <li>the structure of <i>Section 7: Package information</i>.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 22-Jul-2016                                     | 6        | <ul> <li>Updated notes on:</li> <li>All document tables by removing the "not tested in production" specification.</li> <li>Table 13: STM32F301x6/8 pin definitions.</li> <li>Table 20: Voltage characteristics.</li> <li>Table 70: Comparator characteristics.</li> <li>Figure 4: STM32F301x6/8 UFQFN32 pinout.</li> <li>Figure 5: STM32F301x6/8 UFQFP48 pinout.</li> <li>Figure 6: STM32F301x6/8 UCSP49 ballout.</li> <li>Figure 7: STM32F301x6/8 WLCSP49 ballout.</li> <li>Figure 42: Recommended NRST pin protection.</li> <li>Figure 45: UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat package outline.</li> <li>Updated tables:</li> <li>Updated V<sub>REFINT</sub> line on Table 27: Embedded internal reference voltage.</li> <li>Updated "Conditions" column on Table 43: LSE oscillator characteristics (fLSE = 32.768 kHz).</li> <li>Added CMIR and t<sub>STAB</sub> lines on Table 64: ADC characteristics.</li> <li>Updated R<sub>LOAD</sub> line on Table 69: DAC characteristics.</li> <li>Updated figures:</li> <li>Figure 7: STM32F301x6/8 WLCSP49 ballout.</li> <li>Figure 2: Clock tree.</li> <li>Figure 2: Clock tree.</li> <li>Figure 7: STM32F301x6/8 WLCSP49 ballout.</li> <li>Figure 2: Recommended NRST pin protection.</li> <li>Added:</li> <li>Table 39: Wakeup time using USART</li> <li>Updated name of Section 8: Ordering information</li> </ul> |  |  |

Table 82. Document revision history (continued)