Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 16MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-TQFP                                                                 |

| Supplier Device Package    | 44-TQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega16-16aj |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

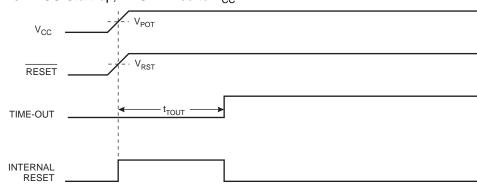

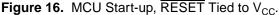

#### **Power-on Reset**

A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The detection level is defined in Table 15. The POR is activated whenever  $V_{CC}$  is below the detection level. The POR circuit can be used to trigger the Start-up Reset, as well as to detect a failure in supply voltage.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching the Power-on Reset threshold voltage invokes the delay counter, which determines how long the device is kept in RESET after  $V_{CC}$  rise. The RESET signal is activated again, without any delay, when  $V_{CC}$  decreases below the detection level.

#### Figure 17. MCU Start-up, RESET Extended Externally

#### **Unconnected pins**

If some pins are unused, it is recommended to ensure that these pins have a defined level. Even though most of the digital inputs are disabled in the deep sleep modes as described above, floating inputs should be avoided to reduce current consumption in all other modes where the digital inputs are enabled (Reset, Active mode and Idle mode).

The simplest method to ensure a defined level of an unused pin, is to enable the internal pull-up. In this case, the pull-up will be disabled during reset. If low power consumption during reset is important, it is recommended to use an external pull-up or pull-down. Connecting unused pins directly to  $V_{CC}$  or GND is not recommended, since this may cause excessive currents if the pin is accidentally configured as an output.

#### Alternate Port Functions

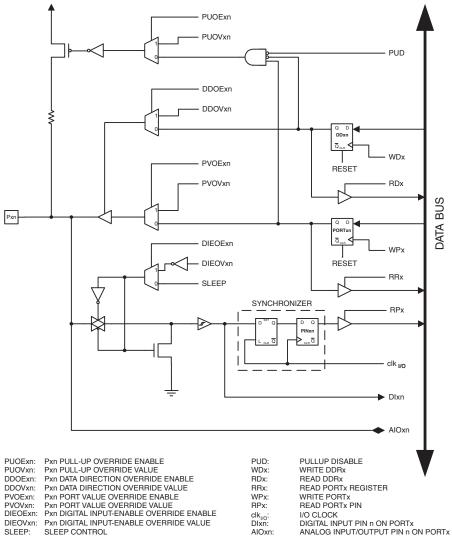

Most port pins have alternate functions in addition to being General Digital I/Os. Figure 26 shows how the port pin control signals from the simplified Figure 23 can be overridden by alternate functions. The overriding signals may not be present in all port pins, but the figure serves as a generic description applicable to all port pins in the AVR microcontroller family.

Figure 26. Alternate Port Functions<sup>(1)</sup>

Note: 1. WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clk<sub>I/O</sub>, SLEEP, and PUD are common to all ports. All other signals are unique for each pin.

| Signal Name | PD3/INT1    | PD2/INT0    | PD1/TXD | PD0/RXD      |

|-------------|-------------|-------------|---------|--------------|

| PUOE        | 0           | 0           | TXEN    | RXEN         |

| PUOV        | 0           | 0           | 0       | PORTD0 • PUD |

| DDOE        | 0           | 0           | TXEN    | RXEN         |

| DDOV        | 0           | 0           | 1       | 0            |

| PVOE        | 0           | 0           | TXEN    | 0            |

| PVOV        | 0           | 0           | TXD     | 0            |

| DIEOE       | INT1 ENABLE | INT0 ENABLE | 0       | 0            |

| DIEOV       | 1           | 1           | 0       | 0            |

| DI          | INT1 INPUT  | INT0 INPUT  | _       | RXD          |

| AIO         | -           | _           | _       | -            |

Table 33. Overriding Signals for Alternate Functions in PD3..PD0

and/or falling edge of the INT1 pin or level sensed. Activity on the pin will cause an interrupt request even if INT1 is configured as an output. The corresponding interrupt of External Interrupt Request 1 is executed from the INT1 interrupt Vector.

#### Bit 6 – INT0: External Interrupt Request 0 Enable

When the INT0 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is enabled. The Interrupt Sense Control0 bits 1/0 (ISC01 and ISC00) in the MCU General Control Register (MCUCR) define whether the External Interrupt is activated on rising and/or falling edge of the INT0 pin or level sensed. Activity on the pin will cause an interrupt request even if INT0 is configured as an output. The corresponding interrupt of External Interrupt Request 0 is executed from the INT0 interrupt vector.

#### Bit 5 – INT2: External Interrupt Request 2 Enable

When the INT2 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is enabled. The Interrupt Sense Control2 bit (ISC2) in the MCU Control and Status Register (MCUCSR) defines whether the External Interrupt is activated on rising or falling edge of the INT2 pin. Activity on the pin will cause an interrupt request even if INT2 is configured as an output. The corresponding interrupt of External Interrupt Request 2 is executed from the INT2 Interrupt Vector.

#### General Interrupt Flag Register – GIFR

| Bit           | 7     | 6     | 5     | 4 | 3 | 2 | 1 | 0 |      |

|---------------|-------|-------|-------|---|---|---|---|---|------|

|               | INTF1 | INTF0 | INTF2 | - | - | - | - | - | GIFR |

| Read/Write    | R/W   | R/W   | R/W   | R | R | R | R | R | •    |

| Initial Value | 0     | 0     | 0     | 0 | 0 | 0 | 0 | 0 |      |

#### • Bit 7 – INTF1: External Interrupt Flag 1

When an edge or logic change on the INT1 pin triggers an interrupt request, INTF1 becomes set (one). If the I-bit in SREG and the INT1 bit in GICR are set (one), the MCU will jump to the corresponding Interrupt Vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical one to it. This flag is always cleared when INT1 is configured as a level interrupt.

#### Bit 6 – INTF0: External Interrupt Flag 0

When an edge or logic change on the INT0 pin triggers an interrupt request, INTF0 becomes set (one). If the I-bit in SREG and the INT0 bit in GICR are set (one), the MCU will jump to the corresponding interrupt vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical one to it. This flag is always cleared when INT0 is configured as a level interrupt.

#### • Bit 5 – INTF2: External Interrupt Flag 2

When an event on the INT2 pin triggers an interrupt request, INTF2 becomes set (one). If the lbit in SREG and the INT2 bit in GICR are set (one), the MCU will jump to the corresponding Interrupt Vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical one to it. Note that when entering some sleep modes with the INT2 interrupt disabled, the input buffer on this pin will be disabled. This may cause a logic change in internal signals which will set the INTF2 Flag. See "Digital Input Enable and Sleep Modes" on page 54 for more information.

For more information on how to access the 16-bit registers refer to "Accessing 16-bit Registers" on page 92.

Input Capture PinThe main trigger source for the Input Capture unit is the Input Capture pin (ICP1).SourceTimer/Counter1 can alternatively use the Analog Comparator output as trigger source for the<br/>Input Capture unit. The Analog Comparator is selected as trigger source by setting the Analog<br/>Comparator Input Capture (ACIC) bit in the Analog Comparator Control and Status Register<br/>(ACSR). Be aware that changing trigger source can trigger a capture. The Input Capture Flag<br/>must therefore be cleared after the change.

Both the *Input Capture pin* (ICP1) and the *Analog Comparator output* (ACO) inputs are sampled using the same technique as for the T1 pin (Figure 38 on page 87). The edge detector is also identical. However, when the noise canceler is enabled, additional logic is inserted before the edge detector, which increases the delay by four system clock cycles. Note that the input of the noise canceler and edge detector is always enabled unless the Timer/Counter is set in a waveform generation mode that uses ICR1 to define TOP.

An Input Capture can be triggered by software by controlling the port of the ICP1 pin.

**Noise Canceler** The noise canceler improves noise immunity by using a simple digital filtering scheme. The noise canceler input is monitored over four samples, and all four must be equal for changing the output that in turn is used by the edge detector.

The noise canceler is enabled by setting the *Input Capture Noise Canceler* (ICNC1) bit in *Timer/Counter Control Register B* (TCCR1B). When enabled the noise canceler introduces additional four system clock cycles of delay from a change applied to the input, to the update of the ICR1 Register. The noise canceler uses the system clock and is therefore not affected by the prescaler.

Using the Input<br/>Capture UnitThe main challenge when using the Input Capture unit is to assign enough processor capacity<br/>for handling the incoming events. The time between two events is critical. If the processor has<br/>not read the captured value in the ICR1 Register before the next event occurs, the ICR1 will be<br/>overwritten with a new value. In this case the result of the capture will be incorrect.

When using the Input Capture Interrupt, the ICR1 Register should be read as early in the interrupt handler routine as possible. Even though the Input Capture Interrupt has relatively high priority, the maximum interrupt response time is dependent on the maximum number of clock cycles it takes to handle any of the other interrupt requests.

Using the Input Capture unit in any mode of operation when the TOP value (resolution) is actively changed during operation, is not recommended.

Measurement of an external signal's duty cycle requires that the trigger edge is changed after each capture. Changing the edge sensing must be done as early as possible after the ICR1 Register has been read. After a change of the edge, the Input Capture Flag (ICF1) must be cleared by software (writing a logical one to the I/O bit location). For measuring frequency only, the clearing of the ICF1 Flag is not required (if an interrupt handler is used).

# SS Pin Functionality

| Slave Mode                     | When the SPI is configured as a Slave, the Slave Select ( $\overline{SS}$ ) pin is always input. When $\overline{SS}$ is held low, the SPI is activated, and MISO becomes an output if configured so by the user. All other pins are inputs. When $\overline{SS}$ is driven high, all pins are inputs except MISO which can be user configured as an output, and the SPI is passive, which means that it will not receive incoming data. Note that the SPI logic will be reset once the $\overline{SS}$ pin is driven high.<br>The $\overline{SS}$ pin is useful for packet/byte synchronization to keep the Slave Bit Counter synchronous with the Master Clock generator. When the $\overline{SS}$ pin is driven high, the SPI Slave will immediately |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Master Mode                    | reset the send and receive logic, and drop any partially received data in the Shift Register.<br>When the SPI is configured as a Master (MSTR in SPCR is set), the user can determine the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                | direction of the SS pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                | If <del>SS</del> is configured as an output, the pin is a general output pin which does not affect the SPI system. Typically, the pin will be driving the <del>SS</del> pin of the SPI Slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                | If $\overline{SS}$ is configured as an input, it must be held high to ensure Master SPI operation. If the $\overline{SS}$ pin is driven low by peripheral circuitry when the SPI is configured as a Master with the $\overline{SS}$ pin defined as an input, the SPI system interprets this as another Master selecting the SPI as a Slave and starting to send data to it. To avoid bus contention, the SPI system takes the following actions:                                                                                                                                                                                                                                                                                                        |

|                                | <ol> <li>The MSTR bit in SPCR is cleared and the SPI system becomes a Slave. As a result of<br/>the SPI becoming a Slave, the MOSI and SCK pins become inputs.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                | <ol><li>The SPIF Flag in SPSR is set, and if the SPI interrupt is enabled, and the I-bit in SREG is<br/>set, the interrupt routine will be executed.</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                | Thus, when interrupt-driven SPI transmission is used in Master mode, and there exists a possi-<br>bility that SS is driven low, the interrupt should always check that the MSTR bit is still set. If the<br>MSTR bit has been cleared by a Slave Select, it must be set by the user to re-enable SPI Master<br>mode.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SPI Control Register –<br>SPCR |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# SPCR

| Bit           | 7    | 6   | 5    | 4    | 3    | 2    | 1    | 0    | _    |

|---------------|------|-----|------|------|------|------|------|------|------|

|               | SPIE | SPE | DORD | MSTR | CPOL | CPHA | SPR1 | SPR0 | SPCR |

| Read/Write    | R/W  | R/W | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | -    |

| Initial Value | 0    | 0   | 0    | 0    | 0    | 0    | 0    | 0    |      |

#### • Bit 7 – SPIE: SPI Interrupt Enable

This bit causes the SPI interrupt to be executed if SPIF bit in the SPSR Register is set and the if the global interrupt enable bit in SREG is set.

#### • Bit 6 – SPE: SPI Enable

When the SPE bit is written to one, the SPI is enabled. This bit must be set to enable any SPI operations.

#### Bit 5 – DORD: Data Order

When the DORD bit is written to one, the LSB of the data word is transmitted first.

When the DORD bit is written to zero, the MSB of the data word is transmitted first.

The following code example shows how to read the UCSRC Register contents.

| Assembly Code Example <sup>(1)</sup>             |

|--------------------------------------------------|

| USART_ReadUCSRC:                                 |

| ; Read UCSRC                                     |

| in r16,UBRRH                                     |

| in r16,UCSRC                                     |

| ret                                              |

| C Code Example <sup>(1)</sup>                    |

| <pre>unsigned char USART_ReadUCSRC( void )</pre> |

| {                                                |

| unsigned char ucsrc;                             |

| /* Read UCSRC */                                 |

| ucsrc = UBRRH;                                   |

| ucsrc = UCSRC;                                   |

| return ucsrc;                                    |

| }                                                |

Note: 1. See "About Code Examples" on page 7.

The assembly code example returns the UCSRC value in r16.

Reading the UBRRH contents is not an atomic operation and therefore it can be read as an ordinary register, as long as the previous instruction did not access the register location.

# USART Register Description

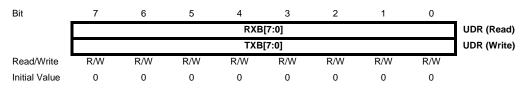

USART I/O Data Register – UDR

The USART Transmit Data Buffer Register and USART Receive Data Buffer Registers share the same I/O address referred to as USART Data Register or UDR. The Transmit Data Buffer Register (TXB) will be the destination for data written to the UDR Register location. Reading the UDR Register location will return the contents of the Receive Data Buffer Register (RXB).

For 5-bit, 6-bit, or 7-bit characters the upper unused bits will be ignored by the Transmitter and set to zero by the Receiver.

The transmit buffer can only be written when the UDRE Flag in the UCSRA Register is set. Data written to UDR when the UDRE Flag is not set, will be ignored by the USART Transmitter. When data is written to the transmit buffer, and the Transmitter is enabled, the Transmitter will load the data into the transmit Shift Register when the Shift Register is empty. Then the data will be serially transmitted on the TxD pin.

The receive buffer consists of a two level FIFO. The FIFO will change its state whenever the receive buffer is accessed. Due to this behavior of the receive buffer, do not use read modify write instructions (SBI and CBI) on this location. Be careful when using bit test instructions (SBIC and SBIS), since these also will change the state of the FIFO.

#### USART Control and Status Register A – UCSRA

| Bit           | 7   | 6   | 5    | 4  | 3   | 2  | 1   | 0    | _     |

|---------------|-----|-----|------|----|-----|----|-----|------|-------|

|               | RXC | TXC | UDRE | FE | DOR | PE | U2X | MPCM | UCSRA |

| Read/Write    | R   | R/W | R    | R  | R   | R  | R/W | R/W  |       |

| Initial Value | 0   | 0   | 1    | 0  | 0   | 0  | 0   | 0    |       |

### • Bit 7 – RXC: USART Receive Complete

This flag bit is set when there are unread data in the receive buffer and cleared when the receive buffer is empty (that is, does not contain any unread data). If the receiver is disabled, the receive buffer will be flushed and consequently the RXC bit will become zero. The RXC Flag can be used to generate a Receive Complete interrupt (see description of the RXCIE bit).

# Bit 6 – TXC: USART Transmit Complete

This flag bit is set when the entire frame in the transmit Shift Register has been shifted out and there are no new data currently present in the transmit buffer (UDR). The TXC Flag bit is automatically cleared when a transmit complete interrupt is executed, or it can be cleared by writing a one to its bit location. The TXC Flag can generate a Transmit Complete interrupt (see description of the TXCIE bit).

### Bit 5 – UDRE: USART Data Register Empty

The UDRE Flag indicates if the transmit buffer (UDR) is ready to receive new data. If UDRE is one, the buffer is empty, and therefore ready to be written. The UDRE Flag can generate a Data Register empty Interrupt (see description of the UDRIE bit).

UDRE is set after a reset to indicate that the transmitter is ready.

### • Bit 4 – FE: Frame Error

This bit is set if the next character in the receive buffer had a Frame Error when received. that is, when the first stop bit of the next character in the receive buffer is zero. This bit is valid until the receive buffer (UDR) is read. The FE bit is zero when the stop bit of received data is one. Always set this bit to zero when writing to UCSRA.

# Bit 3 – DOR: Data OverRun

This bit is set if a Data OverRun condition is detected. A Data OverRun occurs when the receive buffer is full (two characters), it is a new character waiting in the receive Shift Register, and a new start bit is detected. This bit is valid until the receive buffer (UDR) is read. Always set this bit to zero when writing to UCSRA.

# • Bit 2 – PE: Parity Error

This bit is set if the next character in the receive buffer had a Parity Error when received and the parity checking was enabled at that point (UPM1 = 1). This bit is valid until the receive buffer (UDR) is read. Always set this bit to zero when writing to UCSRA.

# Bit 1 – U2X: Double the USART Transmission Speed

This bit only has effect for the asynchronous operation. Write this bit to zero when using synchronous operation.

Writing this bit to one will reduce the divisor of the baud rate divider from 16 to 8 effectively doubling the transfer rate for asynchronous communication.

### TWI Register Description

#### **TWI Bit Rate Register**

– TWBR

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _    |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

|               | TWBR7 | TWBR6 | TWBR5 | TWBR4 | TWBR3 | TWBR2 | TWBR1 | TWBR0 | TWBR |

| Read/Write    | R/W   |      |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |      |

#### • Bits 7..0 - TWI Bit Rate Register

TWBR selects the division factor for the bit rate generator. The bit rate generator is a frequency divider which generates the SCL clock frequency in the Master modes. See "Bit Rate Generator Unit" on page 178 for calculating bit rates.

#### TWI Control Register – TWCR

| Bit           | 7     | 6    | 5     | 4     | 3    | 2    | 1 | 0    | _    |

|---------------|-------|------|-------|-------|------|------|---|------|------|

|               | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE | TWCR |

| Read/Write    | R/W   | R/W  | R/W   | R/W   | R    | R/W  | R | R/W  | •    |

| Initial Value | 0     | 0    | 0     | 0     | 0    | 0    | 0 | 0    |      |

The TWCR is used to control the operation of the TWI. It is used to enable the TWI, to initiate a Master access by applying a START condition to the bus, to generate a receiver acknowledge, to generate a stop condition, and to control halting of the bus while the data to be written to the bus are written to the TWDR. It also indicates a write collision if data is attempted written to TWDR while the register is inaccessible.

#### • Bit 7 – TWINT: TWI Interrupt Flag

This bit is set by hardware when the TWI has finished its current job and expects application software response. If the I-bit in SREG and TWIE in TWCR are set, the MCU will jump to the TWI Interrupt Vector. While the TWINT Flag is set, the SCL low period is stretched. The TWINT Flag must be cleared by software by writing a logic one to it. Note that this flag is not automatically cleared by hardware when executing the interrupt routine. Also note that clearing this flag starts the operation of the TWI, so all accesses to the TWI Address Register (TWAR), TWI Status Register (TWSR), and TWI Data Register (TWDR) must be complete before clearing this flag.

#### • Bit 6 – TWEA: TWI Enable Acknowledge Bit

The TWEA bit controls the generation of the acknowledge pulse. If the TWEA bit is written to one, the ACK pulse is generated on the TWI bus if the following conditions are met:

- 1. The device's own Slave address has been received.

- 2. A general call has been received, while the TWGCE bit in the TWAR is set.

- 3. A data byte has been received in Master Receiver or Slave Receiver mode.

By writing the TWEA bit to zero, the device can be virtually disconnected from the Two-wire Serial Bus temporarily. Address recognition can then be resumed by writing the TWEA bit to one again.

#### Bit 5 – TWSTA: TWI START Condition Bit

The application writes the TWSTA bit to one when it desires to become a Master on the Twowire Serial Bus. The TWI hardware checks if the bus is available, and generates a START condition on the bus if it is free. However, if the bus is not free, the TWI waits until a STOP condition

#### Bits 1..0 – TWPS: TWI Prescaler Bits

These bits can be read and written, and control the bit rate prescaler.

| Table 73. TWI Bit Rate Prescaler | Table 73. |

|----------------------------------|-----------|

|----------------------------------|-----------|

| TWPS1 | TWPS0 | Prescaler Value |

|-------|-------|-----------------|

| 0     | 0     | 1               |

| 0     | 1     | 4               |

| 1     | 0     | 16              |

| 1     | 1     | 64              |

To calculate bit rates, see "Bit Rate Generator Unit" on page 178. The value of TWPS1..0 is used in the equation.

#### TWI Data Register – TWDR

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

|---------------|------|------|------|------|------|------|------|------|------|

|               | TWD7 | TWD6 | TWD5 | TWD4 | TWD3 | TWD2 | TWD1 | TWD0 | TWDR |

| Read/Write    | R/W  | •    |

| Initial Value | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |      |

In Transmit mode, TWDR contains the next byte to be transmitted. In Receive mode, the TWDR contains the last byte received. It is writable while the TWI is not in the process of shifting a byte. This occurs when the TWI Interrupt Flag (TWINT) is set by hardware. Note that the Data Register cannot be initialized by the user before the first interrupt occurs. The data in TWDR remains stable as long as TWINT is set. While data is shifted out, data on the bus is simultaneously shifted in. TWDR always contains the last byte present on the bus, except after a wake up from a sleep mode by the TWI interrupt. In this case, the contents of TWDR is undefined. In the case of a lost bus arbitration, no data is lost in the transition from Master to Slave. Handling of the ACK bit is controlled automatically by the TWI logic, the CPU cannot access the ACK bit directly.

#### Bits 7..0 – TWD: TWI Data Register

These eight bits contain the next data byte to be transmitted, or the latest data byte received on the Two-wire Serial Bus.

#### TWI (Slave) Address Register – TWAR

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0     |      |

|---------------|------|------|------|------|------|------|------|-------|------|

|               | TWA6 | TWA5 | TWA4 | TWA3 | TWA2 | TWA1 | TWA0 | TWGCE | TWAR |

| Read/Write    | R/W   | I    |

| Initial Value | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0     |      |

The TWAR should be loaded with the 7-bit Slave address (in the seven most significant bits of TWAR) to which the TWI will respond when programmed as a Slave Transmitter or receiver. In multi-master systems, TWAR must be set in Masters which can be addressed as Slaves by other Masters.

The LSB of TWAR is used to enable recognition of the general call address (\$00). There is an associated address comparator that looks for the Slave address (or general call address if enabled) in the received serial address. If a match is found, an interrupt request is generated.

#### Bits 7..1 – TWA: TWI (Slave) Address Register

These seven bits constitute the Slave address of the TWI unit.

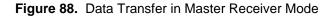

A START condition is sent by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 1     | Х    | 1     | 0     | Х    | 1    | 0 | Х    |

TWEN must be written to one to enable the Two-wire Serial Interface, TWSTA must be written to one to transmit a START condition and TWINT must be set to clear the TWINT Flag. The TWI will then test the Two-wire Serial Bus and generate a START condition as soon as the bus becomes free. After a START condition has been transmitted, the TWINT Flag is set by hardware, and the status code in TWSR will be \$08 (See Table 74). In order to enter MR mode, SLA+R must be transmitted. This is done by writing SLA+R to TWDR. Thereafter the TWINT bit should be cleared (by writing it to one) to continue the transfer. This is accomplished by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 1     | Х    | 0     | 0     | Х    | 1    | 0 | Х    |

When SLA+R have been transmitted and an acknowledgement bit has been received, TWINT is set again and a number of status codes in TWSR are possible. Possible status codes in Master mode are \$38, \$40, or \$48. The appropriate action to be taken for each of these status codes is detailed in Table 75. Received data can be read from the TWDR Register when the TWINT Flag is set high by hardware. This scheme is repeated until the last byte has been received. After the last byte has been received, the MR should inform the ST by sending a NACK after the last received data byte. The transfer is ended by generating a STOP condition or a repeated START condition. A STOP condition is generated by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 1     | Х    | 0     | 1     | Х    | 1    | 0 | Х    |

A REPEATED START condition is generated by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 1     | Х    | 1     | 0     | Х    | 1    | 0 | Х    |

After a repeated START condition (state \$10) the Two-wire Serial Interface can access the same Slave again, or a new Slave without transmitting a STOP condition. Repeated START enables the Master to switch between Slaves, Master Transmitter mode and Master Receiver mode without losing control over the bus.

Table 75. Status Codes for Master Receiver Mode

| Status Code              |                                                                 | Applicat     | tion Softw | are Resp        | onse  |      |                                   |

|--------------------------|-----------------------------------------------------------------|--------------|------------|-----------------|-------|------|-----------------------------------|

| (TWSR)<br>Prescaler Bits | Status of the Two-wire Serial<br>Bus and Two-wire Serial Inter- |              |            | To <sup>-</sup> | TWCR  |      |                                   |

| are 0                    | face Hardware                                                   | To/from TWDR | STA        | STO             | TWINT | TWEA | Next Action Taken by TWI Hardware |

will require 25 ADC clocks. This is because the ADC must be disabled and re-enabled after every conversion.

In Free Running mode, a new conversion will be started immediately after the conversion completes, while ADSC remains high. For a summary of conversion times, see Table 81.

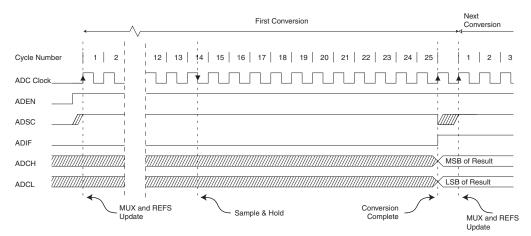

Figure 101. ADC Timing Diagram, First Conversion (Single Conversion Mode)

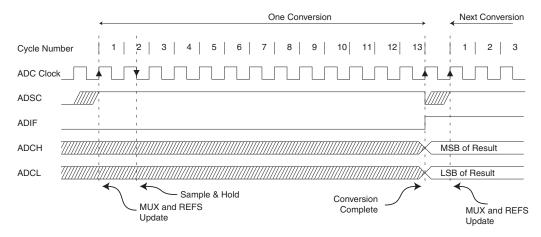

Figure 102. ADC Timing Diagram, Single Conversion

**Boundary-scan Chain** The Boundary-scan Chain has the capability of driving and observing the logic levels on the digital I/O pins, as well as the boundary between digital and analog logic for analog circuitry having Off-chip connections.

See "Boundary-scan Chain" on page 232 for a complete description.

**Boundary-scan Specific JTAG Instructions** The instruction register is 4-bit wide, supporting up to 16 instructions. Listed below are the JTAG instructions useful for Boundary-scan operation. Note that the optional HIGHZ instruction is not implemented, but all outputs with tri-state capability can be set in high-impedant state by using the AVR\_RESET instruction, since the initial state for all port pins is tri-state.

As a definition in this datasheet, the LSB is shifted in and out first for all Shift Registers.

The OPCODE for each instruction is shown behind the instruction name in hex format. The text describes which Data Register is selected as path between TDI and TDO for each instruction.

**EXTEST; \$0** Mandatory JTAG instruction for selecting the Boundary-scan Chain as Data Register for testing circuitry external to the AVR package. For port-pins, Pull-up Disable, Output Control, Output Data, and Input Data are all accessible in the scan chain. For Analog circuits having Off-chip connections, the interface between the analog and the digital logic is in the scan chain. The contents of the latched outputs of the Boundary-scan chain is driven out as soon as the JTAG IR-register is loaded with the EXTEST instruction.

The active states are:

- Capture-DR: Data on the external pins are sampled into the Boundary-scan Chain.

- Shift-DR: The Internal Scan Chain is shifted by the TCK input.

- Update-DR: Data from the scan chain is applied to output pins.

- **IDCODE; \$1** Optional JTAG instruction selecting the 32-bit ID-register as Data Register. The ID-register consists of a version number, a device number and the manufacturer code chosen by JEDEC. This is the default instruction after power-up.

The active states are:

- Capture-DR: Data in the IDCODE-register is sampled into the Boundary-scan Chain.

- Shift-DR: The IDCODE scan chain is shifted by the TCK input.

# SAMPLE\_PRELOAD; Mandatory JTAG instruction for pre-loading the output latches and talking a snap-shot of the input/output pins without affecting the system operation. However, the output latches are not connected to the pins. The Boundary-scan Chain is selected as Data Register.

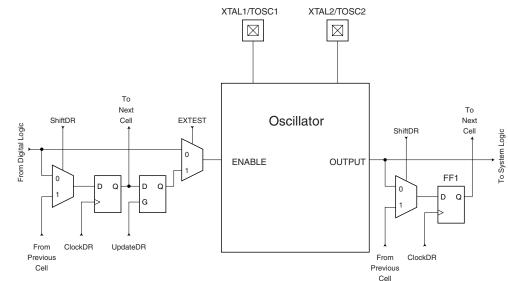

Figure 120. Boundary-scan Cells for Oscillators and Clock Options

Table 90 summaries the scan registers for the external clock pin XTAL1, Oscillators with XTAL1/XTAL2 connections as well as 32 kHz Timer Oscillator.

| Enable Signal | Scanned Clock Line | Clock Option                                      | Scanned Clock Line when not Used |

|---------------|--------------------|---------------------------------------------------|----------------------------------|

| EXTCLKEN      | EXTCLK (XTAL1)     | External Clock                                    | 0                                |

| OSCON         | OSCCK              | External Crystal<br>External Ceramic<br>Resonator | 0                                |

| RCOSCEN       | RCCK               | External RC                                       | 1                                |

| OSC32EN       | OSC32CK            | Low Freq. External Crystal                        | 0                                |

| TOSKON        | TOSCK              | 32 kHz Timer Oscillator                           | 0                                |

| Table 90. Sca | an Signals for the Os | cillators <sup>(1)(2)(3)</sup> |

|---------------|-----------------------|--------------------------------|

|---------------|-----------------------|--------------------------------|

Notes: 1. Do not enable more than one clock source as main clock at a time.

2. Scanning an Oscillator output gives unpredictable results as there is a frequency drift between the Internal Oscillator and the JTAG TCK clock. If possible, scanning an external clock is preferred.

3. The clock configuration is programmed by fuses. As a fuse is not changed run-time, the clock configuration is considered fixed for a given application. The user is advised to scan the same clock option as to be used in the final system. The enable signals are supported in the scan chain because the system logic can disable clock options in sleep modes, thereby disconnecting the Oscillator pins from the scan path if not provided. The INTCAP Fuses are not supported in the scan-chain, so the boundary scan chain can not make a XTAL Oscillator requiring internal capacitors to run unless the fuse is correctly programmed.

Scanning the AnalogThe relevant Comparator signals regarding Boundary-scan are shown in Figure 121. The<br/>Boundary-scan cell from Figure 122 is attached to each of these signals. The signals are<br/>described in Table 91.

The Comparator need not be used for pure connectivity testing, since all analog inputs are shared with a digital port pin as well.

Simple Assembly ;-the routine writes one page of data from RAM to Flash Code Example for a ; the first data location in RAM is pointed to by the Y pointer ; the first data location in Flash is pointed to by the Z pointer **Boot Loader** ;-error handling is not included ;-the routine must be placed inside the boot space ; (at least the Do\_spm sub routine). Only code inside NRWW section can ; be read during self-programming (page erase and page write). ;-registers used: r0, r1, temp1 (r16), temp2 (r17), looplo (r24), ; loophi (r25), spmcrval (r20) ; storing and restoring of registers is not included in the routine ; register usage can be optimized at the expense of code size ;-It is assumed that either the interrupt table is moved to the Boot ; loader section or that the interrupts are disabled. .equ PAGESIZEB = PAGESIZE\*2 ; PAGESIZEB is page size in BYTES, not ; words .org SMALLBOOTSTART Write\_page: ; page erase ldi spmcrval, (1<<PGERS) | (1<<SPMEN) call Do spm ; re-enable the RWW section ldi spmcrval, (1<<RWWSRE) | (1<<SPMEN)</pre> call Do spm ; transfer data from RAM to Flash page buffer ldi looplo, low(PAGESIZEB) ;init loop variable ldi loophi, high(PAGESIZEB) ;not required for PAGESIZEB<=256 Wrloop: ld r0, Y+ ld r1, Y+ ldi spmcrval, (1<<SPMEN) call Do spm adiw ZH:ZL, 2 sbiw loophi:looplo, 2 ;use subi for PAGESIZEB<=256 brne Wrloop ; execute page write subi ZL, low(PAGESIZEB) ;restore pointer sbci ZH, high(PAGESIZEB) ;not required for PAGESIZEB<=256 ldi spmcrval, (1<<PGWRT) | (1<<SPMEN) call Do\_spm ; re-enable the RWW section ldi spmcrval, (1<<RWWSRE) | (1<<SPMEN)</pre> call Do\_spm ; read back and check, optional ldi looplo, low(PAGESIZEB) ;init loop variable ldi loophi, high(PAGESIZEB) ;not required for PAGESIZEB<=256 subi YL, low(PAGESIZEB) ;restore pointer sbci YH, high(PAGESIZEB) Rdloop: lpm r0, Z+ ld r1, Y+ cpse r0, r1 jmp Error sbiw loophi:looplo, 1 ;use subi for PAGESIZEB<=256 brne Rdloop ; return to RWW section ; verify that RWW section is safe to read Return: temp1, SPMCR in

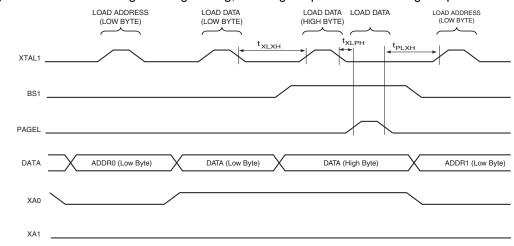

#### Programming the Flash

The Flash is organized in pages, see Table 107 on page 262. When programming the Flash, the program data is latched into a page buffer. This allows one page of program data to be programmed simultaneously. The following procedure describes how to program the entire Flash memory:

- A. Load Command "Write Flash"

- 1. Set XA1, XA0 to "10". This enables command loading.

- 2. Set BS1 to "0".

- 3. Set DATA to "0001 0000". This is the command for Write Flash.

- 4. Give XTAL1 a positive pulse. This loads the command.

- B. Load Address Low byte

- 1. Set XA1, XA0 to "00". This enables address loading.

- 2. Set BS1 to "0". This selects low address.

- 3. Set DATA = Address Low byte (\$00 \$FF).

- 4. Give XTAL1 a positive pulse. This loads the address Low byte.

- C. Load Data Low Byte

- 1. Set XA1, XA0 to "01". This enables data loading.

- 2. Set DATA = Data Low byte (\$00 \$FF).

- 3. Give XTAL1 a positive pulse. This loads the data byte.

- D. Load Data High Byte

- 1. Set BS1 to "1". This selects high data byte.

- 2. Set XA1, XA0 to "01". This enables data loading.

- 3. Set DATA = Data High byte (\$00 \$FF).

- 4. Give XTAL1 a positive pulse. This loads the data byte.

- E. Latch Data

- 1. Set BS1 to "1". This selects high data byte.

- Give PAGEL a positive pulse. This latches the data bytes. (See Figure 129 for signal waveforms)

- F. Repeat B through E until the entire buffer is filled or until all data within the page is loaded.

While the lower bits in the address are mapped to words within the page, the higher bits address the pages within the FLASH. This is illustrated in Figure 128 on page 267. Note that if less than 8 bits are required to address words in the page (pagesize < 256), the most significant bit(s) in the address Low byte are used to address the page when performing a page write.

- G. Load Address High byte

- 1. Set XA1, XA0 to "00". This enables address loading.

- 2. Set BS1 to "1". This selects high address.

- 3. Set DATA = Address High byte (\$00 \$FF).

- 4. Give XTAL1 a positive pulse. This loads the address High byte.

- H. Program Page

- 1. Set BS1 = "0"

- Give WR a negative pulse. This starts programming of the entire page of data. RDY/BSY goes low.

- 3. Wait until RDY/BSY goes high. (See Figure 129 for signal waveforms)

Figure 134. Parallel Programming Timing, Loading Sequence with Timing Requirements<sup>(1)</sup>

Note: 1. The timing requirements shown in Figure 133 (that is, t<sub>DVXH</sub>, t<sub>XHXL</sub>, and t<sub>XLDX</sub>) also apply to loading operation.

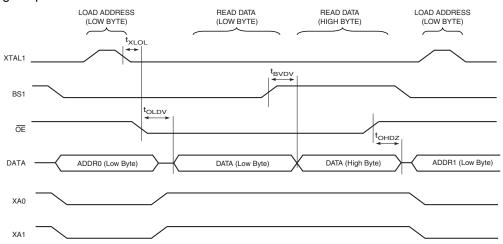

**Figure 135.** Parallel Programming Timing, Reading Sequence (within the Same Page) with Timing Requirements<sup>(1)</sup>

Note: 1. The timing requirements shown in Figure 133 (that is, t<sub>DVXH</sub>, t<sub>XHXL</sub>, and t<sub>XLDX</sub>) also apply to reading operation.

| Table 113. | Parallel Programming | Characteristics. | $V_{CC} = 5V \pm 10\%$ |

|------------|----------------------|------------------|------------------------|

|            |                      |                  |                        |

| Symbol          | Parameter                  | Min  | Тур | Max  | Units |

|-----------------|----------------------------|------|-----|------|-------|

| V <sub>PP</sub> | Programming Enable Voltage | 11.5 |     | 12.5 | V     |

| I <sub>PP</sub> | Programming Enable Current |      |     | 250  | μA    |

# **ADC Characteristics**

Table 122.

ADC Characteristics

| Symbol           | Parameter                                                                              | Condition                                                                                                | Min <sup>(1)</sup>                   | Typ <sup>(1)</sup> | Max <sup>(1)</sup>                   | Units |

|------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------|--------------------------------------|-------|

|                  |                                                                                        | Single Ended Conversion                                                                                  |                                      | 10                 |                                      |       |

|                  | Resolution                                                                             | Differential Conversion<br>Gain = 1x or 10x                                                              |                                      | 8                  |                                      | Bits  |

|                  |                                                                                        | Differential Conversion<br>Gain = 200x                                                                   |                                      | 7                  |                                      |       |

|                  |                                                                                        | Single Ended Conversion<br>$V_{REF} = 4V, V_{CC} = 4V$<br>ADC clock = 200 kHz                            |                                      | 1.5                | 2.5                                  |       |

|                  | Absolute Accuracy (Including INL, DNL,<br>Quantization Error, Gain, and Offset Error). | Single Ended Conversion<br>$V_{REF} = 4V, V_{CC} = 4V$<br>ADC clock = 1 MHz                              |                                      | 3                  | 4                                    |       |

|                  |                                                                                        | Single Ended Conversion<br>$V_{REF} = 4V$ , $V_{CC} = 4V$<br>ADC clock = 200 kHz<br>Noise Reduction mode |                                      | 1.5                |                                      |       |

|                  |                                                                                        | Single Ended Conversion<br>$V_{REF} = 4V, V_{CC} = 4V$<br>ADC clock = 1 MHz<br>Noise Reduction mode      |                                      | 3                  |                                      | LSB   |

|                  | Integral Non-linearity (INL)                                                           | Single Ended Conversion<br>$V_{REF} = 4V, V_{CC} = 4V$<br>ADC clock = 200 kHz                            |                                      | 1                  |                                      |       |

|                  | Differential Non-linearity (DNL)                                                       | Single Ended Conversion<br>$V_{REF} = 4V, V_{CC} = 4V$<br>ADC clock = 200 kHz                            |                                      | 0.5                |                                      |       |

|                  | Gain Error                                                                             | Single Ended Conversion<br>$V_{REF} = 4V, V_{CC} = 4V$<br>ADC clock = 200 kHz                            |                                      | 1                  |                                      |       |

|                  | Offset Error                                                                           | Single Ended Conversion<br>$V_{REF} = 4V$ , $V_{CC} = 4V$<br>ADC clock = 200 kHz                         |                                      |                    |                                      |       |

|                  | Conversion Time                                                                        | Free Running Conversion                                                                                  | 13                                   |                    | 260                                  | μs    |

|                  | Clock Frequency                                                                        |                                                                                                          | 50                                   |                    | 1000                                 | kHz   |

| AVCC             | Analog Supply Voltage                                                                  |                                                                                                          | V <sub>CC</sub> - 0.3 <sup>(2)</sup> |                    | V <sub>CC</sub> + 0.3 <sup>(3)</sup> |       |

| V <sub>REF</sub> | Reference Voltage                                                                      | Single Ended Conversion                                                                                  | 2.0                                  |                    | AVCC                                 |       |

| * KEF            |                                                                                        | Differential Conversion                                                                                  | 2.0                                  |                    | AVCC - 0.2                           | V     |

|                  | Input voltage                                                                          | Single ended channels                                                                                    | GND                                  |                    | V <sub>REF</sub>                     |       |

| V <sub>IN</sub>  |                                                                                        | Differential channels                                                                                    | 0                                    |                    | V <sub>REF</sub>                     |       |

| 11N              | Input bandwidth                                                                        | Single ended channels                                                                                    |                                      | 38.5               |                                      | kHz   |

|                  |                                                                                        | Differential channels                                                                                    |                                      | 4                  |                                      |       |

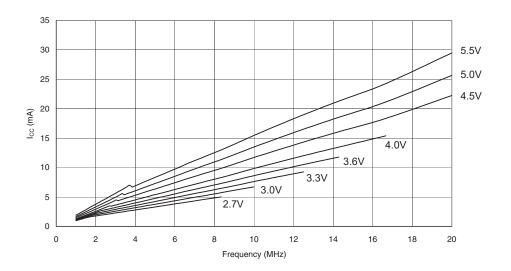

Figure 150. Active Supply Current vs. Frequency (1 MHz - 20 MHz)

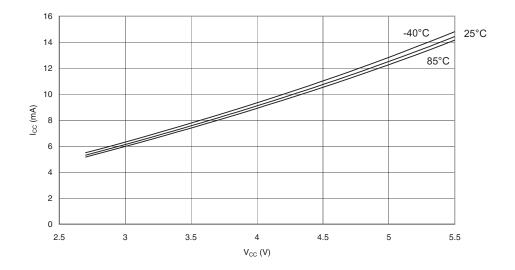

Figure 151. Active Supply Current vs.  $V_{CC}$  (Internal RC Oscillator, 8 MHz)

# Errata

The revision letter in this section refers to the revision of the ATmega16 device.

### ATmega16(L) Rev. M

#### **V.** • First Analog Comparator conversion may be delayed

- Interrupts may be lost when writing the timer registers in the asynchronous timer

- IDCODE masks data from TDI input

- Reading EEPROM by using ST or STS to set EERE bit triggers unexpected interrupt request

#### 1. First Analog Comparator conversion may be delayed

If the device is powered by a slow rising  $V_{CC}$ , the first Analog Comparator conversion will take longer than expected on some devices.

#### **Problem Fix/Workaround**

When the device has been powered or reset, disable then enable the Analog Comparator before the first conversion.

#### 2. Interrupts may be lost when writing the timer registers in the asynchronous timer

The interrupt will be lost if a timer register that is synchronized to the asynchronous timer clock is written when the asynchronous Timer/Counter register(TCNTx) is 0x00.

#### Problem Fix / Workaround

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register(TCCRx), asynchronous Timer Counter Register(TCNTx), or asynchronous Output Compare Register(OCRx).

#### 3. IDCODE masks data from TDI input

The JTAG instruction IDCODE is not working correctly. Data to succeeding devices are replaced by all-ones during Update-DR.

#### **Problem Fix / Workaround**

- If ATmega16 is the only device in the scan chain, the problem is not visible.

- Select the Device ID Register of the ATmega16 by issuing the IDCODE instruction or by entering the Test-Logic-Reset state of the TAP controller to read out the contents of its Device ID Register and possibly data from succeeding devices of the scan chain. Issue the BYPASS instruction to the ATmega16 while reading the Device ID Registers of preceding devices of the boundary scan chain.

- If the Device IDs of all devices in the boundary scan chain must be captured simultaneously, the ATmega16 must be the fist device in the chain.

# 4. Reading EEPROM by using ST or STS to set EERE bit triggers unexpected interrupt request.

Reading EEPROM by using the ST or STS command to set the EERE bit in the EECR register triggers an unexpected EEPROM interrupt request.

#### Problem Fix / Workaround

Always use OUT or SBI to set EERE in EECR.

#### ATmega16(L) Rev. L

- First Analog Comparator conversion may be delayed

- Interrupts may be lost when writing the timer registers in the asynchronous timer

- IDCODE masks data from TDI input

- Reading EEPROM by using ST or STS to set EERE bit triggers unexpected interrupt request

# 1. First Analog Comparator conversion may be delayed

If the device is powered by a slow rising  $V_{CC}$ , the first Analog Comparator conversion will take longer than expected on some devices.