Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                   |

|----------------------------|----------------------------------------------------------|

| Core Processor             | AVR                                                      |

| Core Size                  | 8-Bit                                                    |

| Speed                      | 16MHz                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                    |

| Number of I/O              | 32                                                       |

| Program Memory Size        | 16KB (8K × 16)                                           |

| Program Memory Type        | FLASH                                                    |

| EEPROM Size                | 512 x 8                                                  |

| RAM Size                   | 1K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                              |

| Data Converters            | A/D 8x10b                                                |

| Oscillator Type            | Internal                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                       |

| Mounting Type              | Surface Mount                                            |

| Package / Case             | 44-TQFP                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atmega16-16aq |

|                            |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

also assume that no Flash Boot Loader is present in the software. If such code is present, the EEPROM write function must also wait for any ongoing SPM command to finish.

```

Assembly Code Example

EEPROM_write:

; Wait for completion of previous write

sbic EECR, EEWE

rjmp EEPROM_write

; Set up address (r18:r17) in address register

out EEARH, r18

out EEARL, r17

; Write data (r16) to data register

out EEDR,r16

; Write logical one to EEMWE

sbi EECR, EEMWE

; Start eeprom write by setting EEWE

sbi EECR, EEWE

ret

```

C Code Example

```

void EEPROM_write(unsigned int uiAddress, unsigned char ucData)

{

/* Wait for completion of previous write */

while(EECR & (1<<EEWE))

;

/* Set up address and data registers */

EEAR = uiAddress;

EEDR = ucData;

/* Write logical one to EEMWE */

EECR |= (1<<EEMWE);

/* Start eeprom write by setting EEWE */

EECR |= (1<<EEWE);

}</pre>

```

The next code examples show assembly and C functions for reading the EEPROM. The examples assume that interrupts are controlled so that no interrupts will occur during execution of these functions.

| EEI                                  | PROM read:                                                                                                                                                                                                                                                                                                         |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | : Wait for completion of previous write                                                                                                                                                                                                                                                                            |

|                                      | sbic EECR, EEWE                                                                                                                                                                                                                                                                                                    |

|                                      | rjmp EEPROM read                                                                                                                                                                                                                                                                                                   |

|                                      | : Set up address (r18:r17) in address register                                                                                                                                                                                                                                                                     |

|                                      | put EEARH, r18                                                                                                                                                                                                                                                                                                     |

|                                      | but EEARL, r17                                                                                                                                                                                                                                                                                                     |

| ;                                    | : Start eeprom read by writing EERE                                                                                                                                                                                                                                                                                |

| E                                    | <b>sbi</b> EECR, EERE                                                                                                                                                                                                                                                                                              |

| ;                                    | : Read data from data register                                                                                                                                                                                                                                                                                     |

| i                                    | n r16,EEDR                                                                                                                                                                                                                                                                                                         |

| -                                    |                                                                                                                                                                                                                                                                                                                    |

| L L                                  | ret                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                    |

| Code                                 | e Example                                                                                                                                                                                                                                                                                                          |

| Code                                 |                                                                                                                                                                                                                                                                                                                    |

| Code<br>uns<br>{                     | e Example                                                                                                                                                                                                                                                                                                          |

| Code<br>uns<br>{                     | e Example<br>signed char EEPROM_read(unsigned int uiAddress)                                                                                                                                                                                                                                                       |

| Code<br>uns<br>{                     | e Example<br>signed char EEPROM_read(unsigned int uiAddress)<br>/* Wait for completion of previous write */                                                                                                                                                                                                        |

| Uns<br>{<br>/                        | e Example<br>signed char EEPROM_read(unsigned int uiAddress)<br>/* Wait for completion of previous write */<br>while(EECR & (1< <eewe))< td=""></eewe))<>                                                                                                                                                          |

| Code<br>uns<br>{<br>/                | <pre>e Example signed char EEPROM_read(unsigned int uiAddress) /* Wait for completion of previous write */ while(EECR &amp; (1&lt;<eewe)) ;<="" pre=""></eewe))></pre>                                                                                                                                             |

| Code<br>uns<br>{<br>/<br>w           | <pre>e Example signed char EEPROM_read(unsigned int uiAddress) /* Wait for completion of previous write */ while(EECR &amp; (1&lt;<eewe)) *="" ;="" <="" address="" pre="" register="" set="" up=""></eewe))></pre>                                                                                                |

| Code<br>uns<br>{<br>/<br>w           | <pre>e Example signed char EEPROM_read(unsigned int uiAddress) /* Wait for completion of previous write */ while(EECR &amp; (1&lt;<eewe)) *="" ;="" address="" eear="uiAddress;&lt;/pre" register="" set="" up=""></eewe))></pre>                                                                                  |

| Code<br>uns<br>{<br>/<br>w<br>/<br>E | <pre>e Example signed char EEPROM_read(unsigned int uiAddress) /* Wait for completion of previous write */ while(EECR &amp; (1&lt;<eewe)) *="" ;="" <="" address="" by="" eear="uiAddress;" eeprom="" eere="" pre="" read="" register="" set="" start="" up="" writing=""></eewe))></pre>                          |

| Code<br>uns<br>{<br>/<br>W<br>/<br>E | <pre>e Example signed char EEPROM_read(unsigned int uiAddress) /* Wait for completion of previous write */ while(EECR &amp; (1&lt;<eewe)) *="" ;="" address="" by="" eear="uiAddress;" eecr="" eeprom="" eere="" read="" register="" set="" start="" up="" writing=""  ="(1&lt;&lt;EERE);&lt;/pre"></eewe))></pre> |

| EEPROM Write During<br>Power-down Sleep<br>Mode | When entering Power-down Sleep mode while an EEPROM write operation is active, the EEPROM write operation will continue, and will complete before the Write Access time has passed. However, when the write operation is completed, the Oscillator continues running, and as a consequence, the device does not enter Power-down entirely. It is therefore recommended to verify that the EEPROM write operation is completed before entering Power-down. |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preventing EEPROM<br>Corruption                 | During periods of low $V_{CC}$ , the EEPROM data can be corrupted because the supply voltage is too low for the CPU and the EEPROM to operate properly. These issues are the same as for board level systems using EEPROM, and the same design solutions should be applied.                                                                                                                                                                               |

|                                                 | An EEPROM data corruption can be caused by two situations when the voltage is too low. First, a regular write sequence to the EEPROM requires a minimum voltage to operate correctly. Secondly, the CPU itself can execute instructions incorrectly, if the supply voltage is too low.                                                                                                                                                                    |

#### Alternate Functions of Port C

f The Port C pins with alternate functions are shown in Table 28. If the JTAG interface is enabled, the pull-up resistors on pins PC5(TDI), PC3(TMS) and PC2(TCK) will be activated even if a reset occurs.

| Table 28. | Port C Pins Alternate Functions |

|-----------|---------------------------------|

|-----------|---------------------------------|

| Port Pin | Alternate Function                               |

|----------|--------------------------------------------------|

| PC7      | TOSC2 (Timer Oscillator Pin 2)                   |

| PC6      | TOSC1 (Timer Oscillator Pin 1)                   |

| PC5      | TDI (JTAG Test Data In)                          |

| PC4      | TDO (JTAG Test Data Out)                         |

| PC3      | TMS (JTAG Test Mode Select)                      |

| PC2      | TCK (JTAG Test Clock)                            |

| PC1      | SDA (Two-wire Serial Bus Data Input/Output Line) |

| PC0      | SCL (Two-wire Serial Bus Clock Line)             |

The alternate pin configuration is as follows:

#### • TOSC2 - Port C, Bit 7

TOSC2, Timer Oscillator pin 2: When the AS2 bit in ASSR is set (one) to enable asynchronous clocking of Timer/Counter2, pin PC7 is disconnected from the port, and becomes the inverting output of the Oscillator amplifier. In this mode, a Crystal Oscillator is connected to this pin, and the pin can not be used as an I/O pin.

### • TOSC1 - Port C, Bit 6

TOSC1, Timer Oscillator pin 1: When the AS2 bit in ASSR is set (one) to enable asynchronous clocking of Timer/Counter2, pin PC6 is disconnected from the port, and becomes the input of the inverting Oscillator amplifier. In this mode, a Crystal Oscillator is connected to this pin, and the pin can not be used as an I/O pin.

#### • TDI - Port C, Bit 5

TDI, JTAG Test Data In: Serial input data to be shifted in to the Instruction Register or Data Register (scan chains). When the JTAG interface is enabled, this pin can not be used as an I/O pin.

#### • TDO - Port C, Bit 4

TDO, JTAG Test Data Out: Serial output data from Instruction Register or Data Register. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

The TD0 pin is tri-stated unless TAP states that shifts out data are entered.

#### • TMS – Port C, Bit 3

TMS, JTAG Test Mode Select: This pin is used for navigating through the TAP-controller state machine. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

#### • TCK – Port C, Bit 2

TCK, JTAG Test Clock: JTAG operation is synchronous to TCK. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

| Signal Name | PD3/INT1    | PD2/INT0    | PD1/TXD | PD0/RXD      |

|-------------|-------------|-------------|---------|--------------|

| PUOE        | 0           | 0           | TXEN    | RXEN         |

| PUOV        | 0           | 0           | 0       | PORTD0 • PUD |

| DDOE        | 0           | 0           | TXEN    | RXEN         |

| DDOV        | 0           | 0           | 1       | 0            |

| PVOE        | 0           | 0           | TXEN    | 0            |

| PVOV        | 0           | 0           | TXD     | 0            |

| DIEOE       | INT1 ENABLE | INT0 ENABLE | 0       | 0            |

| DIEOV       | 1           | 1           | 0       | 0            |

| DI          | INT1 INPUT  | INT0 INPUT  | _       | RXD          |

| AIO         | -           | _           | _       | -            |

Table 33. Overriding Signals for Alternate Functions in PD3..PD0

|                                             | The OCR0 Register access may seem complex, but this is not case. When the double buffering is enabled, the CPU has access to the OCR0 Buffer Register, and if double buffering is disabled the CPU will access the OCR0 directly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Force Output<br>Compare                     | In non-PWM waveform generation modes, the match output of the comparator can be forced by writing a one to the Force Output Compare (FOC0) bit. Forcing compare match will not set the OCF0 Flag or reload/clear the timer, but the OC0 pin will be updated as if a real compare match had occurred (the COM01:0 bits settings define whether the OC0 pin is set, cleared or toggled).                                                                                                                                                                                                                                                                                                             |

| Compare Match<br>Blocking by TCNT0<br>Write | All CPU write operations to the TCNT0 Register will block any compare match that occur in the next timer clock cycle, even when the timer is stopped. This feature allows OCR0 to be initialized to the same value as TCNT0 without triggering an interrupt when the Timer/Counter clock is enabled.                                                                                                                                                                                                                                                                                                                                                                                               |

| Using the Output<br>Compare Unit            | Since writing TCNT0 in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNT0 when using the output compare unit, independently of whether the Timer/Counter is running or not. If the value written to TCNT0 equals the OCR0 value, the compare match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT0 value equal to BOTTOM when the counter is downcounting.                                                                                                                                                                                                                 |

|                                             | The setup of the OC0 should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC0 value is to use the Force Output Compare (FOC0) strobe bits in Normal mode. The OC0 Register keeps its value even when changing between waveform generation modes.                                                                                                                                                                                                                                                                                                                                                                              |

|                                             | Be aware that the COM01:0 bits are not double buffered together with the compare value. Changing the COM01:0 bits will take effect immediately.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Compare Match<br>Output Unit                | The Compare Output mode (COM01:0) bits have two functions. The Waveform Generator uses the COM01:0 bits for defining the Output Compare (OC0) state at the next compare match. Also, the COM01:0 bits control the OC0 pin output source. Figure 30 shows a simplified schematic of the logic affected by the COM01:0 bit setting. The I/O Registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O port Control Registers (DDR and PORT) that are affected by the COM01:0 bits are shown. When referring to the OC0 state, the reference is for the internal OC0 Register, not the OC0 pin. If a System Reset occur, the OC0 Register is reset to "0". |

In fast PWM mode, the compare unit allows generation of PWM waveforms on the OC0 pin. Setting the COM01:0 bits to 2 will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM01:0 to 3 (See Table 40 on page 84). The actual OC0 value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by setting (or clearing) the OC0 Register at the compare match between OCR0 and TCNT0, and clearing (or setting) the OC0 Register at the timer clock cycle the counter is cleared (changes from MAX to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{OCnPWM} = \frac{J_{clk\_l/O}}{N \cdot 256}$$

The N variable represents the prescale factor (1, 8, 64, 256, or 1024).

The extreme values for the OCR0 Register represents special cases when generating a PWM waveform output in the fast PWM mode. If the OCR0 is set equal to BOTTOM, the output will be a narrow spike for each MAX+1 timer clock cycle. Setting the OCR0 equal to MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM01:0 bits.)

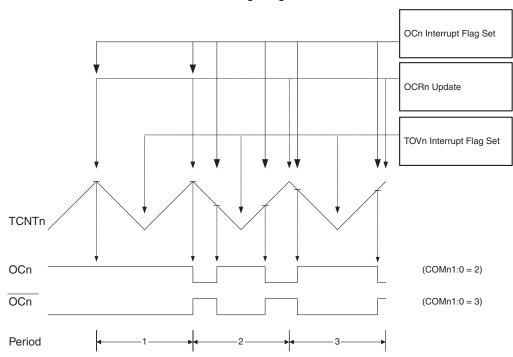

#### Phase Correct PWM Mode

The phase correct PWM mode (WGM01:0 = 1) provides a high resolution phase correct PWM waveform generation option. The phase correct PWM mode is based on a dual-slope operation. The counter counts repeatedly from BOTTOM to MAX and then from MAX to BOTTOM. In non-inverting Compare Output mode, the Output Compare (OC0) is cleared on the compare match between TCNT0 and OCR0 while upcounting, and set on the compare match while downcount-ing. In inverting Output Compare mode, the operation is inverted. The dual-slope operation has lower maximum operation frequency than single slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications.

The PWM resolution for the phase correct PWM mode is fixed to eight bits. In phase correct PWM mode the counter is incremented until the counter value matches MAX. When the counter reaches MAX, it changes the count direction. The TCNT0 value will be equal to MAX for one timer clock cycle. The timing diagram for the phase correct PWM mode is shown on Figure 33. The TCNT0 value is in the timing diagram shown as a histogram for illustrating the dual-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT0 slopes represent compare matches between OCR0 and TCNT0.

Figure 33. Phase Correct PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOV0) is set each time the counter reaches BOTTOM. The Interrupt Flag can be used to generate an interrupt each time the counter reaches the BOTTOM value.

In phase correct PWM mode, the compare unit allows generation of PWM waveforms on the OC0 pin. Setting the COM01:0 bits to 2 will produce a non-inverted PWM. An inverted PWM output can be generated by setting the COM01:0 to 3 (see Table 41 on page 84). The actual OC0 value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by clearing (or setting) the OC0 Register at the compare match between OCR0 and TCNT0 when the counter increments, and setting (or clearing) the OC0 Register at compare match between OCR0 and TCNT0 when the counter decrements. The

#### • Bit 0 – TOIE0: Timer/Counter0 Overflow Interrupt Enable

When the TOIE0 bit is written to one, and the I-bit in the Status Register is set (one), the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter0 occurs, that is, when the TOV0 bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

Timer/Counter Interrupt Flag Register – TIFR

| Bit           | 7    | 6    | 5    | 4     | 3     | 2    | 1    | 0    | _    |

|---------------|------|------|------|-------|-------|------|------|------|------|

|               | OCF2 | TOV2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0 | TOV0 | TIFR |

| Read/Write    | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W  | R/W  | •    |

| Initial Value | 0    | 0    | 0    | 0     | 0     | 0    | 0    | 0    |      |

### • Bit 1 – OCF0: Output Compare Flag 0

The OCF0 bit is set (one) when a compare match occurs between the Timer/Counter0 and the data in OCR0 – Output Compare Register0. OCF0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF0 is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE0 (Timer/Counter0 Compare Match Interrupt Enable), and OCF0 are set (one), the Timer/Counter0 Compare Match Interrupt is executed.

#### • Bit 0 – TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG I-bit, TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set (one), the Timer/Counter0 Overflow interrupt is executed. In phase correct PWM mode, this bit is set when Timer/Counter0 changes counting direction at \$00.

An interrupt can be generated at each time the counter value reaches the TOP value by either using the OCF1A or ICF1 Flag according to the register used to define the TOP value. If the interrupt is enabled, the interrupt handler routine can be used for updating the TOP value. However, changing the TOP to a value close to BOTTOM when the counter is running with none or a low prescaler value must be done with care since the CTC mode does not have the double buffering feature. If the new value written to OCR1A or ICR1 is lower than the current value of TCNT1, the counter will miss the compare match. The counter will then have to count to its maximum value (0xFFFF) and wrap around starting at 0x0000 before the compare match can occur. In many cases this feature is not desirable. An alternative will then be to use the fast PWM mode using OCR1A for defining TOP (WGM13:0 = 15) since the OCR1A then will be double buffered.

For generating a waveform output in CTC mode, the OC1A output can be set to toggle its logical level on each compare match by setting the compare output mode bits to toggle mode (COM1A1:0 = 1). The OC1A value will not be visible on the port pin unless the data direction for the pin is set to output (DDR\_OC1A = 1). The waveform generated will have a maximum frequency of  $f_{OC1A} = f_{clk_l/O}/2$  when OCR1A is set to zero (0x0000). The waveform frequency is defined by the following equation:

$$f_{OCnA} = \frac{f_{clk\_l/O}}{2 \cdot N \cdot (1 + OCRnA)}$$

The N variable represents the prescaler factor (1, 8, 64, 256, or 1024).

As for the Normal mode of operation, the TOV1 Flag is set in the same timer clock cycle that the counter counts from MAX to 0x0000.

**Fast PWM Mode** The *fast Pulse Width Modulation* or fast PWM mode (WGM13:0 = 5,6,7,14, or 15) provides a high frequency PWM waveform generation option. The fast PWM differs from the other PWM options by its single-slope operation. The counter counts from BOTTOM to TOP then restarts from BOTTOM. In non-inverting Compare Output mode, the Output Compare (OC1x) is cleared on the compare match between TCNT1 and OCR1x, and set at BOTTOM. In inverting Compare Output mode output is set on compare match and cleared at BOTTOM. Due to the single-slope operation, the operating frequency of the fast PWM mode can be twice as high as the phase correct and phase and frequency correct PWM modes that use dual-slope operation. This high frequency makes the fast PWM mode well suited for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors), hence reduces total system cost.

The PWM resolution for fast PWM can be fixed to 8-bit, 9-bit, or 10-bit, or defined by either ICR1 or OCR1A. The minimum resolution allowed is 2-bit (ICR1 or OCR1A set to 0x0003), and the maximum resolution is 16-bit (ICR1 or OCR1A set to MAX). The PWM resolution in bits can be calculated by using the following equation:

$$R_{FPWM} = \frac{\log(TOP + 1)}{\log(2)}$$

In fast PWM mode the counter is incremented until the counter value matches either one of the fixed values 0x00FF, 0x01FF, or 0x03FF (WGM13:0 = 5, 6, or 7), the value in ICR1 (WGM13:0 = 14), or the value in OCR1A (WGM13:0 = 15). The counter is then cleared at the following timer clock cycle. The timing diagram for the fast PWM mode is shown in Figure 46. The figure shows fast PWM mode when OCR1A or ICR1 is used to define TOP. The TCNT1 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT1 slopes represent compare matches between OCR1x and TCNT1. The OC1x Interrupt Flag will be set when a compare match occurs.

### Asynchronous Operation of the Timer/Counter

#### Asynchronous Status Register – ASSR

| Bit           | 7 | 6 | 5 | 4 | 3   | 2      | 1      | 0      | _    |

|---------------|---|---|---|---|-----|--------|--------|--------|------|

|               | - | - | - | - | AS2 | TCN2UB | OCR2UB | TCR2UB | ASSR |

| Read/Write    | R | R | R | R | R/W | R      | R      | R      |      |

| Initial Value | 0 | 0 | 0 | 0 | 0   | 0      | 0      | 0      |      |

#### • Bit 3 – AS2: Asynchronous Timer/Counter2

When AS2 is written to zero, Timer/Counter 2 is clocked from the I/O clock,  $clk_{I/O}$ . When AS2 is written to one, Timer/Counter2 is clocked from a Crystal Oscillator connected to the Timer Oscillator 1 (TOSC1) pin. When the value of AS2 is changed, the contents of TCNT2, OCR2, and TCCR2 might be corrupted.

#### • Bit 2 – TCN2UB: Timer/Counter2 Update Busy

When Timer/Counter2 operates asynchronously and TCNT2 is written, this bit becomes set. When TCNT2 has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCNT2 is ready to be updated with a new value.

#### • Bit 1 – OCR2UB: Output Compare Register2 Update Busy

When Timer/Counter2 operates asynchronously and OCR2 is written, this bit becomes set. When OCR2 has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that OCR2 is ready to be updated with a new value.

#### • Bit 0 – TCR2UB: Timer/Counter Control Register2 Update Busy

When Timer/Counter2 operates asynchronously and TCCR2 is written, this bit becomes set. When TCCR2 has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCCR2 is ready to be updated with a new value.

If a write is performed to any of the three Timer/Counter2 Registers while its update busy flag is set, the updated value might get corrupted and cause an unintentional interrupt to occur.

The mechanisms for reading TCNT2, OCR2, and TCCR2 are different. When reading TCNT2, the actual timer value is read. When reading OCR2 or TCCR2, the value in the temporary storage register is read.

When Timer/Counter2 operates asynchronously, some considerations must be taken.

- Warning: When switching between asynchronous and synchronous clocking of Timer/Counter2, the Timer Registers TCNT2, OCR2, and TCCR2 might be corrupted. A safe procedure for switching clock source is:

- 1. Disable the Timer/Counter2 interrupts by clearing OCIE2 and TOIE2.

- 2. Select clock source by setting AS2 as appropriate.

- 3. Write new values to TCNT2, OCR2, and TCCR2.

- 4. To switch to asynchronous operation: Wait for TCN2UB, OCR2UB, and TCR2UB.

- 5. Clear the Timer/Counter2 Interrupt Flags.

- 6. Enable interrupts, if needed.

Timer/Counter2

Asynchronous

**Operation of**

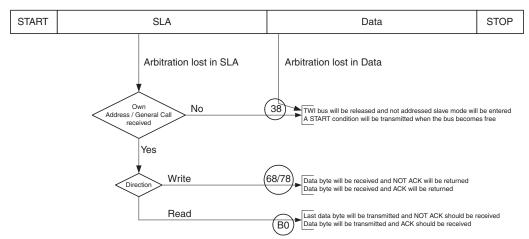

Several different scenarios may arise during arbitration, as described below:

- Two or more Masters are performing identical communication with the same Slave. In this case, neither the Slave nor any of the Masters will know about the bus contention.

- Two or more Masters are accessing the same Slave with different data or direction bit. In this case, arbitration will occur, either in the READ/WRITE bit or in the data bits. The Masters trying to output a one on SDA while another Master outputs a zero will lose the arbitration. Losing Masters will switch to not addressed Slave mode or wait until the bus is free and transmit a new START condition, depending on application software action.

- Two or more Masters are accessing different Slaves. In this case, arbitration will occur in the SLA bits. Masters trying to output a one on SDA while another Master outputs a zero will lose the arbitration. Masters losing arbitration in SLA will switch to Slave mode to check if they are being addressed by the winning Master. If addressed, they will switch to SR or ST mode, depending on the value of the READ/WRITE bit. If they are not being addressed, they will switch to not addressed Slave mode or wait until the bus is free and transmit a new START condition, depending on application software action.

This is summarized in Figure 96. Possible status values are given in circles.

Figure 96. Possible Status Codes Caused by Arbitration

| ADC Input Channels       | When changing channel selections, the user should observe the following guidelines to ensure that the correct channel is selected:                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | In Single Conversion mode, always select the channel before starting the conversion. The chan-<br>nel selection may be changed one ADC clock cycle after writing one to ADSC. However, the<br>simplest method is to wait for the conversion to complete before changing the channel selection.                                                                                                                                                                                                                                                                           |

|                          | In Free Running mode, always select the channel before starting the first conversion. The chan-<br>nel selection may be changed one ADC clock cycle after writing one to ADSC. However, the<br>simplest method is to wait for the first conversion to complete, and then change the channel<br>selection. Since the next conversion has already started automatically, the next result will reflect<br>the previous channel selection. Subsequent conversions will reflect the new channel selection.                                                                    |

|                          | When switching to a differential gain channel, the first conversion result may have a poor accuracy due to the required settling time for the automatic offset cancellation circuitry. The user should preferably disregard the first conversion result.                                                                                                                                                                                                                                                                                                                 |

| ADC Voltage<br>Reference | The reference voltage for the ADC ( $V_{REF}$ ) indicates the conversion range for the ADC. Single ended channels that exceed $V_{REF}$ will result in codes close to 0x3FF. $V_{REF}$ can be selected as either AVCC, internal 2.56V reference, or external AREF pin.                                                                                                                                                                                                                                                                                                   |

|                          | AVCC is connected to the ADC through a passive switch. The internal 2.56V reference is generated from the internal bandgap reference ( $V_{BG}$ ) through an internal amplifier. In either case, the external AREF pin is directly connected to the ADC, and the reference voltage can be made more immune to noise by connecting a capacitor between the AREF pin and ground. $V_{REF}$ can also be measured at the AREF pin with a high impedant voltmeter. Note that $V_{REF}$ is a high impedant source, and only a capacitive load should be connected in a system. |

|                          | If the user has a fixed voltage source connected to the AREF pin, the user may not use the other reference voltage options in the application, as they will be shorted to the external voltage. If no external voltage is applied to the AREF pin, the user may switch between AVCC and 2.56V as reference selection. The first ADC conversion result after switching reference voltage source may be inaccurate, and the user is advised to discard this result.                                                                                                        |

|                          | If differential channels are used, the selected reference should not be closer to AVCC than indicated in Table 122 on page 297.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ADC Noise<br>Canceler    | The ADC features a noise canceler that enables conversion during sleep mode to reduce noise induced from the CPU core and other I/O peripherals. The noise canceler can be used with ADC Noise Reduction and Idle mode. To make use of this feature, the following procedure should be used:                                                                                                                                                                                                                                                                             |

|                          | <ol> <li>Make sure that the ADC is enabled and is not busy converting. Single Conversion<br/>Mode must be selected and the ADC conversion complete interrupt must be<br/>enabled.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                             |

|                          | <ol><li>Enter ADC Noise Reduction mode (or Idle mode). The ADC will start a conversion<br/>once the CPU has been halted.</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                          | 3. If no other interrupts occur before the ADC conversion completes, the ADC interrupt will wake up the CPU and execute the ADC Conversion Complete interrupt routine. If another interrupt wakes up the CPU before the ADC conversion is complete, that interrupt will be executed, and an ADC Conversion Complete interrupt request will be generated when the ADC conversion completes. The CPU will remain in active mode until a new sleep command is executed.                                                                                                     |

|                          | Note that the ADC will not be automatically turned off when entering other sleep modes than Idle mode and ADC Noise Reduction mode. The user is advised to write zero to ADEN before enter-                                                                                                                                                                                                                                                                                                                                                                              |

Noise Reduction mode. The user is advised to write zero to nter ing such sleep modes to avoid excessive power consumption. If the ADC is enabled in such

sleep modes and the user wants to perform differential conversions, the user is advised to switch the ADC off and on after waking up from sleep to prompt an extended conversion to get a valid result.

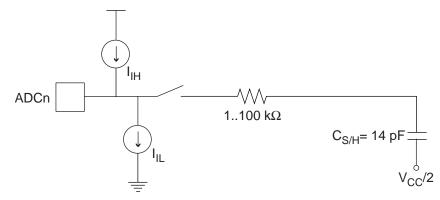

**Analog Input Circuitry** The Analog Input Circuitry for single ended channels is illustrated in Figure 105. An analog source applied to ADCn is subjected to the pin capacitance and input leakage of that pin, regardless of whether that channel is selected as input for the ADC. When the channel is selected, the source must drive the S/H capacitor through the series resistance (combined resistance in the input path).

The ADC is optimized for analog signals with an output impedance of approximately 10 k $\Omega$  or less. If such a source is used, the sampling time will be negligible. If a source with higher impedance is used, the sampling time will depend on how long time the source needs to charge the S/H capacitor, with can vary widely. The user is recommended to only use low impedant sources with slowly varying signals, since this minimizes the required charge transfer to the S/H capacitor.

If differential gain channels are used, the input circuitry looks somewhat different, although source impedances of a few hundred  $k\Omega$  or less is recommended.

Signal components higher than the Nyquist frequency ( $f_{ADC}/2$ ) should not be present for either kind of channels, to avoid distortion from unpredictable signal convolution. The user is advised to remove high frequency components with a low-pass filter before applying the signals as inputs to the ADC.

Figure 105. Analog Input Circuitry

Analog Noise Canceling Techniques

Digital circuitry inside and outside the device generates EMI which might affect the accuracy of analog measurements. If conversion accuracy is critical, the noise level can be reduced by applying the following techniques:

- 1. Keep analog signal paths as short as possible. Keep them well away from highspeed switching digital tracks.

- The AVCC pin on the device should be connected to the digital V<sub>CC</sub> supply voltage via an LC network as shown in Figure 106.

- 3. Use the ADC noise canceler function to reduce induced noise from the CPU.

- 4. If any ADC port pins are used as digital outputs, it is essential that these do not switch while a conversion is in progress.

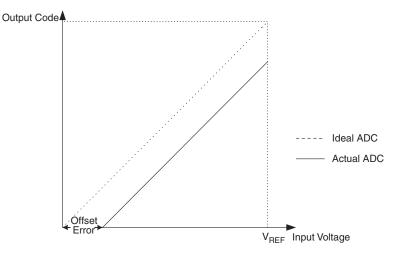

#### Figure 107. Offset Error

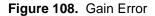

• Gain Error: After adjusting for offset, the Gain Error is found as the deviation of the last transition (0x3FE to 0x3FF) compared to the ideal transition (at 1.5 LSB below maximum). Ideal value: 0 LSB

Integral Non-linearity (INL): After adjusting for offset and gain error, the INL is the maximum deviation of an actual transition compared to an ideal transition for any code. Ideal value: 0 LSB.

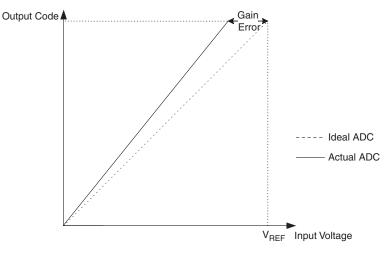

Figure 132. Mapping between BS1, BS2 and the Fuse- and Lock Bits during Read

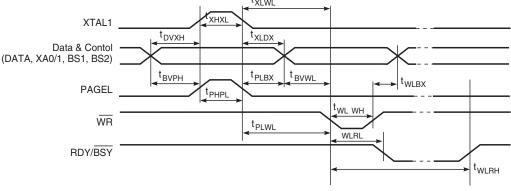

The algorithm for reading the Signature bytes is as follows (refer to "Programming the Flash" on **Reading the Signature Bytes** page 266 for details on Command and Address loading): 1. A: Load Command "0000 1000". 2. B: Load Address Low Byte (\$00 - \$02). Set  $\overline{OE}$  to "0", and BS1 to "0". The selected Signature byte can now be read at DATA. 3. Set OE to "1". 4. Reading the The algorithm for reading the Calibration byte is as follows (refer to "Programming the Flash" on **Calibration Byte** page 266 for details on Command and Address loading): 1. A: Load Command "0000 1000". 2. B: Load Address Low Byte, \$00. 3. Set OE to "0", and BS1 to "1". The Calibration byte can now be read at DATA. Set OE to "1". 4. Parallel Programming Figure 133. Parallel Programming Timing, Including some General Timing Requirements **Characteristics** t<sub>XLWL</sub>

### Table 122. ADC Characteristics (Continued)

| Symbol           | Parameter                  | Condition | Min <sup>(1)</sup> | Typ <sup>(1)</sup> | Max <sup>(1)</sup> | Units |

|------------------|----------------------------|-----------|--------------------|--------------------|--------------------|-------|

| V <sub>INT</sub> | Internal Voltage Reference |           | 2.3                | 2.6                | 2.9                | V     |

| R <sub>REF</sub> | Reference Input Resistance |           |                    | 32                 |                    | kΩ    |

| R <sub>AIN</sub> | Analog Input Resistance    |           |                    | 100                |                    | MΩ    |

Notes: 1. Values are guidelines only.

2. Minimum for AVCC is 2.7V.

3. Maximum for AVCC is 5.5V.

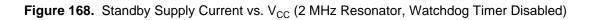

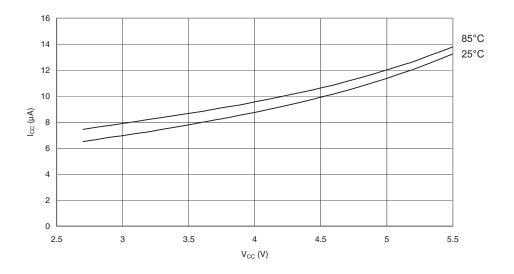

Figure 169. Standby Supply Current vs.  $V_{CC}$  (2 MHz Xtal, Watchdog Timer Disabled)

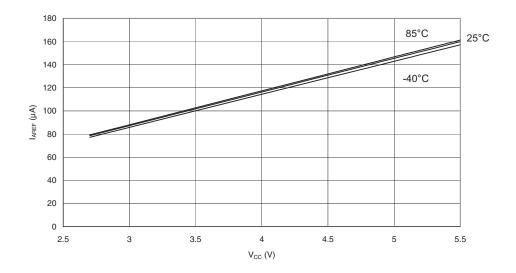

Figure 209. 32khz Tosc Current vs. V<sub>CC</sub> (Watchdog Timer Disabled)

# 4. Reading EEPROM by using ST or STS to set EERE bit triggers unexpected interrupt request.

Reading EEPROM by using the ST or STS command to set the EERE bit in the EECR register triggers an unexpected EEPROM interrupt request.

#### Problem Fix / Workaround

Always use OUT or SBI to set EERE in EECR.

#### ATmega16(L) Rev. • First Analog Comparator conversion may be delayed

- Interrupts may be lost when writing the timer registers in the asynchronous timer

- IDCODE masks data from TDI input

- Reading EEPROM by using ST or STS to set EERE bit triggers unexpected interrupt request

#### 1. First Analog Comparator conversion may be delayed

If the device is powered by a slow rising  $V_{CC}$ , the first Analog Comparator conversion will take longer than expected on some devices.

#### **Problem Fix/Workaround**

When the device has been powered or reset, disable then enable the Analog Comparator before the first conversion.

#### 2. Interrupts may be lost when writing the timer registers in the asynchronous timer

The interrupt will be lost if a timer register that is synchronized to the asynchronous timer clock is written when the asynchronous Timer/Counter register(TCNTx) is 0x00.

#### Problem Fix / Workaround

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register(TCCRx), asynchronous Timer Counter Register(TCNTx), or asynchronous Output Compare Register(OCRx).

#### 3. IDCODE masks data from TDI input

The JTAG instruction IDCODE is not working correctly. Data to succeeding devices are replaced by all-ones during Update-DR.

#### **Problem Fix / Workaround**

- If ATmega16 is the only device in the scan chain, the problem is not visible.

- Select the Device ID Register of the ATmega16 by issuing the IDCODE instruction or by entering the Test-Logic-Reset state of the TAP controller to read out the contents of its Device ID Register and possibly data from succeeding devices of the scan chain. Issue the BYPASS instruction to the ATmega16 while reading the Device ID Registers of preceding devices of the boundary scan chain.

- If the Device IDs of all devices in the boundary scan chain must be captured simultaneously, the ATmega16 must be the fist device in the chain.

# 4. Reading EEPROM by using ST or STS to set EERE bit triggers unexpected interrupt request.

Reading EEPROM by using the ST or STS command to set the EERE bit in the EECR register triggers an unexpected EEPROM interrupt request.

#### Problem Fix / Workaround

Always use OUT or SBI to set EERE in EECR.

н

- 9. Added Table 73, "TWI Bit Rate Prescaler," on page 182 to describe the TWPS bits in the "TWI Status Register TWSR" on page 181.

- 10. Added section "Default Clock Source" on page 25.

- 11. Added note about frequency variation when using an external clock. Note added in "External Clock" on page 31. An extra row and a note added in Table 118 on page 293.

- 12. Various minor TWI corrections.

- 13. Added "Power Consumption" data in "Features" on page 1.

- 14. Added section "EEPROM Write During Power-down Sleep Mode" on page 22.

- 15. Added note about Differential Mode with Auto Triggering in "Prescaling and Conversion Timing" on page 207.

- 16. Added updated "Packaging Information" on page 337.

- Rev. 2466E-10/02 1. Updated "DC Characteristics" on page 291.

- **Rev. 2466D-09/02** 1. Changed all Flash write/erase cycles from 1,000 to 10,000.

- 2. Updated the following tables: Table 4 on page 26, Table 15 on page 38, Table 42 on page 85, Table 45 on page 111, Table 46 on page 111, Table 59 on page 143, Table 67 on page 167, Table 90 on page 235, Table 102 on page 258, "DC Characteristics" on page 291, Table 119 on page 293, Table 121 on page 295, and Table 122 on page 297.

- 3. Updated "Errata" on page 340.

- **Rev. 2466C-03/02** 1. Updated typical EEPROM programming time, Table 1 on page 20.

- 2. Updated typical start-up time in the following tables:

Table 3 on page 25, Table 5 on page 27, Table 6 on page 28, Table 8 on page 29, Table 9 on page 29, and Table 10 on page 29.

- 3. Updated Table 17 on page 43 with typical WDT Time-out.

- 4. Added Some Preliminary Test Limits and Characterization Data.

Removed some of the TBD's in the following tables and pages:

Table 15 on page 38, Table 16 on page 42, Table 116 on page 272 (table removed in document review #D), "Electrical Characteristics" on page 291, Table 119 on page 293, Table 121 on page 295, and Table 122 on page 297.

#### 5. Updated TWI Chapter.

Added the note at the end of the "Bit Rate Generator Unit" on page 178.

- Corrected description of ADSC bit in "ADC Control and Status Register A ADCSRA" on page 219.

- 7. Improved description on how to do a polarity check of the ADC doff results in "ADC Conversion Result" on page 216.