#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 16MHz                                                                   |

| Connectivity               | I²C, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-TQFP                                                                 |

| Supplier Device Package    | 44-TQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega16-16au |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

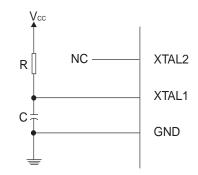

# Low-frequency Crystal Oscillator

To use a 32.768 kHz watch crystal as the clock source for the device, the Low-frequency Crystal Oscillator must be selected by setting the CKSEL Fuses to "1001". The crystal should be connected as shown in Figure 12. By programming the CKOPT Fuse, the user can enable internal capacitors on XTAL1 and XTAL2, thereby removing the need for external capacitors. The internal capacitors have a nominal value of 36 pF.

When this Oscillator is selected, start-up times are determined by the SUT Fuses as shown in Table 6.

| SUT10 | Start-up Time from<br>Power-down and<br>Power-save | Additional Delay<br>from Reset<br>(V <sub>CC</sub> = 5.0V) | Recommended Usage                |  |  |

|-------|----------------------------------------------------|------------------------------------------------------------|----------------------------------|--|--|

| 00    | 1K CK <sup>(1)</sup>                               | 4.1 ms                                                     | Fast rising power or BOD enabled |  |  |

| 01    | 1K CK <sup>(1)</sup>                               | 65 ms                                                      | Slowly rising power              |  |  |

| 10    | 32K CK                                             | 65 ms                                                      | Stable frequency at start-up     |  |  |

| 11    | Reserved                                           |                                                            |                                  |  |  |

Table 6. Start-up Times for the Low-frequency Crystal Oscillator Clock Selection

Note: 1. These options should only be used if frequency stability at start-up is not important for the application.

## External RC Oscillator

For timing insensitive applications, the external RC configuration shown in Figure 13 can be used. The frequency is roughly estimated by the equation f = 1/(3RC). C should be at least 22 pF. By programming the CKOPT Fuse, the user can enable an internal 36 pF capacitor between XTAL1 and GND, thereby removing the need for an external capacitor. For more information on Oscillator operation and details on how to choose R and C, refer to the External RC Oscillator application note.

#### Figure 13. External RC Configuration

The Oscillator can operate in four different modes, each optimized for a specific frequency range. The operating mode is selected by the fuses CKSEL3..0 as shown in Table 7.

Table 7. External RC Oscillator Operating Modes

| CKSEL30 | Frequency Range (MHz) |

|---------|-----------------------|

| 0101    | $0.1 \le 0.9$         |

| 0110    | 0.9 - 3.0             |

| 0111    | 3.0 - 8.0             |

| 1000    | 8.0 - 12.0            |

#### **Unconnected pins**

If some pins are unused, it is recommended to ensure that these pins have a defined level. Even though most of the digital inputs are disabled in the deep sleep modes as described above, floating inputs should be avoided to reduce current consumption in all other modes where the digital inputs are enabled (Reset, Active mode and Idle mode).

The simplest method to ensure a defined level of an unused pin, is to enable the internal pull-up. In this case, the pull-up will be disabled during reset. If low power consumption during reset is important, it is recommended to use an external pull-up or pull-down. Connecting unused pins directly to  $V_{CC}$  or GND is not recommended, since this may cause excessive currents if the pin is accidentally configured as an output.

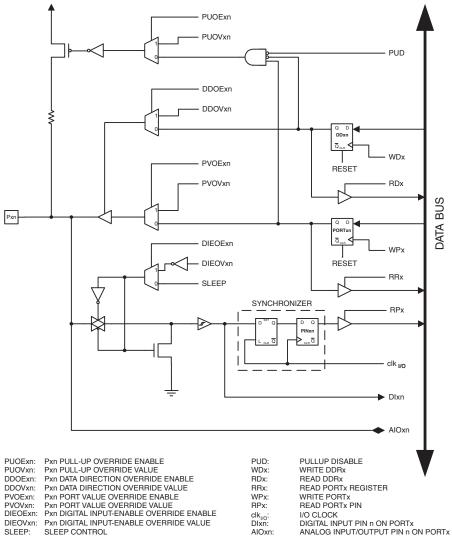

### Alternate Port Functions

Most port pins have alternate functions in addition to being General Digital I/Os. Figure 26 shows how the port pin control signals from the simplified Figure 23 can be overridden by alternate functions. The overriding signals may not be present in all port pins, but the figure serves as a generic description applicable to all port pins in the AVR microcontroller family.

Figure 26. Alternate Port Functions<sup>(1)</sup>

Note: 1. WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clk<sub>I/O</sub>, SLEEP, and PUD are common to all ports. All other signals are unique for each pin.

#### Alternate Functions of Port C

f The Port C pins with alternate functions are shown in Table 28. If the JTAG interface is enabled, the pull-up resistors on pins PC5(TDI), PC3(TMS) and PC2(TCK) will be activated even if a reset occurs.

| Table 28. | Port C Pins Alternate Functions |

|-----------|---------------------------------|

|-----------|---------------------------------|

| Port Pin | Alternate Function                               |

|----------|--------------------------------------------------|

| PC7      | TOSC2 (Timer Oscillator Pin 2)                   |

| PC6      | TOSC1 (Timer Oscillator Pin 1)                   |

| PC5      | TDI (JTAG Test Data In)                          |

| PC4      | TDO (JTAG Test Data Out)                         |

| PC3      | TMS (JTAG Test Mode Select)                      |

| PC2      | TCK (JTAG Test Clock)                            |

| PC1      | SDA (Two-wire Serial Bus Data Input/Output Line) |

| PC0      | SCL (Two-wire Serial Bus Clock Line)             |

The alternate pin configuration is as follows:

#### • TOSC2 - Port C, Bit 7

TOSC2, Timer Oscillator pin 2: When the AS2 bit in ASSR is set (one) to enable asynchronous clocking of Timer/Counter2, pin PC7 is disconnected from the port, and becomes the inverting output of the Oscillator amplifier. In this mode, a Crystal Oscillator is connected to this pin, and the pin can not be used as an I/O pin.

#### • TOSC1 - Port C, Bit 6

TOSC1, Timer Oscillator pin 1: When the AS2 bit in ASSR is set (one) to enable asynchronous clocking of Timer/Counter2, pin PC6 is disconnected from the port, and becomes the input of the inverting Oscillator amplifier. In this mode, a Crystal Oscillator is connected to this pin, and the pin can not be used as an I/O pin.

#### • TDI - Port C, Bit 5

TDI, JTAG Test Data In: Serial input data to be shifted in to the Instruction Register or Data Register (scan chains). When the JTAG interface is enabled, this pin can not be used as an I/O pin.

#### • TDO - Port C, Bit 4

TDO, JTAG Test Data Out: Serial output data from Instruction Register or Data Register. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

The TD0 pin is tri-stated unless TAP states that shifts out data are entered.

#### • TMS – Port C, Bit 3

TMS, JTAG Test Mode Select: This pin is used for navigating through the TAP-controller state machine. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

#### • TCK – Port C, Bit 2

TCK, JTAG Test Clock: JTAG operation is synchronous to TCK. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

# External Interrupts

The External Interrupts are triggered by the INT0, INT1, and INT2 pins. Observe that, if enabled, the interrupts will trigger even if the INT0..2 pins are configured as outputs. This feature provides a way of generating a software interrupt. The external interrupts can be triggered by a falling or rising edge or a low level (INT2 is only an edge triggered interrupt). This is set up as indicated in the specification for the MCU Control Register – MCUCR – and MCU Control and Status Register – MCUCSR. When the external interrupt is enabled and is configured as level triggered (only INT0/INT1), the interrupt will trigger as long as the pin is held low. Note that recognition of falling or rising edge interrupts on INT0 and INT1 requires the presence of an I/O clock, described in "Clock Systems and their Distribution" on page 24. Low level interrupts on INT0/INT1 and the edge interrupt on INT2 are detected asynchronously. This implies that these interrupts can be used for waking the part also from sleep modes other than Idle mode. The I/O clock is halted in all sleep modes except Idle mode.

Note that if a level triggered interrupt is used for wake-up from Power-down mode, the changed level must be held for some time to wake up the MCU. This makes the MCU less sensitive to noise. The changed level is sampled twice by the Watchdog Oscillator clock. The period of the Watchdog Oscillator is 1 µs (nominal) at 5.0V and 25°C. The frequency of the Watchdog Oscillator is voltage dependent as shown in "Electrical Characteristics" on page 291. The MCU will wake up if the input has the required level during this sampling or if it is held until the end of the start-up time. The start-up time is defined by the SUT Fuses as described in "System Clock and Clock Options" on page 24. If the level is sampled twice by the Watchdog Oscillator clock but disappears before the end of the start-up time, the MCU will still wake up, but no interrupt will be generated. The required level must be held long enough for the MCU to complete the wake up to trigger the level interrupt.

**MCU Control Register** The MCU Control Register contains control bits for interrupt sense control and general MCU functions.

| Bit           | 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     |       |

|---------------|-----|-----|-----|-----|-------|-------|-------|-------|-------|

|               | SM2 | SE  | SM1 | SM0 | ISC11 | ISC10 | ISC01 | ISC00 | MCUCR |

| Read/Write    | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   | -     |

| Initial Value | 0   | 0   | 0   | 0   | 0     | 0     | 0     | 0     |       |

#### • Bit 3, 2 – ISC11, ISC10: Interrupt Sense Control 1 Bit 1 and Bit 0

The External Interrupt 1 is activated by the external pin INT1 if the SREG I-bit and the corresponding interrupt mask in the GICR are set. The level and edges on the external INT1 pin that activate the interrupt are defined in Table 34. The value on the INT1 pin is sampled before detecting edges. If edge or toggle interrupt is selected, pulses that last longer than one clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt.

| Table 34. | Interrupt 1 | Sense | Control |

|-----------|-------------|-------|---------|

|-----------|-------------|-------|---------|

| ISC11 | ISC10 | Description                                                |

|-------|-------|------------------------------------------------------------|

| 0     | 0     | The low level of INT1 generates an interrupt request.      |

| 0     | 1     | Any logical change on INT1 generates an interrupt request. |

| 1     | 0     | The falling edge of INT1 generates an interrupt request.   |

| 1     | 1     | The rising edge of INT1 generates an interrupt request.    |

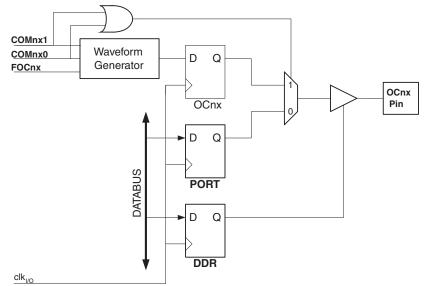

# Compare Match Output Unit

The Compare Output mode (COM1x1:0) bits have two functions. The Waveform Generator uses the COM1x1:0 bits for defining the Output Compare (OC1x) state at the next compare match. Secondly the COM1x1:0 bits control the OC1x pin output source. Figure 44 shows a simplified schematic of the logic affected by the COM1x1:0 bit setting. The I/O Registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O Port Control Registers (DDR and PORT) that are affected by the COM1x1:0 bits are shown. When referring to the OC1x state, the reference is for the internal OC1x Register, not the OC1x pin. If a System Reset occur, the OC1x Register is reset to "0".

#### Figure 44. Compare Match Output Unit, Schematic

The general I/O port function is overridden by the Output Compare (OC1x) from the Waveform Generator if either of the COM1x1:0 bits are set. However, the OC1x pin direction (input or output) is still controlled by the *Data Direction Register* (DDR) for the port pin. The Data Direction Register bit for the OC1x pin (DDR\_OC1x) must be set as output before the OC1x value is visible on the pin. The port override function is generally independent of the Waveform Generation mode, but there are some exceptions. Refer to Table 44, Table 45 and Table 46 for details.

The design of the output compare pin logic allows initialization of the OC1x state before the output is enabled. Note that some COM1x1:0 bit settings are reserved for certain modes of operation. See "16-bit Timer/Counter Register Description" on page 110.

The COM1x1:0 bits have no effect on the Input Capture unit.

Compare Output Mode<br/>and WaveformThe Waveform Generator uses the COM1x1:0 bits differently in normal, CTC, and PWM modes.<br/>For all modes, setting the COM1x1:0 = 0 tells the Waveform Generator that no action on the<br/>OC1x Register is to be performed on the next compare match. For compare output actions in the<br/>non-PWM modes refer to Table 44 on page 110. For fast PWM mode refer to Table 45 on page<br/>111, and for phase correct and phase and frequency correct PWM refer to Table 46 on page<br/>111.

A change of the COM1x1:0 bits state will have effect at the first compare match after the bits are written. For non-PWM modes, the action can be forced to have immediate effect by using the FOC1x strobe bits.

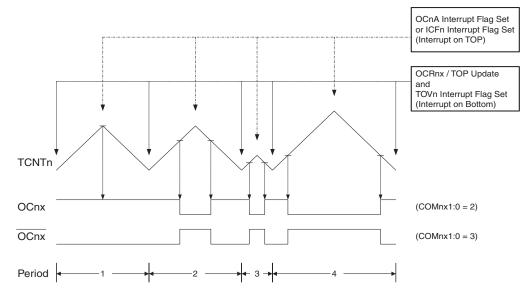

Figure 48. Phase and Frequency Correct PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOV1) is set at the same timer clock cycle as the OCR1x Registers are updated with the double buffer value (at BOTTOM). When either OCR1A or ICR1 is used for defining the TOP value, the OC1A or ICF1 Flag set when TCNT1 has reached TOP. The Interrupt Flags can then be used to generate an interrupt each time the counter reaches the TOP or BOTTOM value.

When changing the TOP value the program must ensure that the new TOP value is higher or equal to the value of all of the Compare Registers. If the TOP value is lower than any of the Compare Registers, a compare match will never occur between the TCNT1 and the OCR1x.

As Figure 48 shows the output generated is, in contrast to the phase correct mode, symmetrical in all periods. Since the OCR1x Registers are updated at BOTTOM, the length of the rising and the falling slopes will always be equal. This gives symmetrical output pulses and is therefore frequency correct.

Using the ICR1 Register for defining TOP works well when using fixed TOP values. By using ICR1, the OCR1A Register is free to be used for generating a PWM output on OC1A. However, if the base PWM frequency is actively changed by changing the TOP value, using the OCR1A as TOP is clearly a better choice due to its double buffer feature.

In phase and frequency correct PWM mode, the compare units allow generation of PWM waveforms on the OC1x pins. Setting the COM1x1:0 bits to 2 will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM1x1:0 to 3 (See Table on page 111). The actual OC1x value will only be visible on the port pin if the data direction for the port pin is set as output (DDR\_OC1x). The PWM waveform is generated by setting (or clearing) the OC1x Register at the compare match between OCR1x and TCNT1 when the counter increments, and clearing (or setting) the OC1x Register at compare match between OCR1x and TCNT1 when the counter decrements. The PWM frequency for the output when using phase and frequency correct PWM can be calculated by the following equation:

$$f_{OCnxPFCPWM} = \frac{f_{clk\_l/O}}{2 \cdot N \cdot TOP}$$

The N variable represents the prescaler divider (1, 8, 64, 256, or 1024).

The extreme values for the OCR1x Register represents special cases when generating a PWM waveform output in the phase correct PWM mode. If the OCR1x is set equal to BOTTOM the

output will be continuously low and if set equal to TOP the output will be set to high for non-inverted PWM mode. For inverted PWM the output will have the opposite logic values. If OCR1A is used to define the TOP value (WGM13:0 = 9) and COM1A1:0 = 1, the OC1A output will toggle with a 50% duty cycle.

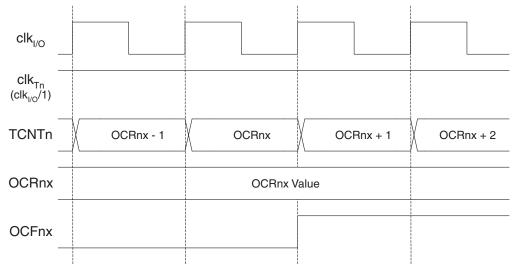

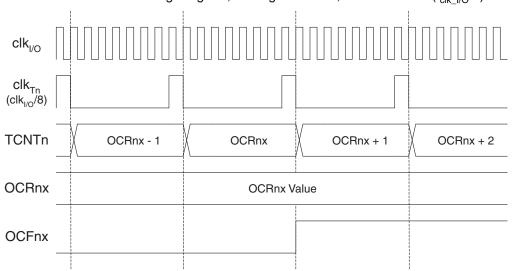

# Timer/Counter Timing Diagrams

The Timer/Counter is a synchronous design and the timer clock ( $clk_{T1}$ ) is therefore shown as a clock enable signal in the following figures. The figures include information on when Interrupt Flags are set, and when the OCR1x Register is updated with the OCR1x buffer value (only for modes utilizing double buffering). Figure 49 shows a timing diagram for the setting of OCF1x.

Figure 49. Timer/Counter Timing Diagram, Setting of OCF1x, No Prescaling

Figure 50 shows the same timing data, but with the prescaler enabled.

Figure 50. Timer/Counter Timing Diagram, Setting of OCF1x, with Prescaler ( $f_{clk\_I/O}$ /8)

Figure 51 shows the count sequence close to TOP in various modes. When using phase and frequency correct PWM mode the OCR1x Register is updated at BOTTOM. The timing diagrams

A FOC1A/FOC1B strobe will not generate any interrupt nor will it clear the timer in Clear Timer on Compare match (CTC) mode using OCR1A as TOP.

The FOC1A/FOC1B bits are always read as zero.

#### • Bit 1:0 - WGM11:0: Waveform Generation Mode

Combined with the WGM13:2 bits found in the TCCR1B Register, these bits control the counting sequence of the counter, the source for maximum (TOP) counter value, and what type of wave-form generation to be used, see Table 47. Modes of operation supported by the Timer/Counter unit are: Normal mode (counter), Clear Timer on Compare match (CTC) mode, and three types of Pulse Width Modulation (PWM) modes. (See "Modes of Operation" on page 101.)

| Mode | WGM13 | WGM12<br>(CTC1) | WGM11<br>(PWM11) | WGM10<br>(PWM10) | Timer/Counter Mode of Operation  | ТОР    | Update of OCR1X | TOV1 Flag Set<br>on |

|------|-------|-----------------|------------------|------------------|----------------------------------|--------|-----------------|---------------------|

| 0    | 0     | 0               | 0                | 0                | Normal                           | 0xFFFF | Immediate       | MAX                 |

| 1    | 0     | 0               | 0                | 1                | PWM, Phase Correct, 8-bit        | 0x00FF | TOP             | воттом              |

| 2    | 0     | 0               | 1                | 0                | PWM, Phase Correct, 9-bit        | 0x01FF | TOP             | BOTTOM              |

| 3    | 0     | 0               | 1                | 1                | PWM, Phase Correct, 10-bit       | 0x03FF | TOP             | BOTTOM              |

| 4    | 0     | 1               | 0                | 0                | СТС                              | OCR1A  | Immediate       | MAX                 |

| 5    | 0     | 1               | 0                | 1                | Fast PWM, 8-bit                  | 0x00FF | BOTTOM          | TOP                 |

| 6    | 0     | 1               | 1                | 0                | Fast PWM, 9-bit                  | 0x01FF | BOTTOM          | TOP                 |

| 7    | 0     | 1               | 1                | 1                | Fast PWM, 10-bit                 | 0x03FF | BOTTOM          | TOP                 |

| 8    | 1     | 0               | 0                | 0                | PWM, Phase and Frequency Correct | ICR1   | BOTTOM          | BOTTOM              |

| 9    | 1     | 0               | 0                | 1                | PWM, Phase and Frequency Correct | OCR1A  | BOTTOM          | воттом              |

| 10   | 1     | 0               | 1                | 0                | PWM, Phase Correct               | ICR1   | TOP             | воттом              |

| 11   | 1     | 0               | 1                | 1                | PWM, Phase Correct               | OCR1A  | TOP             | BOTTOM              |

| 12   | 1     | 1               | 0                | 0                | СТС                              | ICR1   | Immediate       | MAX                 |

| 13   | 1     | 1               | 0                | 1                | Reserved                         | _      | -               | _                   |

| 14   | 1     | 1               | 1                | 0                | Fast PWM                         | ICR1   | BOTTOM          | TOP                 |

| 15   | 1     | 1               | 1                | 1                | Fast PWM                         | OCR1A  | BOTTOM          | TOP                 |

Table 47.

Waveform Generation Mode Bit Description<sup>(1)</sup>

Note: 1. The CTC1 and PWM11:0 bit definition names are obsolete. Use the WGM12:0 definitions. However, the functionality and location of these bits are compatible with previous versions of the timer.

#### • Bit 0 – TXB8: Transmit Data Bit 8

TXB8 is the ninth data bit in the character to be transmitted when operating with serial frames with nine data bits. Must be written before writing the low bits to UDR.

USART Control and Status Register C – UCSRC

| Bit           | 7     | 6     | 5    | 4    | 3    | 2     | 1     | 0     |       |

|---------------|-------|-------|------|------|------|-------|-------|-------|-------|

|               | URSEL | UMSEL | UPM1 | UPM0 | USBS | UCSZ1 | UCSZ0 | UCPOL | UCSRC |

| Read/Write    | R/W   | R/W   | R/W  | R/W  | R/W  | R/W   | R/W   | R/W   |       |

| Initial Value | 1     | 0     | 0    | 0    | 0    | 1     | 1     | 0     |       |

The UCSRC Register shares the same I/O location as the UBRRH Register. See the "Accessing UBRRH/ UCSRC Registers" on page 162 section which describes how to access this register.

#### • Bit 7 – URSEL: Register Select

This bit selects between accessing the UCSRC or the UBRRH Register. It is read as one when reading UCSRC. The URSEL must be one when writing the UCSRC.

#### • Bit 6 - UMSEL: USART Mode Select

This bit selects between Asynchronous and Synchronous mode of operation.

#### Table 63. UMSEL Bit Settings

| UMSEL | Mode                   |  |  |  |  |

|-------|------------------------|--|--|--|--|

| 0     | Asynchronous Operation |  |  |  |  |

| 1     | Synchronous Operation  |  |  |  |  |

#### • Bit 5:4 - UPM1:0: Parity Mode

These bits enable and set type of parity generation and check. If enabled, the transmitter will automatically generate and send the parity of the transmitted data bits within each frame. The Receiver will generate a parity value for the incoming data and compare it to the UPMO setting. If a mismatch is detected, the PE Flag in UCSRA will be set.

#### Table 64. UPM Bits Settings

| UPM1 | UPM0 | Parity Mode          |

|------|------|----------------------|

| 0    | 0    | Disabled             |

| 0    | 1    | Reserved             |

| 1    | 0    | Enabled, Even Parity |

| 1    | 1    | Enabled, Odd Parity  |

#### • Bit 3 – USBS: Stop Bit Select

This bit selects the number of Stop Bits to be inserted by the Transmitter. The Receiver ignores this setting.

Table 65.

USBS Bit Settings

| USBS | Stop Bit(s) |

|------|-------------|

| 0    | 1-bit       |

| 1    | 2-bit       |

#### • Bit 11:0 – UBRR11:0: USART Baud Rate Register

This is a 12-bit register which contains the USART baud rate. The UBRRH contains the four most significant bits, and the UBRRL contains the 8 least significant bits of the USART baud rate. Ongoing transmissions by the transmitter and receiver will be corrupted if the baud rate is changed. Writing UBRRL will trigger an immediate update of the baud rate prescaler.

**Examples of Baud Rate Setting** For standard crystal and resonator frequencies, the most commonly used baud rates for asynchronous operation can be generated by using the UBRR settings in Table 68. UBRR values which yield an actual baud rate differing less than 0.5% from the target baud rate, are bold in the table. Higher error ratings are acceptable, but the receiver will have less noise resistance when the error ratings are high, especially for large serial frames (see "Asynchronous Operational Range" on page 159). The error values are calculated using the following equation:

$$Error[\%] = \left(\frac{BaudRate_{Closest Match}}{BaudRate} - 1\right) \bullet 100\%$$

| Table 68. Examples of UBRR Settings for Commonly Used Oscillator Frequencies | Table 68. | Examples of UBRR | Settings for Commonl | v Used Oscillator Frequencies |

|------------------------------------------------------------------------------|-----------|------------------|----------------------|-------------------------------|

|------------------------------------------------------------------------------|-----------|------------------|----------------------|-------------------------------|

|                    |      | f <sub>osc</sub> = 1.0 | 000 MHz |        |       | f <sub>osc</sub> = 1.8 | 432 MHz |       |      | $f_{osc} = 2.0$ | 000 MHz |       |

|--------------------|------|------------------------|---------|--------|-------|------------------------|---------|-------|------|-----------------|---------|-------|

| Baud<br>Rate       | U2X  | ζ = 0                  | U2X     | ζ = 1  | U2X   | ( = 0                  | U2X     | ζ = 1 | U2X  | ζ = 0           | U2X     | ( = 1 |

| (bps)              | UBRR | Error                  | UBRR    | Error  | UBRR  | Error                  | UBRR    | Error | UBRR | Error           | UBRR    | Error |

| 2400               | 25   | 0.2%                   | 51      | 0.2%   | 47    | 0.0%                   | 95      | 0.0%  | 51   | 0.2%            | 103     | 0.2%  |

| 4800               | 12   | 0.2%                   | 25      | 0.2%   | 23    | 0.0%                   | 47      | 0.0%  | 25   | 0.2%            | 51      | 0.2%  |

| 9600               | 6    | -7.0%                  | 12      | 0.2%   | 11    | 0.0%                   | 23      | 0.0%  | 12   | 0.2%            | 25      | 0.2%  |

| 14.4k              | 3    | 8.5%                   | 8       | -3.5%  | 7     | 0.0%                   | 15      | 0.0%  | 8    | -3.5%           | 16      | 2.1%  |

| 19.2k              | 2    | 8.5%                   | 6       | -7.0%  | 5     | 0.0%                   | 11      | 0.0%  | 6    | -7.0%           | 12      | 0.2%  |

| 28.8k              | 1    | 8.5%                   | 3       | 8.5%   | 3     | 0.0%                   | 7       | 0.0%  | 3    | 8.5%            | 8       | -3.5% |

| 38.4k              | 1    | -18.6%                 | 2       | 8.5%   | 2     | 0.0%                   | 5       | 0.0%  | 2    | 8.5%            | 6       | -7.0% |

| 57.6k              | 0    | 8.5%                   | 1       | 8.5%   | 1     | 0.0%                   | 3       | 0.0%  | 1    | 8.5%            | 3       | 8.5%  |

| 76.8k              | _    | _                      | 1       | -18.6% | 1     | -25.0%                 | 2       | 0.0%  | 1    | -18.6%          | 2       | 8.5%  |

| 115.2k             | _    | _                      | 0       | 8.5%   | 0     | 0.0%                   | 1       | 0.0%  | 0    | 8.5%            | 1       | 8.5%  |

| 230.4k             | _    | _                      | _       | _      | _     | _                      | 0       | 0.0%  | _    | _               | _       | _     |

| 250k               | _    | _                      | _       | _      | _     | _                      | _       | _     | _    | _               | 0       | 0.0%  |

| Max <sup>(1)</sup> | 62.5 | Kbps                   | 125     | Kbps   | 115.2 | Kbps                   | 230.4   | Kbps  | 125  | Kbps            | 250     | Kbps  |

1. UBRR = 0, Error = 0.0%

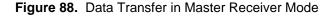

is detected, and then generates a new START condition to claim the bus Master status. TWSTA must be cleared by software when the START condition has been transmitted.

#### • Bit 4 – TWSTO: TWI STOP Condition Bit

Writing the TWSTO bit to one in Master mode will generate a STOP condition on the Two-wire Serial Bus. When the STOP condition is executed on the bus, the TWSTO bit is cleared automatically. In Slave mode, setting the TWSTO bit can be used to recover from an error condition. This will not generate a STOP condition, but the TWI returns to a well-defined unaddressed Slave mode and releases the SCL and SDA lines to a high impedance state.

#### Bit 3 – TWWC: TWI Write Collision Flag

The TWWC bit is set when attempting to write to the TWI Data Register – TWDR when TWINT is low. This flag is cleared by writing the TWDR Register when TWINT is high.

#### Bit 2 – TWEN: TWI Enable Bit

The TWEN bit enables TWI operation and activates the TWI interface. When TWEN is written to one, the TWI takes control over the I/O pins connected to the SCL and SDA pins, enabling the slew-rate limiters and spike filters. If this bit is written to zero, the TWI is switched off and all TWI transmissions are terminated, regardless of any ongoing operation.

#### • Bit 1 – Res: Reserved Bit

This bit is a reserved bit and will always read as zero.

#### • Bit 0 – TWIE: TWI Interrupt Enable

When this bit is written to one, and the I-bit in SREG is set, the TWI interrupt request will be activated for as long as the TWINT Flag is high.

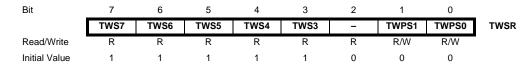

#### TWI Status Register – TWSR

#### Bits 7..3 – TWS: TWI Status

These five bits reflect the status of the TWI logic and the Two-wire Serial Bus. The different status codes are described later in this section. Note that the value read from TWSR contains both the 5-bit status value and the 2-bit prescaler value. The application designer should mask the prescaler bits to zero when checking the Status bits. This makes status checking independent of prescaler setting. This approach is used in this datasheet, unless otherwise noted.

#### Bit 2 – Res: Reserved Bit

This bit is reserved and will always read as zero.

A START condition is sent by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 1     | Х    | 1     | 0     | Х    | 1    | 0 | Х    |

TWEN must be written to one to enable the Two-wire Serial Interface, TWSTA must be written to one to transmit a START condition and TWINT must be set to clear the TWINT Flag. The TWI will then test the Two-wire Serial Bus and generate a START condition as soon as the bus becomes free. After a START condition has been transmitted, the TWINT Flag is set by hardware, and the status code in TWSR will be \$08 (See Table 74). In order to enter MR mode, SLA+R must be transmitted. This is done by writing SLA+R to TWDR. Thereafter the TWINT bit should be cleared (by writing it to one) to continue the transfer. This is accomplished by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 1     | Х    | 0     | 0     | Х    | 1    | 0 | Х    |

When SLA+R have been transmitted and an acknowledgement bit has been received, TWINT is set again and a number of status codes in TWSR are possible. Possible status codes in Master mode are \$38, \$40, or \$48. The appropriate action to be taken for each of these status codes is detailed in Table 75. Received data can be read from the TWDR Register when the TWINT Flag is set high by hardware. This scheme is repeated until the last byte has been received. After the last byte has been received, the MR should inform the ST by sending a NACK after the last received data byte. The transfer is ended by generating a STOP condition or a repeated START condition. A STOP condition is generated by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 1     | Х    | 0     | 1     | Х    | 1    | 0 | Х    |

A REPEATED START condition is generated by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 1     | Х    | 1     | 0     | Х    | 1    | 0 | Х    |

After a repeated START condition (state \$10) the Two-wire Serial Interface can access the same Slave again, or a new Slave without transmitting a STOP condition. Repeated START enables the Master to switch between Slaves, Master Transmitter mode and Master Receiver mode without losing control over the bus.

Table 75. Status Codes for Master Receiver Mode

| Status Code              |                                                                 | Applicat     | ion Softw | are Resp | onse  |      |                                   |

|--------------------------|-----------------------------------------------------------------|--------------|-----------|----------|-------|------|-----------------------------------|

| (TWSR)<br>Prescaler Bits | Status of the Two-wire Serial<br>Bus and Two-wire Serial Inter- |              |           | To T     | WCR   |      |                                   |

| are 0                    | face Hardware                                                   | To/from TWDR | STA       | STO      | TWINT | TWEA | Next Action Taken by TWI Hardware |

The upper seven bits are the address to which the Two-wire Serial Interface will respond when addressed by a Master. If the LSB is set, the TWI will respond to the general call address (\$00), otherwise it will ignore the general call address.

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 0     | 1    | 0     | 0     | 0    | 1    | 0 | Х    |

TWEN must be written to one to enable the TWI. The TWEA bit must be written to one to enable the acknowledgement of the device's own Slave address or the general call address. TWSTA and TWSTO must be written to zero.

When TWAR and TWCR have been initialized, the TWI waits until it is addressed by its own Slave address (or the general call address if enabled) followed by the data direction bit. If the direction bit is "1" (read), the TWI will operate in ST mode, otherwise SR mode is entered. After its own Slave address and the write bit have been received, the TWINT Flag is set and a valid status code can be read from TWSR. The status code is used to determine the appropriate software action. The appropriate action to be taken for each status code is detailed in Table 77. The Slave Transmitter mode may also be entered if arbitration is lost while the TWI is in the Master mode (see state \$B0).

If the TWEA bit is written to zero during a transfer, the TWI will transmit the last byte of the transfer. State \$C0 or state \$C8 will be entered, depending on whether the Master Receiver transmits a NACK or ACK after the final byte. The TWI is switched to the not addressed Slave mode, and will ignore the Master if it continues the transfer. Thus the Master Receiver receives all "1" as serial data. State \$C8 is entered if the Master demands additional data bytes (by transmitting ACK), even though the Slave has transmitted the last byte (TWEA zero and expecting NACK from the Master).

While TWEA is zero, the TWI does not respond to its own Slave address. However, the Twowire Serial Bus is still monitored and address recognition may resume at any time by setting TWEA. This implies that the TWEA bit may be used to temporarily isolate the TWI from the Twowire Serial Bus.

In all sleep modes other than Idle mode, the clock system to the TWI is turned off. If the TWEA bit is set, the interface can still acknowledge its own Slave address or the general call address by using the Two-wire Serial Bus clock as a clock source. The part will then wake up from sleep and the TWI will hold the SCL clock will low during the wake up and until the TWINT Flag is cleared (by writing it to one). Further data transmission will be carried out as normal, with the AVR clocks running as normal. Observe that if the AVR is set up with a long start-up time, the SCL line may be held low for a long time, blocking other data transmissions.

Note that the Two-wire Serial Interface Data Register – TWDR does not reflect the last byte present on the bus when waking up from these sleep modes.

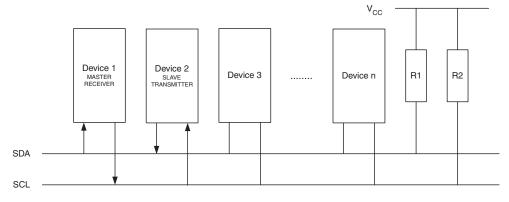

# Analog Comparator

The Analog Comparator compares the input values on the positive pin AIN0 and negative pin AIN1. When the voltage on the positive pin AIN0 is higher than the voltage on the negative pin AIN1, the Analog Comparator Output, ACO, is set. The comparator's output can be set to trigger the Timer/Counter1 Input Capture function. In addition, the comparator can trigger a separate interrupt, exclusive to the Analog Comparator. The user can select Interrupt triggering on comparator output rise, fall or toggle. A block diagram of the comparator and its surrounding logic is shown in Figure 97.

Notes: 1. See Table 80 on page 203.

2. Refer to Figure 1 on page 2 and Table 25 on page 58 for Analog Comparator pin placement.

#### Special Function IO Register – SFIOR

| Bit           | 7     | 6     | 5     | 4 | 3    | 2   | 1    | 0     |       |

|---------------|-------|-------|-------|---|------|-----|------|-------|-------|

|               | ADTS2 | ADTS1 | ADTS0 | - | ACME | PUD | PSR2 | PSR10 | SFIOR |

| Read/Write    | R/W   | R/W   | R/W   | R | R/W  | R/W | R/W  | R/W   |       |

| Initial Value | 0     | 0     | 0     | 0 | 0    | 0   | 0    | 0     |       |

#### • Bit 3 – ACME: Analog Comparator Multiplexer Enable

When this bit is written logic one and the ADC is switched off (ADEN in ADCSRA is zero), the ADC multiplexer selects the negative input to the Analog Comparator. When this bit is written logic zero, AIN1 is applied to the negative input of the Analog Comparator. For a detailed description of this bit, see "Analog Comparator Multiplexed Input" on page 203.

**Boundary-scan Chain** The Boundary-scan Chain has the capability of driving and observing the logic levels on the digital I/O pins, as well as the boundary between digital and analog logic for analog circuitry having Off-chip connections.

See "Boundary-scan Chain" on page 232 for a complete description.

**Boundary-scan Specific JTAG Instructions** The instruction register is 4-bit wide, supporting up to 16 instructions. Listed below are the JTAG instructions useful for Boundary-scan operation. Note that the optional HIGHZ instruction is not implemented, but all outputs with tri-state capability can be set in high-impedant state by using the AVR\_RESET instruction, since the initial state for all port pins is tri-state.

As a definition in this datasheet, the LSB is shifted in and out first for all Shift Registers.

The OPCODE for each instruction is shown behind the instruction name in hex format. The text describes which Data Register is selected as path between TDI and TDO for each instruction.

**EXTEST; \$0** Mandatory JTAG instruction for selecting the Boundary-scan Chain as Data Register for testing circuitry external to the AVR package. For port-pins, Pull-up Disable, Output Control, Output Data, and Input Data are all accessible in the scan chain. For Analog circuits having Off-chip connections, the interface between the analog and the digital logic is in the scan chain. The contents of the latched outputs of the Boundary-scan chain is driven out as soon as the JTAG IR-register is loaded with the EXTEST instruction.

The active states are:

- Capture-DR: Data on the external pins are sampled into the Boundary-scan Chain.

- Shift-DR: The Internal Scan Chain is shifted by the TCK input.

- Update-DR: Data from the scan chain is applied to output pins.

- **IDCODE; \$1** Optional JTAG instruction selecting the 32-bit ID-register as Data Register. The ID-register consists of a version number, a device number and the manufacturer code chosen by JEDEC. This is the default instruction after power-up.

The active states are:

- Capture-DR: Data in the IDCODE-register is sampled into the Boundary-scan Chain.

- Shift-DR: The IDCODE scan chain is shifted by the TCK input.

# SAMPLE\_PRELOAD; Mandatory JTAG instruction for pre-loading the output latches and talking a snap-shot of the input/output pins without affecting the system operation. However, the output latches are not connected to the pins. The Boundary-scan Chain is selected as Data Register.

The active states are:

- Capture-DR: Data on the external pins are sampled into the Boundary-scan Chain.

- Shift-DR: The Boundary-scan Chain is shifted by the TCK input.

- Update-DR: Data from the Boundary-scan Chain is applied to the output latches. However, the output latches are not connected to the pins.

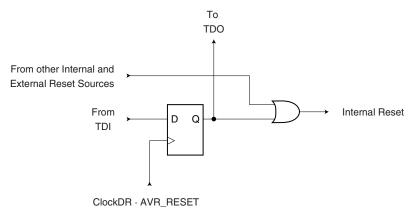

AVR\_RESET; \$C The AVR specific public JTAG instruction for forcing the AVR device into the Reset mode or releasing the JTAG Reset source. The TAP controller is not reset by this instruction. The one bit Reset Register is selected as Data Register. Note that the reset will be active as long as there is a logic 'one' in the Reset Chain. The output from this chain is not latched.

The active states are:

• Shift-DR: The Reset Register is shifted by the TCK input.

**BYPASS; \$F** Mandatory JTAG instruction selecting the Bypass Register for Data Register.

The active states are:

- Capture-DR: Loads a logic "0" into the Bypass Register.

- Shift-DR: The Bypass Register cell between TDI and TDO is shifted.

Boundary-scan Related Register in I/O Memory

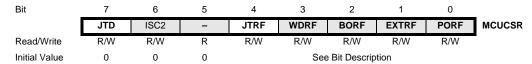

MCU Control and Status Register – MCUCSR The MCU Control and Status Register contains control bits for general MCU functions, and provides information on which reset source caused an MCU Reset.

#### Bit 7 – JTD: JTAG Interface Disable

When this bit is zero, the JTAG interface is enabled if the JTAGEN Fuse is programmed. If this bit is one, the JTAG interface is disabled. In order to avoid unintentional disabling or enabling of the JTAG interface, a timed sequence must be followed when changing this bit: The application software must write this bit to the desired value twice within four cycles to change its value.

If the JTAG interface is left unconnected to other JTAG circuitry, the JTD bit should be set to one. The reason for this is to avoid static current at the TDO pin in the JTAG interface.

#### Bit 4 – JTRF: JTAG Reset Flag

This bit is set if a reset is being caused by a logic one in the JTAG Reset Register selected by the JTAG instruction AVR\_RESET. This bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

#### Table 98. Boot Reset Fuse<sup>(1)</sup>

| BOOTRST | Reset Address                                                |

|---------|--------------------------------------------------------------|

| 1       | Reset Vector = Application reset (address \$0000)            |

| 0       | Reset Vector = Boot Loader reset (see Table 100 on page 257) |

Note: 1. "1" means unprogrammed, "0" means programmed

The Store Program Memory Control Register contains the control bits needed to control the Boot Loader operations.

Bit 7 6 3 2 0 5 4 SPMIE RWWSB RWWSRE BLBSET PGWRT PGERS SPMEN SPMCR -Read/Write R/W R R R/W R/W R/W R/W R/W Initial value 0 0 0 0 0 0 0 0

#### • Bit 7 – SPMIE: SPM Interrupt Enable

When the SPMIE bit is written to one, and the I-bit in the Status Register is set (one), the SPM ready interrupt will be enabled. The SPM ready Interrupt will be executed as long as the SPMEN bit in the SPMCR Register is cleared.

#### • Bit 6 - RWWSB: Read-While-Write Section Busy

When a self-programming (Page Erase or Page Write) operation to the RWW section is initiated, the RWWSB will be set (one) by hardware. When the RWWSB bit is set, the RWW section cannot be accessed. The RWWSB bit will be cleared if the RWWSRE bit is written to one after a Self-Programming operation is completed. Alternatively the RWWSB bit will automatically be cleared if a page load operation is initiated.

#### • Bit 5 – Res: Reserved Bit

This bit is a reserved bit in the ATmega16 and always read as zero.

#### • Bit 4 – RWWSRE: Read-While-Write Section Read Enable

When programming (Page Erase or Page Write) to the RWW section, the RWW section is blocked for reading (the RWWSB will be set by hardware). To re-enable the RWW section, the user software must wait until the programming is completed (SPMEN will be cleared). Then, if the RWWSRE bit is written to one at the same time as SPMEN, the next SPM instruction within four clock cycles re-enables the RWW section. The RWW section cannot be re-enabled while the Flash is busy with a page erase or a page write (SPMEN is set). If the RWWSRE bit is written while the Flash is being loaded, the Flash load operation will abort and the data loaded will be lost.

#### Bit 3 – BLBSET: Boot Lock Bit Set

If this bit is written to one at the same time as SPMEN, the next SPM instruction within four clock cycles sets Boot Lock bits, according to the data in R0. The data in R1 and the address in the Z-pointer are ignored. The BLBSET bit will automatically be cleared upon completion of the Lock bit set, or if no SPM instruction is executed within four clock cycles.

An LPM instruction within three cycles after BLBSET and SPMEN are set in the SPMCR Register, will read either the Lock bits or the Fuse bits (depending on Z0 in the Z-pointer) into the destination register. See "Reading the Fuse and Lock Bits from Software" on page 254 for details.

Store Program Memory Control Register – SPMCR

5] The sum of all IOH, for ports D3 - D7, should not exceed 100 mA.

6] The sum of all IOH, for ports C0 - C7, should not exceed 100 mA.If IOH exceeds the test condition, VOH may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition.

5. Minimum  $V_{CC}$  for Power-down is 2.5V.

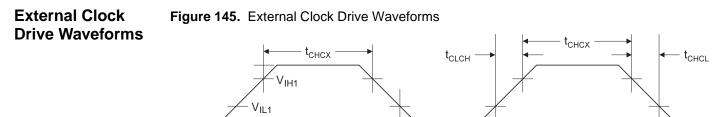

#### External Clock Drive

Table 118. External Clock Drive<sup>(1)</sup>

|                     |                                                         | V <sub>CC</sub> = 2. | 7V to 5.5V | V <sub>CC</sub> = 4.5 | 5V to 5.5V |       |

|---------------------|---------------------------------------------------------|----------------------|------------|-----------------------|------------|-------|

| Symbol              | Parameter                                               | Min                  | Max        | Min                   | Max        | Units |

| 1/t <sub>CLCL</sub> | Oscillator Frequency                                    | 0                    | 8          | 0                     | 16         | MHz   |

| t <sub>CLCL</sub>   | Clock Period                                            | 125                  |            | 62.5                  |            |       |

| t <sub>CHCX</sub>   | High Time                                               | 50                   |            | 25                    |            | ns    |

| t <sub>CLCX</sub>   | Low Time                                                | 50                   |            | 25                    |            |       |

| t <sub>CLCH</sub>   | Rise Time                                               |                      | 1.6        |                       | 0.5        |       |

| t <sub>CHCL</sub>   | Fall Time                                               |                      | 1.6        |                       | 0.5        | μS    |

| $\Delta t_{CLCL}$   | Change in period from<br>one clock cycle to the<br>next |                      | 2          |                       | 2          | %     |

t<sub>CLCX</sub>

t<sub>CLCL</sub>

Note: 1. Refer to "External Clock" on page 31 for details.

| Table 119. Ex | ternal RC Oscillator, | <b>Typical Frequencies</b> | $(V_{CC} = 5)$ |

|---------------|-----------------------|----------------------------|----------------|

|---------------|-----------------------|----------------------------|----------------|

| <b>R [k</b> Ω] <sup>(1)</sup> | C [pF] | <b>f</b> <sup>(2)</sup> |

|-------------------------------|--------|-------------------------|

| 33                            | 22     | 650 kHz                 |

| 10                            | 22     | 2.0 MHz                 |

Notes: 1. R should be in the range  $3 k\Omega - 100 k\Omega$ , and C should be at least 20 pF. 2. The frequency will vary with package type and board layout.

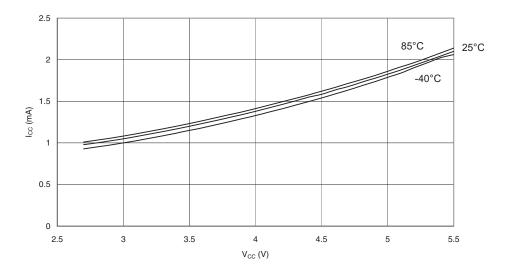

Figure 155. Active Supply Current vs.  $V_{CC}$  (32 kHz External Oscillator)

# Electrical Characteristics 291

Absolute Maximum Ratings\* 291 DC Characteristics 291 External Clock Drive Waveforms 293 External Clock Drive 293 Two-wire Serial Interface Characteristics 294 SPI Timing Characteristics 295 ADC Characteristics 297

# ATmega16 Typical Characteristics 299

# **Register Summary 331**

# Instruction Set Summary 333

# **Ordering Information 336**

## Packaging Information 337

44A 337 40P6 338 44M1 339

## Errata 340

ATmega16(L) Rev. M 340 ATmega16(L) Rev. L 340 ATmega16(L) Rev. K 341 ATmega16(L) Rev. J 342 ATmega16(L) Rev. I 343 ATmega16(L) Rev. H 344

# Datasheet Revision History 345

Rev. 2466T-07/10 345 Rev. 2466S-05/09 345 Rev. 2466R-06/08 345 Rev. 2466Q-05/08 345 Rev. 2466P-08/07 345 Rev. 2466P-03/07 345 Rev. 2466N-10/06 346 Rev. 2466M-04/06 346 Rev. 2466L-06/05 346 Rev. 2466L-06/05 346 Rev. 2466L-10/04 346 Rev. 2466I-10/04 346 Rev. 2466H-12/03 347 Rev. 2466F-02/03 347