Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                   |

|----------------------------|----------------------------------------------------------|

| Core Processor             | AVR                                                      |

| Core Size                  | 8-Bit                                                    |

| Speed                      | 16MHz                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                    |

| Number of I/O              | 32                                                       |

| Program Memory Size        | 16KB (8K x 16)                                           |

| Program Memory Type        | FLASH                                                    |

| EEPROM Size                | 512 x 8                                                  |

| RAM Size                   | 1K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                              |

| Data Converters            | A/D 8x10b                                                |

| Oscillator Type            | Internal                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                       |

| Mounting Type              | Surface Mount                                            |

| Package / Case             | 44-VFQFN Exposed Pad                                     |

| Supplier Device Package    | 44-VQFN (7x7)                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atmega16-16mq |

|                            |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### • Bit 1 – EEWE: EEPROM Write Enable

The EEPROM Write Enable Signal EEWE is the write strobe to the EEPROM. When address and data are correctly set up, the EEWE bit must be written to one to write the value into the EEPROM. The EEMWE bit must be written to one before a logical one is written to EEWE, otherwise no EEPROM write takes place. The following procedure should be followed when writing the EEPROM (the order of steps 3 and 4 is not essential):

- 1. Wait until EEWE becomes zero.

- 2. Wait until SPMEN in SPMCR becomes zero.

- 3. Write new EEPROM address to EEAR (optional).

- 4. Write new EEPROM data to EEDR (optional).

- 5. Write a logical one to the EEMWE bit while writing a zero to EEWE in EECR.

- 6. Within four clock cycles after setting EEMWE, write a logical one to EEWE.

The EEPROM can not be programmed during a CPU write to the Flash memory. The software must check that the Flash programming is completed before initiating a new EEPROM write. Step 2 is only relevant if the software contains a Boot Loader allowing the CPU to program the Flash. If the Flash is never being updated by the CPU, step 2 can be omitted. See "Boot Loader Support – Read-While-Write Self-Programming" on page 246 for details about boot programming.

Caution: An interrupt between step 5 and step 6 will make the write cycle fail, since the EEPROM Master Write Enable will time-out. If an interrupt routine accessing the EEPROM is interrupting another EEPROM Access, the EEAR or EEDR reGister will be modified, causing the interrupted EEPROM Access to fail. It is recommended to have the Global Interrupt Flag cleared during all the steps to avoid these problems.

When the write access time has elapsed, the EEWE bit is cleared by hardware. The user software can poll this bit and wait for a zero before writing the next byte. When EEWE has been set, the CPU is halted for two cycles before the next instruction is executed.

#### Bit 0 – EERE: EEPROM Read Enable

The EEPROM Read Enable Signal – EERE – is the read strobe to the EEPROM. When the correct address is set up in the EEAR Register, the EERE bit must be written to a logic one to trigger the EEPROM read. The EEPROM read access takes one instruction, and the requested data is available immediately. When the EEPROM is read, the CPU is halted for four cycles before the next instruction is executed.

The user should poll the EEWE bit before starting the read operation. If a write operation is in progress, it is neither possible to read the EEPROM, nor to change the EEAR Register.

The calibrated Oscillator is used to time the EEPROM accesses. Table 1 lists the typical programming time for EEPROM access from the CPU.

| Symbol                  | Number of Calibrated RC<br>Oscillator Cycles <sup>(1)</sup> | Typ Programming Time |

|-------------------------|-------------------------------------------------------------|----------------------|

| EEPROM write (from CPU) | 8448                                                        | 8.5 ms               |

Table 1.

EEPROM Programming Time

Note: 1. Uses 1 MHz clock, independent of CKSEL Fuse setting.

The following code examples show one assembly and one C function for writing to the EEPROM. The examples assume that interrupts are controlled (for example by disabling interrupts globally) so that no interrupts will occur during execution of these functions. The examples

Idle Mode When the SM2..0 bits are written to 000, the SLEEP instruction makes the MCU enter Idle mode, stopping the CPU but allowing SPI, USART, Analog Comparator, ADC, Two-wire Serial Interface, Timer/Counters, Watchdog, and the interrupt system to continue operating. This sleep mode basically halts clk<sub>CPU</sub> and clk<sub>FLASH</sub>, while allowing the other clocks to run.

Idle mode enables the MCU to wake up from external triggered interrupts as well as internal ones like the Timer Overflow and USART Transmit Complete interrupts. If wake-up from the Analog Comparator interrupt is not required, the Analog Comparator can be powered down by setting the ACD bit in the Analog Comparator Control and Status Register – ACSR. This will reduce power consumption in Idle mode. If the ADC is enabled, a conversion starts automatically when this mode is entered.

#### ADC Noise Reduction Mode When the SM2..0 bits are written to 001, the SLEEP instruction makes the MCU enter ADC Noise Reduction mode, stopping the CPU but allowing the ADC, the External Interrupts, the Two-wire Serial Interface address watch, Timer/Counter2 and the Watchdog to continue operating (if enabled). This sleep mode basically halts clk<sub>I/O</sub>, clk<sub>CPU</sub>, and clk<sub>FLASH</sub>, while allowing the other clocks to run.

This improves the noise environment for the ADC, enabling higher resolution measurements. If the ADC is enabled, a conversion starts automatically when this mode is entered. Apart form the ADC Conversion Complete interrupt, only an External Reset, a Watchdog Reset, a Brown-out Reset, a Two-wire Serial Interface Address Match Interrupt, a Timer/Counter2 interrupt, an SPM/EEPROM ready interrupt, an External level interrupt on INT0 or INT1, or an external interrupt on INT2 can wake up the MCU from ADC Noise Reduction mode.

**Power-down Mode** When the SM2..0 bits are written to 010, the SLEEP instruction makes the MCU enter Powerdown mode. In this mode, the External Oscillator is stopped, while the External interrupts, the Two-wire Serial Interface address watch, and the Watchdog continue operating (if enabled). Only an External Reset, a Watchdog Reset, a Brown-out Reset, a Two-wire Serial Interface address match interrupt, an External level interrupt on INT0 or INT1, or an External interrupt on INT2 can wake up the MCU. This sleep mode basically halts all generated clocks, allowing operation of asynchronous modules only.

Note that if a level triggered interrupt is used for wake-up from Power-down mode, the changed level must be held for some time to wake up the MCU. Refer to "External Interrupts" on page 68 for details.

When waking up from Power-down mode, there is a delay from the wake-up condition occurs until the wake-up becomes effective. This allows the clock to restart and become stable after having been stopped. The wake-up period is defined by the same CKSEL Fuses that define the reset time-out period, as described in "Clock Sources" on page 25.

**Power-save Mode** When the SM2..0 bits are written to 011, the SLEEP instruction makes the MCU enter Power-save mode. This mode is identical to Power-down, with one exception:

If Timer/Counter2 is clocked asynchronously, that is, the AS2 bit in ASSR is set, Timer/Counter2 will run during sleep. The device can wake up from either Timer Overflow or Output Compare event from Timer/Counter2 if the corresponding Timer/Counter2 interrupt enable bits are set in TIMSK, and the Global Interrupt Enable bit in SREG is set.

If the Asynchronous Timer is NOT clocked asynchronously, Power-down mode is recommended instead of Power-save mode because the contents of the registers in the Asynchronous Timer should be considered undefined after wake-up in Power-save mode if AS2 is 0.

This sleep mode basically halts all clocks except clk<sub>ASY</sub>, allowing operation only of asynchronous modules, including Timer/Counter2 if clocked asynchronously.

Switching between input with pull-up and output low generates the same problem. The user must use either the tri-state ( $\{DDxn, PORTxn\} = 0b00$ ) or the output high state ( $\{DDxn, PORTxn\} = 0b11$ ) as an intermediate step.

Table 20 summarizes the control signals for the pin value.

| DDxn | PORTxn | PUD<br>(in SFIOR) | I/O    | Pull-up | Comment                                     |  |  |  |  |  |  |

|------|--------|-------------------|--------|---------|---------------------------------------------|--|--|--|--|--|--|

| 0    | 0      | Х                 | Input  | No      | Tri-state (Hi-Z)                            |  |  |  |  |  |  |

| 0    | 1      | 0                 | Input  | Yes     | Pxn will source current if ext. pulled low. |  |  |  |  |  |  |

| 0    | 1      | 1                 | Input  | No      | Tri-state (Hi-Z)                            |  |  |  |  |  |  |

| 1    | 0      | Х                 | Output | No      | Output Low (Sink)                           |  |  |  |  |  |  |

| 1    | 1      | Х                 | Output | No      | Output High (Source)                        |  |  |  |  |  |  |

Table 20.

Port Pin Configurations

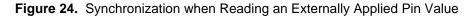

**Reading the Pin Value** Independent of the setting of Data Direction bit DDxn, the port pin can be read through the PINxn Register bit. As shown in Figure 23, the PINxn Register bit and the preceding latch constitute a synchronizer. This is needed to avoid metastability if the physical pin changes value near the edge of the internal clock, but it also introduces a delay. Figure 24 shows a timing diagram of the synchronization when reading an externally applied pin value. The maximum and minimum propagation delays are denoted t<sub>pd,max</sub> and t<sub>pd,min</sub> respectively.

Consider the clock period starting shortly *after* the first falling edge of the system clock. The latch is closed when the clock is low, and goes transparent when the clock is high, as indicated by the shaded region of the "SYNC LATCH" signal. The signal value is latched when the system clock goes low. It is clocked into the PINxn Register at the succeeding positive clock edge. As indicated by the two arrows  $t_{pd,max}$  and  $t_{pd,min}$ , a single signal transition on the pin will be delayed between  $\frac{1}{2}$  and  $\frac{1}{2}$  system clock period depending upon the time of assertion.

#### • MOSI – Port B, Bit 5

MOSI: SPI Master Data output, Slave Data input for SPI channel. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB5. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB5. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB5 bit.

#### • SS – Port B, Bit 4

$\overline{SS}$ : Slave Select input. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB4. As a Slave, the SPI is activated when this pin is driven low. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB4. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB4 bit.

#### • AIN1/OC0 - Port B, Bit 3

AIN1, Analog Comparator Negative Input. Configure the port pin as input with the internal pull-up switched off to avoid the digital port function from interfering with the function of the analog comparator.

OC0, Output Compare Match output: The PB3 pin can serve as an external output for the Timer/Counter0 Compare Match. The PB3 pin has to be configured as an output (DDB3 set (one)) to serve this function. The OC0 pin is also the output pin for the PWM mode timer function.

#### • AIN0/INT2 – Port B, Bit 2

AINO, Analog Comparator Positive input. Configure the port pin as input with the internal pull-up switched off to avoid the digital port function from interfering with the function of the Analog Comparator.

INT2, External Interrupt Source 2: The PB2 pin can serve as an external interrupt source to the MCU.

#### • T1 – Port B, Bit 1

T1, Timer/Counter1 Counter Source.

#### • T0/XCK - Port B, Bit 0

T0, Timer/Counter0 Counter Source.

XCK, USART External Clock. The Data Direction Register (DDB0) controls whether the clock is output (DDB0 set) or input (DDB0 cleared). The XCK pin is active only when the USART operates in Synchronous mode.

Table 26 and Table 27 relate the alternate functions of Port B to the overriding signals shown in Figure 26 on page 55. SPI MSTR INPUT and SPI SLAVE OUTPUT constitute the MISO signal, while MOSI is divided into SPI MSTR OUTPUT and SPI SLAVE INPUT.

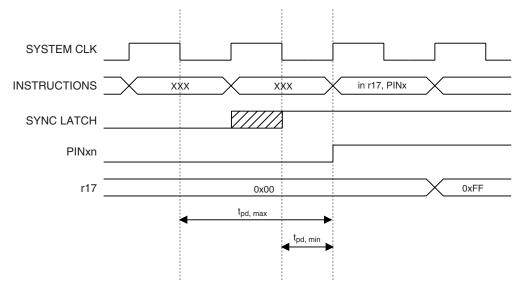

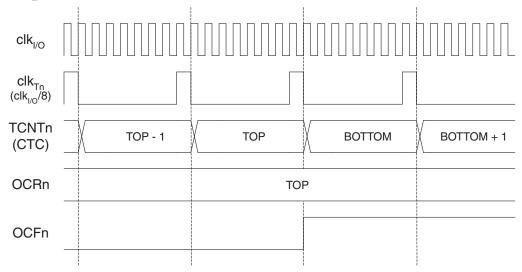

**Figure 36.** Timer/Counter Timing Diagram, Setting of OCF0, with Prescaler ( $f_{clk_l/O}/8$ )

Figure 37 shows the setting of OCF0 and the clearing of TCNT0 in CTC mode.

Figure 37. Timer/Counter Timing Diagram, Clear Timer on Compare Match Mode, with Prescaler ( $f_{clk\_l/O}/8$ )

# 16-bit Timer/Counter The 16-bit Timer/Counter unit allows accurate program execution timing (event management), wave generation, and signal timing measurement. The main features are: True 16-bit Design (that is, allows 16-bit PWM) Two Independent Output Compare Units Double Buffered Output Compare Registers One Input Capture Unit Input Capture Voise Canceler Clear Timer on Compare Match (Auto Reload) Glitch-free, Phase Correct Pulse Width Modulator (PWM) Variable PWM Period Frequency Generator

- External Event Counter

- Four Independent Interrupt Sources (TOV1, OCF1A, OCF1B, and ICF1)

#### **Overview**

Most register and bit references in this section are written in general form. A lower case "n" replaces the Timer/Counter number, and a lower case "x" replaces the output compare unit. However, when using the register or bit defines in a program, the precise form must be used (that is, TCNT1 for accessing Timer/Counter1 counter value and so on).

A simplified block diagram of the 16-bit Timer/Counter is shown in Figure 40. For the actual placement of I/O pins, refer to Figure 1 on page 2. CPU accessible I/O Registers, including I/O bits and I/O pins, are shown in bold. The device specific I/O Register and bit locations are listed in the "16-bit Timer/Counter Register Description" on page 110.

### Accessing 16-bit Registers

The TCNT1, OCR1A/B, and ICR1 are 16-bit registers that can be accessed by the AVR CPU via the 8-bit data bus. The 16-bit register must be byte accessed using two read or write operations. Each 16-bit timer has a single 8-bit register for temporary storing of the High byte of the 16-bit access. The same temporary register is shared between all 16-bit registers within each 16-bit timer. Accessing the Low byte triggers the 16-bit read or write operation. When the Low byte of a 16-bit register is written by the CPU, the High byte stored in the temporary register, and the Low byte written are both copied into the 16-bit register in the same clock cycle. When the Low byte of a 16-bit register is read by the CPU, the High byte of the 16-bit register is copied into the temporary register is copied into the temporary register is read by the CPU.

Not all 16-bit accesses uses the temporary register for the High byte. Reading the OCR1A/B 16bit registers does not involve using the temporary register.

To do a 16-bit write, the High byte must be written before the Low byte. For a 16-bit read, the Low byte must be read before the High byte.

The following code examples show how to access the 16-bit Timer Registers assuming that no interrupts updates the temporary register. The same principle can be used directly for accessing the OCR1A/B and ICR1 Registers. Note that when using "C", the compiler handles the 16-bit access.

| Assembly Code Example <sup>(1)</sup> |

|--------------------------------------|

|                                      |

| ; Set TCNT1 to 0x01FF                |

| <b>ldi</b> r17,0x01                  |

| <b>ldi</b> r16,0xFF                  |

| out TCNT1H,r17                       |

| out TCNT1L,r16                       |

| ; Read TCNT1 into r17:r16            |

| in r16,TCNT1L                        |

| in r17,TCNT1H                        |

|                                      |

| C Code Example <sup>(1)</sup>        |

| unsigned int i;                      |

|                                      |

| /* Set TCNT1 to 0x01FF */            |

| TCNT1 = 0x1FF;                       |

| /* Read TCNT1 into i */              |

| i = TCNT1;                           |

|                                      |

|                                      |

Note: 1. See "About Code Examples" on page 7.

The assembly code example returns the TCNT1 value in the r17:r16 register pair.

It is important to notice that accessing 16-bit registers are atomic operations. If an interrupt occurs between the two instructions accessing the 16-bit register, and the interrupt code updates the temporary register by accessing the same or any other of the 16-bit Timer Registers, then the result of the access outside the interrupt will be corrupted. Therefore, when both the main code and the interrupt code update the temporary register, the main code must disable the interrupts during the 16-bit access.

- 1. Write any value to either of the registers OCR2 or TCCR2.

- 2. Wait for the corresponding Update Busy Flag to be cleared.

- 3. Read TCNT2.

- During asynchronous operation, the synchronization of the Interrupt Flags for the asynchronous timer takes three processor cycles plus one timer cycle. The timer is therefore advanced by at least one before the processor can read the timer value causing the setting of the Interrupt Flag. The output compare pin is changed on the timer clock and is not synchronized to the processor clock.

#### Timer/Counter Interrupt Mask Register – TIMSK

| Bit           | 7     | 6     | 5      | 4      | 3      | 2     | 1     | 0     | _     |

|---------------|-------|-------|--------|--------|--------|-------|-------|-------|-------|

|               | OCIE2 | TOIE2 | TICIE1 | OCIE1A | OCIE1B | TOIE1 | OCIE0 | TOIE0 | TIMSK |

| Read/Write    | R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   |       |

| Initial Value | 0     | 0     | 0      | 0      | 0      | 0     | 0     | 0     |       |

#### • Bit 7 – OCIE2: Timer/Counter2 Output Compare Match Interrupt Enable

When the OCIE2 bit is written to one and the I-bit in the Status Register is set (one), the Timer/Counter2 Compare Match interrupt is enabled. The corresponding interrupt is executed if a compare match in Timer/Counter2 occurs, that is, when the OCF2 bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

#### Bit 6 – TOIE2: Timer/Counter2 Overflow Interrupt Enable

When the TOIE2 bit is written to one and the I-bit in the Status Register is set (one), the Timer/Counter2 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter2 occurs, that is, when the TOV2 bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

Timer/Counter Interrupt Flag Register – TIFR

| Bit           | 7    | 6    | 5    | 4     | 3     | 2    | 1    | 0    | _    |

|---------------|------|------|------|-------|-------|------|------|------|------|

|               | OCF2 | TOV2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0 | TOV0 | TIFR |

| Read/Write    | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W  | R/W  |      |

| Initial Value | 0    | 0    | 0    | 0     | 0     | 0    | 0    | 0    |      |

#### • Bit 7 – OCF2: Output Compare Flag 2

The OCF2 bit is set (one) when a compare match occurs between the Timer/Counter2 and the data in OCR2 – Output Compare Register2. OCF2 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF2 is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE2 (Timer/Counter2 Compare match Interrupt Enable), and OCF2 are set (one), the Timer/Counter2 Compare match Interrupt is executed.

#### • Bit 6 – TOV2: Timer/Counter2 Overflow Flag

The TOV2 bit is set (one) when an overflow occurs in Timer/Counter2. TOV2 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV2 is cleared by writing a logic one to the flag. When the SREG I-bit, TOIE2 (Timer/Counter2 Overflow Interrupt Enable), and TOV2 are set (one), the Timer/Counter2 Overflow interrupt is executed. In PWM mode, this bit is set when Timer/Counter2 changes counting direction at \$00.

| Status Code                    |                                                                    | Application Software Response |         |     |       |                                                               |                                                                                                                                                                                          |

|--------------------------------|--------------------------------------------------------------------|-------------------------------|---------|-----|-------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (TWSR)<br>Prescaler Bits       | Status of the Two-wire Serial Bus<br>and Two-wire Serial Interface |                               | To TWCR |     |       |                                                               | -                                                                                                                                                                                        |

| are 0                          | Hardware                                                           | To/from TWDR                  | STA     | STO | TWINT | TWEA                                                          | Next Action Taken by TWI Hardware                                                                                                                                                        |

| \$A8                           | Own SLA+R has been received;<br>ACK has been returned              | Load data byte or             | х       | 0   | 1     | 0                                                             | Last data byte will be transmitted and NOT ACK should be received                                                                                                                        |

|                                |                                                                    | Load data byte                | Х       | 0   | 1     | 1                                                             | Data byte will be transmitted and ACK should be re-<br>ceived                                                                                                                            |

| \$B0                           | Arbitration lost in SLA+R/W as Master; own SLA+R has been          | Load data byte or             | Х       | 0   | 1     | 0                                                             | Last data byte will be transmitted and NOT ACK should be received                                                                                                                        |

| received; ACK has been returne | Load data byte                                                     | х                             | 0       | 1   | 1     | Data byte will be transmitted and ACK should be re-<br>ceived |                                                                                                                                                                                          |

| \$B8                           | Data byte in TWDR has been transmitted; ACK has been               | Load data byte or             | Х       | 0   | 1     | 0                                                             | Last data byte will be transmitted and NOT ACK should be received                                                                                                                        |

|                                | received                                                           | Load data byte                | х       | 0   | 1     | 1                                                             | Data byte will be transmitted and ACK should be re-<br>ceived                                                                                                                            |

| \$C0                           | Data byte in TWDR has been transmitted; NOT ACK has been           | No TWDR action or             | 0       | 0   | 1     | 0                                                             | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA                                                                                                            |

|                                | received                                                           | No TWDR action or             | 0       | 0   | 1     | 1                                                             | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1"                                                                        |

|                                |                                                                    | No TWDR action or             | 1       | 0   | 1     | 0                                                             | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA;<br>a START condition will be transmitted when the bus<br>becomes free                                     |

|                                |                                                                    | No TWDR action                | 1       | 0   | 1     | 1                                                             | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1";<br>a START condition will be transmitted when the bus<br>becomes free |

| \$C8                           | Last data byte in TWDR has been transmitted (TWEA = "0"); ACK      | No TWDR action or             | 0       | 0   | 1     | 0                                                             | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA                                                                                                            |

|                                |                                                                    | No TWDR action or             | 0       | 0   | 1     | 1                                                             | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1"                                                                        |

|                                |                                                                    | No TWDR action or             | 1       | 0   | 1     | 0                                                             | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA;<br>a START condition will be transmitted when the bus<br>becomes free                                     |

|                                |                                                                    | No TWDR action                | 1       | 0   | 1     | 1                                                             | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1";<br>a START condition will be transmitted when the bus<br>becomes free |

#### Table 77. Status Codes for Slave Transmitter Mode

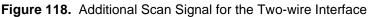

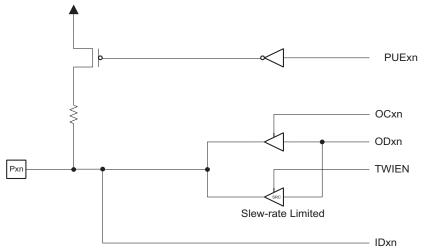

Scanning the RESETThe RESET pin accepts 5V active low logic for standard reset operation, and 12V active high<br/>logic for High Voltage Parallel Programming. An observe-only cell as shown in Figure 119 is<br/>inserted both for the 5V reset signal; RSTT, and the 12V reset signal; RSTHV.

Figure 119. Observe-only Cell

## Scanning the Clock Pins

The AVR devices have many clock options selectable by fuses. These are: Internal RC Oscillator, External RC, External Clock, (High Frequency) Crystal Oscillator, Low Frequency Crystal Oscillator, and Ceramic Resonator.

Figure 120 shows how each Oscillator with external connection is supported in the scan chain. The Enable signal is supported with a general boundary-scan cell, while the Oscillator/Clock output is attached to an observe-only cell. In addition to the main clock, the Timer Oscillator is scanned in the same way. The output from the internal RC Oscillator is not scanned, as this Oscillator does not have external connections.

#### Programming the Flash

The Flash is organized in pages, see Table 107 on page 262. When programming the Flash, the program data is latched into a page buffer. This allows one page of program data to be programmed simultaneously. The following procedure describes how to program the entire Flash memory:

- A. Load Command "Write Flash"

- 1. Set XA1, XA0 to "10". This enables command loading.

- 2. Set BS1 to "0".

- 3. Set DATA to "0001 0000". This is the command for Write Flash.

- 4. Give XTAL1 a positive pulse. This loads the command.

- B. Load Address Low byte

- 1. Set XA1, XA0 to "00". This enables address loading.

- 2. Set BS1 to "0". This selects low address.

- 3. Set DATA = Address Low byte (\$00 \$FF).

- 4. Give XTAL1 a positive pulse. This loads the address Low byte.

- C. Load Data Low Byte

- 1. Set XA1, XA0 to "01". This enables data loading.

- 2. Set DATA = Data Low byte (\$00 \$FF).

- 3. Give XTAL1 a positive pulse. This loads the data byte.

- D. Load Data High Byte

- 1. Set BS1 to "1". This selects high data byte.

- 2. Set XA1, XA0 to "01". This enables data loading.

- 3. Set DATA = Data High byte (\$00 \$FF).

- 4. Give XTAL1 a positive pulse. This loads the data byte.

- E. Latch Data

- 1. Set BS1 to "1". This selects high data byte.

- Give PAGEL a positive pulse. This latches the data bytes. (See Figure 129 for signal waveforms)

- F. Repeat B through E until the entire buffer is filled or until all data within the page is loaded.

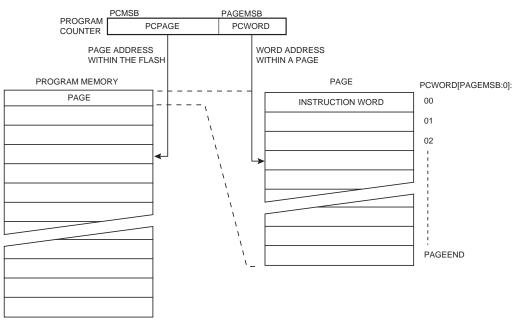

While the lower bits in the address are mapped to words within the page, the higher bits address the pages within the FLASH. This is illustrated in Figure 128 on page 267. Note that if less than 8 bits are required to address words in the page (pagesize < 256), the most significant bit(s) in the address Low byte are used to address the page when performing a page write.

- G. Load Address High byte

- 1. Set XA1, XA0 to "00". This enables address loading.

- 2. Set BS1 to "1". This selects high address.

- 3. Set DATA = Address High byte (\$00 \$FF).

- 4. Give XTAL1 a positive pulse. This loads the address High byte.

- H. Program Page

- 1. Set BS1 = "0"

- Give WR a negative pulse. This starts programming of the entire page of data. RDY/BSY goes low.

- 3. Wait until RDY/BSY goes high. (See Figure 129 for signal waveforms)

I. Repeat B through H until the entire Flash is programmed or until all data has been programmed.

J. End Page Programming

- 1. 1. Set XA1, XA0 to "10". This enables command loading.

- 2. Set DATA to "0000 0000". This is the command for No Operation.

- 3. Give XTAL1 a positive pulse. This loads the command, and the internal write signals are reset.

Figure 128. Addressing the Flash which is Organized in Pages

Note: 1. PCPAGE and PCWORD are listed in Table 107 on page 262.

#### Programming Command Register

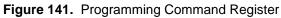

The Programming Command Register is a 15-bit register. This register is used to serially shift in programming commands, and to serially shift out the result of the previous command, if any. The JTAG Programming Instruction Set is shown in Table 117. The state sequence when shifting in the programming commands is illustrated in Figure 142.

Table 117. JTAG Programming Instruction Set (Continued)

a = address high bits, b = address low bits, H = 0 - Low byte, 1 - High Byte, o = data out, i = data in, x = don't care

| Instruction                            | TDI sequence              | TDO sequence              | Notes          |

|----------------------------------------|---------------------------|---------------------------|----------------|

| 5d. Read Data Byte                     | 0110011_ <b>bbbbbbb</b> b | xxxxxxx_xxxxxxx           |                |

|                                        | 0110010_0000000           | XXXXXXX_XXXXXXXX          |                |

|                                        | 0110011_00000000          | xxxxxxx_00000000          |                |

| 6a. Enter Fuse Write                   | 0100011_01000000          | XXXXXXX_XXXXXXX           |                |

| 6b. Load Data Low Byte <sup>(6)</sup>  | 0010011_iiiiiiiii         | xxxxxxx_xxxxxxx           | (3)            |

| 6c. Write Fuse High byte               | 0110111_00000000          | xxxxxxx_xxxxxxx           | (1)            |

|                                        | 0110101_00000000          | XXXXXXX_XXXXXXX           |                |

|                                        | 0110111_00000000          | xxxxxxx_xxxxxxx           |                |

|                                        | 0110111_00000000          | XXXXXXX_XXXXXXX           |                |

| 6d. Poll for Fuse Write complete       | 0110111_00000000          | xxxxx <b>o</b> x_xxxxxxx  | (2)            |

| 6e. Load Data Low Byte <sup>(7)</sup>  | 0010011_iiiiiiiii         | xxxxxxx_xxxxxxx           | (3)            |

| 6f. Write Fuse Low byte                | 0110011_00000000          | xxxxxxx_xxxxxxx           | (1)            |

|                                        | 0110001_00000000          | xxxxxxx_xxxxxxx           |                |

|                                        | 0110011_00000000          | xxxxxxx_xxxxxxx           |                |

|                                        | 0110011_00000000          | XXXXXXX_XXXXXXX           |                |

| 6g. Poll for Fuse Write complete       | 0110011_00000000          | xxxxx <b>o</b> x_xxxxxxxx | (2)            |

| 7a. Enter Lock Bit Write               | 0100011_00100000          | XXXXXXX_XXXXXXXX          |                |

| 7b. Load Data Byte <sup>(8)</sup>      | 0010011_11 <b>iiiii</b>   | XXXXXXX_XXXXXXX           | (4)            |

| 7c. Write Lock Bits                    | 0110011_00000000          | xxxxxxx_xxxxxxx           | (1)            |

|                                        | 0110001_0000000           | xxxxxxx_xxxxxxx           |                |

|                                        | 0110011_00000000          | xxxxxxx_xxxxxxx           |                |

|                                        | 0110011_00000000          | XXXXXXX_XXXXXXX           |                |

| 7d. Poll for Lock Bit Write complete   | 0110011_00000000          | xxxxx <b>o</b> x_xxxxxxx  | (2)            |

| 8a. Enter Fuse/Lock Bit Read           | 0100011_00000100          | xxxxxxx_xxxxxxx           |                |

| 8b. Read Fuse High Byte <sup>(6)</sup> | 0111110_00000000          | XXXXXXX_XXXXXXX           |                |

|                                        | 0111111_00000000          | xxxxxxx_00000000          |                |

| 8c. Read Fuse Low Byte <sup>(7)</sup>  | 0110010_0000000           | XXXXXXX XXXXXXXX          |                |

|                                        | 0110011_00000000          |                           |                |

| 8d. Read Lock Bits <sup>(8)</sup>      | 0110110_00000000          |                           | (5)            |

|                                        | 0110111_00000000          | XXXXXXX_XX <b>000000</b>  |                |

| 8e. Read Fuses and Lock Bits           | 0111110_00000000          |                           | (5)            |

|                                        | 0110010_00000000          |                           | Fuse High Byte |

|                                        | 0110110_0000000           | xxxxxxx_00000000          | Fuse Low Byte  |

|                                        | 0110111_00000000          | xxxxxxx_00000000          | Lock bits      |

| 9a. Enter Signature Byte Read          | 0100011_00001000          | xxxxxxx_xxxxxxx           |                |

| 9b. Load Address Byte                  | 0000011_ <b>bbbbbbb</b>   | xxxxxxx_xxxxxx            |                |

| 9c. Read Signature Byte                | 0110010_00000000          |                           |                |

| - · ·                                  | 0110011_00000000          |                           |                |

| 10a. Enter Calibration Byte Read       | 0100011_00001000          | xxxxxxx_xxxxxxx           |                |

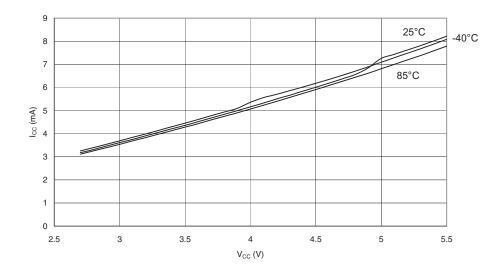

Figure 153. Active Supply Current vs. V<sub>CC</sub> (Internal RC Oscillator, 2 MHz)

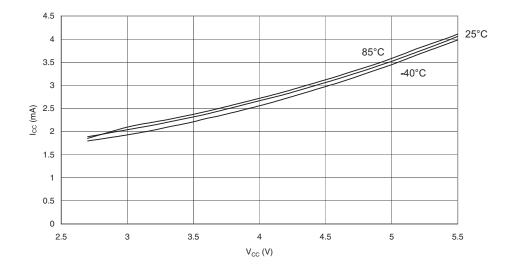

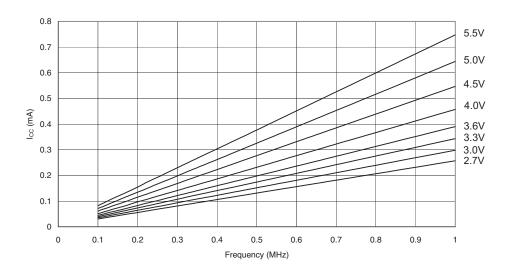

Idle Supply Current Figure 156. Idle Supply Current vs. Frequency (0.1 MHz - 1.0 MHz)

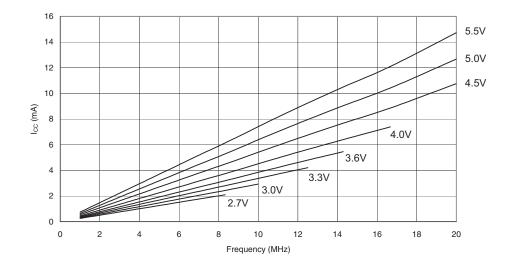

Figure 157. Idle Supply Current vs. Frequency (1 MHz - 20 MHz)

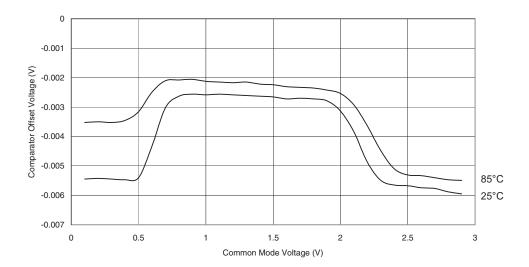

Figure 193. Watchdog Oscillator Frequency vs.  $V_{CC}$

Speed

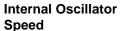

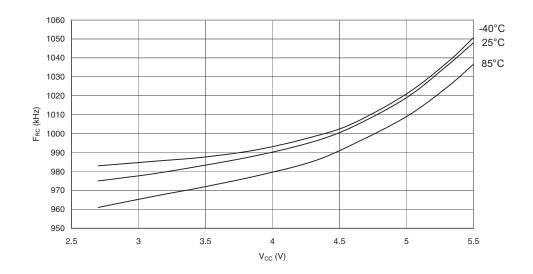

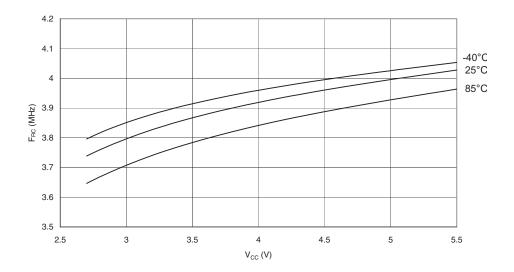

Figure 198. Calibrated 4 MHz RC Oscillator Frequency vs.  $V_{CC}$

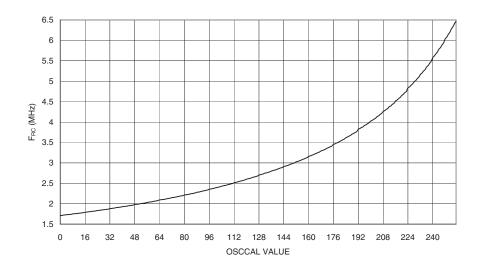

Figure 199. Calibrated 4 MHz RC Oscillator Frequency vs. Osccal Value

## **Register Summary**

| Address                                   | Name           | Bit 7           | Bit 6                       | Bit 5             | Bit 4           | Bit 3           | Bit 2           | Bit 1           | Bit 0           | Page              |  |  |

|-------------------------------------------|----------------|-----------------|-----------------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------------|--|--|

| \$3F (\$5F)                               | SREG           | I               | т                           | Н                 | S               | V               | N               | Z               | С               | 9                 |  |  |

| \$3E (\$5E)                               | SPH            | -               | -                           | -                 | _               | -               | SP10            | SP9             | SP8             | 12                |  |  |

| \$3D (\$5D)                               | SPL            | SP7             | SP6                         | SP5               | SP4             | SP3             | SP2             | SP1             | SP0             | 12                |  |  |

| \$3C (\$5C)                               | OCR0           | Timer/Counter   | r0 Output Compar            | e Register        |                 |                 |                 |                 |                 | 85                |  |  |

| \$3B (\$5B)                               | GICR           | INT1            | INT0                        | INT2              | -               | -               | -               | IVSEL           | IVCE            | 48, 69            |  |  |

| \$3A (\$5A)                               | GIFR           | INTF1           | INTF0                       | INTF2             | -               | -               | -               | -               | -               | 70                |  |  |

| \$39 (\$59)                               | TIMSK          | OCIE2           | TOIE2                       | TICIE1            | OCIE1A          | OCIE1B          | TOIE1           | OCIE0           | TOIE0           | 85, 115, 133      |  |  |

| \$38 (\$58)                               | TIFR           | OCF2            | TOV2                        | ICF1              | OCF1A           | OCF1B           | TOV1            | OCF0            | TOV0            | 86, 115, 133      |  |  |

| \$37 (\$57)                               | SPMCR          | SPMIE           | RWWSB                       | -                 | RWWSRE          | BLBSET          | PGWRT           | PGERS           | SPMEN           | 250               |  |  |

| \$36 (\$56)                               | TWCR           | TWINT           | TWEA                        | TWSTA             | TWSTO           | TWWC            | TWEN            | -               | TWIE            | 180               |  |  |

| \$35 (\$55)                               | MCUCR          | SM2             | SE                          | SM1               | SM0             | ISC11           | ISC10           | ISC01           | ISC00           | 32, 68            |  |  |

| \$34 (\$54)                               | MCUCSR         | JTD<br>FOC0     | ISC2                        | COM01             | JTRF            | WDRF            | BORF            | EXTRF           | PORF            | 41, 69, 231       |  |  |

| \$33 (\$53)<br>\$32 (\$52)                | TCCR0<br>TCNT0 | Timer/Counter   | WGM00                       | CONIDT            | COM00           | WGM01           | CS02            | CS01            | CS00            | 83<br>85          |  |  |

| φ32 (φ32)                                 | OSCCAL         |                 | bration Register            |                   |                 |                 |                 |                 |                 | 30                |  |  |

| \$31 <sup>(1)</sup> (\$51) <sup>(1)</sup> | OCDR           | On-Chip Debu    | Ť                           |                   |                 |                 |                 |                 |                 | 227               |  |  |

| \$30 (\$50)                               | SFIOR          | ADTS2           | ADTS1                       | ADTS0             | _               | ACME            | PUD             | PSR2            | PSR10           | 57,88,134,201,221 |  |  |

| \$2F (\$4F)                               | TCCR1A         | COM1A1          | COM1A0                      | COM1B1            | COM1B0          | FOC1A           | FOC1B           | WGM11           | WGM10           | 110               |  |  |

| \$2E (\$4E)                               | TCCR1B         | ICNC1           | ICES1                       | -                 | WGM13           | WGM12           | CS12            | CS11            | CS10            | 113               |  |  |

| \$2D (\$4D)                               | TCNT1H         |                 | r1 – Counter Regi           | ster High Byte    |                 | •               | ·               | ·               |                 | 114               |  |  |

| \$2C (\$4C)                               | TCNT1L         |                 | r1 – Counter Regi           |                   |                 |                 |                 |                 |                 | 114               |  |  |

| \$2B (\$4B)                               | OCR1AH         | Timer/Counter   | r1 – Output Comp            | are Register A Hi | gh Byte         |                 |                 |                 |                 | 114               |  |  |

| \$2A (\$4A)                               | OCR1AL         |                 | r1 – Output Comp            | 0                 | ,               |                 |                 |                 |                 | 114               |  |  |

| \$29 (\$49)                               | OCR1BH         |                 | r1 – Output Comp            | <u> </u>          |                 |                 |                 |                 |                 | 114               |  |  |

| \$28 (\$48)                               | OCR1BL         | Timer/Counter   | r1 – Output Comp            | are Register B Lo | w Byte          |                 |                 |                 |                 | 114               |  |  |

| \$27 (\$47)                               | ICR1H          |                 | 1 – Input Capture           |                   |                 |                 |                 |                 |                 | 114               |  |  |

| \$26 (\$46)                               | ICR1L          |                 | r1 – Input Capture          | · · · · ·         |                 |                 |                 |                 |                 | 114               |  |  |

| \$25 (\$45)                               | TCCR2          | FOC2            | WGM20                       | COM21             | COM20           | WGM21           | CS22            | CS21            | CS20            | 128               |  |  |

| \$24 (\$44)                               | TCNT2          | Timer/Counter   | . ,                         | - De sister       |                 |                 |                 |                 |                 | 130               |  |  |

| \$23 (\$43)                               | OCR2           |                 | r2 Output Compar            | e Register        |                 | 4.00            | TONOLID         |                 | TOPOLID         | 130               |  |  |

| \$22 (\$42)                               | ASSR<br>WDTCR  | -               | -                           | -                 | –<br>WDTOE      | AS2<br>WDE      | TCN2UB<br>WDP2  | OCR2UB<br>WDP1  | TCR2UB<br>WDP0  | 131<br>43         |  |  |

| \$21 (\$41)                               | UBRRH          | –<br>URSEL      | _                           |                   | WDTOE           | WDE             |                 | R[11:8]         | WDPU            | 167               |  |  |

| \$20 <sup>(2)</sup> (\$40) <sup>(2)</sup> | UCSRC          | URSEL           | UMSEL                       | UPM1              | UPM0            | USBS            | UCSZ1           | UCSZ0           | UCPOL           | 166               |  |  |

| \$1F (\$3F)                               | EEARH          | -               | -                           | -                 | -               | -               | -               | -               | EEAR8           | 19                |  |  |

| \$1E (\$3E)                               | EEARL          | EEPROM Add      | Iress Register Lov          |                   |                 |                 |                 |                 |                 | 19                |  |  |

| \$1D (\$3D)                               | EEDR           | EEPROM Data     | Ť                           | ,                 |                 |                 |                 |                 |                 | 19                |  |  |

| \$1C (\$3C)                               | EECR           | -               | -                           | -                 | -               | EERIE           | EEMWE           | EEWE            | EERE            | 19                |  |  |

| \$1B (\$3B)                               | PORTA          | PORTA7          | PORTA6                      | PORTA5            | PORTA4          | PORTA3          | PORTA2          | PORTA1          | PORTA0          | 66                |  |  |

| \$1A (\$3A)                               | DDRA           | DDA7            | DDA6                        | DDA5              | DDA4            | DDA3            | DDA2            | DDA1            | DDA0            | 66                |  |  |

| \$19 (\$39)                               | PINA           | PINA7           | PINA6                       | PINA5             | PINA4           | PINA3           | PINA2           | PINA1           | PINA0           | 66                |  |  |

| \$18 (\$38)                               | PORTB          | PORTB7          | PORTB6                      | PORTB5            | PORTB4          | PORTB3          | PORTB2          | PORTB1          | PORTB0          | 66                |  |  |

| \$17 (\$37)                               | DDRB           | DDB7            | DDB6                        | DDB5              | DDB4            | DDB3            | DDB2            | DDB1            | DDB0            | 66                |  |  |

| \$16 (\$36)                               | PINB           | PINB7           | PINB6                       | PINB5             | PINB4           | PINB3           | PINB2           | PINB1           | PINB0           | 66                |  |  |

| \$15 (\$35)                               | PORTC          | PORTC7          | PORTC6                      | PORTC5            | PORTC4          | PORTC3          | PORTC2          | PORTC1          | PORTC0          | 67                |  |  |

| \$14 (\$34)                               | DDRC           | DDC7            | DDC6                        | DDC5              | DDC4            | DDC3            | DDC2            | DDC1            | DDC0            | 67                |  |  |

| \$13 (\$33)<br>\$12 (\$32)                | PINC           | PINC7<br>PORTD7 | PINC6<br>PORTD6             | PINC5<br>PORTD5   | PINC4<br>PORTD4 | PINC3<br>PORTD3 | PINC2<br>PORTD2 | PINC1<br>PORTD1 | PINC0<br>PORTD0 | 67<br>67          |  |  |

| \$12 (\$32)<br>\$11 (\$31)                | PORTD<br>DDRD  | DDD7            | DDD6                        | DDD5              | DDD4            | DDD3            | DDD2            | DDD1            | DDD0            | 67                |  |  |

| \$10 (\$30)                               | PIND           | PIND7           | PIND6                       | PIND5             | PIND4           | PIND3           | PIND2           | PIND1           | PIND0           | 67                |  |  |

| \$0F (\$2F)                               | SPDR           | SPI Data Reg    |                             | T IND 3           |                 |                 |                 |                 | TINDO           | 142               |  |  |

| \$0E (\$2E)                               | SPSR           | SPIF            | WCOL                        | -                 | -               | -               | -               | _               | SPI2X           | 142               |  |  |

| \$0D (\$2D)                               | SPCR           | SPIE            | SPE                         | DORD              | MSTR            | CPOL            | CPHA            | SPR1            | SPR0            | 142               |  |  |

| \$0C (\$2C)                               | UDR            | USART I/O Da    |                             |                   |                 |                 |                 |                 |                 | 163               |  |  |

| \$0B (\$2B)                               | UCSRA          | RXC             | TXC                         | UDRE              | FE              | DOR             | PE              | U2X             | MPCM            | 164               |  |  |

| \$0A (\$2A)                               | UCSRB          | RXCIE           | TXCIE                       | UDRIE             | RXEN            | TXEN            | UCSZ2           | RXB8            | TXB8            | 165               |  |  |

| \$09 (\$29)                               | UBRRL          |                 | Rate Register Lo            | w Byte            |                 |                 |                 |                 |                 | 167               |  |  |

| \$08 (\$28)                               | ACSR           | ACD             | ACBG                        | ACO               | ACI             | ACIE            | ACIC            | ACIS1           | ACIS0           | 202               |  |  |

| \$07 (\$27)                               | ADMUX          | REFS1           | REFS0                       | ADLAR             | MUX4            | MUX3            | MUX2            | MUX1            | MUX0            | 217               |  |  |

| \$06 (\$26)                               | ADCSRA         | ADEN            | ADSC                        | ADATE             | ADIF            | ADIE            | ADPS2           | ADPS1           | ADPS0           | 219               |  |  |

| \$05 (\$25)                               | ADCH           |                 | gister High Byte            |                   |                 |                 |                 |                 |                 | 220               |  |  |

|                                           | ADCL           | ADC Data Rec    | ADC Data Register Low Byte  |                   |                 |                 |                 |                 |                 |                   |  |  |

| \$04 (\$24)                               |                | 1               |                             |                   |                 |                 |                 |                 |                 |                   |  |  |

| \$04 (\$24)<br>\$03 (\$23)<br>\$02 (\$22) | TWDR           | 1               | al Interface Data F<br>TWA5 | Register<br>TWA4  | TWA3            | TWA2            | TWA1            | TWA0            | TWGCE           | 182<br>182        |  |  |