Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-TQFP                                                                 |

| Supplier Device Package    | 44-TQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega16l-8aj |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Port B (PB7PB0) | Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The |

|-----------------|---------------------------------------------------------------------------------------------------------|

|                 | Port B output buffers have symmetrical drive characteristics with both high sink and source             |

|                 | capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up    |

|                 | resistors are activated. The Port B pins are tri-stated when a reset condition becomes active,          |

|                 | even if the clock is not running.                                                                       |

Port B also serves the functions of various special features of the ATmega16 as listed on page 58.

Port C (PC7..PC0) Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PC5(TDI), PC3(TMS) and PC2(TCK) will be activated even if a reset occurs.

Port C also serves the functions of the JTAG interface and other special features of the ATmega16 as listed on page 61.

**Port D (PD7..PD0)** Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATmega16 as listed on page 63.

- **RESET** Reset Input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 15 on page 38. Shorter pulses are not guaranteed to generate a reset.

- **XTAL1** Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

- **XTAL2** Output from the inverting Oscillator amplifier.

- AVCC is the supply voltage pin for Port A and the A/D Converter. It should be externally connected to  $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to  $V_{CC}$  through a low-pass filter.

- **AREF** AREF is the analog reference pin for the A/D Converter.

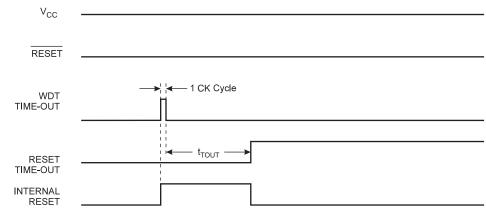

### Watchdog Reset

When the Watchdog times out, it will generate a short reset pulse of one CK cycle duration. On the falling edge of this pulse, the delay timer starts counting the Time-out period t<sub>TOUT</sub>. Refer to page 42 for details on operation of the Watchdog Timer.

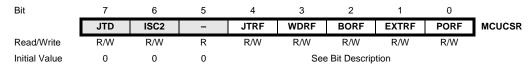

### MCU Control and Status Register – MCUCSR

The MCU Control and Status Register provides information on which reset source caused an MCU Reset.

### Bit 4 – JTRF: JTAG Reset Flag

This bit is set if a reset is being caused by a logic one in the JTAG Reset Register selected by the JTAG instruction AVR\_RESET. This bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

### Bit 3 – WDRF: Watchdog Reset Flag

This bit is set if a Watchdog Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

### Bit 2 – BORF: Brown-out Reset Flag

This bit is set if a Brown-out Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

### Bit 1 – EXTRF: External Reset Flag

This bit is set if an External Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

#### Bit 0 – PORF: Power-on Reset Flag

This bit is set if a Power-on Reset occurs. The bit is reset only by writing a logic zero to the flag.

To make use of the Reset Flags to identify a reset condition, the user should read and then reset the MCUCSR as early as possible in the program. If the register is cleared before another reset occurs, the source of the reset can be found by examining the Reset Flags.

### Interrupts

This section describes the specifics of the interrupt handling as performed in ATmega16. For a general explanation of the AVR interrupt handling, refer to "Reset and Interrupt Handling" on page 13.

### Interrupt Vectors in ATmega16

| Vector No. | Program<br>Address <sup>(2)</sup> | Source       | Interrupt Definition                                                                    |

|------------|-----------------------------------|--------------|-----------------------------------------------------------------------------------------|

| 1          | \$000 <sup>(1)</sup>              | RESET        | External Pin, Power-on Reset, Brown-out<br>Reset, Watchdog Reset, and JTAG AVR<br>Reset |

| 2          | \$002                             | INT0         | External Interrupt Request 0                                                            |

| 3          | \$004                             | INT1         | External Interrupt Request 1                                                            |

| 4          | \$006                             | TIMER2 COMP  | Timer/Counter2 Compare Match                                                            |

| 5          | \$008                             | TIMER2 OVF   | Timer/Counter2 Overflow                                                                 |

| 6          | \$00A                             | TIMER1 CAPT  | Timer/Counter1 Capture Event                                                            |

| 7          | \$00C                             | TIMER1 COMPA | Timer/Counter1 Compare Match A                                                          |

| 8          | \$00E                             | TIMER1 COMPB | Timer/Counter1 Compare Match B                                                          |

| 9          | \$010                             | TIMER1 OVF   | Timer/Counter1 Overflow                                                                 |

| 10         | \$012                             | TIMER0 OVF   | Timer/Counter0 Overflow                                                                 |

| 11         | \$014                             | SPI, STC     | Serial Transfer Complete                                                                |

| 12         | \$016                             | USART, RXC   | USART, Rx Complete                                                                      |

| 13         | \$018                             | USART, UDRE  | USART Data Register Empty                                                               |

| 14         | \$01A                             | USART, TXC   | USART, Tx Complete                                                                      |

| 15         | \$01C                             | ADC          | ADC Conversion Complete                                                                 |

| 16         | \$01E                             | EE_RDY       | EEPROM Ready                                                                            |

| 17         | \$020                             | ANA_COMP     | Analog Comparator                                                                       |

| 18         | \$022                             | TWI          | Two-wire Serial Interface                                                               |

| 19         | \$024                             | INT2         | External Interrupt Request 2                                                            |

| 20         | \$026                             | TIMER0 COMP  | Timer/Counter0 Compare Match                                                            |

| 21         | \$028                             | SPM_RDY      | Store Program Memory Ready                                                              |

Notes: 1. When the BOOTRST Fuse is programmed, the device will jump to the Boot Loader address at reset, see "Boot Loader Support – Read-While-Write Self-Programming" on page 246.

2. When the IVSEL bit in GICR is set, interrupt vectors will be moved to the start of the Boot Flash section. The address of each Interrupt Vector will then be the address in this table added to the start address of the Boot Flash section.

Table 19 shows Reset and Interrupt Vectors placement for the various combinations of BOOTRST and IVSEL settings. If the program never enables an interrupt source, the Interrupt Vectors are not used, and regular program code can be placed at these locations. This is also the case if the Reset Vector is in the Application section while the Interrupt Vectors are in the Boot section or vice versa.

### • MOSI – Port B, Bit 5

MOSI: SPI Master Data output, Slave Data input for SPI channel. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB5. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB5. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB5 bit.

### • SS – Port B, Bit 4

$\overline{SS}$ : Slave Select input. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB4. As a Slave, the SPI is activated when this pin is driven low. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB4. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB4 bit.

### • AIN1/OC0 - Port B, Bit 3

AIN1, Analog Comparator Negative Input. Configure the port pin as input with the internal pull-up switched off to avoid the digital port function from interfering with the function of the analog comparator.

OC0, Output Compare Match output: The PB3 pin can serve as an external output for the Timer/Counter0 Compare Match. The PB3 pin has to be configured as an output (DDB3 set (one)) to serve this function. The OC0 pin is also the output pin for the PWM mode timer function.

#### • AIN0/INT2 – Port B, Bit 2

AINO, Analog Comparator Positive input. Configure the port pin as input with the internal pull-up switched off to avoid the digital port function from interfering with the function of the Analog Comparator.

INT2, External Interrupt Source 2: The PB2 pin can serve as an external interrupt source to the MCU.

### • T1 – Port B, Bit 1

T1, Timer/Counter1 Counter Source.

### • T0/XCK - Port B, Bit 0

T0, Timer/Counter0 Counter Source.

XCK, USART External Clock. The Data Direction Register (DDB0) controls whether the clock is output (DDB0 set) or input (DDB0 cleared). The XCK pin is active only when the USART operates in Synchronous mode.

Table 26 and Table 27 relate the alternate functions of Port B to the overriding signals shown in Figure 26 on page 55. SPI MSTR INPUT and SPI SLAVE OUTPUT constitute the MISO signal, while MOSI is divided into SPI MSTR OUTPUT and SPI SLAVE INPUT.

| Signal<br>Name | PB7/SCK      | PB6/MISO         | PB5/MOSI        | PB4/SS       |

|----------------|--------------|------------------|-----------------|--------------|

| PUOE           | SPE • MSTR   | SPE • MSTR       | SPE • MSTR      | SPE • MSTR   |

| PUOV           | PORTB7 • PUD | PORTB6 • PUD     | PORTB5 • PUD    | PORTB4 • PUD |

| DDOE           | SPE • MSTR   | SPE • MSTR       | SPE • MSTR      | SPE • MSTR   |

| DDOV           | 0            | 0                | 0               | 0            |

| PVOE           | SPE • MSTR   | SPE • MSTR       | SPE • MSTR      | 0            |

| PVOV           | SCK OUTPUT   | SPI SLAVE OUTPUT | SPI MSTR OUTPUT | 0            |

| DIEOE          | 0            | 0                | 0               | 0            |

| DIEOV          | 0            | 0                | 0               | 0            |

| DI             | SCK INPUT    | SPI MSTR INPUT   | SPI SLAVE INPUT | SPI SS       |

| AIO            | _            | _                | _               | _            |

Table 26.

Overriding Signals for Alternate Functions in PB7..PB4

Table 27.

Overriding Signals for Alternate Functions in PB3..PB0

| Signal<br>Name | PB3/OC0/AIN1 | PB2/INT2/AIN0 | PB1/T1   | РВ0/Т0/ХСК         |

|----------------|--------------|---------------|----------|--------------------|

| PUOE           | 0            | 0             | 0        | 0                  |

| PUOV           | 0            | 0             | 0        | 0                  |

| DDOE           | 0            | 0             | 0        | 0                  |

| DDOV           | 0            | 0             | 0        | 0                  |

| PVOE           | OC0 ENABLE   | 0             | 0        | UMSEL              |

| PVOV           | OC0          | 0             | 0        | XCK OUTPUT         |

| DIEOE          | 0            | INT2 ENABLE   | 0        | 0                  |

| DIEOV          | 0            | 1             | 0        | 0                  |

| DI             | -            | INT2 INPUT    | T1 INPUT | XCK INPUT/T0 INPUT |

| AIO            | AIN1 INPUT   | AIN0 INPUT    | _        | _                  |

### Register Description for I/O Ports

| Port A Data | Register – |

|-------------|------------|

|-------------|------------|

| PORTA                  | Bit           | 7         | 6        | 5      | 4         | 3      | 2         | 1        | 0      |       |

|------------------------|---------------|-----------|----------|--------|-----------|--------|-----------|----------|--------|-------|

|                        |               | PORTA7    | PORTA6   | PORTA5 | PORTA4    | PORTA3 | PORTA2    | PORTA1   | PORTA0 | PORTA |

|                        | Read/Write    | R/W       | R/W      | R/W    | R/W       | R/W    | R/W       | R/W      | R/W    |       |

|                        | Initial Value | 0         | 0        | 0      | 0         | 0      | 0         | 0        | 0      |       |

| Port A Data Direction  |               |           |          |        |           |        |           |          |        |       |

| Register – DDRA        | Bit           | 7         | 6        | 5      | 4         | 3      | 2         | 1        | 0      |       |

|                        | ы             | ,<br>DDA7 | DDA6     | DDA5   | 4<br>DDA4 | DDA3   | ∠<br>DDA2 | DDA1     | DDA0   | DDRA  |

|                        | Read/Write    | R/W       | R/W      | R/W    | R/W       | R/W    | R/W       | R/W      | R/W    | DDRA  |

|                        | Initial Value | 0         | 0        | 0      | 0         | 0      | 0         | 0        | 0      |       |

|                        |               | 0         | 0        | 0      | 0         | 0      | 0         | 0        | 0      |       |

| Port A Input Pins      |               |           |          |        |           |        |           |          |        |       |

| Address – PINA         |               | _         | _        | _      | _         | _      | _         |          | _      |       |

|                        | Bit           | 7         | 6        | 5      | 4         | 3      | 2         | 1        | 0      |       |

|                        | D 1447.1      | PINA7     | PINA6    | PINA5  | PINA4     | PINA3  | PINA2     | PINA1    | PINA0  | PINA  |

|                        | Read/Write    | R<br>N/A  | R<br>N/A | R      | R         | R      | R<br>N/A  | R<br>N/A | R      |       |

|                        | Initial Value | N/A       | N/A      | N/A    | N/A       | N/A    | IN/A      | N/A      | N/A    |       |

| Port B Data Register – |               |           |          |        |           |        |           |          |        |       |

| PORTB                  | Bit           | 7         | 6        | 5      | 4         | 3      | 2         | 1        | 0      |       |

|                        |               | PORTB7    | PORTB6   | PORTB5 | PORTB4    | PORTB3 | PORTB2    | PORTB1   | PORTB0 | PORTB |

|                        | Read/Write    | R/W       | R/W      | R/W    | R/W       | R/W    | R/W       | R/W      | R/W    |       |

|                        | Initial Value | 0         | 0        | 0      | 0         | 0      | 0         | 0        | 0      |       |

|                        |               |           |          |        |           |        |           |          |        |       |

| Port B Data Direction  |               |           |          |        |           |        |           |          |        |       |

| Register – DDRB        | Bit           | 7         | 6        | 5      | 4         | 3      | 2         | 1        | 0      |       |

|                        |               | DDB7      | DDB6     | DDB5   | DDB4      | DDB3   | DDB2      | DDB1     | DDB0   | DDRB  |

|                        | Read/Write    | R/W       | R/W      | R/W    | R/W       | R/W    | R/W       | R/W      | R/W    |       |

|                        | Initial Value | 0         | 0        | 0      | 0         | 0      | 0         | 0        | 0      |       |

|                        |               |           |          |        |           |        |           |          |        |       |

| Port B Input Pins      |               |           |          |        |           |        |           |          |        |       |

| Address – PINB         | Bit           | 7         | 6        | 5      | 4         | 3      | 2         | 1        | 0      |       |

|                        |               | PINB7     | PINB6    | PINB5  | PINB4     | PINB3  | PINB2     | PINB1    | PINB0  | PINB  |

|                        | Read/Write    | R         | R        | R      | R         | R      | R         | R        | R      |       |

|                        | Initial Value | N/A       | N/A      | N/A    | N/A       | N/A    | N/A       | N/A      | N/A    |       |

### Input Capture Unit

The Timer/Counter incorporates an Input Capture unit that can capture external events and give them a time-stamp indicating time of occurrence. The external signal indicating an event, or multiple events, can be applied via the ICP1 pin or alternatively, via the Analog Comparator unit. The time-stamps can then be used to calculate frequency, duty-cycle, and other features of the signal applied. Alternatively the time-stamps can be used for creating a log of the events.

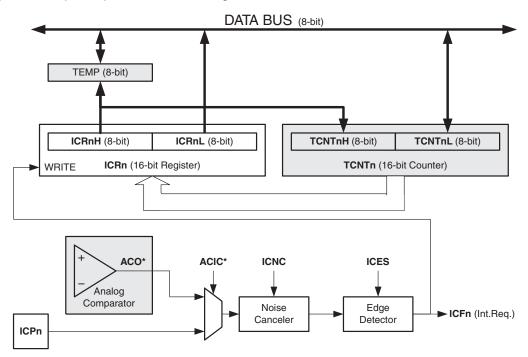

The Input Capture unit is illustrated by the block diagram shown in Figure 42. The elements of the block diagram that are not directly a part of the Input Capture unit are gray shaded. The small "n" in register and bit names indicates the Timer/Counter number.

Figure 42. Input Capture Unit Block Diagram

When a change of the logic level (an event) occurs on the *Input Capture pin* (ICP1), alternatively on the *Analog Comparator output* (ACO), and this change confirms to the setting of the edge detector, a capture will be triggered. When a capture is triggered, the 16-bit value of the counter (TCNT1) is written to the *Input Capture Register* (ICR1). The *Input Capture Flag* (ICF1) is set at the same system clock as the TCNT1 value is copied into ICR1 Register. If enabled (TICIE1 = 1), the Input Capture Flag generates an Input Capture Interrupt. The ICF1 Flag is automatically cleared when the interrupt is executed. Alternatively the ICF1 Flag can be cleared by software by writing a logical one to its I/O bit location.

Reading the 16-bit value in the *Input Capture Register* (ICR1) is done by first reading the Low byte (ICR1L) and then the High byte (ICR1H). When the Low byte is read the High byte is copied into the High byte temporary register (TEMP). When the CPU reads the ICR1H I/O location it will access the TEMP Register.

The ICR1 Register can only be written when using a Waveform Generation mode that utilizes the ICR1 Register for defining the counter's TOP value. In these cases the *Waveform Generation mode* (WGM13:0) bits must be set before the TOP value can be written to the ICR1 Register. When writing the ICR1 Register the High byte must be written to the ICR1H I/O location before the Low byte is written to ICR1L.

### 8-bit Timer/Counter2 with PWM and Asynchronous Operation

Timer/Counter2 is a general purpose, single compare unit, 8-bit Timer/Counter module. The main features are:

- Single Compare unit Counter

- Clear Timer on Compare Match (Auto Reload)

- Glitch-free, Phase Correct Pulse Width Modulator (PWM)

- Frequency Generator

- 10-bit Clock Prescaler

- Overflow and Compare Match Interrupt Sources (TOV2 and OCF2)

- Allows clocking from External 32 kHz Watch Crystal Independent of the I/O Clock

### **Overview**

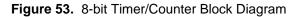

A simplified block diagram of the 8-bit Timer/Counter is shown in Figure 53. For the actual placement of I/O pins, refer to "Pinout ATmega16" on page 2. CPU accessible I/O Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit locations are listed in the "8-bit Timer/Counter Register Description" on page 128.

#### Registers

The Timer/Counter (TCNT2) and Output Compare Register (OCR2) are 8-bit registers. Interrupt request (shorten as Int.Req.) signals are all visible in the Timer Interrupt Flag Register (TIFR). All interrupts are individually masked with the Timer Interrupt Mask Register (TIMSK). TIFR and TIMSK are not shown in the figure since these registers are shared by other timer units.

The Timer/Counter can be clocked internally, via the prescaler, or asynchronously clocked from the TOSC1/2 pins, as detailed later in this section. The asynchronous operation is controlled by the Asynchronous Status Register (ASSR). The Clock Select logic block controls which clock source the Timer/Counter uses to increment (or decrement) its value. The Timer/Counter is inactive when no clock source is selected. The output from the Clock Select logic is referred to as the timer clock ( $clk_{T2}$ ).

The double buffered Output Compare Register (OCR2) is compared with the Timer/Counter value at all times. The result of the compare can be used by the waveform generator to generate a PWM or variable frequency output on the Output Compare Pin (OC2). See "Output Compare Unit" on page 119. for details. The compare match event will also set the Compare Flag (OCF2) which can be used to generate an output compare interrupt request.

**Definitions** Many register and bit references in this document are written in general form. A lower case "n" replaces the Timer/Counter number, in this case 2. However, when using the register or bit defines in a program, the precise form must be used (that is, TCNT2 for accessing Timer/Counter2 counter value and so on). The definitions in Table 49 are also used extensively throughout the document.

Table 49.

Definitions

| BOTTOM | The counter reaches the BOTTOM when it becomes zero (0x00).                                                                                                                                                                                                  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX    | The counter reaches its MAXimum when it becomes 0xFF (decimal 255).                                                                                                                                                                                          |

| ТОР    | The counter reaches the TOP when it becomes equal to the highest value in the count sequence. The TOP value can be assigned to be the fixed value 0xFF (MAX) or the value stored in the OCR2 Register. The assignment is dependent on the mode of operation. |

- Timer/Counter<br/>Clock SourcesThe Timer/Counter can be clocked by an internal synchronous or an external asynchronous<br/>clock source. The clock source  $clk_{T2}$  is by default equal to the MCU clock,  $clk_{I/O}$ . When the AS2<br/>bit in the ASSR Register is written to logic one, the clock source is taken from the Timer/Counter<br/>Oscillator connected to TOSC1 and TOSC2. For details on asynchronous operation, see "Asyn-<br/>chronous Status Register ASSR" on page 131. For details on clock sources and prescaler, see<br/>"Timer/Counter Prescaler" on page 134.

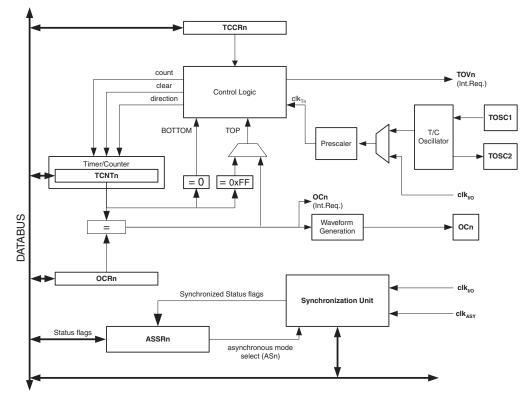

- **Counter Unit** The main part of the 8-bit Timer/Counter is the programmable bi-directional counter unit. Figure 54 shows a block diagram of the counter and its surrounding environment.

Figure 54. Counter Unit Block Diagram

Signal description (internal signals):

| count             | Increment or decrement TCNT2 by 1.               |

|-------------------|--------------------------------------------------|

| direction         | Selects between increment and decrement.         |

| clear             | Clear TCNT2 (set all bits to zero).              |

| clk <sub>T2</sub> | Timer/Counter clock.                             |

| top               | Signalizes that TCNT2 has reached maximum value. |

frame. The Shift Register is loaded with new data if it is in idle state (no ongoing transmission) or immediately after the last stop bit of the previous frame is transmitted. When the Shift Register is loaded with new data, it will transfer one complete frame at the rate given by the Baud Register, U2X bit or by XCK depending on mode of operation.

The following code examples show a simple USART transmit function based on polling of the *Data Register Empty* (UDRE) Flag. When using frames with less than eight bits, the most significant bits written to the UDR are ignored. The USART has to be initialized before the function can be used. For the assembly code, the data to be sent is assumed to be stored in Register R16

Assembly Code Example<sup>(1)</sup>

```

USART_Transmit:

; Wait for empty transmit buffer

sbis UCSRA,UDRE

rjmp USART_Transmit

; Put data (r16) into buffer, sends the data

out UDR,r16

ret

```

C Code Example<sup>(1)</sup>

```

void USART_Transmit( unsigned char data )

{

/* Wait for empty transmit buffer */

while ( !( UCSRA & (1<<UDRE)) )

;

/* Put data into buffer, sends the data */

UDR = data;

}</pre>

```

Note: 1. See "About Code Examples" on page 7.

The function simply waits for the transmit buffer to be empty by checking the UDRE Flag, before loading it with new data to be transmitted. If the Data Register Empty Interrupt is utilized, the interrupt routine writes the data into the buffer.

### Accessing UBRRH/ UCSRC Registers

The UBRRH Register shares the same I/O location as the UCSRC Register. Therefore some special consideration must be taken when accessing this I/O location.

Write Access

When doing a write access of this I/O location, the high bit of the value written, the USART Register Select (URSEL) bit, controls which one of the two registers that will be written. If URSEL is zero during a write operation, the UBRRH value will be updated. If URSEL is one, the UCSRC setting will be updated.

The following code examples show how to access the two registers.

| Assembly Code Example <sup>(1)</sup>                                  |

|-----------------------------------------------------------------------|

|                                                                       |

| ; Set UBRRH to 2                                                      |

| <b>ldi</b> r16,0x02                                                   |

| out UBRRH,r16                                                         |

|                                                                       |

| ; Set the USBS and the UCSZ1 bit to one, and                          |

| ; the remaining bits to zero.                                         |

| ldi r16, (1< <ursel) (1<<ucsz1)<="" (1<<usbs)="" th=""  =""></ursel)> |

| out UCSRC,r16                                                         |

|                                                                       |

| Code Example <sup>(1)</sup>                                           |

|                                                                       |

| /* Set UBRRH to 2 */                                                  |

| UBRRH = $0x02;$                                                       |

|                                                                       |

| /* Set the USBS and the UCSZ1 bit to one, and */                      |

| /* the remaining bits to zero. */                                     |

| UCSRC = (1< <ursel) (1<<ucsz1);<="" (1<<usbs)="" th=""  =""></ursel)> |

|                                                                       |

Note: 1. See "About Code Examples" on page 7.

As the code examples illustrate, write accesses of the two registers are relatively unaffected of the sharing of I/O location.

**Read Access** Doing a read access to the UBRRH or the UCSRC Register is a more complex operation. However, in most applications, it is rarely necessary to read any of these registers.

> The read access is controlled by a timed sequence. Reading the I/O location once returns the UBRRH Register contents. If the register location was read in previous system clock cycle, reading the register in the current clock cycle will return the UCSRC contents. Note that the timed sequence for reading the UCSRC is an atomic operation. Interrupts must therefore be controlled (for example by disabling interrupts globally) during the read operation.

| Status Code                                                                              |                                                               | Application Software Response |     |     |       |      |                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------|-----|-----|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (TWSR) Status of the Two-wire Serial Bus<br>Prescaler Bits and Two-wire Serial Interface |                                                               | To TWCR                       |     |     | TWCR  |      |                                                                                                                                                                                          |

| are 0                                                                                    | Hardware                                                      | To/from TWDR                  | STA | STO | TWINT | TWEA | Next Action Taken by TWI Hardware                                                                                                                                                        |

| \$A8                                                                                     | \$A8 Own SLA+R has been received;<br>ACK has been returned    |                               | х   | 0   | 1     | 0    | Last data byte will be transmitted and NOT ACK should be received                                                                                                                        |

|                                                                                          |                                                               | Load data byte                | Х   | 0   | 1     | 1    | Data byte will be transmitted and ACK should be re-<br>ceived                                                                                                                            |

| \$B0                                                                                     | Arbitration lost in SLA+R/W as Master; own SLA+R has been     | Load data byte or             | Х   | 0   | 1     | 0    | Last data byte will be transmitted and NOT ACK should be received                                                                                                                        |

|                                                                                          | received; ACK has been returned                               | Load data byte                | х   | 0   | 1     | 1    | Data byte will be transmitted and ACK should be re-<br>ceived                                                                                                                            |

| \$B8                                                                                     | Data byte in TWDR has been transmitted; ACK has been          | Load data byte or             | Х   | 0   | 1     | 0    | Last data byte will be transmitted and NOT ACK should be received                                                                                                                        |

|                                                                                          | received                                                      | Load data byte                | х   | 0   | 1     | 1    | Data byte will be transmitted and ACK should be re-<br>ceived                                                                                                                            |

| \$C0                                                                                     | Data byte in TWDR has been transmitted; NOT ACK has been      | No TWDR action or             | 0   | 0   | 1     | 0    | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA                                                                                                            |

|                                                                                          | received                                                      | No TWDR action or             | 0   | 0   | 1     | 1    | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1"                                                                        |

|                                                                                          |                                                               | No TWDR action or             | 1   | 0   | 1     | 0    | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA;<br>a START condition will be transmitted when the bus<br>becomes free                                     |

|                                                                                          |                                                               | No TWDR action                | 1   | 0   | 1     | 1    | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1";<br>a START condition will be transmitted when the bus<br>becomes free |

| \$C8                                                                                     | Last data byte in TWDR has been transmitted (TWEA = "0"); ACK | No TWDR action or             | 0   | 0   | 1     | 0    | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA                                                                                                            |

|                                                                                          | has been received                                             | No TWDR action or             | 0   | 0   | 1     | 1    | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1"                                                                        |

|                                                                                          |                                                               | No TWDR action or             | 1   | 0   | 1     | 0    | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA;<br>a START condition will be transmitted when the bus<br>becomes free                                     |

|                                                                                          |                                                               | No TWDR action                | 1   | 0   | 1     | 1    | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1";<br>a START condition will be transmitted when the bus<br>becomes free |

### Table 77. Status Codes for Slave Transmitter Mode

becomes the analog input to the ADC. If single ended channels are used, the gain amplifier is bypassed altogether.

The ADC is enabled by setting the ADC Enable bit, ADEN in ADCSRA. Voltage reference and input channel selections will not go into effect until ADEN is set. The ADC does not consume power when ADEN is cleared, so it is recommended to switch off the ADC before entering power saving sleep modes.

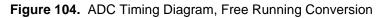

The ADC generates a 10-bit result which is presented in the ADC Data Registers, ADCH and ADCL. By default, the result is presented right adjusted, but can optionally be presented left adjusted by setting the ADLAR bit in ADMUX.

If the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH, to ensure that the content of the Data Registers belongs to the same conversion. Once ADCL is read, ADC access to Data Registers is blocked. This means that if ADCL has been read, and a conversion completes before ADCH is read, neither register is updated and the result from the conversion is lost. When ADCH is read, ADC access to the ADCH and ADCL Registers is re-enabled.

The ADC has its own interrupt which can be triggered when a conversion completes. When ADC access to the Data Registers is prohibited between reading of ADCH and ADCL, the interrupt will trigger even if the result is lost.

# Starting a Conversion

A single conversion is started by writing a logical one to the ADC Start Conversion bit, ADSC. This bit stays high as long as the conversion is in progress and will be cleared by hardware when the conversion is completed. If a different data channel is selected while a conversion is in progress, the ADC will finish the current conversion before performing the channel change.

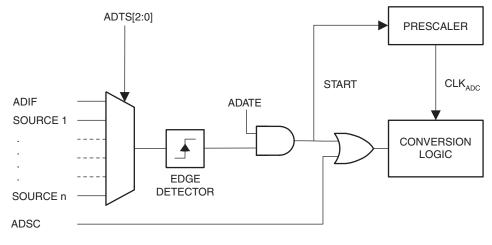

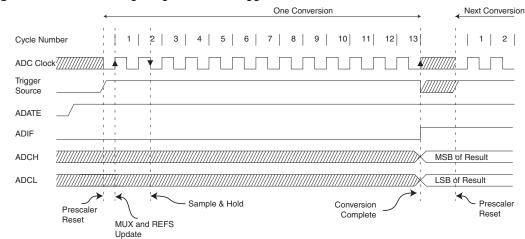

Alternatively, a conversion can be triggered automatically by various sources. Auto Triggering is enabled by setting the ADC Auto Trigger Enable bit, ADATE in ADCSRA. The trigger source is selected by setting the ADC Trigger Select bits, ADTS in SFIOR (see description of the ADTS bits for a list of the trigger sources). When a positive edge occurs on the selected trigger signal, the ADC prescaler is reset and a conversion is started. This provides a method of starting conversions at fixed intervals. If the trigger signal still is set when the conversion completes, a new conversion will not be started. If another positive edge occurs on the trigger signal during conversion, the edge will be ignored. Note that an Interrupt Flag will be set even if the specific interrupt is disabled or the global interrupt enable bit in SREG is cleared. A conversion can thus be triggered without causing an interrupt. However, the Interrupt Flag must be cleared in order to trigger a new conversion at the next interrupt event.

#### Figure 99. ADC Auto Trigger Logic

Figure 103. ADC Timing Diagram, Auto Triggered Conversion

### Table 81. ADC Conversion Time

| Condition                        | Sample & Hold (Cycles<br>from Start of<br>Conversion) | Conversion Time (Cycles) |

|----------------------------------|-------------------------------------------------------|--------------------------|

| First conversion                 | 13.5                                                  | 25                       |

| Normal conversions, single ended | 1.5                                                   | 13                       |

| Auto Triggered conversions       | 2                                                     | 13.5                     |

| Normal conversions, differential | 1.5/2.5                                               | 13/14                    |

### Differential Gain Channels

When using differential gain channels, certain aspects of the conversion need to be taken into consideration.

Differential conversions are synchronized to the internal clock  $CK_{ADC2}$  equal to half the ADC clock. This synchronization is done automatically by the ADC interface in such a way that the sample-and-hold occurs at a specific phase of  $CK_{ADC2}$ . A conversion initiated by the user (that is,

| ADC Input Channels       | When changing channel selections, the user should observe the following guidelines to ensure that the correct channel is selected:                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | In Single Conversion mode, always select the channel before starting the conversion. The chan-<br>nel selection may be changed one ADC clock cycle after writing one to ADSC. However, the<br>simplest method is to wait for the conversion to complete before changing the channel selection.                                                                                                                                                                                                                                                                           |

|                          | In Free Running mode, always select the channel before starting the first conversion. The chan-<br>nel selection may be changed one ADC clock cycle after writing one to ADSC. However, the<br>simplest method is to wait for the first conversion to complete, and then change the channel<br>selection. Since the next conversion has already started automatically, the next result will reflect<br>the previous channel selection. Subsequent conversions will reflect the new channel selection.                                                                    |

|                          | When switching to a differential gain channel, the first conversion result may have a poor accuracy due to the required settling time for the automatic offset cancellation circuitry. The user should preferably disregard the first conversion result.                                                                                                                                                                                                                                                                                                                 |

| ADC Voltage<br>Reference | The reference voltage for the ADC ( $V_{REF}$ ) indicates the conversion range for the ADC. Single ended channels that exceed $V_{REF}$ will result in codes close to 0x3FF. $V_{REF}$ can be selected as either AVCC, internal 2.56V reference, or external AREF pin.                                                                                                                                                                                                                                                                                                   |

|                          | AVCC is connected to the ADC through a passive switch. The internal 2.56V reference is generated from the internal bandgap reference ( $V_{BG}$ ) through an internal amplifier. In either case, the external AREF pin is directly connected to the ADC, and the reference voltage can be made more immune to noise by connecting a capacitor between the AREF pin and ground. $V_{REF}$ can also be measured at the AREF pin with a high impedant voltmeter. Note that $V_{REF}$ is a high impedant source, and only a capacitive load should be connected in a system. |

|                          | If the user has a fixed voltage source connected to the AREF pin, the user may not use the other reference voltage options in the application, as they will be shorted to the external voltage. If no external voltage is applied to the AREF pin, the user may switch between AVCC and 2.56V as reference selection. The first ADC conversion result after switching reference voltage source may be inaccurate, and the user is advised to discard this result.                                                                                                        |

|                          | If differential channels are used, the selected reference should not be closer to AVCC than indicated in Table 122 on page 297.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ADC Noise<br>Canceler    | The ADC features a noise canceler that enables conversion during sleep mode to reduce noise induced from the CPU core and other I/O peripherals. The noise canceler can be used with ADC Noise Reduction and Idle mode. To make use of this feature, the following procedure should be used:                                                                                                                                                                                                                                                                             |

|                          | <ol> <li>Make sure that the ADC is enabled and is not busy converting. Single Conversion<br/>Mode must be selected and the ADC conversion complete interrupt must be<br/>enabled.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                             |

|                          | <ol><li>Enter ADC Noise Reduction mode (or Idle mode). The ADC will start a conversion<br/>once the CPU has been halted.</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                          | 3. If no other interrupts occur before the ADC conversion completes, the ADC interrupt will wake up the CPU and execute the ADC Conversion Complete interrupt routine. If another interrupt wakes up the CPU before the ADC conversion is complete, that interrupt will be executed, and an ADC Conversion Complete interrupt request will be generated when the ADC conversion completes. The CPU will remain in active mode until a new sleep command is executed.                                                                                                     |

|                          | Note that the ADC will not be automatically turned off when entering other sleep modes than Idle mode and ADC Noise Reduction mode. The user is advised to write zero to ADEN before enter-                                                                                                                                                                                                                                                                                                                                                                              |

Noise Reduction mode. The user is advised to write zero to nter ing such sleep modes to avoid excessive power consumption. If the ADC is enabled in such

A debugger, like the AVR Studio, may however use one or more of these resources for its internal purpose, leaving less flexibility to the end-user.

A list of the On-chip Debug specific JTAG instructions is given in "On-chip Debug Specific JTAG Instructions" on page 226.

The JTAGEN Fuse must be programmed to enable the JTAG Test Access Port. In addition, the OCDEN Fuse must be programmed and no Lock bits must be set for the On-chip Debug system to work. As a security feature, the On-chip Debug system is disabled when *any* Lock bits are set. Otherwise, the On-chip Debug system would have provided a back-door into a secured device.

The AVR JTAG ICE from Atmel is a powerful development tool for On-chip Debugging of all AVR 8-bit RISC Microcontrollers with IEEE 1149.1 compliant JTAG interface. The JTAG ICE and the AVR Studio user interface give the user complete control of the internal resources of the microcontroller, helping to reduce development time by making debugging easier. The JTAG ICE performs real-time emulation of the microcontroller while it is running in a target system.

Please refer to the Support Tools section on the AVR pages on www.atmel.com for a full description of the AVR JTEG ICE. AVR Studio can be downloaded free from Software section on the same web site.

All necessary execution commands are available in AVR Studio, both on source level and on disassembly level. The user can execute the program, single step through the code either by tracing into or stepping over functions, step out of functions, place the cursor on a statement and execute until the statement is reached, stop the execution, and reset the execution target. In addition, the user can have an unlimited number of code breakpoints (using the BREAK instruction) and up to two data memory breakpoints, alternatively combined as a mask (range) Break Point.

| On-chip Debug<br>Specific JTAG<br>Instructions | The On-chip Debug support is considered being private JTAG instructions, and distributed within ATMEL and to selected third party vendors only. Instruction opcodes are listed for reference. |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRIVATE0; \$8                                  | Private JTAG instruction for accessing On-chip Debug system.                                                                                                                                  |

| PRIVATE1; \$9                                  | Private JTAG instruction for accessing On-chip Debug system.                                                                                                                                  |

| PRIVATE2; \$A                                  | Private JTAG instruction for accessing On-chip Debug system.                                                                                                                                  |

| PRIVATE3; \$B                                  | Private JTAG instruction for accessing On-chip Debug system.                                                                                                                                  |

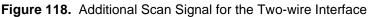

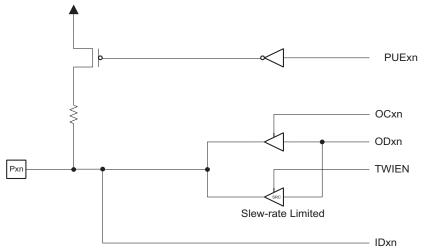

Scanning the RESETThe RESET pin accepts 5V active low logic for standard reset operation, and 12V active high<br/>logic for High Voltage Parallel Programming. An observe-only cell as shown in Figure 119 is<br/>inserted both for the 5V reset signal; RSTT, and the 12V reset signal; RSTHV.

Figure 119. Observe-only Cell

# Scanning the Clock Pins

The AVR devices have many clock options selectable by fuses. These are: Internal RC Oscillator, External RC, External Clock, (High Frequency) Crystal Oscillator, Low Frequency Crystal Oscillator, and Ceramic Resonator.

Figure 120 shows how each Oscillator with external connection is supported in the scan chain. The Enable signal is supported with a general boundary-scan cell, while the Oscillator/Clock output is attached to an observe-only cell. In addition to the main clock, the Timer Oscillator is scanned in the same way. The output from the internal RC Oscillator is not scanned, as this Oscillator does not have external connections.

| Symbol               | Parameter                                            | Min | Тур | Мах | Units |  |

|----------------------|------------------------------------------------------|-----|-----|-----|-------|--|

| t <sub>DVXH</sub>    | Data and Control Valid before XTAL1 High             | 67  |     |     |       |  |

| t <sub>XLXH</sub>    | XTAL1 Low to XTAL1 High                              | 200 |     |     |       |  |

| t <sub>XHXL</sub>    | XTAL1 Pulse Width High                               | 150 |     |     |       |  |

| t <sub>XLDX</sub>    | Data and Control Hold after XTAL1 Low                | 67  |     |     |       |  |

| t <sub>XLWL</sub>    | XTAL1 Low to WR Low                                  | 0   |     |     |       |  |

| t <sub>XLPH</sub>    | XTAL1 Low to PAGEL high                              | 0   |     |     |       |  |

| t <sub>PLXH</sub>    | PAGEL low to XTAL1 high                              | 150 |     |     |       |  |

| t <sub>BVPH</sub>    | BS1 Valid before PAGEL High                          | 67  |     |     | ns    |  |

| t <sub>PHPL</sub>    | PAGEL Pulse Width High                               | 150 |     |     |       |  |

| t <sub>PLBX</sub>    | BS1 Hold after PAGEL Low                             | 67  |     |     |       |  |

| t <sub>WLBX</sub>    | BS2/1 Hold after WR Low                              | 67  |     |     |       |  |

| t <sub>PLWL</sub>    | PAGEL Low to WR Low                                  | 67  |     |     |       |  |

| t <sub>BVWL</sub>    | BS1 Valid to WR Low                                  | 67  |     |     |       |  |

| t <sub>WLWH</sub>    | WR Pulse Width Low                                   | 150 |     |     |       |  |

| t <sub>WLRL</sub>    | WR Low to RDY/BSY Low                                | 0   |     | 1   | μS    |  |

| t <sub>WLRH</sub>    | WR Low to RDY/BSY High <sup>(1)</sup>                | 3.7 |     | 4.5 |       |  |

| t <sub>WLRH_CE</sub> | WR Low to RDY/BSY High for Chip Erase <sup>(2)</sup> | 7.5 |     | 9   | ms    |  |

| t <sub>XLOL</sub>    | XTAL1 Low to OE Low                                  | 0   |     |     |       |  |

| t <sub>BVDV</sub>    | BS1 Valid to DATA valid                              | 0   |     | 250 | ns    |  |

| t <sub>OLDV</sub>    | OE Low to DATA Valid                                 |     |     | 250 |       |  |

| t <sub>OHDZ</sub>    | OE High to DATA Tri-stated                           |     |     | 250 |       |  |

| Table 113. Parallel Program | mming Characteristics, | $V_{\rm CC} = 5V \pm 10\%$ | (Continued) |

|-----------------------------|------------------------|----------------------------|-------------|

|-----------------------------|------------------------|----------------------------|-------------|

Notes: 1. t<sub>WLRH</sub> is valid for the Write Flash, Write EEPROM, Write Fuse bits and Write Lock bits commands.

2.  $t_{WLRH CE}$  is valid for the Chip Erase command.

### Serial Downloading

Both the Flash and EEPROM memory arrays can be programmed using the serial SPI bus while RESET is pulled to GND. The serial interface consists of pins SCK, MOSI (input), and MISO (output). After RESET is set low, the Programming Enable instruction needs to be executed first before program/erase operations can be executed. NOTE, in Table 114 on page 273, the pin mapping for SPI programming is listed. Not all parts use the SPI pins dedicated for the internal SPI interface.

### SPI Serial Programming Pin Mapping

#### Table 114. Pin Mapping SPI Serial Programming

| Symbol | Pins | I/O | Description     |

|--------|------|-----|-----------------|

| MOSI   | PB5  | Ι   | Serial Data in  |

| MISO   | PB6  | 0   | Serial Data out |

| SCK    | PB7  | Ι   | Serial Clock    |

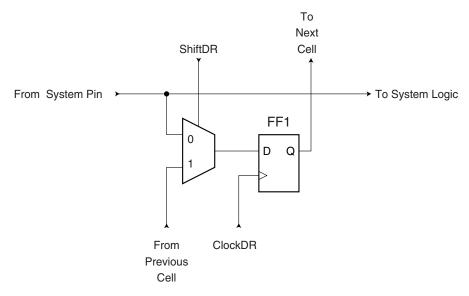

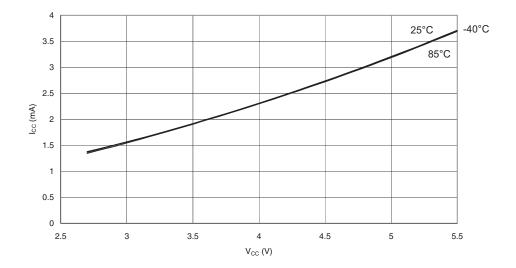

Figure 158. Idle Supply Current vs.  $V_{CC}$  (Internal RC Oscillator, 8 MHz)

Figure 159. Idle Supply Current vs.  $V_{CC}$  (Internal RC Oscillator, 4 MHz)

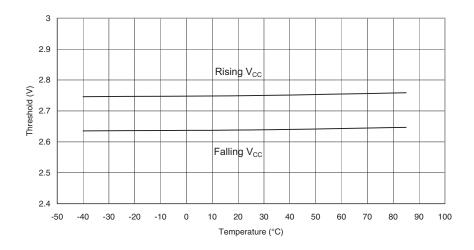

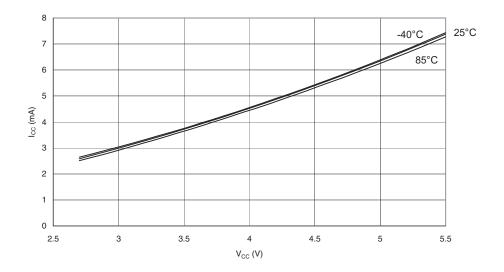

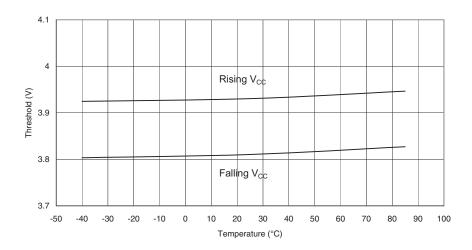

Figure 188. Bod Thresholds vs. Temperature (Bodlevel is 4.0V)

Bod Thresholds And Analog Comparator Offset

Figure 189. Bod Thresholds vs. Temperature (Bodlevel is 2.7V)