Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | AVR                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 32                                                        |

| Program Memory Size        | 16KB (8K x 16)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 512 x 8                                                   |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-TQFP                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atmega16l-8aqr |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

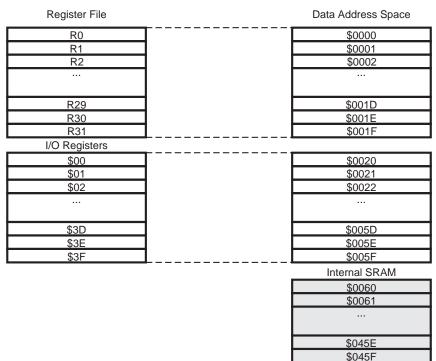

## SRAM Data Memory

Figure 9 shows how the ATmega16 SRAM Memory is organized.

The lower 1120 Data Memory locations address the Register File, the I/O Memory, and the internal data SRAM. The first 96 locations address the Register File and I/O Memory, and the next 1024 locations address the internal data SRAM.

The five different addressing modes for the data memory cover: Direct, Indirect with Displacement, Indirect, Indirect with Pre-decrement, and Indirect with Post-increment. In the Register File, registers R26 to R31 feature the indirect addressing pointer registers.

The direct addressing reaches the entire data space.

The Indirect with Displacement mode reaches 63 address locations from the base address given by the Y-register or Z-register.

When using register indirect addressing modes with automatic pre-decrement and post-increment, the address registers X, Y, and Z are decremented or incremented.

The 32 general purpose working registers, 64 I/O Registers, and the 1024 bytes of internal data SRAM in the ATmega16 are all accessible through all these addressing modes. The Register File is described in "General Purpose Register File" on page 11.

#### Figure 9. Data Memory Map

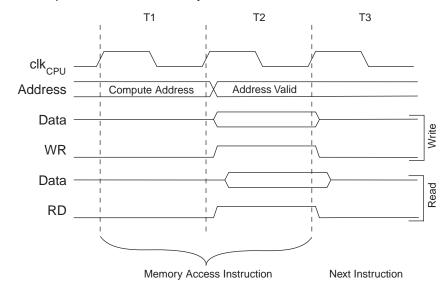

Data Memory Access Times

**s** This section describes the general access timing concepts for internal memory access. The internal data SRAM access is performed in two clk<sub>CPU</sub> cycles as described in Figure 10.

#### Figure 10. On-chip Data SRAM Access Cycles

EEPROM DataThe ATmega16 contains 512 bytes of data EEPROM memory. It is organized as a separate data<br/>space, in which single bytes can be read and written. The EEPROM has an endurance of at<br/>least 100,000 write/erase cycles. The access between the EEPROM and the CPU is described<br/>in the following, specifying the EEPROM Address Registers, the EEPROM Data Register, and<br/>the EEPROM Control Register.

For a detailed description of SPI, JTAG, and Parallel data downloading to the EEPROM, see page 273, page 278, and page 262, respectively.

**EEPROM Read/Write** The EEPROM Access Registers are accessible in the I/O space.

The write access time for the EEPROM is given in Table 1. A self-timing function, however, lets the user software detect when the next byte can be written. If the user code contains instructions that write the EEPROM, some precautions must be taken. In heavily filtered power supplies,  $V_{CC}$  is likely to rise or fall slowly on Power-up/down. This causes the device for some period of time to run at a voltage lower than specified as minimum for the clock frequency used. See "Preventing EEPROM Corruption" on page 22 for details on how to avoid problems in these situations.

In order to prevent unintentional EEPROM writes, a specific write procedure must be followed. Refer to the description of the EEPROM Control Register for details on this.

When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed. When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed.

Access

## The EEPROM Address

Register – EEARH and EEARL

| Bit           | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |       |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|               | -     | -     | -     | -     | -     | -     | -     | EEAR8 | EEARH |

|               | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEARL |

|               | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |       |

| Read/Write    | R     | R     | R     | R     | R     | R     | R     | R/W   |       |

|               | R/W   |       |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | Х     |       |

|               | Х     | х     | Х     | Х     | Х     | х     | Х     | Х     |       |

#### • Bits 15..9 - Res: Reserved Bits

These bits are reserved bits in the ATmega16 and will always read as zero.

#### • Bits 8..0 - EEAR8..0: EEPROM Address

The EEPROM Address Registers – EEARH and EEARL – specify the EEPROM address in the 512 bytes EEPROM space. The EEPROM data bytes are addressed linearly between 0 and 511. The initial value of EEAR is undefined. A proper value must be written before the EEPROM may be accessed.

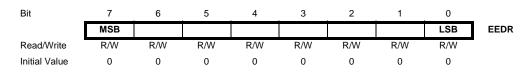

#### The EEPROM Data Register – EEDR

#### • Bits 7..0 - EEDR7.0: EEPROM Data

For the EEPROM write operation, the EEDR Register contains the data to be written to the EEPROM in the address given by the EEAR Register. For the EEPROM read operation, the EEDR contains the data read out from the EEPROM at the address given by EEAR.

# The EEPROM Control Register – EECR

| Bit           | 7 | 6 | 5 | 4 | 3     | 2     | 1    | 0    | _    |

|---------------|---|---|---|---|-------|-------|------|------|------|

|               | - | - | - | - | EERIE | EEMWE | EEWE | EERE | EECR |

| Read/Write    | R | R | R | R | R/W   | R/W   | R/W  | R/W  | •    |

| Initial Value | 0 | 0 | 0 | 0 | 0     | 0     | Х    | 0    |      |

#### • Bits 7..4 - Res: Reserved Bits

These bits are reserved bits in the ATmega16 and will always read as zero.

#### • Bit 3 – EERIE: EEPROM Ready Interrupt Enable

Writing EERIE to one enables the EEPROM Ready Interrupt if the I bit in SREG is set. Writing EERIE to zero disables the interrupt. The EEPROM Ready interrupt generates a constant interrupt when EEWE is cleared.

#### • Bit 2 – EEMWE: EEPROM Master Write Enable

The EEMWE bit determines whether setting EEWE to one causes the EEPROM to be written. When EEMWE is set, setting EEWE within four clock cycles will write data to the EEPROM at the selected address If EEMWE is zero, setting EEWE will have no effect. When EEMWE has been written to one by software, hardware clears the bit to zero after four clock cycles. See the description of the EEWE bit for an EEPROM write procedure.

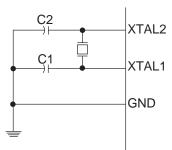

choosing capacitors for use with crystals are given in Table 4. For ceramic resonators, the capacitor values given by the manufacturer should be used.

Figure 12. Crystal Oscillator Connections

The Oscillator can operate in three different modes, each optimized for a specific frequency range. The operating mode is selected by the fuses CKSEL3..1 as shown in Table 4.

Table 4. Crystal Oscillator Operating Modes

| СКОРТ | CKSEL31            | Frequency Range<br>(MHz) | Recommended Range for Capacitors<br>C1 and C2 for Use with Crystals (pF) |

|-------|--------------------|--------------------------|--------------------------------------------------------------------------|

| 1     | 101 <sup>(1)</sup> | 0.4 - 0.9                | _                                                                        |

| 1     | 110                | 0.9 - 3.0                | 12 - 22                                                                  |

| 1     | 111                | 3.0 - 8.0                | 12 - 22                                                                  |

| 0     | 101, 110, 111      | 1.0 ≤                    | 12 - 22                                                                  |

Note: 1. This option should not be used with crystals, only with ceramic resonators.

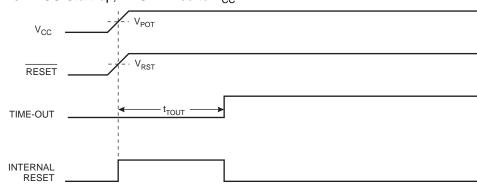

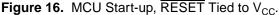

## System Control and Reset

**Resetting the AVR** During Reset, all I/O Registers are set to their initial values, and the program starts execution from the Reset Vector. The instruction placed at the Reset Vector must be a JMP – absolute jump – instruction to the reset handling routine. If the program never enables an interrupt source, the Interrupt Vectors are not used, and regular program code can be placed at these locations. This is also the case if the Reset Vector is in the Application section while the Interrupt Vectors are in the Boot section or vice versa. The circuit diagram in Figure 15 shows the reset logic. Table 15 defines the electrical parameters of the reset circuitry.

The I/O ports of the AVR are immediately reset to their initial state when a reset source goes active. This does not require any clock source to be running.

After all reset sources have gone inactive, a delay counter is invoked, stretching the Internal Reset. This allows the power to reach a stable level before normal operation starts. The time-out period of the delay counter is defined by the user through the CKSEL Fuses. The different selections for the delay period are presented in "Clock Sources" on page 25.

Reset Sources

The ATmega16 has five sources of reset:

- Power-on Reset.

- The MCU is reset when the supply voltage is below the Power-on Reset threshold (V<sub>POT</sub>).

- External Reset.

The MCU is reset when a low level is present on the RESET pin for longer than the minimum pulse length.

- Watchdog Reset. The MCU is reset when the Watchdog Timer period expires and the Watchdog is enabled.

- Brown-out Reset.

The MCU is reset when the supply voltage V<sub>CC</sub> is below the Brown-out Reset threshold (V<sub>BOT</sub>) and the Brown-out Detector is enabled.

- JTAG AVR Reset.

The MCU is reset as long as there is a logic one in the Reset Register, one of the scan chains of the JTAG system. Refer to the section "IEEE 1149.1 (JTAG) Boundary-scan" on page 228 for details.

#### **Power-on Reset**

A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The detection level is defined in Table 15. The POR is activated whenever  $V_{CC}$  is below the detection level. The POR circuit can be used to trigger the Start-up Reset, as well as to detect a failure in supply voltage.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching the Power-on Reset threshold voltage invokes the delay counter, which determines how long the device is kept in RESET after  $V_{CC}$  rise. The RESET signal is activated again, without any delay, when  $V_{CC}$  decreases below the detection level.

#### Figure 17. MCU Start-up, RESET Extended Externally

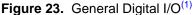

Note: 1. WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clk<sub>I/O</sub>, SLEEP, and PUD are common to all ports.

**Configuring the Pin** Each port pin consists of three register bits: DDxn, PORTxn, and PINxn. As shown in "Register Description for I/O Ports" on page 66, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits at the PORTx I/O address, and the PINxn bits at the PINx I/O address.

The DDxn bit in the DDRx Register selects the direction of this pin. If DDxn is written logic one, Pxn is configured as an output pin. If DDxn is written logic zero, Pxn is configured as an input pin.

If PORTxn is written logic one when the pin is configured as an input pin, the pull-up resistor is activated. To switch the pull-up resistor off, PORTxn has to be written logic zero or the pin has to be configured as an output pin. The port pins are tri-stated when a reset condition becomes active, even if no clocks are running.

If PORTxn is written logic one when the pin is configured as an output pin, the port pin is driven high (one). If PORTxn is written logic zero when the pin is configured as an output pin, the port pin is driven low (zero).

When switching between tri-state ( $\{DDxn, PORTxn\} = 0b00$ ) and output high ( $\{DDxn, PORTxn\} = 0b11$ ), an intermediate state with either pull-up enabled ( $\{DDxn, PORTxn\} = 0b01$ ) or output low ( $\{DDxn, PORTxn\} = 0b10$ ) must occur. Normally, the pull-up enabled state is fully acceptable, as a high-impedant environment will not notice the difference between a strong high driver and a pull-up. If this is not the case, the PUD bit in the SFIOR Register can be set to disable all pull-ups in all ports.

#### Alternate Functions of Port C

f The Port C pins with alternate functions are shown in Table 28. If the JTAG interface is enabled, the pull-up resistors on pins PC5(TDI), PC3(TMS) and PC2(TCK) will be activated even if a reset occurs.

| Table 28. | Port C Pins Alternate Functions |

|-----------|---------------------------------|

|-----------|---------------------------------|

| Port Pin | Alternate Function                               |

|----------|--------------------------------------------------|

| PC7      | TOSC2 (Timer Oscillator Pin 2)                   |

| PC6      | TOSC1 (Timer Oscillator Pin 1)                   |

| PC5      | TDI (JTAG Test Data In)                          |

| PC4      | TDO (JTAG Test Data Out)                         |

| PC3      | TMS (JTAG Test Mode Select)                      |

| PC2      | TCK (JTAG Test Clock)                            |

| PC1      | SDA (Two-wire Serial Bus Data Input/Output Line) |

| PC0      | SCL (Two-wire Serial Bus Clock Line)             |

The alternate pin configuration is as follows:

#### • TOSC2 - Port C, Bit 7

TOSC2, Timer Oscillator pin 2: When the AS2 bit in ASSR is set (one) to enable asynchronous clocking of Timer/Counter2, pin PC7 is disconnected from the port, and becomes the inverting output of the Oscillator amplifier. In this mode, a Crystal Oscillator is connected to this pin, and the pin can not be used as an I/O pin.

#### • TOSC1 - Port C, Bit 6

TOSC1, Timer Oscillator pin 1: When the AS2 bit in ASSR is set (one) to enable asynchronous clocking of Timer/Counter2, pin PC6 is disconnected from the port, and becomes the input of the inverting Oscillator amplifier. In this mode, a Crystal Oscillator is connected to this pin, and the pin can not be used as an I/O pin.

#### • TDI - Port C, Bit 5

TDI, JTAG Test Data In: Serial input data to be shifted in to the Instruction Register or Data Register (scan chains). When the JTAG interface is enabled, this pin can not be used as an I/O pin.

#### • TDO - Port C, Bit 4

TDO, JTAG Test Data Out: Serial output data from Instruction Register or Data Register. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

The TD0 pin is tri-stated unless TAP states that shifts out data are entered.

#### • TMS – Port C, Bit 3

TMS, JTAG Test Mode Select: This pin is used for navigating through the TAP-controller state machine. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

#### • TCK – Port C, Bit 2

TCK, JTAG Test Clock: JTAG operation is synchronous to TCK. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

Unit" on page 73. for details. The compare match event will also set the Compare Flag (OCF0) which can be used to generate an output compare interrupt request.

**Definitions** Many register and bit references in this document are written in general form. A lower case "n" replaces the Timer/Counter number, in this case 0. However, when using the register or bit defines in a program, the precise form must be used, that is, TCNT0 for accessing Timer/Counter0 counter value and so on.

The definitions in Table 37 are also used extensively throughout the document. **Table 37.** Definitions

| BOTTOM | The counter reaches the BOTTOM when it becomes 0x00.                                                                                                                                                                                                         |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX    | The counter reaches its MAXimum when it becomes 0xFF (decimal 255).                                                                                                                                                                                          |

| ТОР    | The counter reaches the TOP when it becomes equal to the highest value in the count sequence. The TOP value can be assigned to be the fixed value 0xFF (MAX) or the value stored in the OCR0 Register. The assignment is dependent on the mode of operation. |

**Timer/Counter Clock Sources** The Timer/Counter can be clocked by an internal or an external clock source. The clock source is selected by the clock select logic which is controlled by the clock select (CS02:0) bits located in the Timer/Counter Control Register (TCCR0). For details on clock sources and prescaler, see "Timer/Counter0 and Timer/Counter1 Prescalers" on page 87.

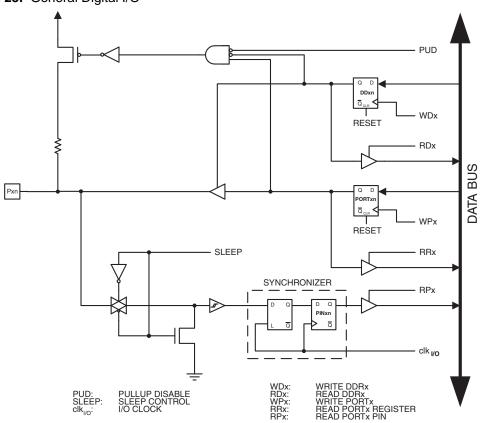

**Counter Unit** The main part of the 8-bit Timer/Counter is the programmable bi-directional counter unit. Figure 28 shows a block diagram of the counter and its surroundings.

Figure 28. Counter Unit Block Diagram

Signal description (internal signals):

| count Increment or decrement TCNT0 | by 1. |

|------------------------------------|-------|

|------------------------------------|-------|

direction Select between increment and decrement.

clear Clear TCNT0 (set all bits to zero).

**clk**<sub>Tn</sub> Timer/Counter clock, referred to as clk<sub>T0</sub> in the following.

**TOP** Signalize that TCNT0 has reached maximum value.

**BOTTOM** Signalize that TCNT0 has reached minimum value (zero).

Depending of the mode of operation used, the counter is cleared, incremented, or decremented at each timer clock ( $clk_{T0}$ ).  $clk_{T0}$  can be generated from an external or internal clock source, selected by the Clock Select bits (CS02:0). When no clock source is selected (CS02:0 = 0) the timer is stopped. However, the TCNT0 value can be accessed by the CPU, regardless of

| Modes of<br>Operation                         | The mode of operation, that is, the behavior of the Timer/Counter and the output compare pins, is defined by the combination of the <i>Waveform Generation mode</i> (WGM13:0) and <i>Compare Output mode</i> (COM1x1:0) bits. The Compare Output mode bits do not affect the counting sequence, while the Waveform Generation mode bits do. The COM1x1:0 bits control whether the PWM output generated should be inverted or not (inverted or non-inverted PWM). For non-PWM modes the COM1x1:0 bits control whether the output should be set, cleared or toggle at a compare match (See "Compare Match Output Unit" on page 100.)                                                                                                                                                                    |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                               | For detailed timing information refer to "Timer/Counter Timing Diagrams" on page 108.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Normal Mode                                   | The simplest mode of operation is the <i>Normal</i> mode (WGM13:0 = 0). In this mode the counting direction is always up (incrementing), and no counter clear is performed. The counter simply overruns when it passes its maximum 16-bit value (MAX = 0xFFFF) and then restarts from the BOTTOM (0x0000). In normal operation the <i>Timer/Counter Overflow Flag</i> (TOV1) will be set in the same timer clock cycle as the TCNT1 becomes zero. The TOV1 Flag in this case behaves like a 17th bit, except that it is only set, not cleared. However, combined with the timer overflow interrupt that automatically clears the TOV1 Flag, the timer resolution can be increased by software. There are no special cases to consider in the Normal mode, a new counter value can be written anytime. |

|                                               | The Input Capture unit is easy to use in Normal mode. However, observe that the maximum interval between the external events must not exceed the resolution of the counter. If the interval between events are too long, the timer overflow interrupt or the prescaler must be used to extend the resolution for the capture unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                               | The output compare units can be used to generate interrupts at some given time. Using the output compare to generate waveforms in Normal mode is not recommended, since this will occupy too much of the CPU time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

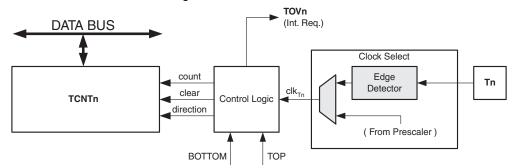

| Clear Timer on<br>Compare Match (CTC)<br>Mode | In <i>Clear Timer on Compare</i> or CTC mode (WGM13:0 = 4 or 12), the OCR1A or ICR1 Register are used to manipulate the counter resolution. In CTC mode the counter is cleared to zero when the counter value (TCNT1) matches either the OCR1A (WGM13:0 = 4) or the ICR1 (WGM13:0 = 12). The OCR1A or ICR1 define the top value for the counter, hence also its resolution. This mode allows greater control of the compare match output frequency. It also simplifies the opera-                                                                                                                                                                                                                                                                                                                     |

The timing diagram for the CTC mode is shown in Figure 45. The counter value (TCNT1) increases until a compare match occurs with either OCR1A or ICR1, and then counter (TCNT1) is cleared.

Figure 45. CTC Mode, Timing Diagram

tion of counting external events.

- 1. Write any value to either of the registers OCR2 or TCCR2.

- 2. Wait for the corresponding Update Busy Flag to be cleared.

- 3. Read TCNT2.

- During asynchronous operation, the synchronization of the Interrupt Flags for the asynchronous timer takes three processor cycles plus one timer cycle. The timer is therefore advanced by at least one before the processor can read the timer value causing the setting of the Interrupt Flag. The output compare pin is changed on the timer clock and is not synchronized to the processor clock.

#### Timer/Counter Interrupt Mask Register – TIMSK

| Bit           | 7     | 6     | 5      | 4      | 3      | 2     | 1     | 0     | _     |

|---------------|-------|-------|--------|--------|--------|-------|-------|-------|-------|

|               | OCIE2 | TOIE2 | TICIE1 | OCIE1A | OCIE1B | TOIE1 | OCIE0 | TOIE0 | TIMSK |

| Read/Write    | R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   |       |

| Initial Value | 0     | 0     | 0      | 0      | 0      | 0     | 0     | 0     |       |

#### • Bit 7 – OCIE2: Timer/Counter2 Output Compare Match Interrupt Enable

When the OCIE2 bit is written to one and the I-bit in the Status Register is set (one), the Timer/Counter2 Compare Match interrupt is enabled. The corresponding interrupt is executed if a compare match in Timer/Counter2 occurs, that is, when the OCF2 bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

#### Bit 6 – TOIE2: Timer/Counter2 Overflow Interrupt Enable

When the TOIE2 bit is written to one and the I-bit in the Status Register is set (one), the Timer/Counter2 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter2 occurs, that is, when the TOV2 bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

Timer/Counter Interrupt Flag Register – TIFR

| Bit           | 7    | 6    | 5    | 4     | 3     | 2    | 1    | 0    | _    |

|---------------|------|------|------|-------|-------|------|------|------|------|

|               | OCF2 | TOV2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0 | TOV0 | TIFR |

| Read/Write    | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W  | R/W  |      |

| Initial Value | 0    | 0    | 0    | 0     | 0     | 0    | 0    | 0    |      |

#### • Bit 7 – OCF2: Output Compare Flag 2

The OCF2 bit is set (one) when a compare match occurs between the Timer/Counter2 and the data in OCR2 – Output Compare Register2. OCF2 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF2 is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE2 (Timer/Counter2 Compare match Interrupt Enable), and OCF2 are set (one), the Timer/Counter2 Compare match Interrupt is executed.

#### • Bit 6 – TOV2: Timer/Counter2 Overflow Flag

The TOV2 bit is set (one) when an overflow occurs in Timer/Counter2. TOV2 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV2 is cleared by writing a logic one to the flag. When the SREG I-bit, TOIE2 (Timer/Counter2 Overflow Interrupt Enable), and TOV2 are set (one), the Timer/Counter2 Overflow interrupt is executed. In PWM mode, this bit is set when Timer/Counter2 changes counting direction at \$00.

#### • Bit 11:0 - UBRR11:0: USART Baud Rate Register

This is a 12-bit register which contains the USART baud rate. The UBRRH contains the four most significant bits, and the UBRRL contains the 8 least significant bits of the USART baud rate. Ongoing transmissions by the transmitter and receiver will be corrupted if the baud rate is changed. Writing UBRRL will trigger an immediate update of the baud rate prescaler.

**Examples of Baud Rate Setting** For standard crystal and resonator frequencies, the most commonly used baud rates for asynchronous operation can be generated by using the UBRR settings in Table 68. UBRR values which yield an actual baud rate differing less than 0.5% from the target baud rate, are bold in the table. Higher error ratings are acceptable, but the receiver will have less noise resistance when the error ratings are high, especially for large serial frames (see "Asynchronous Operational Range" on page 159). The error values are calculated using the following equation:

$$Error[\%] = \left(\frac{BaudRate_{Closest Match}}{BaudRate} - 1\right) \bullet 100\%$$

| Table CO  | Evennelse of LIDDE | Catting of far Common | Uland Oneilleter Frequencies  |

|-----------|--------------------|-----------------------|-------------------------------|

| Table 68. | Examples of UBRR   | Commoni               | y Used Oscillator Frequencies |

|                    | f <sub>osc</sub> = 1.0000 MHz |        |         | f <sub>osc</sub> = 1.8432 MHz |         |        |         | f <sub>osc</sub> = 2.0000 MHz |         |        |         |       |

|--------------------|-------------------------------|--------|---------|-------------------------------|---------|--------|---------|-------------------------------|---------|--------|---------|-------|

| Baud<br>Rate       | U2X = 0                       |        | U2X = 1 |                               | U2X = 0 |        | U2X = 1 |                               | U2X = 0 |        | U2X = 1 |       |

| (bps)              | UBRR                          | Error  | UBRR    | Error                         | UBRR    | Error  | UBRR    | Error                         | UBRR    | Error  | UBRR    | Error |

| 2400               | 25                            | 0.2%   | 51      | 0.2%                          | 47      | 0.0%   | 95      | 0.0%                          | 51      | 0.2%   | 103     | 0.2%  |

| 4800               | 12                            | 0.2%   | 25      | 0.2%                          | 23      | 0.0%   | 47      | 0.0%                          | 25      | 0.2%   | 51      | 0.2%  |

| 9600               | 6                             | -7.0%  | 12      | 0.2%                          | 11      | 0.0%   | 23      | 0.0%                          | 12      | 0.2%   | 25      | 0.2%  |

| 14.4k              | 3                             | 8.5%   | 8       | -3.5%                         | 7       | 0.0%   | 15      | 0.0%                          | 8       | -3.5%  | 16      | 2.1%  |

| 19.2k              | 2                             | 8.5%   | 6       | -7.0%                         | 5       | 0.0%   | 11      | 0.0%                          | 6       | -7.0%  | 12      | 0.2%  |

| 28.8k              | 1                             | 8.5%   | 3       | 8.5%                          | 3       | 0.0%   | 7       | 0.0%                          | 3       | 8.5%   | 8       | -3.5% |

| 38.4k              | 1                             | -18.6% | 2       | 8.5%                          | 2       | 0.0%   | 5       | 0.0%                          | 2       | 8.5%   | 6       | -7.0% |

| 57.6k              | 0                             | 8.5%   | 1       | 8.5%                          | 1       | 0.0%   | 3       | 0.0%                          | 1       | 8.5%   | 3       | 8.5%  |

| 76.8k              | _                             | _      | 1       | -18.6%                        | 1       | -25.0% | 2       | 0.0%                          | 1       | -18.6% | 2       | 8.5%  |

| 115.2k             | _                             | _      | 0       | 8.5%                          | 0       | 0.0%   | 1       | 0.0%                          | 0       | 8.5%   | 1       | 8.5%  |

| 230.4k             | _                             | _      | _       | _                             | _       | _      | 0       | 0.0%                          | _       | _      | _       | _     |

| 250k               | _                             | _      | _       | _                             | _       | _      | _       | _                             | _       | _      | 0       | 0.0%  |

| Max <sup>(1)</sup> | 62.5                          | Kbps   | 125     | Kbps                          | 115.2   | Kbps   | 230.4   | Kbps                          | 125     | Kbps   | 250     | Kbps  |

1. UBRR = 0, Error = 0.0%

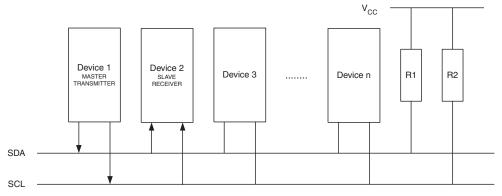

## Transmission Modes

The TWI can operate in one of four major modes. These are named Master Transmitter (MT), Master Receiver (MR), Slave Transmitter (ST) and Slave Receiver (SR). Several of these modes can be used in the same application. As an example, the TWI can use MT mode to write data into a TWI EEPROM, MR mode to read the data back from the EEPROM. If other Masters are present in the system, some of these might transmit data to the TWI, and then SR mode would be used. It is the application software that decides which modes are legal.

The following sections describe each of these modes. Possible status codes are described along with figures detailing data transmission in each of the modes. These figures contain the following abbreviations:

S: START condition

**Rs: REPEATED START condition**

R: Read bit (high level at SDA)

W: Write bit (low level at SDA)

A: Acknowledge bit (low level at SDA)

A: Not acknowledge bit (high level at SDA)

Data: 8-bit data byte

P: STOP condition

SLA: Slave Address

In Figure 87 to Figure 93, circles are used to indicate that the TWINT Flag is set. The numbers in the circles show the status code held in TWSR, with the prescaler bits masked to zero. At these points, actions must be taken by the application to continue or complete the TWI transfer. The TWI transfer is suspended until the TWINT Flag is cleared by software.

When the TWINT Flag is set, the status code in TWSR is used to determine the appropriate software action. For each status code, the required software action and details of the following serial transfer are given in Table 74 to Table 77. Note that the prescaler bits are masked to zero in these tables.

# Master TransmitterIn the Master Transmitter mode, a number of data bytes are transmitted to a Slave ReceiverMode(see Figure 86). In order to enter a Master mode, a START condition must be transmitted. The<br/>format of the following address packet determines whether Master Transmitter or Master<br/>Receiver mode is to be entered. If SLA+W is transmitted, MT mode is entered, if SLA+R is trans-<br/>mitted, MR mode is entered. All the status codes mentioned in this section assume that the<br/>prescaler bits are zero or are masked to zero.

#### Figure 86. Data Transfer in Master Transmitter Mode

all single conversions, and the first free running conversion) when  $CK_{ADC2}$  is low will take the same amount of time as a single ended conversion (13 ADC clock cycles from the next prescaled clock cycle). A conversion initiated by the user when  $CK_{ADC2}$  is high will take 14 ADC clock cycles due to the synchronization mechanism. In Free Running mode, a new conversion is initiated immediately after the previous conversion completes, and since  $CK_{ADC2}$  is high at this time, all automatically started (that is, all but the first) free running conversions will take 14 ADC clock cycles.

The gain stage is optimized for a bandwidth of 4 kHz at all gain settings. Higher frequencies may be subjected to non-linear amplification. An external low-pass filter should be used if the input signal contains higher frequency components than the gain stage bandwidth. Note that the ADC clock frequency is independent of the gain stage bandwidth limitation. For example, the ADC clock period may be 6 µs, allowing a channel to be sampled at 12 kSPS, regardless of the bandwidth of this channel.

If differential gain channels are used and conversions are started by Auto Triggering, the ADC must be switched off between conversions. When Auto Triggering is used, the ADC prescaler is reset before the conversion is started. Since the gain stage is dependent of a stable ADC clock prior to the conversion, this conversion will not be valid. By disabling and then re-enabling the ADC between each conversion (writing ADEN in ADCSRA to "0" then to "1"), only extended conversions are performed. The result from the extended conversions will be valid. See "Prescaling and Conversion Timing" on page 207 for timing details.

**Changing Channel or Reference Selection** The MUXn and REFS1:0 bits in the ADMUX Register are single buffered through a temporary register to which the CPU has random access. This ensures that the channels and reference selection only takes place at a safe point during the conversion. The channel and reference selection is continuously updated until a conversion is started. Once the conversion starts, the channel and reference selection is locked to ensure a sufficient sampling time for the ADC. Continuous updating resumes in the last ADC clock cycle before the conversion completes (ADIF in ADCSRA is set). Note that the conversion starts on the following rising ADC clock edge after ADSC is written. The user is thus advised not to write new channel or reference selection values to ADMUX until one ADC clock cycle after ADSC is written.

If Auto Triggering is used, the exact time of the triggering event can be indeterministic. Special care must be taken when updating the ADMUX Register, in order to control which conversion will be affected by the new settings.

If both ADATE and ADEN is written to one, an interrupt event can occur at any time. If the ADMUX Register is changed in this period, the user cannot tell if the next conversion is based on the old or the new settings. ADMUX can be safely updated in the following ways:

- 1. When ADATE or ADEN is cleared.

- 2. During conversion, minimum one ADC clock cycle after the trigger event.

- 3. After a conversion, before the Interrupt Flag used as trigger source is cleared.

When updating ADMUX in one of these conditions, the new settings will affect the next ADC conversion.

Special care should be taken when changing differential channels. Once a differential channel has been selected, the gain stage may take as much as 125  $\mu$ s to stabilize to the new value. Thus conversions should not be started within the first 125  $\mu$ s after selecting a new differential channel. Alternatively, conversion results obtained within this period should be discarded.

The same settling time should be observed for the first differential conversion after changing ADC reference (by changing the REFS1:0 bits in ADMUX).

| V <sub>ADCn</sub>                                  | Read code | Corresponding Decimal Value |

|----------------------------------------------------|-----------|-----------------------------|

| V <sub>ADCm</sub> + V <sub>REF</sub> /GAIN         | 0x1FF     | 511                         |

| V <sub>ADCm</sub> + 511/512 V <sub>REF</sub> /GAIN | 0x1FF     | 511                         |

| V <sub>ADCm</sub> + 510/512 V <sub>REF</sub> /GAIN | 0x1FE     | 510                         |

|                                                    |           |                             |

| V <sub>ADCm</sub> + 1/512 V <sub>REF</sub> /GAIN   | 0x001     | 1                           |

| V <sub>ADCm</sub>                                  | 0x000     | 0                           |

| V <sub>ADCm</sub> - 1/512 V <sub>REF</sub> /GAIN   | 0x3FF     | -1                          |

|                                                    |           |                             |

| V <sub>ADCm</sub> - 511/512 V <sub>REF</sub> /GAIN | 0x201     | -511                        |

| V <sub>ADCm</sub> - V <sub>REF</sub> /GAIN         | 0x200     | -512                        |

Table 82. Correlation between Input Voltage and Output Codes

Example:

ADMUX = 0xED (ADC3 - ADC2, 10x gain, 2.56V reference, left adjusted result)

Voltage on ADC3 is 300 mV, voltage on ADC2 is 500 mV.

ADCR = 512 × 10 × (300 - 500) / 2560 = -400 = 0x270

ADCL will thus read 0x00, and ADCH will read 0x9C. Writing zero to ADLAR right adjusts the result: ADCL = 0x70, ADCH = 0x02.

#### ADC Multiplexer Selection Register – ADMUX

| Bit           | 7     | 6     | 5     | 4    | 3    | 2    | 1    | 0    | _     |

|---------------|-------|-------|-------|------|------|------|------|------|-------|

|               | REFS1 | REFS0 | ADLAR | MUX4 | MUX3 | MUX2 | MUX1 | MUX0 | ADMUX |

| Read/Write    | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | -     |

| Initial Value | 0     | 0     | 0     | 0    | 0    | 0    | 0    | 0    |       |

#### • Bit 7:6 - REFS1:0: Reference Selection Bits

These bits select the voltage reference for the ADC, as shown in Table 83. If these bits are changed during a conversion, the change will not go in effect until this conversion is complete (ADIF in ADCSRA is set). The internal voltage reference options may not be used if an external reference voltage is being applied to the AREF pin.

Table 83.

Voltage Reference Selections for ADC

| REFS1 | REFS0 | Voltage Reference Selection                                          |

|-------|-------|----------------------------------------------------------------------|

| 0     | 0     | AREF, Internal Vref turned off                                       |

| 0     | 1     | AVCC with external capacitor at AREF pin                             |

| 1     | 0     | Reserved                                                             |

| 1     | 1     | Internal 2.56V Voltage Reference with external capacitor at AREF pin |

#### Bit 5 – ADLAR: ADC Left Adjust Result

The ADLAR bit affects the presentation of the ADC conversion result in the ADC Data Register. Write one to ADLAR to left adjust the result. Otherwise, the result is right adjusted. Changing the ADLAR bit will affect the ADC Data Register immediately, regardless of any ongoing conver-

| Table 84. | Input Channel and Gain Selections ( | (Continued) | ) |

|-----------|-------------------------------------|-------------|---|

|-----------|-------------------------------------|-------------|---|

| MUX40 | Single Ended<br>Input    | Positive Differential<br>Input | Negative Differential<br>Input | Gain |

|-------|--------------------------|--------------------------------|--------------------------------|------|

| 11101 |                          | ADC5                           | ADC2                           | 1x   |

| 11110 | 1.22V (V <sub>BG</sub> ) | N/A                            |                                |      |

| 11111 | 0 V (GND)                |                                |                                |      |

#### ADC Control and Status Register A – ADCSRA

| Bit           | 7    | 6    | 5     | 4    | 3    | 2     | 1     | 0     | _      |

|---------------|------|------|-------|------|------|-------|-------|-------|--------|

|               | ADEN | ADSC | ADATE | ADIF | ADIE | ADPS2 | ADPS1 | ADPS0 | ADCSRA |

| Read/Write    | R/W  | R/W  | R/W   | R/W  | R/W  | R/W   | R/W   | R/W   | -      |

| Initial Value | 0    | 0    | 0     | 0    | 0    | 0     | 0     | 0     |        |

#### • Bit 7 – ADEN: ADC Enable

Writing this bit to one enables the ADC. By writing it to zero, the ADC is turned off. Turning the ADC off while a conversion is in progress, will terminate this conversion.

#### • Bit 6 – ADSC: ADC Start Conversion

In Single Conversion mode, write this bit to one to start each conversion. In Free Running Mode, write this bit to one to start the first conversion. The first conversion after ADSC has been written after the ADC has been enabled, or if ADSC is written at the same time as the ADC is enabled, will take 25 ADC clock cycles instead of the normal 13. This first conversion performs initialization of the ADC.

ADSC will read as one as long as a conversion is in progress. When the conversion is complete, it returns to zero. Writing zero to this bit has no effect.

#### • Bit 5 – ADATE: ADC Auto Trigger Enable

When this bit is written to one, Auto Triggering of the ADC is enabled. The ADC will start a conversion on a positive edge of the selected trigger signal. The trigger source is selected by setting the ADC Trigger Select bits, ADTS in SFIOR.

#### • Bit 4 – ADIF: ADC Interrupt Flag

This bit is set when an ADC conversion completes and the Data Registers are updated. The ADC Conversion Complete Interrupt is executed if the ADIE bit and the I-bit in SREG are set. ADIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ADIF is cleared by writing a logical one to the flag. Beware that if doing a Read-Modify-Write on ADCSRA, a pending interrupt can be disabled. This also applies if the SBI and CBI instructions are used.

#### Bit 3 – ADIE: ADC Interrupt Enable

When this bit is written to one and the I-bit in SREG is set, the ADC Conversion Complete Interrupt is activated.

#### Bits 2:0 – ADPS2:0: ADC Prescaler Select Bits

These bits determine the division factor between the XTAL frequency and the input clock to the ADC.

The active states are:

- Capture-DR: Data on the external pins are sampled into the Boundary-scan Chain.

- Shift-DR: The Boundary-scan Chain is shifted by the TCK input.

- Update-DR: Data from the Boundary-scan Chain is applied to the output latches. However, the output latches are not connected to the pins.

AVR\_RESET; \$C The AVR specific public JTAG instruction for forcing the AVR device into the Reset mode or releasing the JTAG Reset source. The TAP controller is not reset by this instruction. The one bit Reset Register is selected as Data Register. Note that the reset will be active as long as there is a logic 'one' in the Reset Chain. The output from this chain is not latched.

The active states are:

• Shift-DR: The Reset Register is shifted by the TCK input.

**BYPASS; \$F** Mandatory JTAG instruction selecting the Bypass Register for Data Register.

The active states are:

- Capture-DR: Loads a logic "0" into the Bypass Register.

- Shift-DR: The Bypass Register cell between TDI and TDO is shifted.

Boundary-scan Related Register in I/O Memory

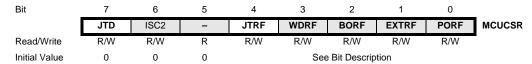

MCU Control and Status Register – MCUCSR The MCU Control and Status Register contains control bits for general MCU functions, and provides information on which reset source caused an MCU Reset.

#### Bit 7 – JTD: JTAG Interface Disable

When this bit is zero, the JTAG interface is enabled if the JTAGEN Fuse is programmed. If this bit is one, the JTAG interface is disabled. In order to avoid unintentional disabling or enabling of the JTAG interface, a timed sequence must be followed when changing this bit: The application software must write this bit to the desired value twice within four cycles to change its value.

If the JTAG interface is left unconnected to other JTAG circuitry, the JTD bit should be set to one. The reason for this is to avoid static current at the TDO pin in the JTAG interface.

#### Bit 4 – JTRF: JTAG Reset Flag

This bit is set if a reset is being caused by a logic one in the JTAG Reset Register selected by the JTAG instruction AVR\_RESET. This bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

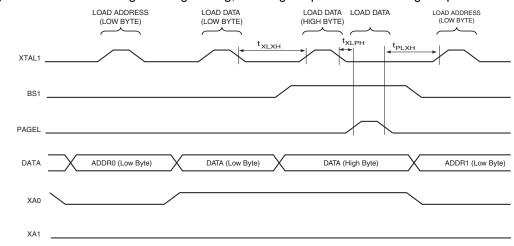

Figure 134. Parallel Programming Timing, Loading Sequence with Timing Requirements<sup>(1)</sup>

Note: 1. The timing requirements shown in Figure 133 (that is, t<sub>DVXH</sub>, t<sub>XHXL</sub>, and t<sub>XLDX</sub>) also apply to loading operation.

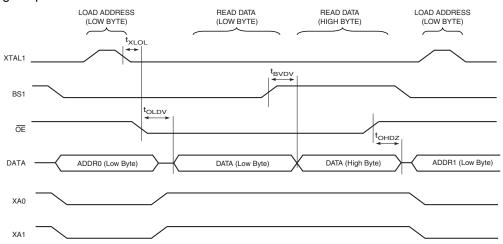

**Figure 135.** Parallel Programming Timing, Reading Sequence (within the Same Page) with Timing Requirements<sup>(1)</sup>

Note: 1. The timing requirements shown in Figure 133 (that is, t<sub>DVXH</sub>, t<sub>XHXL</sub>, and t<sub>XLDX</sub>) also apply to reading operation.

| Table 113. | Parallel Programming | Characteristics. | $V_{CC} = 5V \pm 10\%$ |

|------------|----------------------|------------------|------------------------|

|            |                      |                  |                        |

| Symbol          | Parameter                  | Min  | Тур | Max  | Units |

|-----------------|----------------------------|------|-----|------|-------|

| V <sub>PP</sub> | Programming Enable Voltage | 11.5 |     | 12.5 | V     |

| I <sub>PP</sub> | Programming Enable Current |      |     | 250  | μA    |

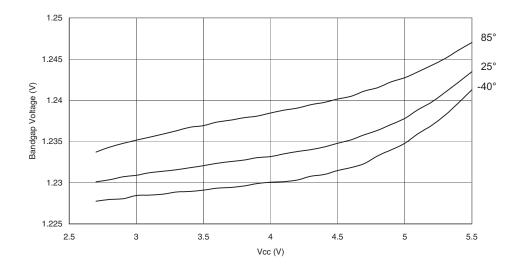

Figure 190. Bandgap Voltage vs.  $V_{CC}$

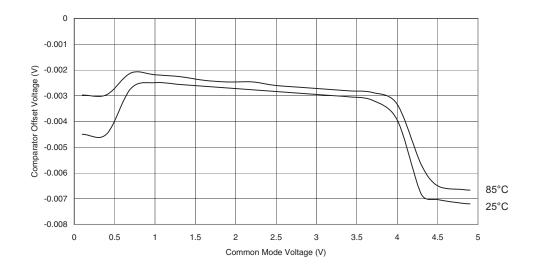

Figure 191. Analog Comparator Offset Voltage vs. Common Mode Voltage ( $V_{CC} = 5V$ )

- 8. Added JTAG version number for rev. H in Table 87 on page 229.

- 9. Added not regarding OCDEN Fuse below Table 105 on page 260.

- 10. Updated Programming Figures:

Figure 127 on page 262 and Figure 136 on page 274 are updated to also reflect that AVCC must be connected during Programming mode. Figure 131 on page 270 added to illustrate how to program the fuses.

- 11. Added a note regarding usage of the "PROG\_PAGELOAD (\$6)" on page 280 and "PROG\_PAGEREAD (\$7)" on page 280.

- 12. Removed alternative algortihm for leaving JTAG Programming mode.

See "Leaving Programming Mode" on page 288.

- 13. Added Calibrated RC Oscillator characterization curves in section "ATmega16 Typical Characteristics" on page 299.

- 14. Corrected ordering code for QFN/MLF package (16 MHz) in "Ordering Information" on page 336.

- 15. Corrected Table 90, "Scan Signals for the Oscillators(1)(2)(3)," on page 235.