#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega16l-8aur |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Port B (PB7PB0) | Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The |

|-----------------|---------------------------------------------------------------------------------------------------------|

|                 | Port B output buffers have symmetrical drive characteristics with both high sink and source             |

|                 | capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up    |

|                 | resistors are activated. The Port B pins are tri-stated when a reset condition becomes active,          |

|                 | even if the clock is not running.                                                                       |

Port B also serves the functions of various special features of the ATmega16 as listed on page 58.

Port C (PC7..PC0) Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PC5(TDI), PC3(TMS) and PC2(TCK) will be activated even if a reset occurs.

Port C also serves the functions of the JTAG interface and other special features of the ATmega16 as listed on page 61.

**Port D (PD7..PD0)** Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATmega16 as listed on page 63.

- **RESET** Reset Input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 15 on page 38. Shorter pulses are not guaranteed to generate a reset.

- **XTAL1** Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

- **XTAL2** Output from the inverting Oscillator amplifier.

- AVCC is the supply voltage pin for Port A and the A/D Converter. It should be externally connected to  $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to  $V_{CC}$  through a low-pass filter.

- **AREF** AREF is the analog reference pin for the A/D Converter.

Idle Mode When the SM2..0 bits are written to 000, the SLEEP instruction makes the MCU enter Idle mode, stopping the CPU but allowing SPI, USART, Analog Comparator, ADC, Two-wire Serial Interface, Timer/Counters, Watchdog, and the interrupt system to continue operating. This sleep mode basically halts clk<sub>CPU</sub> and clk<sub>FLASH</sub>, while allowing the other clocks to run.

Idle mode enables the MCU to wake up from external triggered interrupts as well as internal ones like the Timer Overflow and USART Transmit Complete interrupts. If wake-up from the Analog Comparator interrupt is not required, the Analog Comparator can be powered down by setting the ACD bit in the Analog Comparator Control and Status Register – ACSR. This will reduce power consumption in Idle mode. If the ADC is enabled, a conversion starts automatically when this mode is entered.

#### ADC Noise Reduction Mode When the SM2..0 bits are written to 001, the SLEEP instruction makes the MCU enter ADC Noise Reduction mode, stopping the CPU but allowing the ADC, the External Interrupts, the Two-wire Serial Interface address watch, Timer/Counter2 and the Watchdog to continue operating (if enabled). This sleep mode basically halts clk<sub>I/O</sub>, clk<sub>CPU</sub>, and clk<sub>FLASH</sub>, while allowing the other clocks to run.

This improves the noise environment for the ADC, enabling higher resolution measurements. If the ADC is enabled, a conversion starts automatically when this mode is entered. Apart form the ADC Conversion Complete interrupt, only an External Reset, a Watchdog Reset, a Brown-out Reset, a Two-wire Serial Interface Address Match Interrupt, a Timer/Counter2 interrupt, an SPM/EEPROM ready interrupt, an External level interrupt on INT0 or INT1, or an external interrupt on INT2 can wake up the MCU from ADC Noise Reduction mode.

**Power-down Mode** When the SM2..0 bits are written to 010, the SLEEP instruction makes the MCU enter Powerdown mode. In this mode, the External Oscillator is stopped, while the External interrupts, the Two-wire Serial Interface address watch, and the Watchdog continue operating (if enabled). Only an External Reset, a Watchdog Reset, a Brown-out Reset, a Two-wire Serial Interface address match interrupt, an External level interrupt on INT0 or INT1, or an External interrupt on INT2 can wake up the MCU. This sleep mode basically halts all generated clocks, allowing operation of asynchronous modules only.

Note that if a level triggered interrupt is used for wake-up from Power-down mode, the changed level must be held for some time to wake up the MCU. Refer to "External Interrupts" on page 68 for details.

When waking up from Power-down mode, there is a delay from the wake-up condition occurs until the wake-up becomes effective. This allows the clock to restart and become stable after having been stopped. The wake-up period is defined by the same CKSEL Fuses that define the reset time-out period, as described in "Clock Sources" on page 25.

**Power-save Mode** When the SM2..0 bits are written to 011, the SLEEP instruction makes the MCU enter Power-save mode. This mode is identical to Power-down, with one exception:

If Timer/Counter2 is clocked asynchronously, that is, the AS2 bit in ASSR is set, Timer/Counter2 will run during sleep. The device can wake up from either Timer Overflow or Output Compare event from Timer/Counter2 if the corresponding Timer/Counter2 interrupt enable bits are set in TIMSK, and the Global Interrupt Enable bit in SREG is set.

If the Asynchronous Timer is NOT clocked asynchronously, Power-down mode is recommended instead of Power-save mode because the contents of the registers in the Asynchronous Timer should be considered undefined after wake-up in Power-save mode if AS2 is 0.

This sleep mode basically halts all clocks except clk<sub>ASY</sub>, allowing operation only of asynchronous modules, including Timer/Counter2 if clocked asynchronously.

Moving Interrupts Between Application and Boot Space The General Interrupt Control Register controls the placement of the Interrupt Vector table.

General Interrupt Control Register – GICR

| Bit           | 7    | 6    | 5    | 4 | 3 | 2 | 1     | 0    | _    |

|---------------|------|------|------|---|---|---|-------|------|------|

|               | INT1 | INT0 | INT2 | - | - | - | IVSEL | IVCE | GICR |

| Read/Write    | R/W  | R/W  | R/W  | R | R | R | R/W   | R/W  |      |

| Initial Value | 0    | 0    | 0    | 0 | 0 | 0 | 0     | 0    |      |

### • Bit 1 – IVSEL: Interrupt Vector Select

When the IVSEL bit is cleared (zero), the Interrupt Vectors are placed at the start of the Flash memory. When this bit is set (one), the interrupt vectors are moved to the beginning of the Boot Loader section of the Flash. The actual address of the start of the Boot Flash section is determined by the BOOTSZ Fuses. Refer to the section "Boot Loader Support – Read-While-Write Self-Programming" on page 246 for details. To avoid unintentional changes of Interrupt Vector tables, a special write procedure must be followed to change the IVSEL bit:

- 1. Write the Interrupt Vector Change Enable (IVCE) bit to one.

- 2. Within four cycles, write the desired value to IVSEL while writing a zero to IVCE.

Interrupts will automatically be disabled while this sequence is executed. Interrupts are disabled in the cycle IVCE is set, and they remain disabled until after the instruction following the write to IVSEL. If IVSEL is not written, interrupts remain disabled for four cycles. The I-bit in the Status Register is unaffected by the automatic disabling.

- Note: If Interrupt Vectors are placed in the Boot Loader section and Boot Lock bit BLB02 is programmed, interrupts are disabled while executing from the Application section. If Interrupt Vectors are placed in the Application section and Boot Lock bit BLB12 is programed, interrupts are disabled while executing from the Boot Loader section. Refer to the section "Boot Loader Support Read-While-Write Self-Programming" on page 246 for details on Boot Lock bits.

- Bit 0 IVCE: Interrupt Vector Change Enable

The IVCE bit must be written to logic one to enable change of the IVSEL bit. IVCE is cleared by hardware four cycles after it is written or when IVSEL is written. Setting the IVCE bit will disable interrupts, as explained in the IVSEL description above. See Code Example below

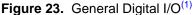

Note: 1. WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clk<sub>I/O</sub>, SLEEP, and PUD are common to all ports.

**Configuring the Pin** Each port pin consists of three register bits: DDxn, PORTxn, and PINxn. As shown in "Register Description for I/O Ports" on page 66, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits at the PORTx I/O address, and the PINxn bits at the PINx I/O address.

The DDxn bit in the DDRx Register selects the direction of this pin. If DDxn is written logic one, Pxn is configured as an output pin. If DDxn is written logic zero, Pxn is configured as an input pin.

If PORTxn is written logic one when the pin is configured as an input pin, the pull-up resistor is activated. To switch the pull-up resistor off, PORTxn has to be written logic zero or the pin has to be configured as an output pin. The port pins are tri-stated when a reset condition becomes active, even if no clocks are running.

If PORTxn is written logic one when the pin is configured as an output pin, the port pin is driven high (one). If PORTxn is written logic zero when the pin is configured as an output pin, the port pin is driven low (zero).

When switching between tri-state ( $\{DDxn, PORTxn\} = 0b00$ ) and output high ( $\{DDxn, PORTxn\} = 0b11$ ), an intermediate state with either pull-up enabled ( $\{DDxn, PORTxn\} = 0b01$ ) or output low ( $\{DDxn, PORTxn\} = 0b10$ ) must occur. Normally, the pull-up enabled state is fully acceptable, as a high-impedant environment will not notice the difference between a strong high driver and a pull-up. If this is not the case, the PUD bit in the SFIOR Register can be set to disable all pull-ups in all ports.

When OC0 is connected to the pin, the function of the COM01:0 bits depends on the WGM01:0 bit setting. Table 39 shows the COM01:0 bit functionality when the WGM01:0 bits are set to a normal or CTC mode (non-PWM).

| COM01 | COM00 | Description                              |

|-------|-------|------------------------------------------|

| 0     | 0     | Normal port operation, OC0 disconnected. |

| 0     | 1     | Toggle OC0 on compare match              |

| 1     | 0     | Clear OC0 on compare match               |

| 1     | 1     | Set OC0 on compare match                 |

Table 39.

Compare Output Mode, non-PWM Mode

Table 40 shows the COM01:0 bit functionality when the WGM01:0 bits are set to fast PWM mode.

| Table 40. | Compare | Output M | ode, Fast | PWM Mode <sup>(1)</sup> |

|-----------|---------|----------|-----------|-------------------------|

|-----------|---------|----------|-----------|-------------------------|

| COM01 | COM00 | Description                                                         |

|-------|-------|---------------------------------------------------------------------|

| 0     | 0     | Normal port operation, OC0 disconnected.                            |

| 0     | 1     | Reserved                                                            |

| 1     | 0     | Clear OC0 on compare match, set OC0 at BOTTOM, (non-inverting mode) |

| 1     | 1     | Set OC0 on compare match, clear OC0 at BOTTOM, (inverting mode)     |

Note: 1. A special case occurs when OCR0 equals TOP and COM01 is set. In this case, the compare match is ignored, but the set or clear is done at TOP. See "Fast PWM Mode" on page 77 for more details.

Table 41 shows the COM01:0 bit functionality when the WGM01:0 bits are set to phase correct PWM mode.

| Table 41. | Compare Out | out Mode, Phase | Correct PWM Mode <sup>(1)</sup> |

|-----------|-------------|-----------------|---------------------------------|

|-----------|-------------|-----------------|---------------------------------|

| COM01 | COM00 | Description                                                                              |

|-------|-------|------------------------------------------------------------------------------------------|

| 0     | 0     | Normal port operation, OC0 disconnected.                                                 |

| 0     | 1     | Reserved                                                                                 |

| 1     | 0     | Clear OC0 on compare match when up-counting. Set OC0 on compare match when downcounting. |

| 1     | 1     | Set OC0 on compare match when up-counting. Clear OC0 on compare match when downcounting. |

Note: 1. A special case occurs when OCR0 equals TOP and COM01 is set. In this case, the compare match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 79 for more details.

## • Bit 0 – TOIE0: Timer/Counter0 Overflow Interrupt Enable

When the TOIE0 bit is written to one, and the I-bit in the Status Register is set (one), the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter0 occurs, that is, when the TOV0 bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

Timer/Counter Interrupt Flag Register – TIFR

| Bit           | 7    | 6    | 5    | 4     | 3     | 2    | 1    | 0    | _    |

|---------------|------|------|------|-------|-------|------|------|------|------|

|               | OCF2 | TOV2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0 | TOV0 | TIFR |

| Read/Write    | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W  | R/W  | •    |

| Initial Value | 0    | 0    | 0    | 0     | 0     | 0    | 0    | 0    |      |

## • Bit 1 – OCF0: Output Compare Flag 0

The OCF0 bit is set (one) when a compare match occurs between the Timer/Counter0 and the data in OCR0 – Output Compare Register0. OCF0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF0 is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE0 (Timer/Counter0 Compare Match Interrupt Enable), and OCF0 are set (one), the Timer/Counter0 Compare Match Interrupt is executed.

## • Bit 0 – TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG I-bit, TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set (one), the Timer/Counter0 Overflow interrupt is executed. In phase correct PWM mode, this bit is set when Timer/Counter0 changes counting direction at \$00.

The Input Capture is updated with the counter (TCNT1) value each time an event occurs on the ICP1 pin (or optionally on the analog comparator output for Timer/Counter1). The Input Capture can be used for defining the counter TOP value.

The Input Capture Register is 16-bit in size. To ensure that both the high and Low bytes are read simultaneously when the CPU accesses these registers, the access is performed using an 8-bit temporary High Byte Register (TEMP). This temporary register is shared by all the other 16-bit registers. See "Accessing 16-bit Registers" on page 92.

### **Timer/Counter** Interrupt Mask Register – TIMSK<sup>(1)</sup>

| Bit           | 7     | 6     | 5      | 4      | 3      | 2     | 1     | 0     | _     |

|---------------|-------|-------|--------|--------|--------|-------|-------|-------|-------|

|               | OCIE2 | TOIE2 | TICIE1 | OCIE1A | OCIE1B | TOIE1 | OCIE0 | TOIE0 | TIMSK |

| Read/Write    | R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   |       |

| Initial Value | 0     | 0     | 0      | 0      | 0      | 0     | 0     | 0     |       |

1. This register contains interrupt control bits for several Timer/Counters, but only Timer1 bits are Note: described in this section. The remaining bits are described in their respective timer sections.

### Bit 5 – TICIE1: Timer/Counter1, Input Capture Interrupt Enable

When this bit is written to one, and the I-flag in the Status Register is set (interrupts globally enabled), the Timer/Counter1 Input Capture Interrupt is enabled. The corresponding Interrupt Vector (See "Interrupts" on page 45.) is executed when the ICF1 Flag, located in TIFR, is set.

### • Bit 4 – OCIE1A: Timer/Counter1, Output Compare A Match Interrupt Enable

When this bit is written to one, and the I-flag in the Status Register is set (interrupts globally enabled), the Timer/Counter1 Output Compare A match interrupt is enabled. The corresponding Interrupt Vector (See "Interrupts" on page 45.) is executed when the OCF1A Flag, located in TIFR, is set.

### Bit 3 – OCIE1B: Timer/Counter1, Output Compare B Match Interrupt Enable

When this bit is written to one, and the I-flag in the Status Register is set (interrupts globally enabled), the Timer/Counter1 Output Compare B match interrupt is enabled. The corresponding Interrupt Vector (See "Interrupts" on page 45.) is executed when the OCF1B Flag, located in TIFR, is set.

### Bit 2 – TOIE1: Timer/Counter1, Overflow Interrupt Enable

When this bit is written to one, and the I-flag in the Status Register is set (interrupts globally enabled), the Timer/Counter1 Overflow Interrupt is enabled. The corresponding Interrupt Vector (See "Interrupts" on page 45.) is executed when the TOV1 Flag, located in TIFR, is set.

| Interrupt Flag Register | Bit           | 7    | 6    | 5    | 4     | 3     | 2    | 1    | 0    |      |

|-------------------------|---------------|------|------|------|-------|-------|------|------|------|------|

| – TIFR                  |               | OCF2 | TOV2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0 | TOV0 | TIFR |

|                         | Read/Write    | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W  | R/W  | I    |

|                         | Initial Value | 0    | 0    | 0    | 0     | 0     | 0    | 0    | 0    |      |

Note: This register contains flag bits for several Timer/Counters, but only Timer1 bits are described in this section. The remaining bits are described in their respective timer sections.

Timer/Counter

## **Data Modes**

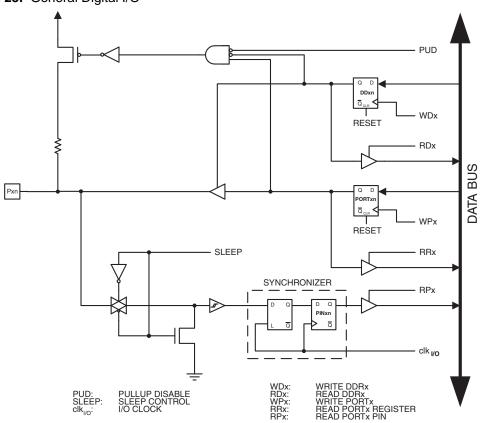

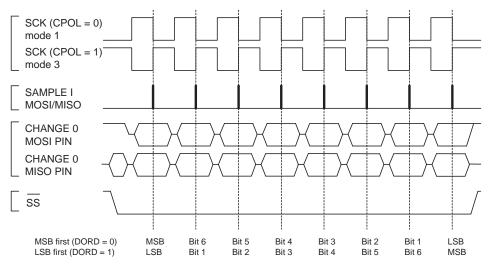

There are four combinations of SCK phase and polarity with respect to serial data, which are determined by control bits CPHA and CPOL. The SPI data transfer formats are shown in Figure 67 and Figure 68. Data bits are shifted out and latched in on opposite edges of the SCK signal, ensuring sufficient time for data signals to stabilize. This is clearly seen by summarizing Table 56 and Table 57, as done below:

Table 59. CPOL and CPHA Functionality

|                    | Leading Edge     | Trailing Edge    | SPI Mode |

|--------------------|------------------|------------------|----------|

| CPOL = 0, CPHA = 0 | Sample (Rising)  | Setup (Falling)  | 0        |

| CPOL = 0, CPHA = 1 | Setup (Rising)   | Sample (Falling) | 1        |

| CPOL = 1, CPHA = 0 | Sample (Falling) | Setup (Rising)   | 2        |

| CPOL = 1, CPHA = 1 | Setup (Falling)  | Sample (Rising)  | 3        |

Figure 68. SPI Transfer Format with CPHA = 1

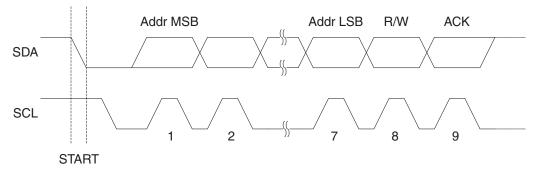

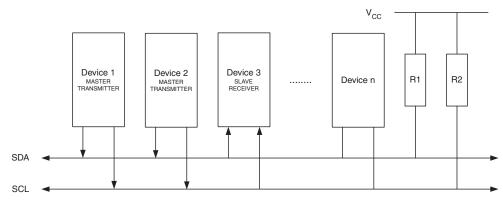

#### Address Packet Format

All address packets transmitted on the TWI bus are nine bits long, consisting of seven address bits, one READ/WRITE control bit and an acknowledge bit. If the READ/WRITE bit is set, a read operation is to be performed, otherwise a write operation should be performed. When a Slave recognizes that it is being addressed, it should acknowledge by pulling SDA low in the ninth SCL (ACK) cycle. If the addressed Slave is busy, or for some other reason can not service the Master's request, the SDA line should be left high in the ACK clock cycle. The Master can then transmit a STOP condition, or a REPEATED START condition to initiate a new transmission. An address packet consisting of a Slave address and a READ or a WRITE bit is called SLA+R or SLA+W, respectively.

The MSB of the address byte is transmitted first. Slave addresses can freely be allocated by the designer, but the address 0000 000 is reserved for a general call.

When a general call is issued, all Slaves should respond by pulling the SDA line low in the ACK cycle. A general call is used when a Master wishes to transmit the same message to several Slaves in the system. When the general call address followed by a Write bit is transmitted on the bus, all Slaves set up to acknowledge the general call will pull the SDA line low in the ack cycle. The following data packets will then be received by all the Slaves that acknowledged the general call. Note that transmitting the general call address followed by a Read bit is meaningless, as this would cause contention if several Slaves started transmitting different data.

All addresses of the format 1111 xxx should be reserved for future purposes.

### Figure 79. Address Packet Format

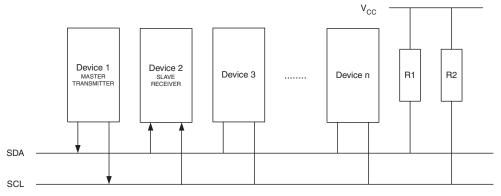

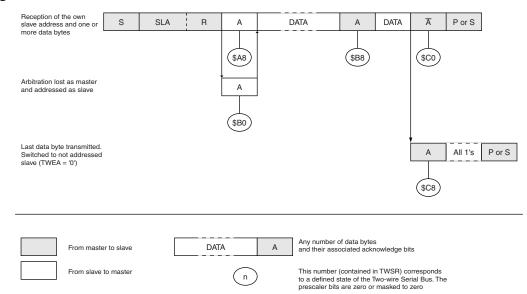

## Transmission Modes

The TWI can operate in one of four major modes. These are named Master Transmitter (MT), Master Receiver (MR), Slave Transmitter (ST) and Slave Receiver (SR). Several of these modes can be used in the same application. As an example, the TWI can use MT mode to write data into a TWI EEPROM, MR mode to read the data back from the EEPROM. If other Masters are present in the system, some of these might transmit data to the TWI, and then SR mode would be used. It is the application software that decides which modes are legal.

The following sections describe each of these modes. Possible status codes are described along with figures detailing data transmission in each of the modes. These figures contain the following abbreviations:

S: START condition

**Rs: REPEATED START condition**

R: Read bit (high level at SDA)

W: Write bit (low level at SDA)

A: Acknowledge bit (low level at SDA)

A: Not acknowledge bit (high level at SDA)

Data: 8-bit data byte

P: STOP condition

SLA: Slave Address

In Figure 87 to Figure 93, circles are used to indicate that the TWINT Flag is set. The numbers in the circles show the status code held in TWSR, with the prescaler bits masked to zero. At these points, actions must be taken by the application to continue or complete the TWI transfer. The TWI transfer is suspended until the TWINT Flag is cleared by software.

When the TWINT Flag is set, the status code in TWSR is used to determine the appropriate software action. For each status code, the required software action and details of the following serial transfer are given in Table 74 to Table 77. Note that the prescaler bits are masked to zero in these tables.

Master TransmitterIn the Master Transmitter mode, a number of data bytes are transmitted to a Slave ReceiverMode(see Figure 86). In order to enter a Master mode, a START condition must be transmitted. The<br/>format of the following address packet determines whether Master Transmitter or Master<br/>Receiver mode is to be entered. If SLA+W is transmitted, MT mode is entered, if SLA+R is trans-<br/>mitted, MR mode is entered. All the status codes mentioned in this section assume that the<br/>prescaler bits are zero or are masked to zero.

Figure 86. Data Transfer in Master Transmitter Mode

### Figure 93. Formats and States in the Slave Transmitter Mode

**Miscellaneous States** There are two status codes that do not correspond to a defined TWI state, see Table 78.

Status \$F8 indicates that no relevant information is available because the TWINT Flag is not set. This occurs between other states, and when the TWI is not involved in a serial transfer.

Status \$00 indicates that a bus error has occurred during a Two-wire Serial Bus transfer. A bus error occurs when a START or STOP condition occurs at an illegal position in the format frame. Examples of such illegal positions are during the serial transfer of an address byte, a data byte, or an acknowledge bit. When a bus error occurs, TWINT is set. To recover from a bus error, the TWSTO Flag must set and TWINT must be cleared by writing a logic one to it. This causes the TWI to enter the not addressed Slave mode and to clear the TWSTO Flag (no other bits in TWCR are affected). The SDA and SCL lines are released, and no STOP condition is transmitted.

## Table 78. Miscellaneous States

| Status Code                                                             |                                                      | Application Software Response |                |         |       |      |                                                                                                                                               |

|-------------------------------------------------------------------------|------------------------------------------------------|-------------------------------|----------------|---------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| (TWSR)<br>Prescaler Bits                                                | (TWSR) Status of the Two-wire Serial                 |                               | To TWCR        |         |       |      |                                                                                                                                               |

| Prescaler Bits<br>are 0 Bus and Two-wire Serial Inter-<br>face Hardware |                                                      | To/from TWDR                  | STA            | STO     | TWINT | TWEA | Next Action Taken by TWI Hardware                                                                                                             |

| \$F8                                                                    | No relevant state information available; TWINT = "0" | No TWDR action                | No TWCR action |         |       |      | Wait or proceed current transfer                                                                                                              |

| \$00                                                                    | Bus error due to an illegal START or STOP condition  | No TWDR action                | 0              | 0 1 1 X |       | х    | Only the internal hardware is affected, no STOP condi-<br>tion is sent on the bus. In all cases, the bus is released<br>and TWSTO is cleared. |

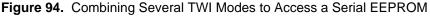

## Combining Several TWI Modes

In some cases, several TWI modes must be combined in order to complete the desired action. Consider for example reading data from a serial EEPROM. Typically, such a transfer involves the following steps:

- 1. The transfer must be initiated

- 2. The EEPROM must be instructed what location should be read

- 3. The reading must be performed

- 4. The transfer must be finished

Note that data is transmitted both from Master to Slave and vice versa. The Master must instruct the Slave what location it wants to read, requiring the use of the MT mode. Subsequently, data must be read from the Slave, implying the use of the MR mode. Thus, the transfer direction must be changed. The Master must keep control of the bus during all these steps, and the steps should be carried out as an atomical operation. If this principle is violated in a multi-master system, another Master can alter the data pointer in the EEPROM between steps 2 and 3, and the Master will read the wrong data location. Such a change in transfer direction is accomplished by transmitting a REPEATED START between the transmission of the address byte and reception of the data. After a REPEATED START, the Master keeps ownership of the bus. The following figure shows the flow in this transfer.

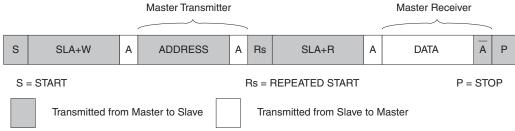

## Multi-master Systems and Arbitration

If multiple Masters are connected to the same bus, transmissions may be initiated simultaneously by one or more of them. The TWI standard ensures that such situations are handled in such a way that one of the Masters will be allowed to proceed with the transfer, and that no data will be lost in the process. An example of an arbitration situation is depicted below, where two Masters are trying to transmit data to a Slave Receiver.

### Figure 95. An Arbitration Example

## JTAG Interface and On-chip Debug System

| Features                  | <ul> <li>JTAG (IEEE std. 1149.1 Compliant) Interface</li> <li>Boundary-scan Capabilities According to the IEEE std. 1149.1 (JTAG) Standard</li> <li>Debugger Access to: <ul> <li>All Internal Peripheral Units</li> <li>Internal and External RAM</li> <li>The Internal Register File</li> <li>Program Counter</li> <li>EEPROM and Flash Memories</li> <li>Extensive On-chip Debug Support for Break Conditions, Including</li> <li>AVR <i>Break</i> Instruction</li> <li>Break on Change of Program Memory Flow</li> <li>Single Step Break</li> <li>Program Memory Breakpoints on Single Address or Address Range</li> <li>Data Memory Breakpoints on Single Address or Address Range</li> </ul> </li> <li>Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface</li> <li>On-chip Debugging Supported by AVR Studio<sup>®</sup></li> </ul> |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overview                  | The AVR IEEE std. 1149.1 compliant JTAG interface can be used for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                           | <ul> <li>Testing PCBs by using the JTAG Boundary-scan capability</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                           | <ul> <li>Programming the non-volatile memories, Fuses and Lock bits</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                           | On-chip Debugging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                           | A brief description is given in the following sections. Detailed descriptions for Programming via the JTAG interface, and using the Boundary-scan Chain can be found in the sections "Programming via the JTAG Interface" on page 278 and "IEEE 1149.1 (JTAG) Boundary-scan" on page 228, respectively. The On-chip Debug support is considered being private JTAG instructions, and distributed within ATMEL and to selected third party vendors only.                                                                                                                                                                                                                                                                                                                                                                                                             |

|                           | Figure 112 shows a block diagram of the JTAG interface and the On-chip Debug system. The TAP Controller is a state machine controlled by the TCK and TMS signals. The TAP Controller selects either the JTAG Instruction Register or one of several Data Registers as the scan chain (Shift Register) between the TDI input and TDO output. The Instruction Register holds JTAG instructions controlling the behavior of a Data Register.                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                           | The ID-Register, Bypass Register, and the Boundary-scan Chain are the Data Registers used for board-level testing. The JTAG Programming Interface (actually consisting of several physical and virtual Data Registers) is used for JTAG Serial Programming via the JTAG interface. The Internal Scan Chain and Break Point Scan Chain are used for On-chip Debugging only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Test Access Port –<br>TAP | The JTAG interface is accessed through four of the AVR's pins. In JTAG terminology, these pins constitute the Test Access Port – TAP. These pins are:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                           | <ul> <li>TMS: Test Mode Select. This pin is used for navigating through the TAP-controller state<br/>machine.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                           | <ul> <li>TCK: Test Clock. JTAG operation is synchronous to TCK.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                           | <ul> <li>TDI: Test Data In. Serial input data to be shifted in to the Instruction Register or Data<br/>Register (Scan Chains).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                           | TDO: Test Data Out. Serial output data from Instruction register or Data Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## On-chip Debug Related Register in I/O Memory

| On-chip  | Debug  |

|----------|--------|

| Register | - OCDR |

| Bit           | 7        | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _    |

|---------------|----------|-----|-----|-----|-----|-----|-----|-----|------|

|               | MSB/IDRD |     |     |     |     |     |     | LSB | OCDR |

| Read/Write    | R/W      | R/W | R/W | R/W | R/W | R/W | R/W | R/W | -    |

| Initial Value | 0        | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

The OCDR Register provides a communication channel from the running program in the microcontroller to the debugger. The CPU can transfer a byte to the debugger by writing to this location. At the same time, an Internal Flag; I/O Debug Register Dirty – IDRD – is set to indicate to the debugger that the register has been written. When the CPU reads the OCDR Register the 7 LSB will be from the OCDR Register, while the MSB is the IDRD bit. The debugger clears the IDRD bit when it has read the information.

In some AVR devices, this register is shared with a standard I/O location. In this case, the OCDR Register can only be accessed if the OCDEN Fuse is programmed, and the debugger enables access to the OCDR Register. In all other cases, the standard I/O location is accessed.

Refer to the debugger documentation for further information on how to use this register.

**Using the JTAG Programming Capabilities** Programming of AVR parts via JTAG is performed via the 4-pin JTAG port, TCK, TMS, TDI and TDO. These are the only pins that need to be controlled/observed to perform JTAG programming (in addition to power pins). It is not required to apply 12V externally. The JTAGEN Fuse must be programmed and the JTD bit in the MCUSR Register must be cleared to enable the JTAG Test Access Port.

The JTAG programming capability supports:

- Flash programming and verifying

- EEPROM programming and verifying

- Fuse programming and verifying

- Lock bit programming and verifying

The Lock bit security is exactly as in Parallel Programming mode. If the Lock bits LB1 or LB2 are programmed, the OCDEN Fuse cannot be programmed unless first doing a chip erase. This is a security feature that ensures no back-door exists for reading out the content of a secured device.

The details on programming through the JTAG interface and programming specific JTAG instructions are given in the section "Programming via the JTAG Interface" on page 278.

Bibliography

For more information about general Boundary-scan, the following literature can be consulted:

- IEEE: IEEE Std. 1149.1-1990. IEEE Standard Test Access Port and Boundary-scan Architecture, IEEE, 1993

- Colin Maunder: The Board Designers Guide to Testable Logic Circuits, Addison-Wesley, 1992

## Memory Programming

**Program And Data** Memory Lock Bits

The ATmega16 provides six Lock bits which can be left unprogrammed ("1") or can be programmed ("0") to obtain the additional features listed in Table 104. The Lock bits can only be erased to "1" with the Chip Erase command.

| Lock Bit Byte | Bit No. | Description   | Default Value    |  |

|---------------|---------|---------------|------------------|--|

|               | 7       | -             | 1 (unprogrammed) |  |

|               | 6       | -             | 1 (unprogrammed) |  |

| BLB12         | 5       | Boot Lock bit | 1 (unprogrammed) |  |

| BLB11         | 4       | Boot Lock bit | 1 (unprogrammed) |  |

| BLB02         | 3       | Boot Lock bit | 1 (unprogrammed) |  |

| BLB01         | 2       | Boot Lock bit | 1 (unprogrammed) |  |

| LB2           | 1       | Lock bit      | 1 (unprogrammed) |  |

| LB1           | 0       | Lock bit      | 1 (unprogrammed) |  |

Note: 1. "1" means unprogrammed, "0" means programmed

Table 104. Lock Bit Protection Modes

| Memory Lock Bits <sup>(2)</sup> |       |       | Protection Type                                                                                                                                                                                                                                                                                           |

|---------------------------------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LB Mode                         | LB2   | LB1   |                                                                                                                                                                                                                                                                                                           |

| 1                               | 1     | 1     | No memory lock features enabled.                                                                                                                                                                                                                                                                          |

| 2                               | 1     | 0     | Further programming of the Flash and EEPROM is disabled in Parallel and SPI/JTAG Serial Programming mode. The Fuse bits are locked in both Serial and Parallel Programming mode. <sup>(1)</sup>                                                                                                           |

| 3                               | 0     | 0     | Further programming and verification of the Flash and EEPROM is disabled in Parallel and SPI/JTAG Serial Programming mode. The Fuse bits are locked in both Serial and Parallel Programming mode. <sup>(1)</sup>                                                                                          |

| BLB0 Mode                       | BLB02 | BLB01 |                                                                                                                                                                                                                                                                                                           |

| 1                               | 1     | 1     | No restrictions for SPM or LPM accessing the Application section.                                                                                                                                                                                                                                         |

| 2                               | 1     | 0     | SPM is not allowed to write to the Application section.                                                                                                                                                                                                                                                   |

| 3                               | 0     | 0     | SPM is not allowed to write to the Application section, and<br>LPM executing from the Boot Loader section is not<br>allowed to read from the Application section. If interrupt<br>vectors are placed in the Boot Loader section, interrupts<br>are disabled while executing from the Application section. |

| 4                               | 0     | 1     | LPM executing from the Boot Loader section is not<br>allowed to read from the Application section. If interrupt<br>vectors are placed in the Boot Loader section, interrupts<br>are disabled while executing from the Application section.                                                                |

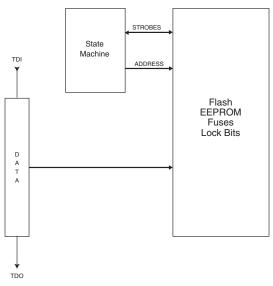

Figure 143. Virtual Flash Page Load Register

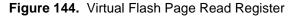

## Virtual Flash Page Read Register

The Virtual Flash Page Read Register is a virtual scan chain with length equal to the number of bits in one Flash page plus 8. Internally the Shift Register is 8-bit, and the data are automatically transferred from the Flash data page byte by byte. The first 8 cycles are used to transfer the first byte to the internal Shift Register, and the bits that are shifted out during these 8 cycles should be ignored. Following this initialization, data are shifted out starting with the LSB of the first instruction in the page and ending with the MSB of the last instruction in the page. This provides an efficient way to read one full Flash page to verify programming.

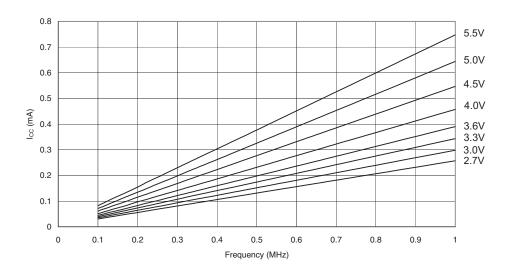

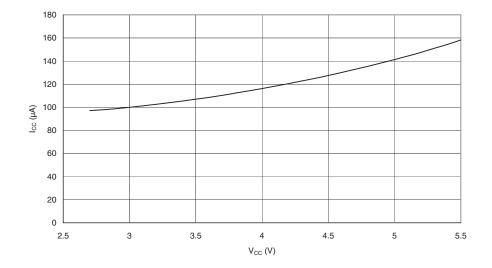

Idle Supply Current Figure 156. Idle Supply Current vs. Frequency (0.1 MHz - 1.0 MHz)

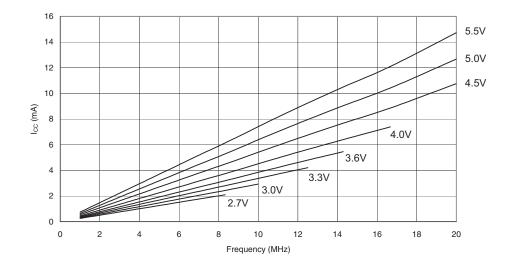

Figure 157. Idle Supply Current vs. Frequency (1 MHz - 20 MHz)

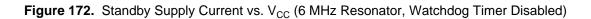

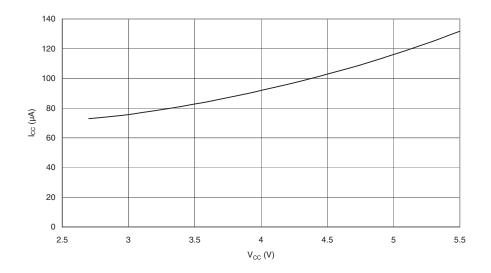

Figure 173. Standby Supply Current vs.  $V_{CC}$  (6 MHz Xtal, Watchdog Timer Disabled)

## **Pin Pullup**

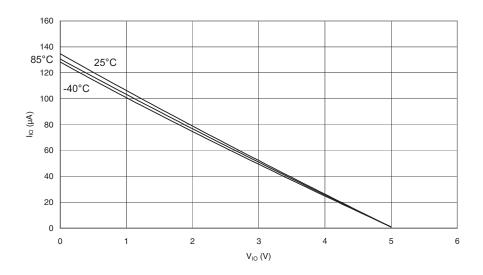

Figure 174. I/O Pin Pull-Up Resistor Current vs. Input Voltage ( $V_{CC} = 5V$ )

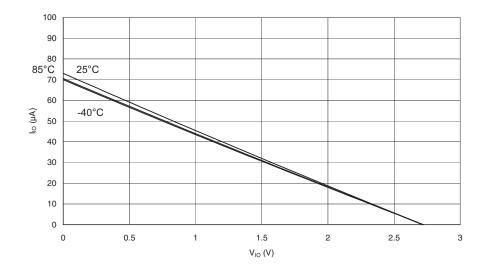

Figure 175. I/O Pin Pull-Up Resistor Current vs. Input Voltage (V<sub>CC</sub> = 2.7V)

Prescaling and Conversion Timing 207 Changing Channel or Reference Selection 210 ADC Noise Canceler 211 ADC Conversion Result 216

## JTAG Interface and On-chip Debug System 222

Features 222 Overview 222 Test Access Port – TAP 222 TAP Controller 224 Using the Boundary-scan Chain 225 Using the On-chip Debug System 225 On-chip Debug Specific JTAG Instructions 226 On-chip Debug Related Register in I/O Memory 227 Using the JTAG Programming Capabilities 227 Bibliography 227

## IEEE 1149.1 (JTAG) Boundary-scan 228

Features 228 System Overview 228 Data Registers 228 Boundary-scan Specific JTAG Instructions 230 Boundary-scan Chain 232 ATmega16 Boundary-scan Order 241 Boundary-scan Description Language Files 245

## Boot Loader Support – Read-While-Write Self-Programming 246

Features 246 Application and Boot Loader Flash Sections 246 Read-While-Write and no Read-While-Write Flash Sections 246 Boot Loader Lock Bits 248 Entering the Boot Loader Program 249 Addressing the Flash during Self-Programming 251 Self-Programming the Flash 252

## Memory Programming 259

Program And Data Memory Lock Bits 259 Fuse Bits 260 Signature Bytes 261 Calibration Byte 261 Page Size 262 Parallel Programming Parameters, Pin Mapping, and Commands 262 Parallel Programming 265 Serial Downloading 273 Programming via the JTAG Interface 278

# iv ATmega16(L)