Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

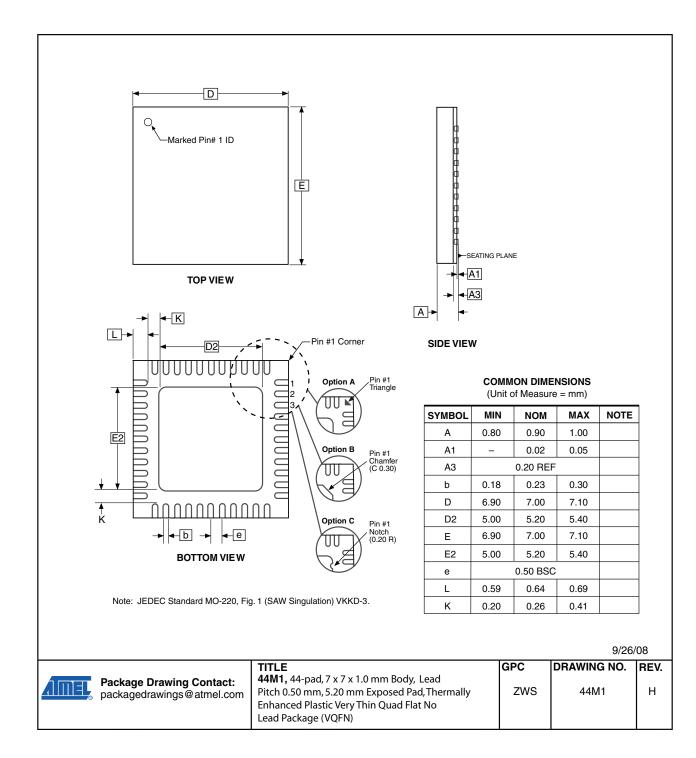

| Package / Case             | 44-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 44-VQFN (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega16I-8mi |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## About Code Examples

This documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C Compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C Compiler documentation for more details.

## AVR ATmega16 Memories

This section describes the different memories in the ATmega16. The AVR architecture has two main memory spaces, the Data Memory and the Program Memory space. In addition, the ATmega16 features an EEPROM Memory for data storage. All three memory spaces are linear and regular.

## In-System Reprogrammable Flash Program Memory

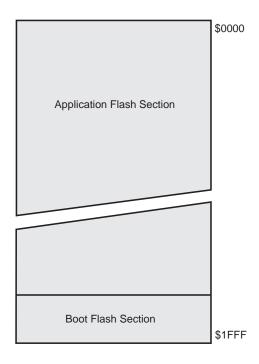

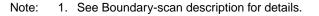

The ATmega16 contains 16 Kbytes On-chip In-System Reprogrammable Flash memory for program storage. Since all AVR instructions are 16 or 32 bits wide, the Flash is organized as 8K × 16. For software security, the Flash Program memory space is divided into two sections, Boot Program section and Application Program section.

The Flash memory has an endurance of at least 10,000 write/erase cycles. The ATmega16 Program Counter (PC) is 13 bits wide, thus addressing the 8K program memory locations. The operation of Boot Program section and associated Boot Lock bits for software protection are described in detail in "Boot Loader Support – Read-While-Write Self-Programming" on page 246. "Memory Programming" on page 259 contains a detailed description on Flash data serial downloading using the SPI pins or the JTAG interface.

Constant tables can be allocated within the entire program memory address space (see the LPM – Load Program Memory Instruction Description).

Timing diagrams for instruction fetch and execution are presented in "Instruction Execution Timing" on page 13.

Figure 8. Program Memory Map

## Oscillator Calibration Register – OSCCAL

| Bit           | 7    | 6    | 5    | 4           | 3             | 2     | 1    | 0    | _      |

|---------------|------|------|------|-------------|---------------|-------|------|------|--------|

|               | CAL7 | CAL6 | CAL5 | CAL4        | CAL3          | CAL2  | CAL1 | CAL0 | OSCCAL |

| Read/Write    | R/W  | R/W  | R/W  | R/W         | R/W           | R/W   | R/W  | R/W  | •      |

| Initial Value |      |      | Devi | ce Specific | Calibration \ | /alue |      |      |        |

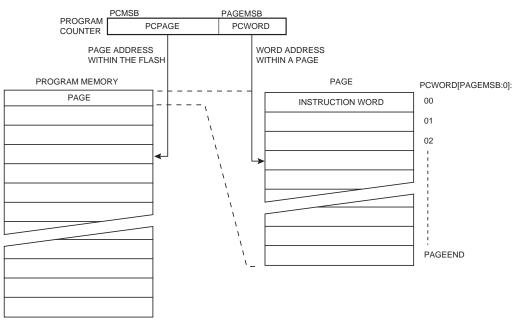

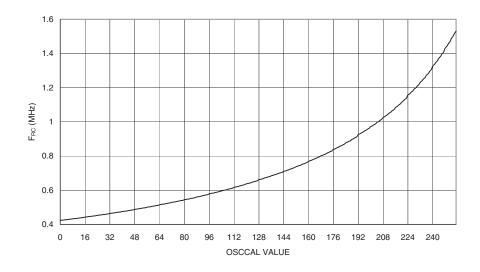

## • Bits 7..0 - CAL7..0: Oscillator Calibration Value

Writing the calibration byte to this address will trim the Internal Oscillator to remove process variations from the Oscillator frequency. This is done automatically during Chip Reset. When OSCCAL is zero, the lowest available frequency is chosen. Writing non-zero values to this register will increase the frequency of the Internal Oscillator. Writing \$FF to the register gives the highest available frequency. The calibrated Oscillator is used to time EEPROM and Flash access. If EEPROM or Flash is written, do not calibrate to more than 10% above the nominal frequency. Otherwise, the EEPROM or Flash write may fail. Note that the Oscillator is intended for calibration to 1.0 MHz, 2.0 MHz, 4.0 MHz, or 8.0 MHz. Tuning to other values is not guaranteed, as indicated in Table 11.

| OSCCAL Value | Min Frequency in Percentage of<br>Nominal Frequency (%) | Max Frequency in Percentage of<br>Nominal Frequency (%) |

|--------------|---------------------------------------------------------|---------------------------------------------------------|

| \$00         | 50                                                      | 100                                                     |

| \$7F         | 75                                                      | 150                                                     |

| \$FF         | 100                                                     | 200                                                     |

Table 11. Internal RC Oscillator Frequency Range.

- **Minimizing Power Consumption** There are several issues to consider when trying to minimize the power consumption in an AVR controlled system. In general, sleep modes should be used as much as possible, and the sleep mode should be selected so that as few as possible of the device's functions are operating. All functions not needed should be disabled. In particular, the following modules may need special consideration when trying to achieve the lowest possible power consumption.

- Analog to DigitalIf enabled, the ADC will be enabled in all sleep modes. To save power, the ADC should be dis-<br/>abled before entering any sleep mode. When the ADC is turned off and on again, the next<br/>conversion will be an extended conversion. Refer to "Analog to Digital Converter" on page 204<br/>for details on ADC operation.

- Analog Comparator When entering Idle mode, the Analog Comparator should be disabled if not used. When entering ADC Noise Reduction mode, the Analog Comparator should be disabled. In the other sleep modes, the Analog Comparator is automatically disabled. However, if the Analog Comparator is set up to use the Internal Voltage Reference as input, the Analog Comparator should be disabled in all sleep modes. Otherwise, the Internal Voltage Reference will be enabled, independent of sleep mode. Refer to "Analog Comparator" on page 201 for details on how to configure the Analog Comparator.

- **Brown-out Detector** If the Brown-out Detector is not needed in the application, this module should be turned off. If the Brown-out Detector is enabled by the BODEN Fuse, it will be enabled in all sleep modes, and hence, always consume power. In the deeper sleep modes, this will contribute significantly to the total current consumption. Refer to "Brown-out Detection" on page 40 for details on how to configure the Brown-out Detector.

- Internal Voltage The Internal Voltage Reference will be enabled when needed by the Brown-out Detector, the Analog Comparator or the ADC. If these modules are disabled as described in the sections above, the internal voltage reference will be disabled and it will not be consuming power. When turned on again, the user must allow the reference to start up before the output is used. If the reference is kept on in sleep mode, the output can be used immediately. Refer to "Internal Voltage Reference" on page 42 for details on the start-up time.

- Watchdog Timer If the Watchdog Timer is not needed in the application, this module should be turned off. If the Watchdog Timer is enabled, it will be enabled in all sleep modes, and hence, always consume power. In the deeper sleep modes, this will contribute significantly to the total current consumption. Refer to "Watchdog Timer" on page 42 for details on how to configure the Watchdog Timer.

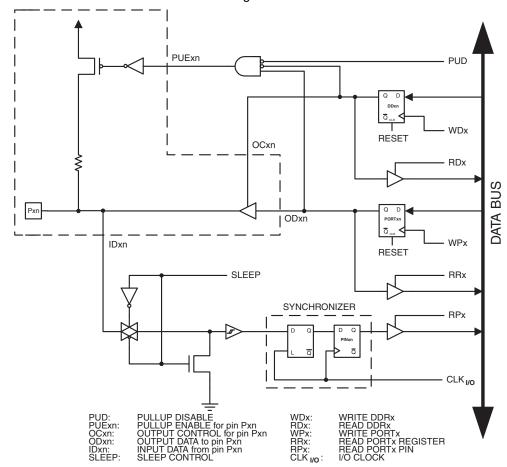

- **Port Pins** When entering a sleep mode, all port pins should be configured to use minimum power. The most important thing is then to ensure that no pins drive resistive loads. In sleep modes where the both the I/O clock ( $clk_{I/O}$ ) and the ADC clock ( $clk_{ADC}$ ) are stopped, the input buffers of the device will be disabled. This ensures that no power is consumed by the input logic when not needed. In some cases, the input logic is needed for detecting wake-up conditions, and it will then be enabled. Refer to the section "Digital Input Enable and Sleep Modes" on page 54 for details on which pins are enabled. If the input buffer is enabled and the input signal is left floating or have an analog signal level close to  $V_{CC}/2$ , the input buffer will use excessive power.

## • Bit 1, 0 – ISC01, ISC00: Interrupt Sense Control 0 Bit 1 and Bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask are set. The level and edges on the external INT0 pin that activate the interrupt are defined in Table 35. The value on the INT0 pin is sampled before detecting edges. If edge or toggle interrupt is selected, pulses that last longer than one clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt.

| ISC01 | ISC00 | Description                                                |  |

|-------|-------|------------------------------------------------------------|--|

| 0     | 0     | The low level of INT0 generates an interrupt request.      |  |

| 0     | 1     | Any logical change on INT0 generates an interrupt request. |  |

| 1     | 0     | The falling edge of INT0 generates an interrupt request.   |  |

| 1     | 1     | The rising edge of INT0 generates an interrupt request.    |  |

## Table 35. Interrupt 0 Sense Control

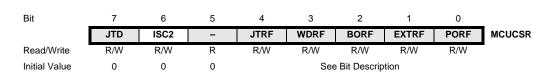

## MCU Control and Status Register – MCUCSR

## • Bit 6 – ISC2: Interrupt Sense Control 2

The Asynchronous External Interrupt 2 is activated by the external pin INT2 if the SREG I-bit and the corresponding interrupt mask in GICR are set. If ISC2 is written to zero, a falling edge on INT2 activates the interrupt. If ISC2 is written to one, a rising edge on INT2 activates the interrupt. Edges on INT2 are registered asynchronously. Pulses on INT2 wider than the minimum pulse width given in Table 36 will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. When changing the ISC2 bit, an interrupt can occur. Therefore, it is recommended to first disable INT2 by clearing its Interrupt Enable bit in the GICR Register. Then, the ISC2 bit can be changed. Finally, the INT2 Interrupt Flag should be cleared by writing a logical one to its Interrupt Flag bit (INTF2) in the GIFR Register before the interrupt is re-enabled.

## Table 36. Asynchronous External Interrupt Characteristics

| Symbol           | Parameter                                                  | Condition | Min | Тур | Max | Units |

|------------------|------------------------------------------------------------|-----------|-----|-----|-----|-------|

| t <sub>INT</sub> | Minimum pulse width for<br>asynchronous external interrupt |           |     | 50  |     | ns    |

## General Interrupt Control Register – GICR

## • Bit 7 – INT1: External Interrupt Request 1 Enable

When the INT1 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is enabled. The Interrupt Sense Control1 bits 1/0 (ISC11 and ISC10) in the MCU General Control Register (MCUCR) define whether the External Interrupt is activated on rising

When OC0 is connected to the pin, the function of the COM01:0 bits depends on the WGM01:0 bit setting. Table 39 shows the COM01:0 bit functionality when the WGM01:0 bits are set to a normal or CTC mode (non-PWM).

| COM01 | COM01 COM00 Description |                                          |

|-------|-------------------------|------------------------------------------|

| 0     | 0                       | Normal port operation, OC0 disconnected. |

| 0     | 1                       | Toggle OC0 on compare match              |

| 1     | 0                       | Clear OC0 on compare match               |

| 1     | 1                       | Set OC0 on compare match                 |

Table 39.

Compare Output Mode, non-PWM Mode

Table 40 shows the COM01:0 bit functionality when the WGM01:0 bits are set to fast PWM mode.

| Table 40. | Compare | Output M | ode, Fast | PWM Mode <sup>(1)</sup> |

|-----------|---------|----------|-----------|-------------------------|

|-----------|---------|----------|-----------|-------------------------|

| COM01 | COM00 | Description                                                         |  |

|-------|-------|---------------------------------------------------------------------|--|

| 0     | 0     | Normal port operation, OC0 disconnected.                            |  |

| 0     | 1     | Reserved                                                            |  |

| 1     | 0     | Clear OC0 on compare match, set OC0 at BOTTOM, (non-inverting mode) |  |

| 1     | 1     | Set OC0 on compare match, clear OC0 at BOTTOM, (inverting mode)     |  |

Note: 1. A special case occurs when OCR0 equals TOP and COM01 is set. In this case, the compare match is ignored, but the set or clear is done at TOP. See "Fast PWM Mode" on page 77 for more details.

Table 41 shows the COM01:0 bit functionality when the WGM01:0 bits are set to phase correct PWM mode.

| Table 41. | Compare Out | out Mode, Phase | Correct PWM Mode <sup>(1)</sup> |

|-----------|-------------|-----------------|---------------------------------|

|-----------|-------------|-----------------|---------------------------------|

| COM01 | COM00                                                                                      | Description                                                                              |

|-------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 0     | 0                                                                                          | Normal port operation, OC0 disconnected.                                                 |

| 0     | 1                                                                                          | Reserved                                                                                 |

| 1     | 0 Clear OC0 on compare match when up-counting. Set OC0 on comp<br>match when downcounting. |                                                                                          |

| 1     | 1                                                                                          | Set OC0 on compare match when up-counting. Clear OC0 on compare match when downcounting. |

Note: 1. A special case occurs when OCR0 equals TOP and COM01 is set. In this case, the compare match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 79 for more details.

| Table 45. Compare Output Mode, Fast PWI | /\'' |

|-----------------------------------------|------|

|-----------------------------------------|------|

| COM1A1/COM1B1 | COM1A0/COM1B0 | Description                                                                                  |

|---------------|---------------|----------------------------------------------------------------------------------------------|

| 0             | 0             | Normal port operation, OC1A/OC1B disconnected.                                               |

| 0             | 1             | WGM13:0 = 15: Toggle OC1A on Compare<br>Match, OC1B disconnected (normal port<br>operation). |

|               |               | For all other WGM13:0 settings, normal port operation, OCnA/OCnB disconnected.               |

| 1             | 0             | Clear OC1A/OC1B on compare match, set<br>OC1A/OC1B at BOTTOM,<br>(non-inverting mode)        |

| 1             | 1             | Set OC1A/OC1B on compare match, clear<br>OC1A/OC1B at BOTTOM,<br>(inverting mode)            |

Note: 1. A special case occurs when OCR1A/OCR1B equals TOP and COM1A1/COM1B1 is set. In this case the compare match is ignored, but the set or clear is done at BOTTOM. See "Fast PWM Mode" on page 102. for more details.

Table 46 shows the COM1x1:0 bit functionality when the WGM13:0 bits are set to the phase correct or the phase and frequency correct, PWM mode.

| COM1A1/COM1B1 | COM1A0/COM1B0 | Description                                                                                                                                                                            |

|---------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | 0             | Normal port operation, OC1A/OC1B disconnected.                                                                                                                                         |

| 0             | 1             | WGM13:0 = 9 or 14: Toggle OCnA on<br>Compare Match, OCnB disconnected (normal<br>port operation).<br>For all other WGM13:0 settings, normal port<br>operation, OC1A/OC1B disconnected. |

| 1             | 0             | Clear OC1A/OC1B on compare match when<br>up-counting. Set OC1A/OC1B on compare<br>match when downcounting.                                                                             |

| 1             | 1             | Set OC1A/OC1B on compare match when up-<br>counting. Clear OC1A/OC1B on compare<br>match when downcounting.                                                                            |

Table 46. Compare Output Mode, Phase Correct and Phase and Frequency Correct PWM <sup>(1)</sup>

Note: 1. A special case occurs when OCR1A/OCR1B equals TOP and COM1A1/COM1B1 is set. See "Phase Correct PWM Mode" on page 104. for more details.

- Bit 3 FOC1A: Force Output Compare for Channel A

- Bit 2 FOC1B: Force Output Compare for Channel B

The FOC1A/FOC1B bits are only active when the WGM13:0 bits specifies a non-PWM mode. However, for ensuring compatibility with future devices, these bits must be set to zero when TCCR1A is written when operating in a PWM mode. When writing a logical one to the FOC1A/FOC1B bit, an immediate compare match is forced on the Waveform Generation unit. The OC1A/OC1B output is changed according to its COM1x1:0 bits setting. Note that the FOC1A/FOC1B bits are implemented as strobes. Therefore it is the value present in the COM1x1:0 bits that determine the effect of the forced compare.

**bottom** Signalizes that TCNT2 has reached minimum value (zero).

Depending on the mode of operation used, the counter is cleared, incremented, or decremented at each timer clock ( $clk_{T2}$ ).  $clk_{T2}$  can be generated from an external or internal clock source, selected by the Clock Select bits (CS22:0). When no clock source is selected (CS22:0 = 0) the timer is stopped. However, the TCNT2 value can be accessed by the CPU, regardless of whether  $clk_{T2}$  is present or not. A CPU write overrides (has priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the WGM21 and WGM20 bits located in the Timer/Counter Control Register (TCCR2). There are close connections between how the counter behaves (counts) and how waveforms are generated on the Output Compare output OC2. For more details about advanced counting sequences and waveform generation, see "Modes of Operation" on page 122.

The Timer/Counter Overflow (TOV2) Flag is set according to the mode of operation selected by the WGM21:0 bits. TOV2 can be used for generating a CPU interrupt.

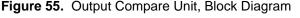

**Output Compare Unit** The 8-bit comparator continuously compares TCNT2 with the Output Compare Register (OCR2). Whenever TCNT2 equals OCR2, the comparator signals a match. A match will set the Output Compare Flag (OCF2) at the next timer clock cycle. If enabled (OCIE2 = 1), the Output Compare Flag generates an output compare interrupt. The OCF2 Flag is automatically cleared when the interrupt is executed. Alternatively, the OCF2 Flag can be cleared by software by writing a logical one to its I/O bit location. The waveform generator uses the match signal to generate an output according to operating mode set by the WGM21:0 bits and Compare Output mode (COM21:0) bits. The max and bottom signals are used by the waveform generator for handling the special cases of the extreme values in some modes of operation ("Modes of Operation" on page 122). Figure 55 shows a block diagram of the output compare unit.

The OCR2 Register is double buffered when using any of the Pulse Width Modulation (PWM) modes. For the normal and Clear Timer on Compare (CTC) modes of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR2 Compare Register

to either top or bottom of the counting sequence. The synchronization prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby making the output glitch-free.

The OCR2 Register access may seem complex, but this is not case. When the double buffering is enabled, the CPU has access to the OCR2 Buffer Register, and if double buffering is disabled the CPU will access the OCR2 directly.

Force OutputIn non-PWM waveform generation modes, the match output of the comparator can be forced by<br/>writing a one to the Force Output Compare (FOC2) bit. Forcing compare match will not set the<br/>OCF2 Flag or reload/clear the timer, but the OC2 pin will be updated as if a real compare match<br/>had occurred (the COM21:0 bits settings define whether the OC2 pin is set, cleared or toggled).

Compare MatchAll CPU write operations to the TCNT2 Register will block any compare match that occurs in the<br/>next timer clock cycle, even when the timer is stopped. This feature allows OCR2 to be initialized<br/>to the same value as TCNT2 without triggering an interrupt when the Timer/Counter clock is<br/>enabled.

#### Using the Output Compare Unit Since writing TCNT2 in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNT2 when using the output compare unit, independently of whether the Timer/Counter is running or not. If the value written to TCNT2 equals the OCR2 value, the compare match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT2 value equal to BOTTOM when the counter is downcounting.

The setup of the OC2 should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC2 value is to use the Force Output Compare (FOC2) strobe bit in Normal mode. The OC2 Register keeps its value even when changing between Waveform Generation modes.

Be aware that the COM21:0 bits are not double buffered together with the compare value. Changing the COM21:0 bits will take effect immediately.

## **Data Modes**

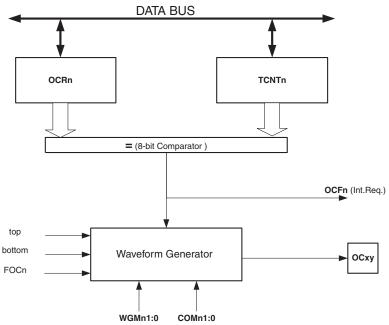

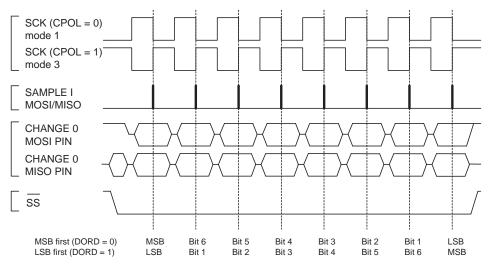

There are four combinations of SCK phase and polarity with respect to serial data, which are determined by control bits CPHA and CPOL. The SPI data transfer formats are shown in Figure 67 and Figure 68. Data bits are shifted out and latched in on opposite edges of the SCK signal, ensuring sufficient time for data signals to stabilize. This is clearly seen by summarizing Table 56 and Table 57, as done below:

Table 59. CPOL and CPHA Functionality

|                    | Leading Edge     | Trailing Edge    | SPI Mode |

|--------------------|------------------|------------------|----------|

| CPOL = 0, CPHA = 0 | Sample (Rising)  | Setup (Falling)  | 0        |

| CPOL = 0, CPHA = 1 | Setup (Rising)   | Sample (Falling) | 1        |

| CPOL = 1, CPHA = 0 | Sample (Falling) | Setup (Rising)   | 2        |

| CPOL = 1, CPHA = 1 | Setup (Falling)  | Sample (Rising)  | 3        |

Figure 68. SPI Transfer Format with CPHA = 1

| f                     |               | f <sub>osc</sub> = 8.0000 MHz |         |       | f <sub>osc</sub> = 11.0592 MHz |             |         | f <sub>osc</sub> = 14.7456 MHz |         |             |         |       |

|-----------------------|---------------|-------------------------------|---------|-------|--------------------------------|-------------|---------|--------------------------------|---------|-------------|---------|-------|

| Baud<br>Rate<br>(bps) | U2X = 0       |                               | U2X = 1 |       | U2X = 0                        |             | U2X = 1 |                                | U2X = 0 |             | U2X = 1 |       |

|                       | UBRR          | Error                         | UBRR    | Error | UBRR                           | Error       | UBRR    | Error                          | UBRR    | Error       | UBRR    | Error |

| 2400                  | 207           | 0.2%                          | 416     | -0.1% | 287                            | 0.0%        | 575     | 0.0%                           | 383     | 0.0%        | 767     | 0.0%  |

| 4800                  | 103           | 0.2%                          | 207     | 0.2%  | 143                            | 0.0%        | 287     | 0.0%                           | 191     | 0.0%        | 383     | 0.0%  |

| 9600                  | 51            | 0.2%                          | 103     | 0.2%  | 71                             | 0.0%        | 143     | 0.0%                           | 95      | 0.0%        | 191     | 0.0%  |

| 14.4k                 | 34            | -0.8%                         | 68      | 0.6%  | 47                             | 0.0%        | 95      | 0.0%                           | 63      | 0.0%        | 127     | 0.0%  |

| 19.2k                 | 25            | 0.2%                          | 51      | 0.2%  | 35                             | 0.0%        | 71      | 0.0%                           | 47      | 0.0%        | 95      | 0.0%  |

| 28.8k                 | 16            | 2.1%                          | 34      | -0.8% | 23                             | 0.0%        | 47      | 0.0%                           | 31      | 0.0%        | 63      | 0.0%  |

| 38.4k                 | 12            | 0.2%                          | 25      | 0.2%  | 17                             | 0.0%        | 35      | 0.0%                           | 23      | 0.0%        | 47      | 0.0%  |

| 57.6k                 | 8             | -3.5%                         | 16      | 2.1%  | 11                             | 0.0%        | 23      | 0.0%                           | 15      | 0.0%        | 31      | 0.0%  |

| 76.8k                 | 6             | -7.0%                         | 12      | 0.2%  | 8                              | 0.0%        | 17      | 0.0%                           | 11      | 0.0%        | 23      | 0.0%  |

| 115.2k                | 3             | 8.5%                          | 8       | -3.5% | 5                              | 0.0%        | 11      | 0.0%                           | 7       | 0.0%        | 15      | 0.0%  |

| 230.4k                | 1             | 8.5%                          | 3       | 8.5%  | 2                              | 0.0%        | 5       | 0.0%                           | 3       | 0.0%        | 7       | 0.0%  |

| 250k                  | 1             | 0.0%                          | 3       | 0.0%  | 2                              | -7.8%       | 5       | -7.8%                          | 3       | -7.8%       | 6       | 5.3%  |

| 0.5M                  | 0             | 0.0%                          | 1       | 0.0%  | _                              | _           | 2       | -7.8%                          | 1       | -7.8%       | 3       | -7.8% |

| 1M                    | -             | _                             | 0       | 0.0%  | -                              | _           | _       | -                              | 0       | -7.8%       | 1       | -7.8% |

| Max <sup>(1)</sup>    | 0.5 Mbps 1 Mb |                               | bps     | 691.2 | Kbps                           | 1.3824 Mbps |         | 921.6 Kbps                     |         | 1.8432 Mbps |         |       |

| Table 70. Examples of UBRR Settings for Commonly Used Oscillator Frequencies (Continued) |  |

|------------------------------------------------------------------------------------------|--|

|------------------------------------------------------------------------------------------|--|

1. UBRR = 0, Error = 0.0%

## **Two-wire Serial** Interface

| Features                                       | <ul> <li>Simple Yet Powerful and Flexible Communication Interface, Only Two Bus Lines Needed</li> <li>Both Master and Slave Operation Supported</li> <li>Device Can Operate as Transmitter or Receiver</li> <li>7-bit Address Space allows up to 128 Different Slave Addresses</li> <li>Multi-master Arbitration Support</li> <li>Up to 400 kHz Data Transfer Speed</li> <li>Slew-rate Limited Output Drivers</li> <li>Noise Suppression Circuitry Rejects Spikes on Bus Lines</li> <li>Fully Programmable Slave Address with General Call Support</li> <li>Address Recognition causes Wake-up when AVR is in Sleep Mode</li> </ul> |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

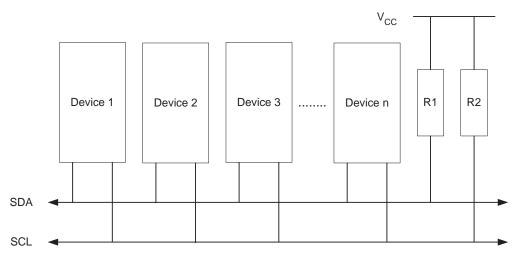

| Two-wire Serial<br>Interface Bus<br>Definition | The Two-wire Serial Interface (TWI) is ideally suited for typical microcontroller applications. The TWI protocol allows the systems designer to interconnect up to 128 different devices using only two bi-directional bus lines, one for clock (SCL) and one for data (SDA). The only external hardware needed to implement the bus is a single pull-up resistor for each of the TWI bus lines. All                                                                                                                                                                                                                                |

g only hardes. All devices connected to the bus have individual addresses, and mechanisms for resolving bus contention are inherent in the TWI protocol.

## Figure 76. TWI Bus Interconnection

## **TWI Terminology**

The following definitions are frequently encountered in this section.

## Table 72. TWI Terminology

| Term        | Description                                                                                       |

|-------------|---------------------------------------------------------------------------------------------------|

| Master      | The device that initiates and terminates a transmission. The Master also generates the SCL clock. |

| Slave       | The device addressed by a Master.                                                                 |

| Transmitter | The device placing data on the bus.                                                               |

| Receiver    | The device reading data from the bus.                                                             |

## Electrical Interconnection

As depicted in Figure 76, both bus lines are connected to the positive supply voltage through pull-up resistors. The bus drivers of all TWI-compliant devices are open-drain or open-collector. This implements a wired-AND function which is essential to the operation of the interface. A low level on a TWI bus line is generated when one or more TWI devices output a zero. A high level is output when all TWI devices tri-state their outputs, allowing the pull-up resistors to pull the line high. Note that all AVR devices connected to the TWI bus must be powered in order to allow any bus operation.

The number of devices that can be connected to the bus is only limited by the bus capacitance limit of 400 pF and the 7-bit Slave address space. A detailed specification of the electrical characteristics of the TWI is given in "Two-wire Serial Interface Characteristics" on page 294. Two different sets of specifications are presented there, one relevant for bus speeds below 100 kHz, and one valid for bus speeds up to 400 kHz.

## Data Transfer and Frame Format

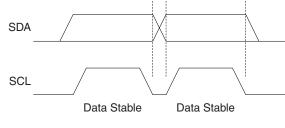

## **Transferring Bits**

Each data bit transferred on the TWI bus is accompanied by a pulse on the clock line. The level of the data line must be stable when the clock line is high. The only exception to this rule is for generating start and stop conditions.

Figure 77. Data Validity

Data Change

# **START and STOP Conditions** The Master initiates and terminates a data transmission. The transmission is initiated when the Master issues a STOP condition on the bus, and it is terminated when the Master issues a STOP condition. Between a START and a STOP condition, the bus is considered busy, and no other Master should try to seize control of the bus. A special case occurs when a new START condition is issued between a START and STOP condition. This is referred to as a REPEATED START condition, and is used when the Master wishes to initiate a new transfer without releasing control of the bus. After a REPEATED START, the bus is considered busy until the next STOP. This is identical to the START behavior, and therefore START is used to describe both START and REPEATED START for the remainder of this datasheet, unless otherwise noted. As depicted below, START and STOP conditions are signalled by changing the level of the SDA line when the SCL line is high.

| ADC Input Channels       | When changing channel selections, the user should observe the following guidelines to ensure that the correct channel is selected:                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | In Single Conversion mode, always select the channel before starting the conversion. The chan-<br>nel selection may be changed one ADC clock cycle after writing one to ADSC. However, the<br>simplest method is to wait for the conversion to complete before changing the channel selection.                                                                                                                                                                                                                                                                           |

|                          | In Free Running mode, always select the channel before starting the first conversion. The chan-<br>nel selection may be changed one ADC clock cycle after writing one to ADSC. However, the<br>simplest method is to wait for the first conversion to complete, and then change the channel<br>selection. Since the next conversion has already started automatically, the next result will reflect<br>the previous channel selection. Subsequent conversions will reflect the new channel selection.                                                                    |

|                          | When switching to a differential gain channel, the first conversion result may have a poor accuracy due to the required settling time for the automatic offset cancellation circuitry. The user should preferably disregard the first conversion result.                                                                                                                                                                                                                                                                                                                 |

| ADC Voltage<br>Reference | The reference voltage for the ADC ( $V_{REF}$ ) indicates the conversion range for the ADC. Single ended channels that exceed $V_{REF}$ will result in codes close to 0x3FF. $V_{REF}$ can be selected as either AVCC, internal 2.56V reference, or external AREF pin.                                                                                                                                                                                                                                                                                                   |

|                          | AVCC is connected to the ADC through a passive switch. The internal 2.56V reference is generated from the internal bandgap reference ( $V_{BG}$ ) through an internal amplifier. In either case, the external AREF pin is directly connected to the ADC, and the reference voltage can be made more immune to noise by connecting a capacitor between the AREF pin and ground. $V_{REF}$ can also be measured at the AREF pin with a high impedant voltmeter. Note that $V_{REF}$ is a high impedant source, and only a capacitive load should be connected in a system. |

|                          | If the user has a fixed voltage source connected to the AREF pin, the user may not use the other reference voltage options in the application, as they will be shorted to the external voltage. If no external voltage is applied to the AREF pin, the user may switch between AVCC and 2.56V as reference selection. The first ADC conversion result after switching reference voltage source may be inaccurate, and the user is advised to discard this result.                                                                                                        |

|                          | If differential channels are used, the selected reference should not be closer to AVCC than indicated in Table 122 on page 297.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ADC Noise<br>Canceler    | The ADC features a noise canceler that enables conversion during sleep mode to reduce noise induced from the CPU core and other I/O peripherals. The noise canceler can be used with ADC Noise Reduction and Idle mode. To make use of this feature, the following procedure should be used:                                                                                                                                                                                                                                                                             |

|                          | <ol> <li>Make sure that the ADC is enabled and is not busy converting. Single Conversion<br/>Mode must be selected and the ADC conversion complete interrupt must be<br/>enabled.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                             |

|                          | <ol><li>Enter ADC Noise Reduction mode (or Idle mode). The ADC will start a conversion<br/>once the CPU has been halted.</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                          | 3. If no other interrupts occur before the ADC conversion completes, the ADC interrupt will wake up the CPU and execute the ADC Conversion Complete interrupt routine. If another interrupt wakes up the CPU before the ADC conversion is complete, that interrupt will be executed, and an ADC Conversion Complete interrupt request will be generated when the ADC conversion completes. The CPU will remain in active mode until a new sleep command is executed.                                                                                                     |

|                          | Note that the ADC will not be automatically turned off when entering other sleep modes than Idle mode and ADC Noise Reduction mode. The user is advised to write zero to ADEN before enter-                                                                                                                                                                                                                                                                                                                                                                              |

Noise Reduction mode. The user is advised to write zero to nter ing such sleep modes to avoid excessive power consumption. If the ADC is enabled in such

Boundary-scan and the Two-wire Interface

The 2 Two-wire Interface pins SCL and SDA have one additional control signal in the scanchain; Two-wire Interface Enable – TWIEN. As shown in Figure 118, the TWIEN signal enables a tri-state buffer with slew-rate control in parallel with the ordinary digital port pins. A general scan cell as shown in Figure 122 is attached to the TWIEN signal.

- Notes: 1. A separate scan chain for the 50 ns spike filter on the input is not provided. The ordinary scan support for digital port pins suffice for connectivity tests. The only reason for having TWIEN in the scan path, is to be able to disconnect the slew-rate control buffer when doing boundary-scan.

- 2. Make sure the OC and TWIEN signals are not asserted simultaneously, as this will lead to drive contention.

## Table 98. Boot Reset Fuse<sup>(1)</sup>

| BOOTRST | Reset Address                                                |

|---------|--------------------------------------------------------------|

| 1       | Reset Vector = Application reset (address \$0000)            |

| 0       | Reset Vector = Boot Loader reset (see Table 100 on page 257) |

Note: 1. "1" means unprogrammed, "0" means programmed

The Store Program Memory Control Register contains the control bits needed to control the Boot Loader operations.

Bit 7 6 3 2 0 5 4 SPMIE RWWSB RWWSRE BLBSET PGWRT PGERS SPMEN SPMCR -Read/Write R/W R R R/W R/W R/W R/W R/W Initial value 0 0 0 0 0 0 0 0

## • Bit 7 – SPMIE: SPM Interrupt Enable

When the SPMIE bit is written to one, and the I-bit in the Status Register is set (one), the SPM ready interrupt will be enabled. The SPM ready Interrupt will be executed as long as the SPMEN bit in the SPMCR Register is cleared.

## • Bit 6 - RWWSB: Read-While-Write Section Busy

When a self-programming (Page Erase or Page Write) operation to the RWW section is initiated, the RWWSB will be set (one) by hardware. When the RWWSB bit is set, the RWW section cannot be accessed. The RWWSB bit will be cleared if the RWWSRE bit is written to one after a Self-Programming operation is completed. Alternatively the RWWSB bit will automatically be cleared if a page load operation is initiated.

### • Bit 5 – Res: Reserved Bit

This bit is a reserved bit in the ATmega16 and always read as zero.

## • Bit 4 – RWWSRE: Read-While-Write Section Read Enable

When programming (Page Erase or Page Write) to the RWW section, the RWW section is blocked for reading (the RWWSB will be set by hardware). To re-enable the RWW section, the user software must wait until the programming is completed (SPMEN will be cleared). Then, if the RWWSRE bit is written to one at the same time as SPMEN, the next SPM instruction within four clock cycles re-enables the RWW section. The RWW section cannot be re-enabled while the Flash is busy with a page erase or a page write (SPMEN is set). If the RWWSRE bit is written while the Flash is being loaded, the Flash load operation will abort and the data loaded will be lost.

## Bit 3 – BLBSET: Boot Lock Bit Set

If this bit is written to one at the same time as SPMEN, the next SPM instruction within four clock cycles sets Boot Lock bits, according to the data in R0. The data in R1 and the address in the Z-pointer are ignored. The BLBSET bit will automatically be cleared upon completion of the Lock bit set, or if no SPM instruction is executed within four clock cycles.

An LPM instruction within three cycles after BLBSET and SPMEN are set in the SPMCR Register, will read either the Lock bits or the Fuse bits (depending on Z0 in the Z-pointer) into the destination register. See "Reading the Fuse and Lock Bits from Software" on page 254 for details.

Store Program Memory Control Register – SPMCR I. Repeat B through H until the entire Flash is programmed or until all data has been programmed.

J. End Page Programming

- 1. 1. Set XA1, XA0 to "10". This enables command loading.

- 2. Set DATA to "0000 0000". This is the command for No Operation.

- 3. Give XTAL1 a positive pulse. This loads the command, and the internal write signals are reset.

Figure 128. Addressing the Flash which is Organized in Pages

Note: 1. PCPAGE and PCWORD are listed in Table 107 on page 262.

| Programming the       | 1. | Enter JTAG instruction PROG_COMMANDS.                                                                                                                                                                                                                      |

|-----------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fuses                 | 2. | Enable Fuse write using programming instruction 6a.                                                                                                                                                                                                        |

|                       | 3. | Load data High byte using programming instructions 6b. A bit value of "0" will program the corresponding fuse, a "1" will unprogram the fuse.                                                                                                              |

|                       | 4. | Write Fuse High byte using programming instruction 6c.                                                                                                                                                                                                     |

|                       | 5. | Poll for Fuse write complete using programming instruction 6d, or wait for t <sub>WLRH</sub> (refer to Table 113 on page 272).                                                                                                                             |

|                       | 6. | Load data Low byte using programming instructions 6e. A "0" will program the fuse, a "1" will unprogram the fuse.                                                                                                                                          |

|                       | 7. | Write Fuse Low byte using programming instruction 6f.                                                                                                                                                                                                      |

|                       | 8. | Poll for Fuse write complete using programming instruction 6g, or wait for $t_{WLRH}$ (refer to Table 113 on page 272).                                                                                                                                    |

| Programming the Lock  | 1. | Enter JTAG instruction PROG_COMMANDS.                                                                                                                                                                                                                      |

| Bits                  | 2. | Enable Lock bit write using programming instruction 7a.                                                                                                                                                                                                    |

|                       | 3. | Load data using programming instructions 7b. A bit value of "0" will program the corre-<br>sponding Lock bit, a "1" will leave the Lock bit unchanged.                                                                                                     |

|                       | 4. | Write Lock bits using programming instruction 7c.                                                                                                                                                                                                          |

|                       | 5. | Poll for Lock bit write complete using programming instruction 7d, or wait for $t_{WLRH}$ (refer to Table 113 on page 272).                                                                                                                                |

| Reading the Fuses     | 1. | Enter JTAG instruction PROG_COMMANDS.                                                                                                                                                                                                                      |

| and Lock Bits         | 2. | Enable Fuse/Lock bit read using programming instruction 8a.                                                                                                                                                                                                |

|                       | 3. | To read all Fuses and Lock bits, use programming instruction 8e.<br>To only read Fuse High byte, use programming instruction 8b.<br>To only read Fuse Low byte, use programming instruction 8c.<br>To only read Lock bits, use programming instruction 8d. |

| Reading the Signature | 1. | Enter JTAG instruction PROG COMMANDS.                                                                                                                                                                                                                      |

| Bytes                 |    | Enable Signature byte read using programming instruction 9a.                                                                                                                                                                                               |

|                       | 3. | Load address \$00 using programming instruction 9b.                                                                                                                                                                                                        |

|                       | -  | Read first signature byte using programming instruction 9c.                                                                                                                                                                                                |

|                       |    | Repeat steps 3 and 4 with address \$01 and address \$02 to read the second and third                                                                                                                                                                       |

|                       | 0. | signature bytes, respectively.                                                                                                                                                                                                                             |

| Reading the           | 1. | Enter JTAG instruction PROG_COMMANDS.                                                                                                                                                                                                                      |

| Calibration Byte      | 2. | Enable Calibration byte read using programming instruction 10a.                                                                                                                                                                                            |

|                       | 3. | Load address \$00 using programming instruction 10b.                                                                                                                                                                                                       |

|                       | 4. | Read the calibration byte using programming instruction 10c.                                                                                                                                                                                               |

Figure 204. Calibrated 1 MHz RC Oscillator Frequency vs.  $V_{CC}$

Figure 205. Calibrated 1 MHz RC Oscillator Frequency vs. Osccal Value

## 44M1