Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

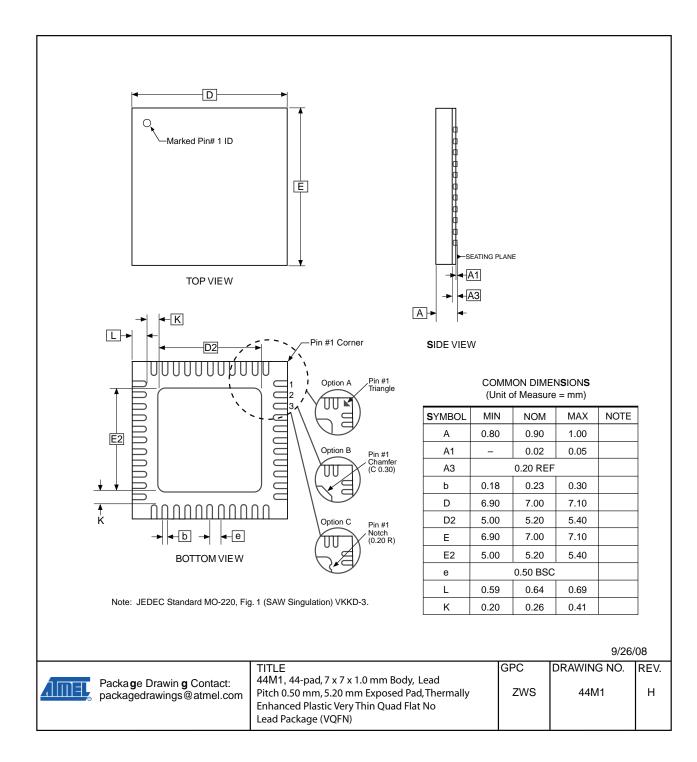

| Package / Case             | 44-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 44-VQFN (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega16l-8mj |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Alternate Functions of Port C

The Port C pins with alternate functions are shown in Table 28. If the JTAG interface is enabled, the pull-up resistors on pins PC5(TDI), PC3(TMS) and PC2(TCK) will be activated even if a reset occurs.

| Table 28. | Port C Pins Alternate Functions |

|-----------|---------------------------------|

|-----------|---------------------------------|

| Port Pin | Alternate Function                               |

|----------|--------------------------------------------------|

| PC7      | TOSC2 (Timer Oscillator Pin 2)                   |

| PC6      | TOSC1 (Timer Oscillator Pin 1)                   |

| PC5      | TDI (JTAG Test Data In)                          |

| PC4      | TDO (JTAG Test Data Out)                         |

| PC3      | TMS (JTAG Test Mode Select)                      |

| PC2      | TCK (JTAG Test Clock)                            |

| PC1      | SDA (Two-wire Serial Bus Data Input/Output Line) |

| PC0      | SCL (Two-wire Serial Bus Clock Line)             |

The alternate pin configuration is as follows:

• TOSC2 - Port C, Bit 7

TOSC2, Timer Oscillator pin 2: When the AS2 bit in ASSR is set (one) to enable asynchronous clocking of Timer/Counter2, pin PC7 is disconnected from the port, and becomes the inverting output of the Oscillator amplifier. In this mode, a Crystal Oscillator is connected to this pin, and the pin can not be used as an I/O pin.

• TOSC1 - Port C, Bit 6

TOSC1, Timer Oscillator pin 1: When the AS2 bit in ASSR is set (one) to enable asynchronous clocking of Timer/Counter2, pin PC6 is disconnected from the port, and becomes the input of the inverting Oscillator amplifier. In this mode, a Crystal Oscillator is connected to this pin, and the pin can not be used as an I/O pin.

• TDI - Port C, Bit 5

TDI, JTAG Test Data In: Serial input data to be shifted in to the Instruction Register or Data Register (scan chains). When the JTAG interface is enabled, this pin can not be used as an I/O pin.

• TDO – Port C, Bit 4

TDO, JTAG Test Data Out: Serial output data from Instruction Register or Data Register. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

The TD0 pin is tri-stated unless TAP states that shifts out data are entered.

• TMS – Port C, Bit 3

TMS, JTAG Test Mode Select: This pin is used for navigating through the TAP-controller state machine. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

• TCK – Port C, Bit 2

TCK, JTAG Test Clock: JTAG operation is synchronous to TCK. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

Unit" on page 73. for details. The compare match event will also set the Compare Flag (OCF0) which can be used to generate an output compare interrupt request.

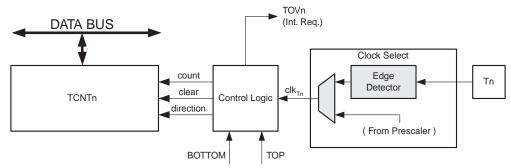

Definitions Many register and bit references in this document are written in general form. A lower case "n" replaces the Timer/Counter number, in this case 0. However, when using the register or bit defines in a program, the precise form must be used, that is, TCNT0 for accessing Timer/Counter0 counter value and so on.

The definitions in Table 37 are also used extensively throughout the document. Table 37. Definitions

| BOTTOM | The counter reaches the BOTTOM when it becomes 0x00.                                                                                                                                                                                                         |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX    | The counter reaches its MAXimum when it becomes 0xFF (decimal 255).                                                                                                                                                                                          |

| ТОР    | The counter reaches the TOP when it becomes equal to the highest value in the count sequence. The TOP value can be assigned to be the fixed value 0xFF (MAX) or the value stored in the OCR0 Register. The assignment is dependent on the mode of operation. |

Timer/CounterThe Timer/Counter can be clocked by an internal or an external clock source. The clock sourceClock Sourcesis selected by the clock select logic which is controlled by the clock select (CS02:0) bits located<br/>in the Timer/Counter Control Register (TCCR0). For details on clock sources and prescaler, see<br/>"Timer/Counter0 and Timer/Counter1 Prescalers" on page 87.

Counter Unit The main part of the 8-bit Timer/Counter is the programmable bi-directional counter unit. Figure 28 shows a block diagram of the counter and its surroundings.

Figure 28. Counter Unit Block Diagram

Signal description (internal signals):

| count | Increment or decrement TCNT0 by 1. |

|-------|------------------------------------|

|       |                                    |

direction Select between increment and decrement.

clear Clear TCNT0 (set all bits to zero).

$clk_{Tn}$  Timer/Counter clock, referred to as  $clk_{T0}$  in the following.

TOP Signalize that TCNT0 has reached maximum value.

BOTTOM Signalize that TCNT0 has reached minimum value (zero).

Depending of the mode of operation used, the counter is cleared, incremented, or decremented at each timer clock ( $clk_{T0}$ ).  $clk_{T0}$  can be generated from an external or internal clock source, selected by the Clock Select bits (CS02:0). When no clock source is selected (CS02:0 = 0) the timer is stopped. However, the TCNT0 value can be accessed by the CPU, regardless of

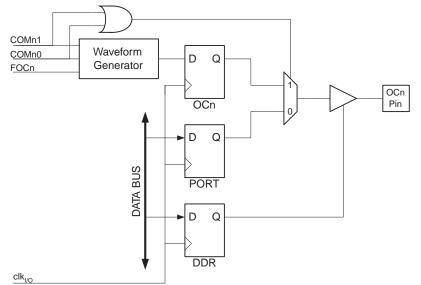

Figure 30. Compare Match Output Unit, Schematic

The general I/O port function is overridden by the Output Compare (OC0) from the Waveform Generator if either of the COM01:0 bits are set. However, the OC0 pin direction (input or output) is still controlled by the Data Direction Register (DDR) for the port pin. The Data Direction Register bit for the OC0 pin (DDR\_OC0) must be set as output before the OC0 value is visible on the pin. The port override function is independent of the Waveform Generation mode.

The design of the output compare pin logic allows initialization of the OC0 state before the output is enabled. Note that some COM01:0 bit settings are reserved for certain modes of operation. See "8-bit Timer/Counter Register Description" on page 83.

Compare Output Mode and Waveform Generation

The Waveform Generator uses the COM01:0 bits differently in normal, CTC, and PWM modes. For all modes, setting the COM01:0 = 0 tells the waveform generator that no action on the OC0 Register is to be performed on the next compare match. For compare output actions in the non-PWM modes refer to Table 39 on page 84. For fast PWM mode, refer to Table 40 on page 84, and for phase correct PWM refer to Table 41 on page 84.

A change of the COM01:0 bits state will have effect at the first compare match after the bits are written. For non-PWM modes, the action can be forced to have immediate effect by using the FOC0 strobe bits.

#### • Bit 0 - TOIE0: Timer/Counter0 Overflow Interrupt Enable

When the TOIE0 bit is written to one, and the I-bit in the Status Register is set (one), the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter0 occurs, that is, when the TOV0 bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

Timer/Counter Interrupt Flag Register – TIFR

| Bit           | 7    | 6    | 5    | 4     | 3     | 2    | 1    | 0    | _    |

|---------------|------|------|------|-------|-------|------|------|------|------|

|               | OCF2 | TOV2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0 | TOV0 | TIFR |

| Read/Write    | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W  | R/W  | -    |

| Initial Value | 0    | 0    | 0    | 0     | 0     | 0    | 0    | 0    |      |

• Bit 1 – OCF0: Output Compare Flag 0

The OCF0 bit is set (one) when a compare match occurs between the Timer/Counter0 and the data in OCR0 – Output Compare Register0. OCF0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF0 is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE0 (Timer/Counter0 Compare Match Interrupt Enable), and OCF0 are set (one), the Timer/Counter0 Compare Match Interrupt is executed.

Bit 0 – TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG I-bit, TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set (one), the Timer/Counter0 Overflow interrupt is executed. In phase correct PWM mode, this bit is set when Timer/Counter0 changes counting direction at \$00.

USART Control and Status Register A – UCSRA

| Bit           | 7   | -   | 5    | -  | -   | _  |     | 0    |       |

|---------------|-----|-----|------|----|-----|----|-----|------|-------|

|               | RXC | TXC | UDRE | FE | DOR | PE | U2X | MPCM | UCSRA |

| Read/Write    | R   | R/W | R    | R  | R   | R  | R/W | R/W  |       |

| Initial Value | 0   | 0   | 1    | 0  | 0   | 0  | 0   | 0    |       |

• Bit 7 - RXC: USAR T Receive Complete

This flag bit is set when there are unread data in the receive buffer and cleared when the receive buffer is empty (that is, does not contain any unread data). If the receiver is disabled, the receive buffer will be flushed and consequently the RXC bit will become zero. The RXC Flag can be used to generate a Receive Complete interrupt (see description of the RXCIE bit).

Bit 6 – TXC: USART Transmit Complete

This flag bit is set when the entire frame in the transmit Shift Register has been shifted out and there are no new data currently present in the transmit buffer (UDR). The TXC Flag bit is automatically cleared when a transmit complete interrupt is executed, or it can be cleared by writing a one to its bit location. The TXC Flag can generate a Transmit Complete interrupt (see description of the TXCIE bit).

Bit 5 – UDRE: USART Data Register Empty

The UDRE Flag indicates if the transmit buffer (UDR) is ready to receive new data. If UDRE is one, the buffer is empty, and therefore ready to be written. The UDRE Flag can generate a Data Register empty Interrupt (see description of the UDRIE bit).

UDRE is set after a reset to indicate that the transmitter is ready.

• Bit 4 – FE: Frame Error

This bit is set if the next character in the receive buffer had a Frame Error when received. that is, when the first stop bit of the next character in the receive buffer is zero. This bit is valid until the receive buffer (UDR) is read. The FE bit is zero when the stop bit of received data is one. Always set this bit to zero when writing to UCSRA.

• Bit 3 – DOR: Data OverRun

This bit is set if a Data OverRun condition is detected. A Data OverRun occurs when the receive buffer is full (two characters), it is a new character waiting in the receive Shift Register, and a new start bit is detected. This bit is valid until the receive buffer (UDR) is read. Always set this bit to zero when writing to UCSRA.

• Bit 2 – PE: Parity Error

This bit is set if the next character in the receive buffer had a Parity Error when received and the parity checking was enabled at that point (UPM1 = 1). This bit is valid until the receive buffer (UDR) is read. Always set this bit to zero when writing to UCSRA.

Bit 1 – U2X: Double the USART Transmission Speed

This bit only has effect for the asynchronous operation. Write this bit to zero when using synchronous operation.

Writing this bit to one will reduce the divisor of the baud rate divider from 16 to 8 effectively doubling the transfer rate for asynchronous communication.

| Status Code              |                                                                    | Application Software Response |     |     |       |      |                                                                                                                                                                                        |

|--------------------------|--------------------------------------------------------------------|-------------------------------|-----|-----|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (TWSR)<br>Prescaler Bits | Status of the Two-wire Serial Bus<br>and Two-wire Serial Interface |                               |     | То  | TWCR  |      |                                                                                                                                                                                        |

| are 0                    | Hardware                                                           | To/from TWDR                  | STA | STO | TWINT | TWEA | Next Action Taken by TWI Hardware                                                                                                                                                      |

| \$A8                     | \$A8 Own SLA+R has been received;<br>ACK has been returned         |                               | х   | 0   | 1     | 0    | Last data byte will be transmitted and NOT ACK should be received                                                                                                                      |

|                          |                                                                    | Load data byte                | х   | 0   | 1     | 1    | Data byte will be transmitted and ACK should be received                                                                                                                               |

| \$B0                     | Arbitration lost in SLA+R/W as Master; own SLA+R has been          | Load data byte or             | х   | 0   | 1     | 0    | Last data byte will be transmitted and NOT ACK should be received                                                                                                                      |

|                          | received; ACK has been returned                                    | Load data byte                | х   | 0   | 1     | 1    | Data byte will be transmitted and ACK should be received                                                                                                                               |

| \$B8                     | Data byte in TWDR has been transmitted; ACK has been               | Load data byte or             | х   | 0   | 1     | 0    | Last data byte will be transmitted and NOT ACK should be received                                                                                                                      |

|                          | received                                                           | Load data byte                | х   | 0   | 1     | 1    | Data byte will be transmitted and ACK should be received                                                                                                                               |

| \$C0                     | Data byte in TWDR has been transmitted; NOT ACK has been           | No TWDR action or             | 0   | 0   | 1     | 0    | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA                                                                                                          |

|                          | received                                                           | No TWDR action or             | 0   | 0   | 1     | 1    | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = 1                                                                        |

|                          |                                                                    | No TWDR action or             | 1   | 0   | 1     | 0    | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA;<br>a START condition will be transmitted when the bus<br>becomes free                                   |

|                          |                                                                    | No TWDR action                | 1   | 0   | 1     | 1    | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = 1;<br>a START condition will be transmitted when the bus<br>becomes free |

| \$C8                     | Last data byte in TWDR has been transmitted (TWEA = "0"); ACK      | No TWDR action or             | 0   | 0   | 1     | 0    | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA                                                                                                          |

|                          | has been received                                                  | No TWDR action or             | 0   | 0   | 1     | 1    | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = 1                                                                        |

|                          |                                                                    |                               | 1   | 0   | 1     | 0    | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA;<br>a START condition will be transmitted when the bus<br>becomes free                                   |

|                          |                                                                    | No TWDR action                | 1   | 0   | 1     | 1    | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = 1;<br>a START condition will be transmitted when the bus<br>becomes free |

# Table 77. Status Codes for Slave Transmitter Mode

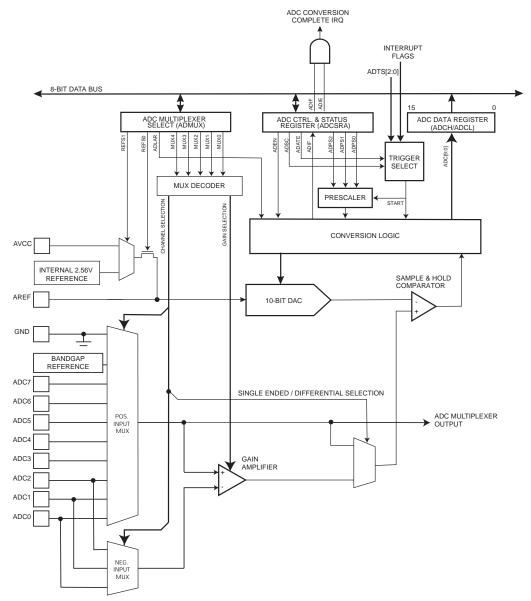

Figure 98. Analog to Digital Converter Block Schematic

## Operation

The ADC converts an analog input voltage to a 10-bit digital value through successive approximation. The minimum value represents GND and the maximum value represents the voltage on the AREF pin minus 1 LSB. Optionally, AVCC or an internal 2.56V reference voltage may be connected to the AREF pin by writing to the REFSn bits in the ADMUX Register. The internal voltage reference may thus be decoupled by an external capacitor at the AREF pin to improve noise immunity.

The analog input channel and differential gain are selected by writing to the MUX bits in ADMUX. Any of the ADC input pins, as well as GND and a fixed bandgap voltage reference, can be selected as single ended inputs to the ADC. A selection of ADC input pins can be selected as positive and negative inputs to the differential gain amplifier.

If differential channels are selected, the differential gain stage amplifies the voltage difference between the selected input channel pair by the selected gain factor. This amplified value then

A debugger, like the AVR Studio, may however use one or more of these resources for its internal purpose, leaving less flexibility to the end-user.

A list of the On-chip Debug specific JTAG instructions is given in "On-chip Debug Specific JTAG Instructions" on page 226.

The JTAGEN Fuse must be programmed to enable the JTAG Test Access Port. In addition, the OCDEN Fuse must be programmed and no Lock bits must be set for the On-chip Debug system to work. As a security feature, the On-chip Debug system is disabled when any Lock bits are set. Otherwise, the On-chip Debug system would have provided a back-door into a secured device.

The AVR JTAG ICE from Atmel is a powerful development tool for On-chip Debugging of all AVR 8-bit RISC Microcontrollers with IEEE 1149.1 compliant JTAG interface. The JTAG ICE and the AVR Studio user interface give the user complete control of the internal resources of the microcontroller, helping to reduce development time by making debugging easier. The JTAG ICE performs real-time emulation of the microcontroller while it is running in a target system.

Please refer to the Support Tools section on the AVR pages on www.atmel.com for a full description of the AVR JTEG ICE. AVR Studio can be downloaded free from Software section on the same web site.

All necessary execution commands are available in AVR Studio, both on source level and on disassembly level. The user can execute the program, single step through the code either by tracing into or stepping over functions, step out of functions, place the cursor on a statement and execute until the statement is reached, stop the execution, and reset the execution target. In addition, the user can have an unlimited number of code breakpoints (using the BREAK instruction) and up to two data memory breakpoints, alternatively combined as a mask (range) Break Point.

| On-chip Debug<br>Specific JTAG<br>Instructions | The On-chip Debug support is considered being private JTAG instructions, and distributed within ATMEL and to selected third party vendors only. Instruction opcodes are listed for reference. |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRIVATE0; \$8                                  | Private JTAG instruction for accessing On-chip Debug system.                                                                                                                                  |

| PRIVATE1; \$9                                  | Private JTAG instruction for accessing On-chip Debug system.                                                                                                                                  |

| PRIVATE2; \$A                                  | Private JTAG instruction for accessing On-chip Debug system.                                                                                                                                  |

| PRIVATE3; \$B                                  | Private JTAG instruction for accessing On-chip Debug system.                                                                                                                                  |

Figure 118. Additional Scan Signal for the Two-wire Interface

Scanning the RESET The RESET pin accepts 5V active low logic for standard reset operation, and 12V active high logic for High Voltage Parallel Programming. An observe-only cell as shown in Figure 119 is inserted both for the 5V reset signal; RSTT, and the 12V reset signal; RSTHV.

Figure 119. Observe-only Cell

Scanning the Clock Pins The AVR devices have many clock options selectable by fuses. These are: Internal RC Oscillator, External RC, External Clock, (High Frequency) Crystal Oscillator, Low Frequency Crystal Oscillator, and Ceramic Resonator.

Figure 120 shows how each Oscillator with external connection is supported in the scan chain. The Enable signal is supported with a general boundary-scan cell, while the Oscillator/Clock out-

- 4. The Flash is programmed one page at a time. The page size is found in Table 107 on page 262. The memory page is loaded one byte at a time by supplying the 6 LSB of the address and data together with the Load Program Memory Page instruction. To ensure correct loading of the page, the data Low byte must be loaded before data High byte is applied for a given address. The Program Memory Page is stored by loading the Write Program Memory Page instruction with the 7 MSB of the address. If polling is not used, the user must wait at least t<sub>WD\_FLASH</sub> before issuing the next page. (See Table 115). Accessing the SPI Serial Programming interface before the Flash write operation completes can result in incorrect programming.

- 5. The EEPROM array is programmed one byte at a time by supplying the address and data together with the appropriate Write instruction. An EEPROM memory location is first automatically erased before new data is written. If polling is not used, the user must wait at least t<sub>WD\_EEPROM</sub> before issuing the next byte. (See Table 115). In a chip erased device, no \$FFs in the data file(s) need to be programmed.

- 6. Any memory location can be verified by using the Read instruction which returns the content at the selected address at serial output MISO.

- 7. At the end of the programming session, RESET can be set high to commence normal operation.

- Power-off sequence (if needed): Set RESET to "1". Turn V<sub>CC</sub> power off.

- Data Polling Flash When a page is being programmed into the Flash, reading an address location within the page being programmed will give the value \$FF. At the time the device is ready for a new page, the programmed value will read correctly. This is used to determine when the next page can be written. Note that the entire page is written simultaneously and any address within the page can be used for polling. Data polling of the Flash will not work for the value \$FF, so when programming this value, the user will have to wait for at least t<sub>WD\_FLASH</sub> before programming the next page. As a chip erased device contains \$FF in all locations, programming of addresses that are meant to contain \$FF, can be skipped. See Table 115 for t<sub>WD\_FLASH</sub> value

- Data Polling EEPROM When a new byte has been written and is being programmed into EEPROM, reading the address location being programmed will give the value \$FF. At the time the device is ready for a new byte, the programmed value will read correctly. This is used to determine when the next byte can be written. This will not work for the value \$FF, but the user should have the following in mind: As a chip erased device contains \$FF in all locations, programming of addresses that are meant to contain \$FF, can be skipped. This does not apply if the EEPROM is re-programmed without chip erasing the device. In this case, data polling cannot be used for the value \$FF, and the user will have to wait at least t<sub>WD\_EEPROM</sub> before programming the next byte. See Table 115 for t<sub>WD EEPROM</sub> value.

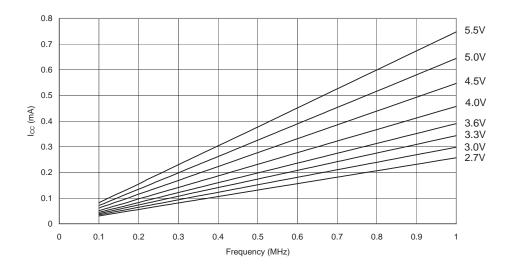

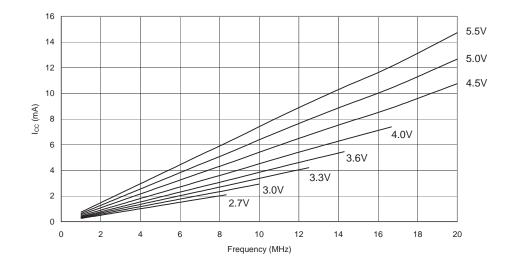

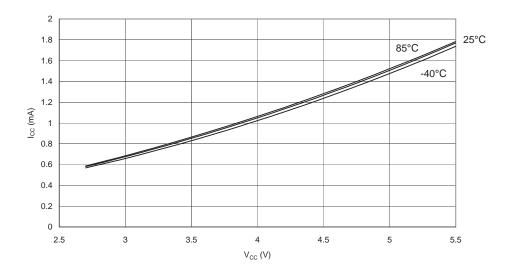

### Idle Supply Current

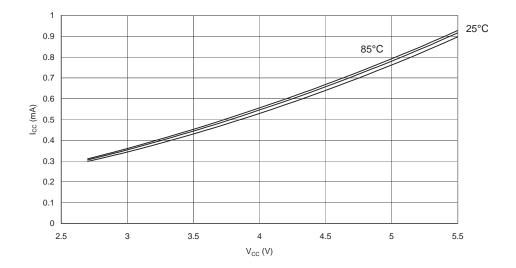

Figure 156. Idle Supply Current vs. Frequency (0.1 MHz - 1.0 MHz)

Figure 157. Idle Supply Current vs. Frequency (1 MHz - 20 MHz)

Figure 160. Idle Supply Current vs. V<sub>CC</sub> (Internal RC Oscillator, 2 MHz)

Figure 161. Idle Supply Current vs. V<sub>CC</sub> (Internal RC Oscillator, 1 MHz)

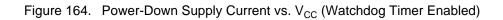

Figure 165. Power-Save Supply Current vs.  $V_{\text{CC}}$  (Watchdog Timer Disabled)

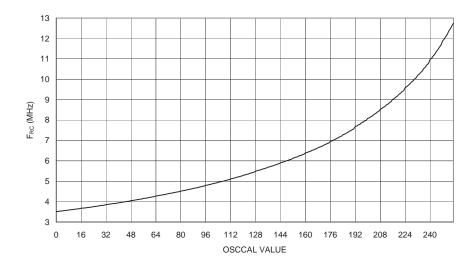

Figure 197. Calibrated 4 MHz RC Oscillator Frequency vs. Temperature

## 44M1