#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega16l-8pu |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Assembly Code Example

```

Move_interrupts:

; Enable change of interrupt vectors

ldi r16, (1<<IVCE)

out GICR, r16

; Move interrupts to boot Flash section

ldi r16, (1<<IVSEL)</pre>

out GICR, r16

ret

C Code Example

```

```

void Move_interrupts(void)

{

/* Enable change of interrupt vectors */

GICR = (1<<IVCE);

/* Move interrupts to boot Flash section */

GICR = (1<<IVSEL);

}

```

|                                             | The OCR0 Register access may seem complex, but this is not case. When the double buffering is enabled, the CPU has access to the OCR0 Buffer Register, and if double buffering is disabled the CPU will access the OCR0 directly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Force Output<br>Compare                     | In non-PWM waveform generation modes, the match output of the comparator can be forced by writing a one to the Force Output Compare (FOC0) bit. Forcing compare match will not set the OCF0 Flag or reload/clear the timer, but the OC0 pin will be updated as if a real compare match had occurred (the COM01:0 bits settings define whether the OC0 pin is set, cleared or toggled).                                                                                                                                                                                                                                                                                                             |

| Compare Match<br>Blocking by TCNT0<br>Write | All CPU write operations to the TCNT0 Register will block any compare match that occur in the next timer clock cycle, even when the timer is stopped. This feature allows OCR0 to be initialized to the same value as TCNT0 without triggering an interrupt when the Timer/Counter clock is enabled.                                                                                                                                                                                                                                                                                                                                                                                               |

| Using the Output<br>Compare Unit            | Since writing TCNT0 in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNT0 when using the output compare unit, independently of whether the Timer/Counter is running or not. If the value written to TCNT0 equals the OCR0 value, the compare match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT0 value equal to BOTTOM when the counter is downcounting.                                                                                                                                                                                                                 |

|                                             | The setup of the OC0 should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC0 value is to use the Force Output Compare (FOC0) strobe bits in Normal mode. The OC0 Register keeps its value even when changing between waveform generation modes.                                                                                                                                                                                                                                                                                                                                                                              |

|                                             | Be aware that the COM01:0 bits are not double buffered together with the compare value. Changing the COM01:0 bits will take effect immediately.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Compare Match<br>Output Unit                | The Compare Output mode (COM01:0) bits have two functions. The Waveform Generator uses the COM01:0 bits for defining the Output Compare (OC0) state at the next compare match. Also, the COM01:0 bits control the OC0 pin output source. Figure 30 shows a simplified schematic of the logic affected by the COM01:0 bit setting. The I/O Registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O port Control Registers (DDR and PORT) that are affected by the COM01:0 bits are shown. When referring to the OC0 state, the reference is for the internal OC0 Register, not the OC0 pin. If a System Reset occur, the OC0 Register is reset to "0". |

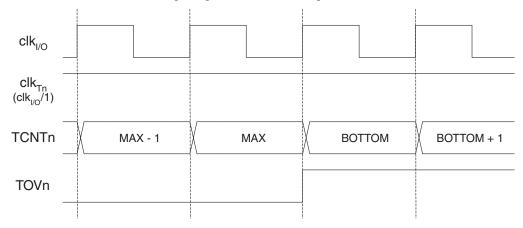

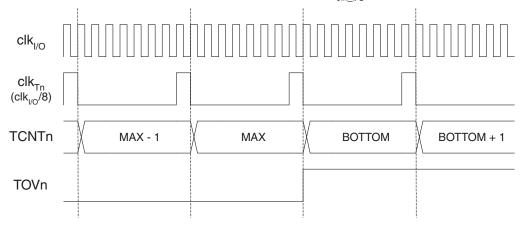

# Timer/Counter Timing Diagrams

The Timer/Counter is a synchronous design and the timer clock ( $clk_{T0}$ ) is therefore shown as a clock enable signal in the following figures. The figures include information on when Interrupt Flags are set. Figure 34 contains timing data for basic Timer/Counter operation. The figure shows the count sequence close to the MAX value in all modes other than phase correct PWM mode.

Figure 34. Timer/Counter Timing Diagram, no Prescaling

Figure 35 shows the same timing data, but with the prescaler enabled.

Figure 35. Timer/Counter Timing Diagram, with Prescaler (f<sub>clk I/O</sub>/8)

Figure 36 shows the setting of OCF0 in all modes except CTC mode.

| Timer/Counter0<br>and<br>Timer/Counter1<br>Prescalers | Timer/Counter1 and Timer/Counter0 share the same prescaler module, but the Timer/Counters can have different prescaler settings. The description below applies to both Timer/Counter1 and Timer/Counter0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Clock Source                                 | The Timer/Counter can be clocked directly by the system clock (by setting the CSn2:0 = 1). This provides the fastest operation, with a maximum Timer/Counter clock frequency equal to system clock frequency ( $f_{CLK\_I/O}$ ). Alternatively, one of four taps from the prescaler can be used as a clock source. The prescaled clock has a frequency of either $f_{CLK\_I/O}/8$ , $f_{CLK\_I/O}/64$ , $f_{CLK\_I/O}/256$ , or $f_{CLK\_I/O}/1024$ .                                                                                                                                                                                                                     |

| Prescaler Reset                                       | The prescaler is free running, that is, operates independently of the clock select logic of the Timer/Counter, and it is shared by Timer/Counter1 and Timer/Counter0. Since the prescaler is not affected by the Timer/Counter's clock select, the state of the prescaler will have implications for situations where a prescaled clock is used. One example of prescaling artifacts occurs when the timer is enabled and clocked by the prescaler ( $6 > CSn2:0 > 1$ ). The number of system clock cycles from when the timer is enabled to the first count occurs can be from 1 to N+1 system clock cycles, where N equals the prescaler divisor (8, 64, 256, or 1024). |

|                                                       | It is possible to use the Prescaler Reset for synchronizing the Timer/Counter to program execu-<br>tion. However, care must be taken if the other Timer/Counter that shares the same prescaler<br>also uses prescaling. A prescaler reset will affect the prescaler period for all Timer/Counters it is<br>connected to.                                                                                                                                                                                                                                                                                                                                                  |

| External Clock Source                                 | An external clock source applied to the T1/T0 pin can be used as Timer/Counter clock $(c k_{-})$ . The T1/T0 pin is sampled once every system clock cycle by the pin synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

**An external clock source** applied to the 11/10 pin can be used as Timer/Counter clock ( $clk_{T1}/clk_{T0}$ ). The T1/T0 pin is sampled once every system clock cycle by the pin synchronization logic. The synchronized (sampled) signal is then passed through the edge detector. Figure 38 shows a functional equivalent block diagram of the T1/T0 synchronization and edge detector logic. The registers are clocked at the positive edge of the internal system clock ( $clk_{I/O}$ ). The latch is transparent in the high period of the internal system clock.

The edge detector generates one  $clk_{T1}/clk_{T0}$  pulse for each positive (CSn2:0 = 7) or negative (CSn2:0 = 6) edge it detects.

|                      |                 |               | Tn_sync<br>(To Clock<br>Select Logic) |

|----------------------|-----------------|---------------|---------------------------------------|

| clk <sub>i/0</sub> — | Synchronization | Edge Detector |                                       |

Figure 38. T1/T0 Pin Sampling

The synchronization and edge detector logic introduces a delay of 2.5 to 3.5 system clock cycles from an edge has been applied to the T1/T0 pin to the counter is updated.

Enabling and disabling of the clock input must be done when T1/T0 has been stable for at least one system clock cycle, otherwise it is a risk that a false Timer/Counter clock pulse is generated.

Each half period of the external clock applied must be longer than one system clock cycle to ensure correct sampling. The external clock must be guaranteed to have less than half the system clock frequency ( $f_{ExtClk} < f_{clk}$  //2) given a 50/50% duty cycle. Since the edge detector uses

# 8-bit Timer/Counter Register Description

Timer/Counter Control Register – TCCR2

| Bit           | 7    | 6     | 5     | 4     | 3     | 2    | 1    | 0    | _     |

|---------------|------|-------|-------|-------|-------|------|------|------|-------|

|               | FOC2 | WGM20 | COM21 | COM20 | WGM21 | CS22 | CS21 | CS20 | TCCR2 |

| Read/Write    | W    | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | -     |

| Initial Value | 0    | 0     | 0     | 0     | 0     | 0    | 0    | 0    |       |

# • Bit 7 – FOC2: Force Output Compare

The FOC2 bit is only active when the WGM bits specify a non-PWM mode. However, for ensuring compatibility with future devices, this bit must be set to zero when TCCR2 is written when operating in PWM mode. When writing a logical one to the FOC2 bit, an immediate compare match is forced on the waveform generation unit. The OC2 output is changed according to its COM21:0 bits setting. Note that the FOC2 bit is implemented as a strobe. Therefore it is the value present in the COM21:0 bits that determines the effect of the forced compare.

A FOC2 strobe will not generate any interrupt, nor will it clear the timer in CTC mode using OCR2 as TOP.

The FOC2 bit is always read as zero.

# • Bit 3, 6 – WGM21:0: Waveform Generation Mode

These bits control the counting sequence of the counter, the source for the maximum (TOP) counter value, and what type of waveform generation to be used. Modes of operation supported by the Timer/Counter unit are: Normal mode, Clear Timer on Compare match (CTC) mode, and two types of Pulse Width Modulation (PWM) modes. See Table 50 and "Modes of Operation" on page 122.

| Mode | WGM21<br>(CTC2) | WGM20<br>(PWM2) | Timer/Counter Mode of<br>Operation | ТОР  | Update of<br>OCR2 | TOV2 Flag<br>Set on |

|------|-----------------|-----------------|------------------------------------|------|-------------------|---------------------|

| 0    | 0               | 0               | Normal                             | 0xFF | Immediate         | MAX                 |

| 1    | 0               | 1               | PWM, Phase Correct                 | 0xFF | TOP               | BOTTOM              |

| 2    | 1               | 0               | CTC                                | OCR2 | Immediate         | MAX                 |

| 3    | 1               | 1               | Fast PWM                           | 0xFF | BOTTOM            | MAX                 |

| <b>Table 50.</b> Waveform Generation Mode Bit Description |

|-----------------------------------------------------------|

|-----------------------------------------------------------|

Note: 1. The CTC2 and PWM2 bit definition names are now obsolete. Use the WGM21:0 definitions. However, the functionality and location of these bits are compatible with previous versions of the timer.

# • Bit 5:4 – COM21:0: Compare Match Output Mode

These bits control the Output Compare pin (OC2) behavior. If one or both of the COM21:0 bits are set, the OC2 output overrides the normal port functionality of the I/O pin it is connected to. However, note that the Data Direction Register (DDR) bit corresponding to OC2 pin must be set in order to enable the output driver.

# • Bit 4 – MSTR: Master/Slave Select

This bit selects Master SPI mode when written to one, and Slave SPI mode when written logic zero. If  $\overline{SS}$  is configured as an input and is driven low while MSTR is set, MSTR will be cleared, and SPIF in SPSR will become set. The user will then have to set MSTR to re-enable SPI Master mode.

# • Bit 3 – CPOL: Clock Polarity

When this bit is written to one, SCK is high when idle. When CPOL is written to zero, SCK is low when idle. Refer to Figure 67 and Figure 68 for an example. The CPOL functionality is summarized below:

## Table 56. CPOL Functionality

| CPOL | Leading Edge | Trailing Edge |

|------|--------------|---------------|

| 0    | Rising       | Falling       |

| 1    | Falling      | Rising        |

# • Bit 2 – CPHA: Clock Phase

The settings of the Clock Phase bit (CPHA) determine if data is sampled on the leading (first) or trailing (last) edge of SCK. Refer to Figure 67 and Figure 68 for an example. The CPHA functionality is summarized below:

## Table 57. CPHA Functionality

| СРНА | Leading Edge | Trailing Edge |

|------|--------------|---------------|

| 0    | Sample       | Setup         |

| 1    | Setup        | Sample        |

# • Bits 1, 0 – SPR1, SPR0: SPI Clock Rate Select 1 and 0

These two bits control the SCK rate of the device configured as a Master. SPR1 and SPR0 have no effect on the Slave. The relationship between SCK and the Oscillator Clock frequency  $f_{osc}$  is shown in the following table:

| SPI2X | SPR1 | SPR0 | SCK Frequency         |

|-------|------|------|-----------------------|

| 0     | 0    | 0    | f <sub>osc</sub> /4   |

| 0     | 0    | 1    | f <sub>osc</sub> /16  |

| 0     | 1    | 0    | f <sub>osc</sub> /64  |

| 0     | 1    | 1    | f <sub>osc</sub> /128 |

| 1     | 0    | 0    | f <sub>osc</sub> /2   |

| 1     | 0    | 1    | f <sub>osc</sub> /8   |

| 1     | 1    | 0    | f <sub>osc</sub> /32  |

| 1     | 1    | 1    | f <sub>osc</sub> /64  |

Table 58. Relationship Between SCK and the Oscillator Frequency

# Sending Frames with 9 Data Bit

If 9-bit characters are used (UCSZ = 7), the ninth bit must be written to the TXB8 bit in UCSRB before the Low byte of the character is written to UDR. The following code examples show a transmit function that handles 9-bit characters. For the assembly code, the data to be sent is assumed to be stored in Registers R17:R16.

```

Assembly Code Example<sup>(1)</sup>

USART Transmit:

; Wait for empty transmit buffer

sbis UCSRA, UDRE

rjmp USART Transmit

; Copy 9th bit from r17 to TXB8

cbi

UCSRB, TXB8

sbrc r17,0

UCSRB, TXB8

sbi

; Put LSB data (r16) into buffer, sends the data

UDR,r16

out

ret

C Code Example<sup>(1)</sup>

void USART Transmit( unsigned int data )

{

/* Wait for empty transmit buffer */

while ( !( UCSRA & (1<<UDRE))) )</pre>

;

/* Copy 9th bit to TXB8 */

UCSRB &= ~(1<<TXB8);

if ( data & 0x0100 )

UCSRB | = (1 < TXB8);

/* Put data into buffer, sends the data */

UDR = data;

```

}

These transmit functions are written to be general functions. They can be optimized if the contents of the UCSRB is static. (that is, only the TXB8 bit of the UCSRB Register is used after initialization).

The ninth bit can be used for indicating an address frame when using multi processor communication mode or for other protocol handling as for example synchronization.

Transmitter Flags and<br/>InterruptsThe USART transmitter has two flags that indicate its state: USART Data Register Empty<br/>(UDRE) and Transmit Complete (TXC). Both flags can be used for generating interrupts.

The Data Register Empty (UDRE) Flag indicates whether the transmit buffer is ready to receive new data. This bit is set when the transmit buffer is empty, and cleared when the transmit buffer contains data to be transmitted that has not yet been moved into the Shift Register. For compatibility with future devices, always write this bit to zero when writing the UCSRA Register.

When the Data Register empty Interrupt Enable (UDRIE) bit in UCSRB is written to one, the USART Data Register Empty Interrupt will be executed as long as UDRE is set (provided that global interrupts are enabled). UDRE is cleared by writing UDR. When interrupt-driven data transmission is used, the Data Register Empty Interrupt routine must either write new data to UDR in order to clear UDRE or disable the Data Register empty Interrupt, otherwise a new interrupt will occur once the interrupt routine terminates.

# Asynchronous Operational Range

The operational range of the receiver is dependent on the mismatch between the received bit rate and the internally generated baud rate. If the Transmitter is sending frames at too fast or too slow bit rates, or the internally generated baud rate of the receiver does not have a similar (see Table 61) base frequency, the receiver will not be able to synchronize the frames to the start bit.

The following equations can be used to calculate the ratio of the incoming data rate and internal receiver baud rate.

$$R_{slow} = \frac{(D+1)S}{S-1+D\cdot S+S_F}$$

$$R_{fast} = \frac{(D+2)S}{(D+1)S+S_M}$$

- D Sum of character size and parity size (D = 5 to 10 bit)

- S Samples per bit. S = 16 for Normal Speed mode and S = 8 for Double Speed mode.

- $S_F$  First sample number used for majority voting.  $S_F = 8$  for Normal Speed and  $S_F = 4$  for Double Speed mode.

- $S_M$  Middle sample number used for majority voting.  $S_M = 9$  for Normal Speed and  $S_M = 5$  for Double Speed mode.

- R<sub>slow</sub> is the ratio of the slowest incoming data rate that can be accepted in relation to the receiver baud rate. R<sub>fast</sub> is the ratio of the fastest incoming data rate that can be accepted in relation to the receiver baud rate.

Table 61 and Table 62 list the maximum receiver baud rate error that can be tolerated. Note that

Normal Speed mode has higher toleration of baud rate variations.

**Table 61.** Recommended Maximum Receiver Baud Rate Error for Normal Speed Mode (U2X = 0)

| D<br># (Data+Parity Bit) | R <sub>slow</sub> (%) | R <sub>fast</sub> (%) | Max Total<br>Error (%) | Recommended Max<br>Receiver Error (%) |

|--------------------------|-----------------------|-----------------------|------------------------|---------------------------------------|

| 5                        | 93.20                 | 106.67                | +6.67/-6.8             | ±3.0                                  |

| 6                        | 94.12                 | 105.79                | +5.79/-5.88            | ±2.5                                  |

| 7                        | 94.81                 | 105.11                | +5.11/-5.19            | ±2.0                                  |

| 8                        | 95.36                 | 104.58                | +4.58/-4.54            | ±2.0                                  |

| 9                        | 95.81                 | 104.14                | +4.14/-4.19            | ±1.5                                  |

| 10                       | 96.17                 | 103.78                | +3.78/-3.83            | ±1.5                                  |

Table 62.

Recommended Maximum Receiver Baud Rate Error for Double Speed Mode (U2X = 1)

| D<br># (Data+Parity Bit) | R <sub>slow</sub> (%) | R <sub>fast</sub> (%) | Max Total<br>Error (%) | Recommended Max<br>Receiver Error (%) |

|--------------------------|-----------------------|-----------------------|------------------------|---------------------------------------|

| 5                        | 94.12                 | 105.66                | +5.66/-5.88            | ±2.5                                  |

| 6                        | 94.92                 | 104.92                | +4.92/-5.08            | ±2.0                                  |

| 7                        | 95.52                 | 104.35                | +4.35/-4.48            | ±1.5                                  |

**Table 62.** Recommended Maximum Receiver Baud Rate Error for Double Speed Mode (U2X = 1)

| D<br># (Data+Parity Bit) | R <sub>slow</sub> (%) | R <sub>fast</sub> (%) | Max Total<br>Error (%) | Recommended Max<br>Receiver Error (%) |

|--------------------------|-----------------------|-----------------------|------------------------|---------------------------------------|

| 8                        | 96.00                 | 103.90                | +3.90/-4.00            | ±1.5                                  |

| 9                        | 96.39                 | 103.53                | +3.53/-3.61            | ±1.5                                  |

| 10                       | 96.70                 | 103.23                | +3.23/-3.30            | ±1.0                                  |

The recommendations of the maximum receiver baud rate error was made under the assumption that the receiver and transmitter equally divides the maximum total error.

There are two possible sources for the receivers baud rate error. The receiver's system clock (XTAL) will always have some minor instability over the supply voltage range and the temperature range. When using a crystal to generate the system clock, this is rarely a problem, but for a resonator the system clock may differ more than 2% depending of the resonators tolerance. The second source for the error is more controllable. The baud rate generator can not always do an exact division of the system frequency to get the baud rate wanted. In this case an UBRR value that gives an acceptable low error can be used if possible.

# Accessing UBRRH/ UCSRC Registers

The UBRRH Register shares the same I/O location as the UCSRC Register. Therefore some special consideration must be taken when accessing this I/O location.

Write Access

When doing a write access of this I/O location, the high bit of the value written, the USART Register Select (URSEL) bit, controls which one of the two registers that will be written. If URSEL is zero during a write operation, the UBRRH value will be updated. If URSEL is one, the UCSRC setting will be updated.

The following code examples show how to access the two registers.

| Assembly Code Example <sup>(1)</sup>                                  |

|-----------------------------------------------------------------------|

|                                                                       |

| ; Set UBRRH to 2                                                      |

| <b>ldi</b> r16,0x02                                                   |

| out UBRRH,r16                                                         |

|                                                                       |

| ; Set the USBS and the UCSZ1 bit to one, and                          |

| ; the remaining bits to zero.                                         |

| ldi r16, (1< <ursel) (1<<ucsz1)<="" (1<<usbs)="" th=""  =""></ursel)> |

| out UCSRC,r16                                                         |

|                                                                       |

| Code Example <sup>(1)</sup>                                           |

|                                                                       |

| /* Set UBRRH to 2 */                                                  |

| UBRRH = $0x02;$                                                       |

|                                                                       |

| /* Set the USBS and the UCSZ1 bit to one, and */                      |

| /* the remaining bits to zero. */                                     |

| UCSRC = (1< <ursel) (1<<ucsz1);<="" (1<<usbs)="" th=""  =""></ursel)> |

|                                                                       |

Note: 1. See "About Code Examples" on page 7.

As the code examples illustrate, write accesses of the two registers are relatively unaffected of the sharing of I/O location.

**Read Access** Doing a read access to the UBRRH or the UCSRC Register is a more complex operation. However, in most applications, it is rarely necessary to read any of these registers.

> The read access is controlled by a timed sequence. Reading the I/O location once returns the UBRRH Register contents. If the register location was read in previous system clock cycle, reading the register in the current clock cycle will return the UCSRC contents. Note that the timed sequence for reading the UCSRC is an atomic operation. Interrupts must therefore be controlled (for example by disabling interrupts globally) during the read operation.

A START condition is sent by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 1     | Х    | 1     | 0     | Х    | 1    | 0 | Х    |

TWEN must be set to enable the Two-wire Serial Interface, TWSTA must be written to one to transmit a START condition and TWINT must be written to one to clear the TWINT Flag. The TWI will then test the Two-wire Serial Bus and generate a START condition as soon as the bus becomes free. After a START condition has been transmitted, the TWINT Flag is set by hardware, and the status code in TWSR will be \$08 (See Table 74). In order to enter MT mode, SLA+W must be transmitted. This is done by writing SLA+W to TWDR. Thereafter the TWINT bit should be cleared (by writing it to one) to continue the transfer. This is accomplished by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 1     | Х    | 0     | 0     | Х    | 1    | 0 | Х    |

When SLA+W have been transmitted and an acknowledgement bit has been received, TWINT is set again and a number of status codes in TWSR are possible. Possible status codes in Master mode are \$18, \$20, or \$38. The appropriate action to be taken for each of these status codes is detailed in Table 74.

When SLA+W has been successfully transmitted, a data packet should be transmitted. This is done by writing the data byte to TWDR. TWDR must only be written when TWINT is high. If not, the access will be discarded, and the Write Collision bit (TWWC) will be set in the TWCR Register. After updating TWDR, the TWINT bit should be cleared (by writing it to one) to continue the transfer. This is accomplished by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 1     | Х    | 0     | 0     | Х    | 1    | 0 | Х    |

This scheme is repeated until the last byte has been sent and the transfer is ended by generating a STOP condition or a repeated START condition. A STOP condition is generated by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 1     | Х    | 0     | 1     | Х    | 1    | 0 | Х    |

A REPEATED START condition is generated by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 1     | Х    | 1     | 0     | Х    | 1    | 0 | Х    |

After a repeated START condition (state \$10) the Two-wire Serial Interface can access the same Slave again, or a new Slave without transmitting a STOP condition. Repeated START enables the Master to switch between Slaves, Master Transmitter mode and Master Receiver mode without losing control of the bus.

Table 74.

Status Codes for Master Transmitter Mode

| Status Code              |                                                                 | Applica       | ation Softw | are Resp | onse  |      |                                                                         |

|--------------------------|-----------------------------------------------------------------|---------------|-------------|----------|-------|------|-------------------------------------------------------------------------|

| (TWSR)<br>Prescaler Bits | Status of the Two-wire Serial<br>Bus and Two-wire Serial Inter- | To/from TWDR  |             | To       | TWCR  |      |                                                                         |

| are 0                    |                                                                 |               | STA         | STO      | TWINT | TWEA | Next Action Taken by TWI Hardware                                       |

| \$08                     | A START condition has been transmitted                          | Load SLA+W    | 0           | 0        | 1     | Х    | SLA+W will be transmitted;<br>ACK or NOT ACK will be received           |

| \$10                     | A repeated START condition has been transmitted                 | Load SLA+W or | 0           | 0        | 1     | Х    | SLA+W will be transmitted;<br>ACK or NOT ACK will be received           |

|                          |                                                                 | Load SLA+R    | 0           | 0        | 1     | Х    | SLA+R will be transmitted;<br>Logic will switch to Master Receiver mode |

Note that the Two-wire Serial Interface Data Register – TWDR does not reflect the last byte present on the bus when waking up from these sleep modes.

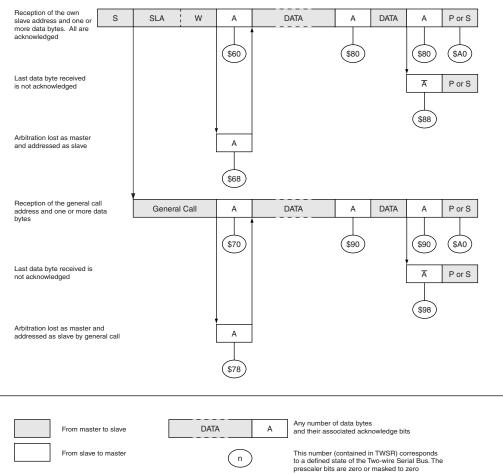

# Figure 91. Formats and States in the Slave Receiver Mode

# **Slave Transmitter** Mode

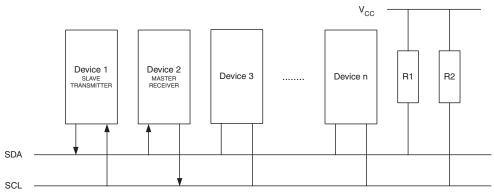

In the Slave Transmitter mode, a number of data bytes are transmitted to a Master Receiver (see Figure 92). All the status codes mentioned in this section assume that the prescaler bits are zero or are masked to zero.

To initiate the Slave Transmitter mode, TWAR and TWCR must be initialized as follows:

| TWAR  | TWA6                       | TWA5 | TWA4 | TWA3 | TWA2 | TWA1 | TWA0 | TWGCE |

|-------|----------------------------|------|------|------|------|------|------|-------|

| Value | Device's Own Slave Address |      |      |      |      |      |      |       |

## Table 79. ACIS1/ACIS0 Settings

| ACIS1 | ACIS0 | Interrupt Mode                              |

|-------|-------|---------------------------------------------|

| 0     | 0     | Comparator Interrupt on Output Toggle       |

| 0     | 1     | Reserved                                    |

| 1     | 0     | Comparator Interrupt on Falling Output Edge |

| 1     | 1     | Comparator Interrupt on Rising Output Edge  |

When changing the ACIS1/ACIS0 bits, the Analog Comparator Interrupt must be disabled by clearing its Interrupt Enable bit in the ACSR Register. Otherwise an interrupt can occur when the bits are changed.

# Analog Comparator Multiplexed Input

It is possible to select any of the ADC7..0 pins to replace the negative input to the Analog Comparator. The ADC multiplexer is used to select this input, and consequently, the ADC must be switched off to utilize this feature. If the Analog Comparator Multiplexer Enable bit (ACME in SFIOR) is set and the ADC is switched off (ADEN in ADCSRA is zero), MUX2..0 in ADMUX select the input pin to replace the negative input to the Analog Comparator, as shown in Table 80. If ACME is cleared or ADEN is set, AIN1 is applied to the negative input to the Analog Comparator.

| Table 80. Analog Comparator Multiplexed Input | Table 80. | Analog | Comparator | Multiplexed | I Input |

|-----------------------------------------------|-----------|--------|------------|-------------|---------|

|-----------------------------------------------|-----------|--------|------------|-------------|---------|

| ACME | ADEN | MUX20 | Analog Comparator Negative Input |

|------|------|-------|----------------------------------|

| 0    | х    | ххх   | AIN1                             |

| 1    | 1    | ххх   | AIN1                             |

| 1    | 0    | 000   | ADC0                             |

| 1    | 0    | 001   | ADC1                             |

| 1    | 0    | 010   | ADC2                             |

| 1    | 0    | 011   | ADC3                             |

| 1    | 0    | 100   | ADC4                             |

| 1    | 0    | 101   | ADC5                             |

| 1    | 0    | 110   | ADC6                             |

| 1    | 0    | 111   | ADC7                             |

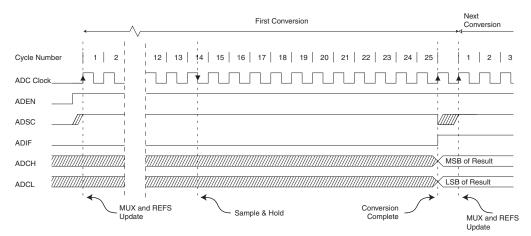

will require 25 ADC clocks. This is because the ADC must be disabled and re-enabled after every conversion.

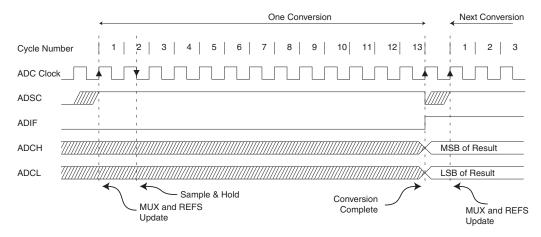

In Free Running mode, a new conversion will be started immediately after the conversion completes, while ADSC remains high. For a summary of conversion times, see Table 81.

Figure 101. ADC Timing Diagram, First Conversion (Single Conversion Mode)

Figure 102. ADC Timing Diagram, Single Conversion

# Special FunctionIO Register – SFIOR

| Bit           | 7     | 6     | 5     | 4 | 3    | 2   | 1    | 0     |       |

|---------------|-------|-------|-------|---|------|-----|------|-------|-------|

|               | ADTS2 | ADTS1 | ADTS0 | - | ACME | PUD | PSR2 | PSR10 | SFIOR |

| Read/Write    | R/W   | R/W   | R/W   | R | R/W  | R/W | R/W  | R/W   | l     |

| Initial Value | 0     | 0     | 0     | 0 | 0    | 0   | 0    | 0     |       |

# • Bit 7:5 – ADTS2:0: ADC Auto Trigger Source

If ADATE in ADCSRA is written to one, the value of these bits selects which source will trigger an ADC conversion. If ADATE is cleared, the ADTS2:0 settings will have no effect. A conversion will be triggered by the rising edge of the selected Interrupt Flag. Note that switching from a trigger source that is cleared to a trigger source that is set, will generate a positive edge on the trigger signal. If ADEN in ADCSRA is set, this will start a conversion. Switching to Free Running mode (ADTS[2:0]=0) will not cause a trigger event, even if the ADC Interrupt Flag is set.

| Table 86. | ADC Auto | Trigger | Source | Selections |

|-----------|----------|---------|--------|------------|

|-----------|----------|---------|--------|------------|

| ADTS2 | ADTS1 | ADTS0 | Trigger Source                 |  |

|-------|-------|-------|--------------------------------|--|

| 0     | 0     | 0     | Free Running mode              |  |

| 0     | 0     | 1     | Analog Comparator              |  |

| 0     | 1     | 0     | External Interrupt Request 0   |  |

| 0     | 1     | 1     | Timer/Counter0 Compare Match   |  |

| 1     | 0     | 0     | Timer/Counter0 Overflow        |  |

| 1     | 0     | 1     | Timer/Counter1 Compare Match B |  |

| 1     | 1     | 0     | Timer/Counter1 Overflow        |  |

| 1     | 1     | 1     | Timer/Counter1 Capture Event   |  |

# • Bit 4 - Res: Reserved Bit

This bit is reserved for future use. To ensure compatibility with future devices, this bit must be written to zero when SFIOR is written.

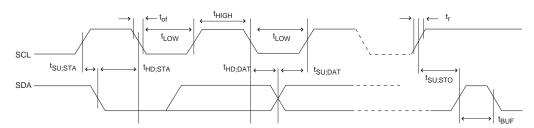

This requirement applies to all ATmega16 Two-wire Serial Interface operation. Other devices connected to the Two-wire Serial Bus need only obey the general f<sub>SCL</sub> requirement.

# Figure 146. Two-wire Serial Bus Timing

# SPI Timing Characteristics

## See Figure 147 and Figure 148 for details.

## Table 121. SPI Timing Parameters

|    | Description          | Mode   | Min                  | Тур                    | Max |    |

|----|----------------------|--------|----------------------|------------------------|-----|----|

| 1  | SCK period           | Master |                      | See Table 58           |     |    |

| 2  | SCK high/low         | Master |                      | 50% duty cycle         |     |    |

| 3  | Rise/Fall time       | Master |                      | 3.6                    |     |    |

| 4  | Setup                | Master |                      | 10                     |     |    |

| 5  | Hold                 | Master |                      | 10                     |     |    |

| 6  | Out to SCK           | Master |                      | 0.5 • t <sub>SCK</sub> |     | ns |

| 7  | SCK to out           | Master |                      | 10                     |     |    |

| 8  | SCK to out high      | Master |                      | 10                     |     |    |

| 9  | SS low to out        | Slave  |                      | 15                     |     |    |

| 10 | SCK period           | Slave  | 4 ∙ t <sub>SCK</sub> |                        |     |    |

| 11 | SCK high/low         | Slave  | 2 • t <sub>SCK</sub> |                        |     |    |

| 12 | Rise/Fall time       | Slave  |                      |                        | 1.6 | μs |

| 13 | Setup                | Slave  | 10                   |                        |     |    |

| 14 | Hold                 | Slave  | 10                   |                        |     |    |

| 15 | SCK to out           | Slave  |                      | 15                     |     |    |

| 16 | SCK to SS high       | Slave  | 20                   |                        |     | ns |

| 17 | SS high to tri-state | Slave  |                      | 10                     |     |    |

| 18 | SS low to SCK        | Slave  | 2 • t <sub>SCK</sub> |                        |     |    |

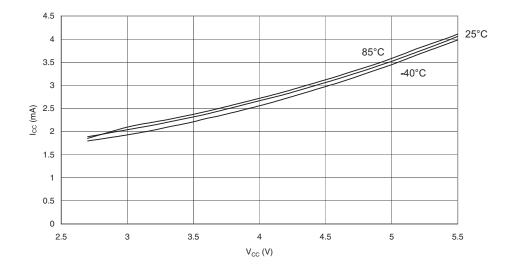

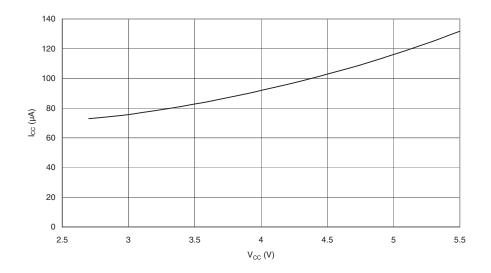

Figure 153. Active Supply Current vs. V<sub>CC</sub> (Internal RC Oscillator, 2 MHz)

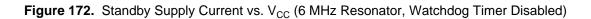

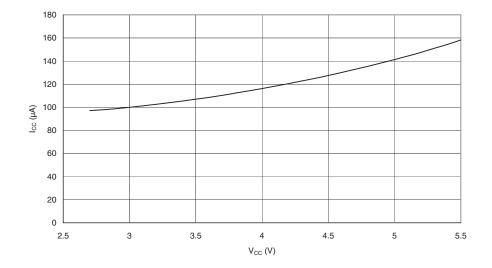

Figure 173. Standby Supply Current vs.  $V_{CC}$  (6 MHz Xtal, Watchdog Timer Disabled)

| Mnemonics                | Operands | Description                   | Operation                                | Flags | #Clocks |  |  |

|--------------------------|----------|-------------------------------|------------------------------------------|-------|---------|--|--|

| CLH                      |          | Clear Half Carry Flag in SREG | H ← 0                                    | Н     | 1       |  |  |

| MCU CONTROL INSTRUCTIONS |          |                               |                                          |       |         |  |  |

| NOP                      |          | No Operation                  |                                          | None  | 1       |  |  |

| SLEEP                    |          | Sleep                         | (see specific descr. for Sleep function) | None  | 1       |  |  |

| WDR                      |          | Watchdog Reset                | (see specific descr. for WDR/timer)      | None  | 1       |  |  |

| BREAK                    |          | Break                         | For On-Chip Debug Only                   | None  | N/A     |  |  |