Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 80 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c620-04i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

## 4.2 Data Memory Organization

The data memory (Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7) is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20-7Fh (Bank0) on the PIC16C620A/CR620A/621A and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16C622 and PIC16C622A are General Purpose Registers implemented as static RAM. Some Special Purpose Registers are mapped in Bank 1.

Addresses F0h-FFh of bank1 are implemented as common ram and mapped back to addresses 70h-7Fh in bank0 on the PIC16C620A/621A/622A/CR620A.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 80 x 8 in the PIC16C620/621, 96 x 8 in the PIC16C620A/621A/CR620A and 128 x 8 in the PIC16C622(A). Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM. The Special Function Registers can be classified into two sets (core and peripheral). The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name          | Bit 7               | Bit 6              | Bit 5       | Bit 4        | Bit 3        | Bit 2        | Bit 1       | Bit 0      | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|---------------|---------------------|--------------------|-------------|--------------|--------------|--------------|-------------|------------|-----------------------|------------------------------------------------|

| Bank 0  |               |                     |                    |             |              |              |              |             |            |                       |                                                |

| 00h     | INDF          | Addressin register) | g this locati      | ion uses co | ntents of FS | SR to addre  | ess data me  | mory (not a | n physical | XXXX XXXX             | XXXX XXXX                                      |

| 01h     | TMR0          | Timer0 Mo           | odule's Reg        | ister       |              |              |              |             |            | xxxx xxxx             | uuuu uuuu                                      |

| 02h     | PCL           | Program 0           | Counter's (F       | PC) Least S | ignificant B | yte          |              |             |            | 0000 0000             | 0000 0000                                      |

| 03h     | STATUS        | IRP <sup>(2)</sup>  | RP1 <sup>(2)</sup> | RP0         | TO           | PD           | Z            | DC          | С          | 0001 1xxx             | 000q quuu                                      |

| 04h     | FSR           | Indirect da         | ata memory         | address po  | ointer       |              |              |             |            | xxxx xxxx             | uuuu uuuu                                      |

| 05h     | PORTA         | —                   | _                  | —           | RA4          | RA3          | RA2          | RA1         | RA0        | x 0000                | u 0000                                         |

| 06h     | PORTB         | RB7                 | RB6                | RB5         | RB4          | RB3          | RB2          | RB1         | RB0        | xxxx xxxx             | uuuu uuuu                                      |

| 07h-09h | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 0Ah     | PCLATH        | _                   | _                  | _           | Write buffe  | er for upper | 5 bits of pr | ogram coui  | nter       | 0 0000                | 0 0000                                         |

| 0Bh     | INTCON        | GIE                 | PEIE               | T0IE        | INTE         | RBIE         | T0IF         | INTF        | RBIF       | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1          | _                   | CMIF               | —           | _            | —            | _            | —           | —          | -0                    | -0                                             |

| 0Dh-1Eh | Unimplemented |                     |                    |             |              |              | _            | _           |            |                       |                                                |

| 1Fh     | CMCON         | C2OUT               | C1OUT              | —           | _            | CIS          | CM2          | CM1         | CM0        | 00 0000               | 00 0000                                        |

| Bank 1  |               |                     |                    |             |              |              |              |             |            |                       |                                                |

| 80h     | INDF          | Addressin register) | g this locati      | on uses co  | ntents of FS | SR to addre  | ess data me  | mory (not a | ı physical | xxxx xxxx             | xxxx xxxx                                      |

| 81h     | OPTION        | RBPU                | INTEDG             | TOCS        | TOSE         | PSA          | PS2          | PS1         | PS0        | 1111 1111             | 1111 1111                                      |

| 82h     | PCL           | Program 0           | Counter's (F       | PC) Least S | ignificant B | yte          |              |             |            | 0000 0000             | 0000 0000                                      |

| 83h     | STATUS        | IRP <sup>(2)</sup>  | RP1 <sup>(2)</sup> | RP0         | TO           | PD           | Z            | DC          | С          | 0001 1xxx             | 000q quuu                                      |

| 84h     | FSR           | Indirect da         | ata memory         | address po  | ointer       |              |              |             |            | xxxx xxxx             | uuuu uuuu                                      |

| 85h     | TRISA         | —                   | _                  | _           | TRISA4       | TRISA3       | TRISA2       | TRISA1      | TRISA0     | 1 1111                | 1 1111                                         |

| 86h     | TRISB         | TRISB7              | TRISB6             | TRISB5      | TRISB4       | TRISB3       | TRISB2       | TRISB1      | TRISB0     | 1111 1111             | 1111 1111                                      |

| 87h-89h | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 8Ah     | PCLATH        | —                   | _                  | _           | Write buffe  | er for upper | 5 bits of pr | ogram coui  | nter       | 0 0000                | 0 0000                                         |

| 8Bh     | INTCON        | GIE                 | PEIE               | T0IE        | INTE         | RBIE         | T0IF         | INTF        | RBIF       | 0000 000x             | 0000 000u                                      |

| 8Ch     | PIE1          | —                   | CMIE               | —           | —            | —            | —            | —           | —          | -0                    | -0                                             |

| 8Dh     | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 8Eh     | PCON          | —                   |                    | _           |              | _            |              | POR         | BOR        | 0x                    | uq                                             |

| 8Fh-9Eh | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 9Fh     | VRCON         | VREN                | VROE               | VRR         | —            | VR3          | VR2          | VR1         | VR0        | 000- 0000             | 000- 0000                                      |

TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16C62X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown,

${\rm q}$  = value depends on condition, shaded = unimplemented

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

2: IRP & RP1 bits are reserved; always maintain these bits clear.

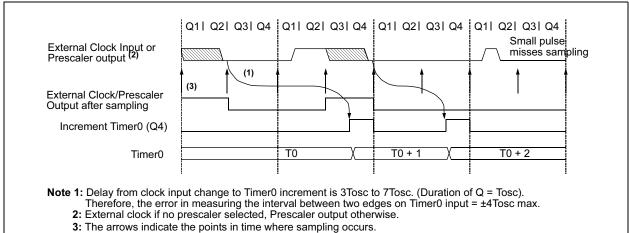

## 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to WDT.)

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

|          |              | ,                                             |

|----------|--------------|-----------------------------------------------|

| 1.BCF    | STATUS, RPO  | ;Skip if already in<br>;Bank 0                |

| 2.CLRWDT |              | ;Clear WDT                                    |

| 3.CLRF   | TMR0         | ;Clear TMR0 & Prescaler                       |

| 4.BSF    | STATUS, RPO  | ;Bank 1                                       |

| 5.MOVLW  | '00101111'b; | ;These 3 lines (5, 6, 7)                      |

| 6.MOVWF  | OPTION       | ;are required only if<br>;desired PS<2:0> are |

| 7.CLRWDT |              | ;000 or 001                                   |

| 8.MOVLW  | '00101xxx'b  | ;Set Postscaler to                            |

| 9.MOVWF  | OPTION       | ;desired WDT rate                             |

| 10.BCF   | STATUS, RPO  | ;Return to Bank 0                             |

|          |              |                                               |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 6-2. This precaution must be taken even if the WDT is disabled.

# EXAMPLE 6-2:

#### CHANGING PRESCALER (WDT→TIMER0)

|        | •           | ,                                        |

|--------|-------------|------------------------------------------|

| CLRWDT |             | ;Clear WDT and                           |

|        |             | ;prescaler                               |

| BSF    | STATUS, RPO |                                          |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new<br>;prescale value and |

|        |             | ;clock source                            |

| MOVWF  | OPTION REG  |                                          |

| BCF    | STATUS, RPO |                                          |

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6                | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|----------|----------------------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 r | mer0 module register |       |        |        |        |        |        |                 | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE      | PEIE                 | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | RBPU     | INTEDG               | TOCS  | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _        |                      | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

**Note:** Shaded bits are not used by TMR0 module.

NOTES:

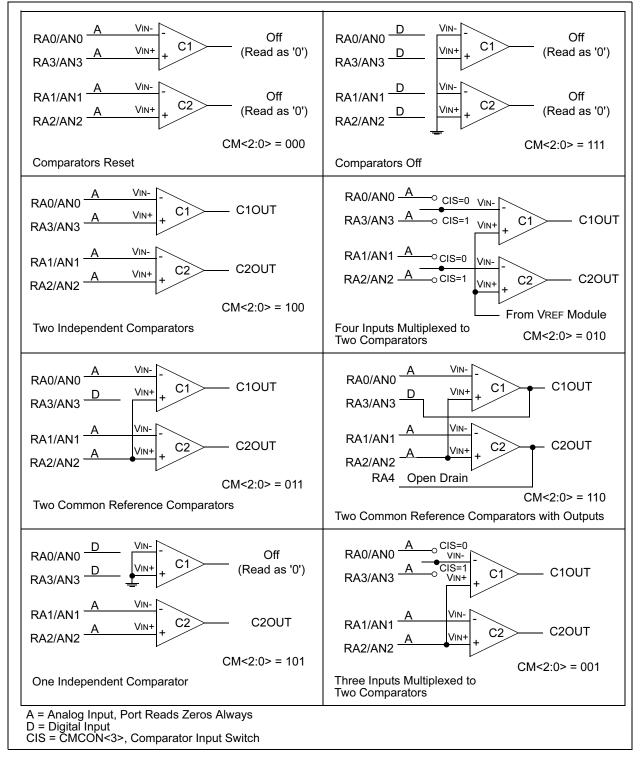

#### 7.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 7-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 12-2.

**Note:** Comparator interrupts should be disabled during a Comparator mode change otherwise a false interrupt may occur.

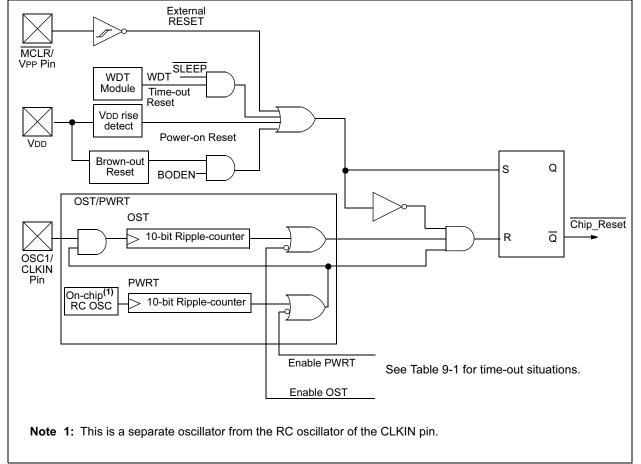

# 9.3 RESET

The PIC16C62X differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) WDT Reset (normal operation)

- e) WDT wake-up (SLEEP)

- f) Brown-out Reset (BOR)

Some registers are not affected in any RESET condition Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset,

MCLR Reset, WDT Reset and MCLR Reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 9-2. These bits are used in software to determine the nature of the RESET. See Table 9-5 for a full description of RESET states of all registers.

A simplified block diagram of the on-chip RESET circuit is shown in Figure 9-6.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 12-5 for pulse width specification.

#### 9.9 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip  | does   | not   | recommend | code |

|-------|------------|--------|-------|-----------|------|

|       | protecting | windov | ved d | evices.   |      |

#### 9.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify. Only the Least Significant 4 bits of the ID locations are used.

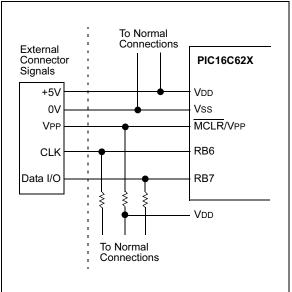

# 9.11 In-Circuit Serial Programming™

The PIC16C62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X/9XX Programming Specification (DS30228).

A typical In-Circuit Serial Programming connection is shown in Figure 9-19.

# FIGURE 9-19:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| BTFSS            | Bit Test f, Skip if Set                                                                                                                          | CALL             | Call Subroutine                                                                                                                                                            |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                              | Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                    |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                | Operands:        | $0 \leq k \leq 2047$                                                                                                                                                       |  |

|                  | $0 \le b < 7$                                                                                                                                    | Operation:       | $(PC)$ + 1 $\rightarrow$ TOS,                                                                                                                                              |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                          |                  | $k \rightarrow PC<10:0>$ ,<br>(PCLATH<4:3>) $\rightarrow PC<12:11>$                                                                                                        |  |

| Status Affected: | None                                                                                                                                             | Status Affected: | None                                                                                                                                                                       |  |

| Encoding:        | 01 11bb bfff ffff                                                                                                                                | Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                          |  |

| Description:     | If bit 'b' in register 'f' is '1', then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next instruc-                         | Description:     | Call Subroutine. First, return<br>address (PC+1) is pushed onto                                                                                                            |  |

|                  | tion fetched during the current<br>instruction execution, is discarded<br>and a NOP is executed instead,<br>making this a two-cycle instruction. |                  | the stack. The eleven bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. |  |

| Words:           | 1                                                                                                                                                | Words:           | 1                                                                                                                                                                          |  |

| Cycles:          | 1(2)                                                                                                                                             | Cycles:          | 2                                                                                                                                                                          |  |

| Example          | HERE BTFSS <b>FLAG,1</b><br>FALSE GOTO <b>PROCESS_CO</b>                                                                                         | Example          | HERE CALL                                                                                                                                                                  |  |

|                  | TRUE DE                                                                                                                                          | Example          | THER                                                                                                                                                                       |  |

|                  | Before Instruction<br>PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,<br>PC = address FALSE<br>if FLAG<1> = 1,                         |                  | Before Instruction<br>PC = Address HERE<br>After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                 |  |

|                  | PC = address TRUE                                                                                                                                | CLRF             | Clear f                                                                                                                                                                    |  |

|                  |                                                                                                                                                  | Syntax:          | [label] CLRF f                                                                                                                                                             |  |

|                  |                                                                                                                                                  | Operands:        | $0 \leq f \leq 127$                                                                                                                                                        |  |

|                  |                                                                                                                                                  | Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$                                                                                                      |  |

|                  |                                                                                                                                                  | Status Affected: | Z                                                                                                                                                                          |  |

|                  |                                                                                                                                                  | Encoding:        | 00 0001 1fff ffff                                                                                                                                                          |  |

|                  |                                                                                                                                                  | Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.                                                                                                          |  |

|                  |                                                                                                                                                  | Words:           | 1                                                                                                                                                                          |  |

|                  |                                                                                                                                                  | Cycles:          | 1                                                                                                                                                                          |  |

|                  |                                                                                                                                                  | Example          | CLRF FLAG_REG                                                                                                                                                              |  |

|                  |                                                                                                                                                  |                  | Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction                                                                                                                 |  |

|                  |                                                                                                                                                  |                  | $FLAG_REG = 0x00$<br>Z = 1                                                                                                                                                 |  |

## 11.14 PICDEM 1 PICmicro Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include analog input, push button switches and eight LEDs.

#### 11.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham

## 11.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessary hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 FLASH microcontrollers.

# 11.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

## 11.18 PICDEM 4 8/14/18-Pin Demonstration Board

The PICDEM 4 can be used to demonstrate the capabilities of the 8-, 14-, and 18-pin PIC16XXXX and PIC18XXXX MCUs, including the PIC16F818/819, PIC16F87/88, PIC16F62XA and the PIC18F1320 family of microcontrollers. PICDEM 4 is intended to showcase the many features of these low pin count parts, including LIN and Motor Control using ECCP. Special provisions are made for low power operation with the supercapacitor circuit, and jumpers allow onboard hardware to be disabled to eliminate current draw in this mode. Included on the demo board are provisions for Crystal, RC or Canned Oscillator modes, a five volt regulator for use with a nine volt wall adapter or battery, DB-9 RS-232 interface, ICD connector for programming via ICSP and development with MPLAB ICD 2, 2x16 liquid crystal display, PCB footprints for H-Bridge motor driver, LIN transceiver and EEPROM. Also included are: header for expansion, eight LEDs, four potentiometers, three push buttons and a prototyping area. Included with the kit is a PIC16F627A and a PIC18F1320. Tutorial firmware is included along with the User's Guide.

# 11.19 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board FLASH memory. A generous prototype area is available for user hardware expansion. NOTES:

#### 12.2 DC Characteristics: PIC16C62XA-04 (Commercial, Industrial, Extended) PIC16C62XA-20 (Commercial, Industrial, Extended) PIC16LC62XA-04 (Commercial, Industrial, Extended)

| PIC16C        | C62XA |                                               | Opera<br>Stand | $\begin{array}{rl} \textbf{Standard Operating Conditions (unless otherwise stated)}\\ Operating temperature & -40^{\circ}C & \leq TA \leq +85^{\circ}C \text{ for industrial and}\\ 0^{\circ}C & \leq TA \leq +70^{\circ}C \text{ for commercial and}\\ -40^{\circ}C & \leq TA \leq +125^{\circ}C \text{ for extended} \end{array}$ |      |       |                                              |  |  |  |

|---------------|-------|-----------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------------------|--|--|--|

| Param.<br>No. | Sym   | Characteristic                                | Min            | Тур†                                                                                                                                                                                                                                                                                                                                | Мах  | Units | Conditions                                   |  |  |  |

| D001          | Vdd   | Supply Voltage                                | 3.0            | _                                                                                                                                                                                                                                                                                                                                   | 5.5  | V     | See Figures 12-1, 12-2, 12-3, 12-4, and 12-5 |  |  |  |

| D001          | Vdd   | Supply Voltage                                | 2.5            | _                                                                                                                                                                                                                                                                                                                                   | 5.5  | V     | See Figures 12-1, 12-2, 12-3, 12-4, and 12-5 |  |  |  |

| D002          | Vdr   | RAM Data Retention<br>Voltage <sup>(1)</sup>  |                | 1.5*                                                                                                                                                                                                                                                                                                                                |      | V     | Device in SLEEP mode                         |  |  |  |

| D002          | Vdr   | RAM Data Retention Voltage <sup>(1)</sup>     |                | 1.5*                                                                                                                                                                                                                                                                                                                                | —    | V     | Device in SLEEP mode                         |  |  |  |

| D003          | VPOR  | VDD start voltage to<br>ensure Power-on Reset |                | Vss                                                                                                                                                                                                                                                                                                                                 | _    | V     | See section on Power-on Reset for details    |  |  |  |

| D003          | VPOR  | VDD start voltage to<br>ensure Power-on Reset |                | Vss                                                                                                                                                                                                                                                                                                                                 | —    | V     | See section on Power-on Reset for details    |  |  |  |

| D004          | SVDD  | VDD rise rate to ensure<br>Power-on Reset     | 0.05*          | —                                                                                                                                                                                                                                                                                                                                   | —    | V/ms  | See section on Power-on Reset for details    |  |  |  |

| D004          | SVDD  | VDD rise rate to ensure<br>Power-on Reset     | 0.05*          | —                                                                                                                                                                                                                                                                                                                                   | —    | V/ms  | See section on Power-on Reset for details    |  |  |  |

| D005          | VBOR  | Brown-out Detect Voltage                      | 3.7            | 4.0                                                                                                                                                                                                                                                                                                                                 | 4.35 | V     | BOREN configuration bit is cleared           |  |  |  |

| D005          | VBOR  | Brown-out Detect Voltage                      | 3.7            | 4.0                                                                                                                                                                                                                                                                                                                                 | 4.35 | V     | BOREN configuration bit is cleared           |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD, MCLR = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

**6:** Commercial temperature range only.

#### 12.2 DC Characteristics: PIC16C62XA-04 (Commercial, Industrial, Extended) PIC16C62XA-20 (Commercial, Industrial, Extended) PIC16LC62XA-04 (Commercial, Industrial, Extended) (CONT.)

| PIC16C        | C62XA | Oper<br>Stand<br>Oper             | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq TA \leq +85^{\circ}$ C for industrial and $0^{\circ}$ C $\leq TA \leq +70^{\circ}$ C for commercial and $-40^{\circ}$ C $\leq TA \leq +125^{\circ}$ C for extendedStandard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq TA \leq +85^{\circ}$ C for industrial and $0^{\circ}$ C $\leq TA \leq +85^{\circ}$ C for industrial and $0^{\circ}$ C $\leq TA \leq +70^{\circ}$ C for commercial and $-40^{\circ}$ C $\leq TA \leq +70^{\circ}$ C for commercial and $-40^{\circ}$ C $\leq TA \leq +125^{\circ}$ C for extended |                   |                         |                      |                                                                                                                                                                       |  |  |

|---------------|-------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Sym   | Characteristic                    | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Тур†              | Мах                     | Units                | Conditions                                                                                                                                                            |  |  |

| D010          | IDD   | Supply Current <sup>(2, 4)</sup>  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.2<br>0.4<br>1.0 | 2.0<br>1.2<br>2.0       | mA<br>mA<br>mA       | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT mode, (Note 4)*<br>Fosc = 4 MHz, VDD = 3.0V, WDT disabled,<br>XT mode, (Note 4)*<br>Fosc = 10 MHz, VDD = 3.0V, WDT dis- |  |  |

|               |       |                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.0               | 6.0<br>7.0              | mA<br>mA             | abled, HS mode, (Note 6)<br>Fosc = 20 MHz, VDD = 4.5V, WDT dis-<br>abled, HS mode<br>Fosc = 20 MHz, VDD = 5.5V, WDT dis-                                              |  |  |

|               |       |                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35                | 70                      | μA                   | abled*, HS mode<br>Fosc = 32 kHz, VDD = 3.0V, WDT dis-<br>abled, LP mode                                                                                              |  |  |

| D010          | IDD   | Supply Current <sup>(2)</sup>     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.2<br>—<br>35    | 2.0<br>1.1<br>70        | mA<br>mA<br>μA       | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT mode, (Note 4)*<br>Fosc = 4 MHz, VDD = 2.5V, WDT disabled,<br>XT mode, (Note 4)<br>Fosc = 32 kHz, VDD = 2.5V, WDT dis-  |  |  |

| D020          | IPD   | Power-down Current <sup>(3)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   | 2.2<br>5.0<br>9.0<br>15 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 3.0V           VDD = 4.5V*           VDD = 5.5V           VDD = 5.5V Extended Temp.                                                                             |  |  |

| D020          | IPD   | Power-down Current <sup>(3)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <br>              | 2.0<br>2.2<br>9.0<br>15 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 2.5V<br>VDD = 3.0V*<br>VDD = 5.5V<br>VDD = 5.5V Extended Temp.                                                                                                  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

# 12.5 DC CHARACTERISTICS: PIC16C620A/C621A/C622A-40<sup>(7)</sup> (Commercial) PIC16CR620A-40<sup>(7)</sup> (Commercial)

| DC CH         | ARACTER                           | ISTICS                                                                 | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |          |           |            |                                                                            |  |  |  |

|---------------|-----------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|------------|----------------------------------------------------------------------------|--|--|--|

| Param<br>No.  | Sym                               | Characteristic                                                         | Min                                                                                                                                | Тур†     | Max       | Units      | Conditions                                                                 |  |  |  |

| D001          | Vdd                               | Supply Voltage                                                         | 3.0                                                                                                                                | _        | 5.5       | V          | Fosc = DC to 20 MHz                                                        |  |  |  |

| D002          | Vdr                               | RAM Data Retention Voltage <sup>(1)</sup>                              |                                                                                                                                    | 1.5*     |           | V          | Device in SLEEP mode                                                       |  |  |  |

| D003          | VPOR                              | VDD start voltage to ensure<br>Power-on Reset                          | —                                                                                                                                  | Vss      | _         | V          | See section on Power-on Reset for details                                  |  |  |  |

| D004          | SVDD                              | VDD rise rate to ensure Power-on<br>Reset                              | 0.05<br>*                                                                                                                          | —        | _         | V/ms       | See section on Power-on Reset for details                                  |  |  |  |

| D005          | VBOR                              | Brown-out Detect Voltage                                               | 3.65                                                                                                                               | 4.0      | 4.35      | V          | BOREN configuration bit is cleared                                         |  |  |  |

| D010          | IDD                               | Supply Current <sup>(2,4)</sup>                                        | —                                                                                                                                  | 1.2      | 2.0       | mA         | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT Osc mode, ( <b>Note 4</b> )* |  |  |  |

|               |                                   |                                                                        | —                                                                                                                                  | 0.4      | 1.2       | mA         | Fosc = 4 MHz, VDD = 3.0V, WDT disabled,<br>XT Osc mode, (Note 4)           |  |  |  |

|               |                                   |                                                                        | —                                                                                                                                  | 1.0      | 2.0       | mA         | Fosc = 10 MHz, VDD = 3.0V, WDT disabled,<br>HS Osc mode, ( <b>Note 6</b> ) |  |  |  |

|               |                                   |                                                                        | —                                                                                                                                  | 4.0      | 6.0       | mA         | Fosc = 20 MHz, VDD = 4.5V, WDT disabled,<br>HS Osc mode                    |  |  |  |

|               |                                   |                                                                        | —                                                                                                                                  | 4.0      | 7.0       | mA         | Fosc = 20 MHz, VDD = 5.5V, WDT disabled*,<br>HS Osc mode                   |  |  |  |

|               |                                   |                                                                        | —                                                                                                                                  | 35       | 70        | μA         | Fosc = 32 kHz, VDD = 3.0V, WDT disabled,<br>LP Osc mode                    |  |  |  |

| D020          | IPD                               | Power Down Current <sup>(3)</sup>                                      | _                                                                                                                                  | _        | 2.2       | μA         | VDD = 3.0V                                                                 |  |  |  |

|               |                                   |                                                                        | —                                                                                                                                  | —        | 5.0       | μA         | VDD = 4.5V*                                                                |  |  |  |

|               |                                   |                                                                        | —                                                                                                                                  | —        | 9.0       | μA         | VDD = 5.5V                                                                 |  |  |  |

|               |                                   | (5)                                                                    | —                                                                                                                                  | —        | 15        | μA         | VDD = 5.5V Extended                                                        |  |  |  |

| D022          | $\Delta$ IWDT                     | WDT Current <sup>(5)</sup>                                             | —                                                                                                                                  | 6.0      | 10        | μA         | VDD = 4.0V                                                                 |  |  |  |

| D022A         |                                   | Brown-out Reset Current <sup>(5)</sup>                                 |                                                                                                                                    | 75       | 12        | μA         | $(125^{\circ}C)$                                                           |  |  |  |

| D022A<br>D023 | $\Delta$ IBOR<br>$\Delta$ ICOMP   | Comparator Current for each                                            | _                                                                                                                                  | 75<br>30 | 125<br>60 | μA<br>μA   | BOD enabled, VDD = 5.0V<br>VDD = 4.0V                                      |  |  |  |

|               |                                   | Comparator <sup>(5)</sup>                                              |                                                                                                                                    |          |           |            |                                                                            |  |  |  |

| D023A         | $\Delta IVREF$                    | VREF Current <sup>(5)</sup>                                            | —                                                                                                                                  | 80       | 135       | μA         | VDD = 4.0V                                                                 |  |  |  |

|               | $\Delta \text{IEE Write}$         | Operating Current                                                      | —                                                                                                                                  |          | 3         | mA         | Vcc = 5.5V, SCL = 400 kHz                                                  |  |  |  |

|               | $\Delta \text{IEE} \ \text{Read}$ | Operating Current                                                      | —                                                                                                                                  |          | 1         | mA         |                                                                            |  |  |  |

|               | $\Delta IEE$                      | Standby Current                                                        | —                                                                                                                                  |          | 30        | μA         | Vcc = 3.0V, EE Vdd = Vcc                                                   |  |  |  |

|               | ΔIEE                              | Standby Current                                                        | —                                                                                                                                  |          | 100       | μA         | Vcc = 3.0V, EE Vdd = Vcc                                                   |  |  |  |

| 1A            | Fosc                              | LP Oscillator Operating Frequency                                      | 0                                                                                                                                  | —        | 200       | kHz        | All temperatures                                                           |  |  |  |

|               |                                   | RC Oscillator Operating Frequency                                      | 0                                                                                                                                  | -        | 4         | MHz        | All temperatures                                                           |  |  |  |

|               |                                   | XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0                                                                                                                                  | _        | 4<br>20   | MHz<br>MHz | All temperatures<br>All temperatures                                       |  |  |  |

|               |                                   | The Oscillator Operating Frequency                                     | U                                                                                                                                  |          | 20        | IVI⊓Z      | Air temperatures                                                           |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption. The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD, MCLR = VDD; WDT enabled/disabled as specified.

The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP

mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/ 2REXT (mA) with REXT in kΩ.

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

7: See Section 12.1 and Section 12.3 for 16C62X and 16CR62X devices for operation between 20 MHz and 40 MHz for valid modified characteristics.

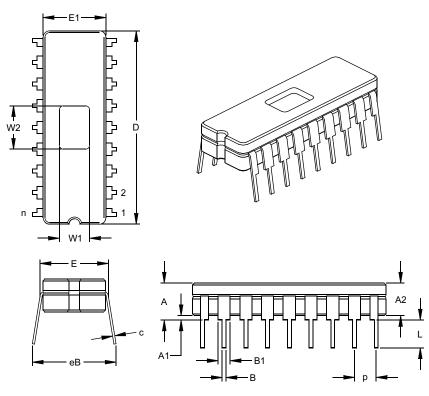

# 14.0 PACKAGING INFORMATION

18-Lead Ceramic Dual In-line with Window (JW) – 300 mil (CERDIP)

|                            | Units |      | INCHES* |      | MILLIMETERS |       |       |  |

|----------------------------|-------|------|---------|------|-------------|-------|-------|--|

| Dimension                  | MIN   | NOM  | MAX     | MIN  | NOM         | MAX   |       |  |

| Number of Pins             | n     |      | 18      |      |             | 18    |       |  |

| Pitch                      | р     |      | .100    |      |             | 2.54  |       |  |

| Top to Seating Plane       | Α     | .170 | .183    | .195 | 4.32        | 4.64  | 4.95  |  |

| Ceramic Package Height     | A2    | .155 | .160    | .165 | 3.94        | 4.06  | 4.19  |  |

| Standoff                   | A1    | .015 | .023    | .030 | 0.38        | 0.57  | 0.76  |  |

| Shoulder to Shoulder Width | Е     | .300 | .313    | .325 | 7.62        | 7.94  | 8.26  |  |

| Ceramic Pkg. Width         | E1    | .285 | .290    | .295 | 7.24        | 7.37  | 7.49  |  |

| Overall Length             | D     | .880 | .900    | .920 | 22.35       | 22.86 | 23.37 |  |

| Tip to Seating Plane       | L     | .125 | .138    | .150 | 3.18        | 3.49  | 3.81  |  |

| Lead Thickness             | С     | .008 | .010    | .012 | 0.20        | 0.25  | 0.30  |  |

| Upper Lead Width           | B1    | .050 | .055    | .060 | 1.27        | 1.40  | 1.52  |  |

| Lower Lead Width           | В     | .016 | .019    | .021 | 0.41        | 0.47  | 0.53  |  |

| Overall Row Spacing §      | eB    | .345 | .385    | .425 | 8.76        | 9.78  | 10.80 |  |

| Window Width               | W1    | .130 | .140    | .150 | 3.30        | 3.56  | 3.81  |  |

| Window Length              | W2    | .190 | .200    | .210 | 4.83        | 5.08  | 5.33  |  |

\* Controlling Parameter

§ Significant Characteristic

JEDEC Equivalent: MO-036

Drawing No. C04-010

# **PIC16C62X**

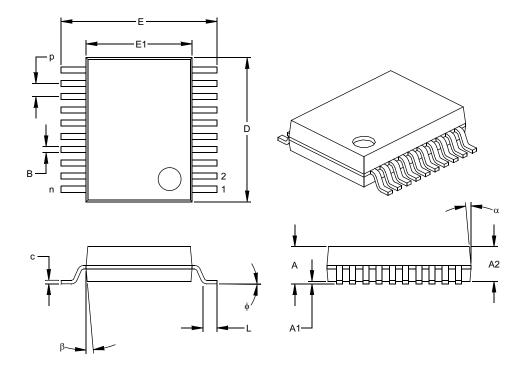

20-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

|                          | Units |      | INCHES* |      | MILLIMETERS |        |        |  |

|--------------------------|-------|------|---------|------|-------------|--------|--------|--|

| Dimensi                  | MIN   | NOM  | MAX     | MIN  | NOM         | MAX    |        |  |

| Number of Pins           | n     |      | 20      |      |             | 20     |        |  |

| Pitch                    | р     |      | .026    |      |             | 0.65   |        |  |

| Overall Height           | Α     | .068 | .073    | .078 | 1.73        | 1.85   | 1.98   |  |

| Molded Package Thickness | A2    | .064 | .068    | .072 | 1.63        | 1.73   | 1.83   |  |

| Standoff §               | A1    | .002 | .006    | .010 | 0.05        | 0.15   | 0.25   |  |

| Overall Width            | E     | .299 | .309    | .322 | 7.59        | 7.85   | 8.18   |  |

| Molded Package Width     | E1    | .201 | .207    | .212 | 5.11        | 5.25   | 5.38   |  |

| Overall Length           | D     | .278 | .284    | .289 | 7.06        | 7.20   | 7.34   |  |

| Foot Length              | L     | .022 | .030    | .037 | 0.56        | 0.75   | 0.94   |  |

| Lead Thickness           | С     | .004 | .007    | .010 | 0.10        | 0.18   | 0.25   |  |

| Foot Angle               | φ     | 0    | 4       | 8    | 0.00        | 101.60 | 203.20 |  |

| Lead Width               | В     | .010 | .013    | .015 | 0.25        | 0.32   | 0.38   |  |

| Mold Draft Angle Top     | α     | 0    | 5       | 10   | 0           | 5      | 10     |  |

| Mold Draft Angle Bottom  | β     | 0    | 5       | 10   | 0           | 5      | 10     |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-150 Drawing No. C04-072

DS30235J-page 116

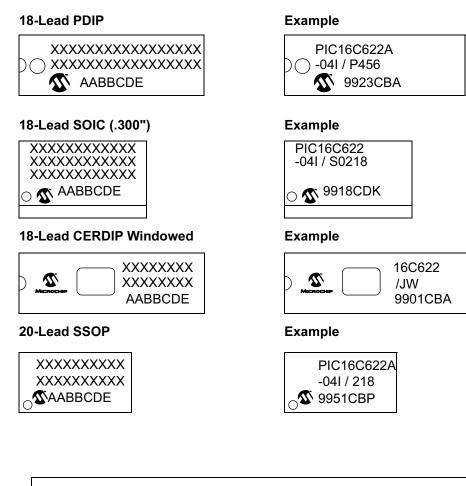

## 14.1 Package Marking Information

| Legend | d: XXX<br>Y<br>YY<br>WW<br>NNN | Customer specific information*<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code |

|--------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carried                     | nt the full Microchip part number cannot be marked on one line, it will<br>over to the next line thus limiting the number of available characters<br>her specific information.                          |

\* Standard PICmicro device marking consists of Microchip part number, year code, week code, and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

# PIC16C62X

NOTES:

# INDEX

| Α                      |    |

|------------------------|----|

| ADDLW Instruction      | 63 |

| ADDWF Instruction      | 63 |

| ANDLW Instruction      | 63 |

| ANDWF Instruction      | 63 |

| Architectural Overview | 9  |

| Assembler              |    |

| MPASM Assembler        | 75 |

| В                      |    |

| 8                                 |    |

|-----------------------------------|----|

| BCF Instruction                   | 64 |

| Block Diagram                     |    |

| TIMER0                            |    |

| TMR0/WDT PRESCALER                |    |

| Brown-Out Detect (BOD)            | 50 |

| BSF Instruction                   |    |

| BTFSC Instruction                 | 64 |

| BTFSS Instruction                 | 65 |

| С                                 |    |

| C Compilers                       |    |

| MPLAB C17                         |    |

| MPLAB C18                         |    |

| MPLAB C30                         |    |

| CALL Instruction                  |    |

| Clocking Scheme/Instruction Cycle |    |

| CLRF Instruction                  |    |

| CLRW Instruction                  |    |

| CLRWDT Instruction                |    |

|                                   |    |

| C Compilers                       |    |

|-----------------------------------|----|

| MPLAB C17                         | 76 |

| MPLAB C18                         | 76 |

| MPLAB C30                         |    |

| CALL Instruction                  |    |

| Clocking Scheme/Instruction Cycle | 12 |

| CLRF Instruction                  | 65 |

| CLRW Instruction                  |    |

| CLRWDT Instruction                |    |

| Code Protection                   | 60 |

| COMF Instruction                  |    |

| Comparator Configuration          |    |

| Comparator Interrupts             |    |

| Comparator Module                 |    |

| Comparator Operation              |    |

| Comparator Reference              |    |

| Configuration Bits                |    |

| Configuring the Voltage Reference |    |

| Crystal Operation                 |    |

|                                   |    |

## D

| Data Memory Organization14                   |

|----------------------------------------------|

| DC Characteristics                           |

| PIC16C717/770/771 88, 89, 90, 91, 96, 97, 98 |

| DECF Instruction                             |

| DECFSZ Instruction                           |

| Demonstration Boards                         |

| PICDEM 1                                     |

| PICDEM 17                                    |

| PICDEM 18R PIC18C601/80179                   |

| PICDEM 2 Plus                                |

| PICDEM 3 PIC16C92X                           |

| PICDEM 4                                     |

| PICDEM LIN PIC16C43X79                       |

| PICDEM USB PIC16C7X579                       |

| PICDEM.net Internet/Ethernet                 |

| Development Support75                        |

| E                                            |

| Errata                                       |

| Evaluation and Programming Tools             |

| External Crystal Oscillator Circuit          |

| G                                            |

| General purpose Register File                |

| GOTO Instruction                             |

| I                                                                        |    |  |  |  |

|--------------------------------------------------------------------------|----|--|--|--|

| I/O Ports                                                                |    |  |  |  |

| I/O Programming Considerations                                           |    |  |  |  |

| ID Locations                                                             |    |  |  |  |

| INCF Instruction                                                         |    |  |  |  |

| INCFSZ Instruction<br>In-Circuit Serial Programming                      |    |  |  |  |

| Indirect Addressing, INDF and FSR Registers                              |    |  |  |  |

| Instruction Flow/Pipelining                                              |    |  |  |  |

| Instruction Set                                                          |    |  |  |  |

| ADDLW                                                                    | 63 |  |  |  |

| ADDWF                                                                    |    |  |  |  |

| ANDLW                                                                    |    |  |  |  |

| ANDWF                                                                    |    |  |  |  |

| BCF                                                                      |    |  |  |  |

| BSF<br>BTFSC                                                             |    |  |  |  |

| BTFSS                                                                    |    |  |  |  |

| CALL                                                                     |    |  |  |  |

| CLRF                                                                     |    |  |  |  |

| CLRW                                                                     | 66 |  |  |  |

| CLRWDT                                                                   | 66 |  |  |  |

| COMF                                                                     |    |  |  |  |

| DECF                                                                     |    |  |  |  |

| DECFSZ                                                                   |    |  |  |  |

| GOTO                                                                     |    |  |  |  |

| INCF<br>INCFSZ                                                           |    |  |  |  |

| INCI 32                                                                  |    |  |  |  |

| IORWF                                                                    |    |  |  |  |

| MOVF                                                                     |    |  |  |  |

| MOVLW                                                                    | 68 |  |  |  |