Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 80 × 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c620-04i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Device Differences**

| Device                     | Voltage Range | Oscillator | Process Technology<br>(Microns) |

|----------------------------|---------------|------------|---------------------------------|

| PIC16C620 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C621 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C622 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C620A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

| PIC16CR620A <sup>(2)</sup> | 2.5 - 5.5     | See Note 1 | 0.7                             |

| PIC16C621A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

| PIC16C622A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

2: For ROM parts, operation from 2.5V - 3.0V will require the PIC16LCR62X parts.

**3:** For OTP parts, operation from 2.5V - 3.0V will require the PIC16LC62X parts.

4: For OTP parts, operations from 2.7V - 3.0V will require the PIC16LC62XA parts.

NOTES:

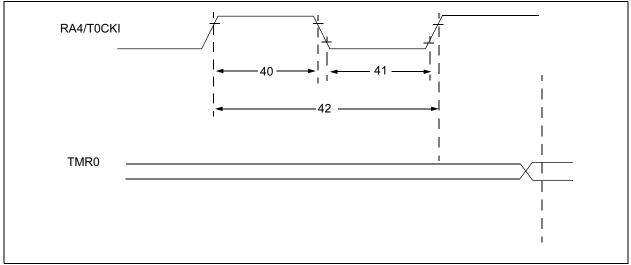

#### **OPTION Register** 4.2.2.2

The OPTION register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |

|-------|-------------------------------------------|

|       | TMR0, assign the prescaler to the WDT     |

|       | (PSA = 1).                                |

|         | R/W-1                    | R/W-1                                                                                                            | R/W-1                      | R/W-1                        | R/W-1         | R/W-1 | R/W-1 | R/W-1 |  |

|---------|--------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------|---------------|-------|-------|-------|--|

|         | RBPU                     | INTEDG                                                                                                           | TOCS                       | TOSE                         | PSA           | PS2   | PS1   | PS0   |  |

|         | bit 7                    |                                                                                                                  |                            |                              |               | •     |       | bit 0 |  |

| bit 7   | RBPU: PO                 | RTB Pull-u                                                                                                       | p Enable bi                | it                           |               |       |       |       |  |

|         |                          | 3 pull-ups ai<br>3 pull-ups ai                                                                                   |                            | y individual                 | port latch va | alues |       |       |  |

| bit 6   | INTEDG: I                | nterrupt Edg                                                                                                     | e Select bit               | -                            |               |       |       |       |  |

|         |                          |                                                                                                                  | edge of RB0<br>edge of RB0 |                              |               |       |       |       |  |

| bit 5   | TOCS: TMI                | R0 Clock Sc                                                                                                      | ource Select               | bit                          |               |       |       |       |  |

|         |                          | ion on RA4/<br>Il instruction                                                                                    | T0CKI pin<br>cycle clock   | (CLKOUT)                     |               |       |       |       |  |

| bit 4   | TOSE: TM                 | R0 Source E                                                                                                      | Edge Select                | bit                          |               |       |       |       |  |

|         |                          |                                                                                                                  |                            | ition on RA4<br>ition on RA4 |               |       |       |       |  |

| bit 3   | PSA: Pres                | caler Assigr                                                                                                     | ment bit                   |                              | -             |       |       |       |  |

|         |                          | <ul> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul> |                            |                              |               |       |       |       |  |

| bit 2-0 | <b>PS&lt;2:0&gt;</b> : F | Prescaler Ra                                                                                                     | ate Select bi              | ts                           |               |       |       |       |  |

|         | E                        | Bit Value T                                                                                                      | MR0 Rate                   | WDT Rate                     |               |       |       |       |  |

|         | -                        | 0000001                                                                                                          | 1:2<br>1:4                 | 1:1<br>1:2                   |               |       |       |       |  |

|         |                          | 010<br>011                                                                                                       | 1 : 8<br>1 : 16            | 1:4<br>1:8                   |               |       |       |       |  |

|         |                          | 100                                                                                                              | 1:32                       | 1:16                         |               |       |       |       |  |

|         |                          | 101                                                                                                              | 1:64                       | 1:32                         |               |       |       |       |  |

|         |                          | 110                                                                                                              | 1:128                      | 1:64                         |               |       |       |       |  |

|         |                          | 111                                                                                                              | 1:256                      | 1 : 128                      |               |       |       |       |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 7.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise the maximum delay of the comparators should be used (Table 12-2).

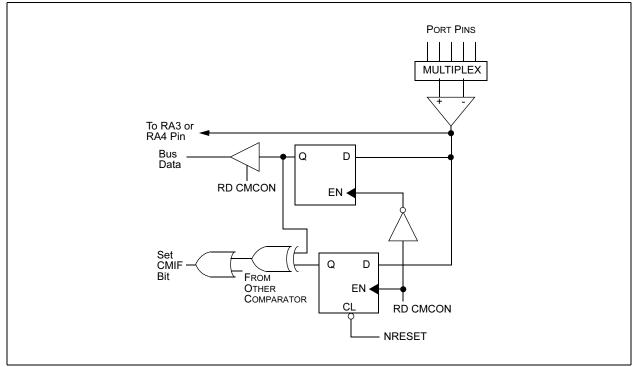

#### 7.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 7-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3 and RA4 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

#### FIGURE 7-3: COMPARATOR OUTPUT BLOCK DIAGRAM

#### 7.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be RESET by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | If a change in the CMCON register          |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | (C1OUT or C2OUT) should occur when a       |  |  |  |  |  |  |  |  |

|       | read operation is being executed (start of |  |  |  |  |  |  |  |  |

|       | the Q2 cycle), then the CMIF (PIR1<6>)     |  |  |  |  |  |  |  |  |

|       | interrupt flag may not get set.            |  |  |  |  |  |  |  |  |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

## 7.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will

Vdd ∆Vt = 0.6V RIC Rs < 10K Δικ **I**LEAKAGE CPIN VT = 0.6V ±500 nA 5 pF Vss Input Capacitance Legend CPIN = Threshold Voltage Vт = Leakage Current at the pin due to various junctions ILEAKAGE = = Interconnect Resistance RIC Rs = Source Impedance Analog Voltage VA =

FIGURE 7-4: ANALOG INPUT MODEL

wake up the device from SLEEP mode when enabled. While the comparator is powered-up, higher SLEEP currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering SLEEP. If the device wakes up from SLEEP, the contents of the CMCON register are not affected.

#### 7.8 Effects of a RESET

A device RESET forces the CMCON register to its RESET state. This forces the comparator module to be in the comparator RESET mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at RESET time. The comparators will be powered-down during the RESET interval.

#### 7.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 7-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latchup may occur. A maximum source impedance of  $10 \ k\Omega$ is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

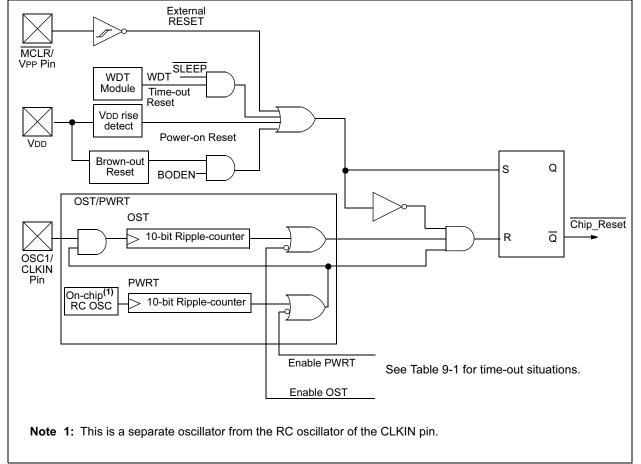

### 9.3 RESET

The PIC16C62X differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) WDT Reset (normal operation)

- e) WDT wake-up (SLEEP)

- f) Brown-out Reset (BOR)

Some registers are not affected in any RESET condition Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset,

MCLR Reset, WDT Reset and MCLR Reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 9-2. These bits are used in software to determine the nature of the RESET. See Table 9-5 for a full description of RESET states of all registers.

A simplified block diagram of the on-chip RESET circuit is shown in Figure 9-6.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 12-5 for pulse width specification.

#### **FIGURE 9-11: EXTERNAL POWER-ON RESET CIRCUIT (FOR** SLOW VDD POWER-UP) Vdd Vdd D R R1 MCLR PIC16C62X С Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down. **2:** < 40 k $\Omega$ is recommended to make sure that voltage drop across R does not violate the device's electrical specification. **3:** R1 = $100\Omega$ to 1 k $\Omega$ will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin

breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

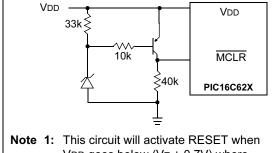

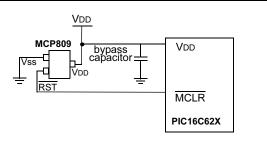

#### FIGURE 9-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate RESET when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- **2:** Internal Brown-out Reset circuitry should be disabled when using this circuit.

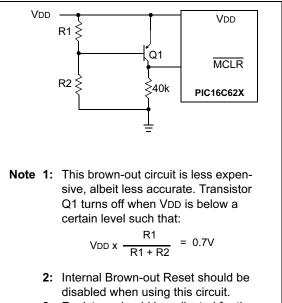

#### FIGURE 9-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

**3:** Resistors should be adjusted for the characteristics of the transistor.

#### FIGURE 9-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active RESET pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

| RLF              | Rotate                                                                                                                                                                                                           | Left f thr                                       | oua              | h Car                     | rv   |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------|---------------------------|------|--|

| Syntax:          | [ label ]                                                                                                                                                                                                        | RLF                                              | f,d              |                           |      |  |

| Operands:        | 0 ≤ f ≤ 1<br>d ∈ [0,1                                                                                                                                                                                            |                                                  |                  |                           |      |  |

| Operation:       | See des                                                                                                                                                                                                          | scription I                                      | pelov            | N                         |      |  |

| Status Affected: | С                                                                                                                                                                                                                |                                                  |                  |                           |      |  |

| Encoding:        | 00                                                                                                                                                                                                               | 1101                                             | df               | ff                        | ffff |  |

| escription:      | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |                                                  |                  |                           |      |  |

| Vords:           | 1                                                                                                                                                                                                                |                                                  |                  |                           |      |  |

| Cycles:          | 1                                                                                                                                                                                                                |                                                  |                  |                           |      |  |

| xample           | RLF                                                                                                                                                                                                              | REG1,                                            | 0                |                           |      |  |

|                  | Before I<br>After Ins                                                                                                                                                                                            | nstructio<br>REG1<br>C<br>struction<br>REG1<br>W | n<br>=<br>=<br>= | 1110<br>0<br>1110<br>1100 |      |  |

|                  |                                                                                                                                                                                                                  | С                                                | =                | 1                         |      |  |

| RRF              | Rotate R                                                                                                                                                                                                          | ight f th      | nroug       | gh Ca             | arry |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-------------------|------|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                         | RRF f          | ,d          |                   |      |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                |                |             |                   |      |  |  |  |

| Operation:       | See desc                                                                                                                                                                                                          | ription b      | elow        | '                 |      |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |                |             |                   |      |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                                | 1100           | df          | ff                | ffff |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |                |             |                   |      |  |  |  |

|                  | C Register f                                                                                                                                                                                                      |                |             |                   |      |  |  |  |

| Words:           | 1                                                                                                                                                                                                                 |                |             |                   |      |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                 |                |             |                   |      |  |  |  |

| Example          | rrf <b>REG1</b> ,<br>0                                                                                                                                                                                            |                |             |                   |      |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                |                |             |                   |      |  |  |  |

|                  |                                                                                                                                                                                                                   | REG1<br>C      | =<br>=      | 1110<br>0         | 0110 |  |  |  |

|                  | After Inst                                                                                                                                                                                                        |                |             |                   |      |  |  |  |

|                  | 1                                                                                                                                                                                                                 | REG1<br>W<br>C | =<br>=<br>= | 1110<br>0111<br>0 |      |  |  |  |

SLEEP

| <b>VIII</b>      |                                                                                                                                                                                                                                                       |       |           |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|--|--|--|--|

| Syntax:          | [ label<br>]                                                                                                                                                                                                                                          | SLEEF | D         |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                                  |       |           |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow \underline{W}DT \text{ prescaler,} \\ 1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                               |       |           |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                |       |           |  |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                                                                    | 0000  | 0000 0110 |  |  |  |  |

| Description:     | The power-down STATUS bit,<br>PD is cleared. Time-out<br>STATUS bit, TO is set. Watch-<br>dog Timer and its prescaler are<br>cleared.<br>The processor is put into SLEEP<br>mode with the oscillator<br>stopped. See Section 9.8 for<br>more details. |       |           |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                     |       |           |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                     |       |           |  |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                 |       |           |  |  |  |  |

#### 11.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 11.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 11.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command-line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities, and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping, and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high level source debugging with the MPLAB IDE.

## 11.6 MPLAB ASM30 Assembler, Linker, and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

#### 11.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PICmicro series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break, or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

#### 11.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

### 11.9 MPLAB ICE 2000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 2000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers. Software control of the MPLAB ICE 2000 in-circuit emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PICmicro microcontrollers.

The MPLAB ICE 2000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

### 11.10 MPLAB ICE 4000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 4000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for highend PICmicro microcontrollers. Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICD 4000 is a premium emulator system, providing the features of MPLAB ICE 2000, but with increased emulation memory and high speed performance for dsPIC30F and PIC18XXXX devices. Its advanced emulator features include complex triggering and timing, up to 2 Mb of emulation memory, and the ability to view variables in real-time.

The MPLAB ICE 4000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

## 11.11 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low cost, run-time development tool, connecting to the host PC via an RS-232 or high speed USB interface. This tool is based on the FLASH PICmicro MCUs and can be used to develop for these and other PICmicro microcontrollers. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers cost effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single-stepping and watching variables, CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real-time. MPLAB ICD 2 also serves as a development programmer for selected PICmicro devices.

### 11.12 PRO MATE II Universal Device Programmer

The PRO MATE II is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features an LCD display for instructions and error messages and a modular detachable socket assembly to support various package types. In Stand-Alone mode, the PRO MATE II device programmer can read, verify, and program PICmicro devices without a PC connection. It can also set code protection in this mode.

#### 11.13 PICSTART Plus Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus development programmer supports most PICmicro devices up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

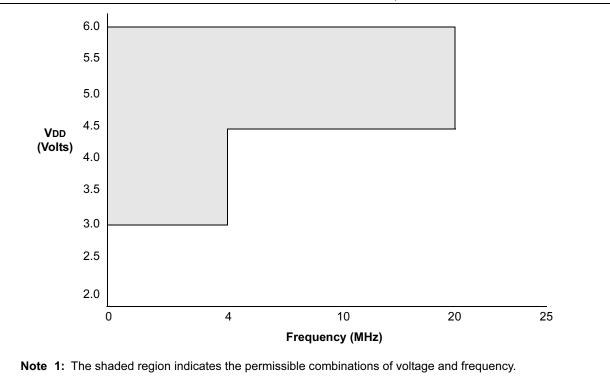

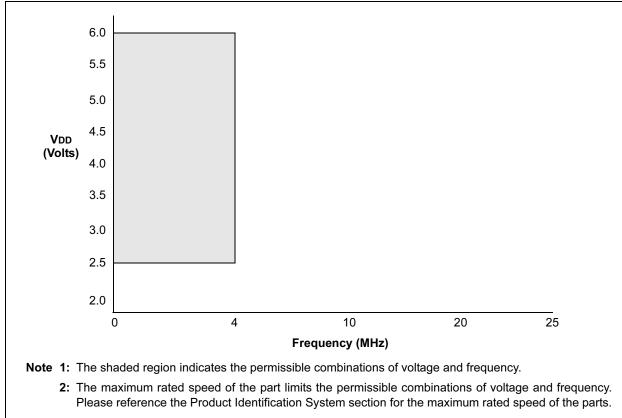

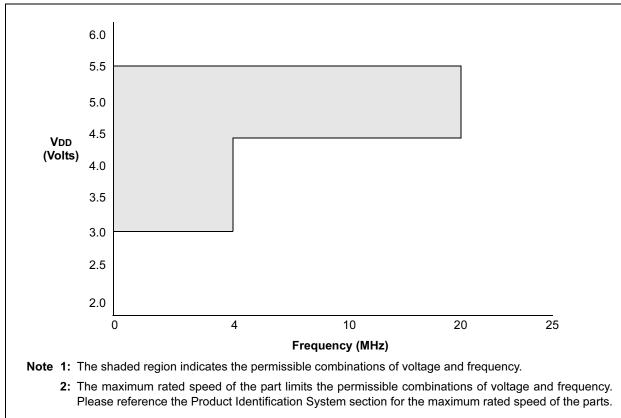

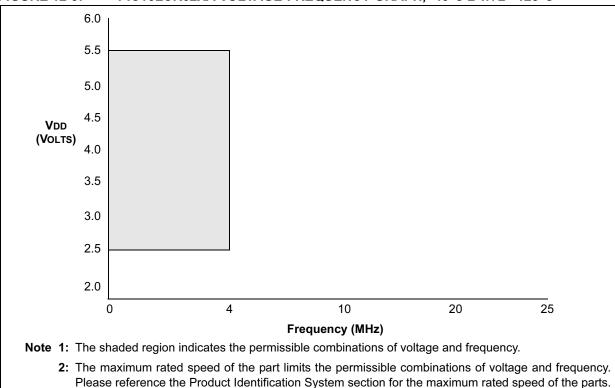

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

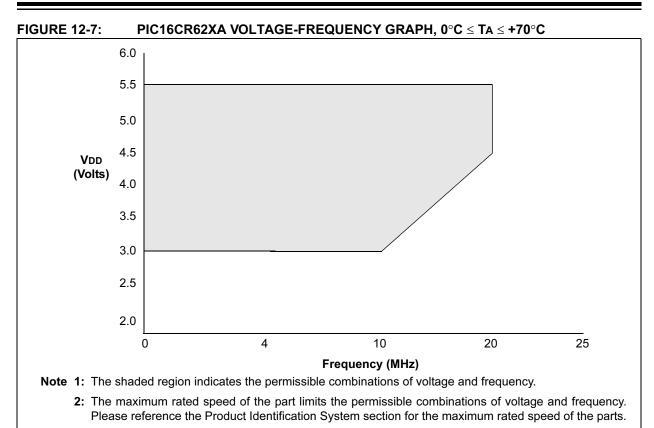

FIGURE 12-8: PIC16CR62XA VOLTAGE-FREQUENCY GRAPH, -40°C  $\leq$  TA  $\leq$  0°C, +70°C  $\leq$  TA  $\leq$  +125°C

#### 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended)

| PIC16C62X       Standard Operating Conditions (unless otherwis<br>Operating temperature -40°C ≤ TA ≤ +85°C for ind<br>0°C ≤ TA ≤ +70°C for con<br>-40°C ≤ TA ≤ +125°C for ex         Standard Operating Conditions (unless otherwise)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | dustrial and mmercial and                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                          |

| $\begin{array}{c} \mbox{PIC16LC62X} \\ \mbox{PIC16LC62X} \\ \mbox{Operating temperature} & -40^{\circ} C & \leq TA \leq +85^{\circ} C \mbox{ for ind} \\ & 0^{\circ} C & \leq TA \leq +70^{\circ} C \mbox{ for out} \\ & -40^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & = 0^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & = 0^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & = 0^{\circ} C \mbox{ for expansion} \\ & 0^{\circ$ | dustrial and<br>mmercial and<br>extended |

| Param.         Sym         Characteristic         Min         Typ†         Max         Units         Conditio           No.                Conditio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ns                                       |

| D001         VDD         Supply Voltage         3.0         —         6.0         V         See Figures 12-1, 12-2, 12-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3, 12-4, and 12-5                        |

| D001         VDD         Supply Voltage         2.5         —         6.0         V         See Figures 12-1, 12-2, 12-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3, 12-4, and 12-5                        |

| D002 VDR RAM Data Retention Voltage <sup>(1)</sup> — 1.5* — V Device in SLEEP mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                          |

| D002 VDR RAM Data Retention Voltage <sup>(1)</sup> — 1.5* — V Device in SLEEP mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                          |

| D003         VPOR         VDD start voltage to ensure         —         Vss         —         V         See section on Power-on Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | eset for details                         |

| D003         VPOR         VDD start voltage to<br>ensure Power-on Reset         —         Vss         —         V         See section on Power-on Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | eset for details                         |

| D004         SVDD         VDD rise rate to ensure         0.05*         —         —         V/ms         See section on Power-on Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | eset for details                         |

| D004         SVDD         VDD rise rate to ensure         0.05*         —         —         V/ms         See section on Power-on Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | eset for details                         |

| D005 VBOR Brown-out Detect Voltage 3.7 4.0 4.3 V BOREN configuration bit is c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | cleared                                  |