Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 896B (512 x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 80 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

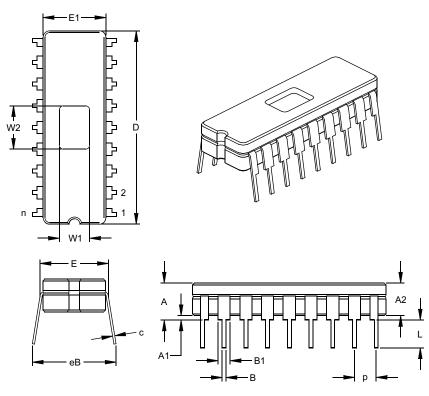

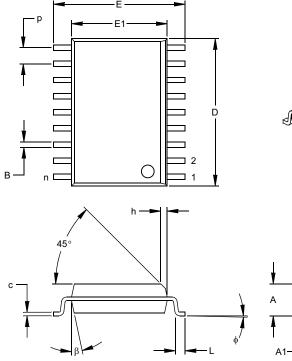

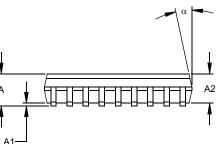

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c620-20-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Device Differences**

| Device                     | Voltage Range | Oscillator | Process Technology<br>(Microns) |

|----------------------------|---------------|------------|---------------------------------|

| PIC16C620 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C621 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C622 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C620A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

| PIC16CR620A <sup>(2)</sup> | 2.5 - 5.5     | See Note 1 | 0.7                             |

| PIC16C621A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

| PIC16C622A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

2: For ROM parts, operation from 2.5V - 3.0V will require the PIC16LCR62X parts.

**3:** For OTP parts, operation from 2.5V - 3.0V will require the PIC16LC62X parts.

4: For OTP parts, operations from 2.7V - 3.0V will require the PIC16LC62XA parts.

NOTES:

#### 4.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

| E PE<br>Global Internables all un<br>isables all in<br>Peripheral<br>nables all p<br>TMR0 Ove<br>nables the T<br>isables the                            | N-0     R/W-0       EIE     TOIE       rrupt Enable bit       n-masked interrunts       Interrupts       Interrupt Enable       n-masked periphoral interrunt       peripheral interrunt       erflow Interrupt End       TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | R/W-0<br>RBIE                                                                                                                                                        | R/W-0<br>T0IF                                                                                                                                                                                                                                | R/W-0<br>INTF                                                                                                                                                                                                            | R/W-x<br>RBIF<br>bit 0                                                                                                                                                                                                                                                                     |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the                                  | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          | bit 0                                                                                                                                                                                                                                                                                      |  |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the                                  | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the                                  | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

| sables all in<br>Peripheral<br>nables all un<br>sables all p<br>TMR0 Ove<br>nables the T<br>isables the                                                 | nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                                                                          | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

| nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the                                                                                  | n-masked periph<br>peripheral interru<br>rflow Interrupt Er<br>TMR0 interrupt                                                                                                                                                            | neral interrupt<br>pts                                                                                                  | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

| sables all p<br>TMR0 Ove<br>nables the<br>sables the                                                                                                    | peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                                                                                                                              | pts                                                                                                                     | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

| TMR0 Ove<br>nables the<br>sables the                                                                                                                    | rflow Interrupt Er<br>TMR0 interrupt                                                                                                                                                                                                     |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

| nables the<br>isables the                                                                                                                               | TMR0 interrupt                                                                                                                                                                                                                           | nable bit                                                                                                               |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

| sables the                                                                                                                                              |                                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

|                                                                                                                                                         | I MRU interrupt                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

|                                                                                                                                                         |                                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

|                                                                                                                                                         | External Interrupt                                                                                                                                                                                                                       |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

|                                                                                                                                                         | RB0/INT externa<br>RB0/INT externa                                                                                                                                                                                                       |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

|                                                                                                                                                         | hange Interrupt E                                                                                                                                                                                                                        |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

|                                                                                                                                                         | RB port change i                                                                                                                                                                                                                         |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

|                                                                                                                                                         | RB port change                                                                                                                                                                                                                           | •                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

| T0IF: TMR0 Overflow Interrupt Flag bit                                                                                                                  |                                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

| MR0 registe                                                                                                                                             | er has overflowed                                                                                                                                                                                                                        | d (must be cle                                                                                                          | eared in soft                                                                                                                                                        | ware)                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

| MR0 registe                                                                                                                                             | er did not overflov                                                                                                                                                                                                                      | W                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

| RB0/INT E                                                                                                                                               | xternal Interrupt                                                                                                                                                                                                                        | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

| <ul> <li>1 = The RB0/INT external interrupt occurred (must be cleared in software)</li> <li>0 = The RB0/INT external interrupt did not occur</li> </ul> |                                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

| RB Port Cl                                                                                                                                              | hange Interrupt F                                                                                                                                                                                                                        | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |

| 'hen at leas                                                                                                                                            |                                                                                                                                                                                                                                          | •                                                                                                                       | -                                                                                                                                                                    | (must be cle                                                                                                                                                                                                                                 | ared in softw                                                                                                                                                                                                            | ware)                                                                                                                                                                                                                                                                                      |  |

|                                                                                                                                                         | ne RB0/INT<br>ne RB0/INT<br>RB Port C<br>hen at leas                                                                                                                                                                                     | ne RB0/INT external interrune<br>RB0/INT external interrun<br>RB Port Change Interrupt I<br>hen at least one of the RB< | ne RB0/INT external interrupt did not occ<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins cha<br>one of the RB<7:4> pins have changed s | ne RB0/INT external interrupt occurred (must be clea<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state<br>one of the RB<7:4> pins have changed state | ne RB0/INT external interrupt occurred (must be cleared in softwa<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cle | ne RB0/INT external interrupt occurred (must be cleared in software)<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cleared in softwore)<br>one of the RB<7:4> pins have changed state |  |

| REGISTER 4-3: | INTCON REGISTER (ADDRESS 0BH OR 8BH) |

|---------------|--------------------------------------|

|---------------|--------------------------------------|

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 4.2.2.4 PIE1 Register

This register contains the individual enable bit for the comparator interrupt.

| <b>REGISTER 4-4:</b> | PIE1 REGISTER (ADDRESS 8CH)                                                                                                                       |            |          |     |     |     |     |       |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|-----|-----|-----|-----|-------|

|                      | U-0                                                                                                                                               | R/W-0      | U-0      | U-0 | U-0 | U-0 | U-0 | U-0   |

|                      |                                                                                                                                                   | CMIE       | _        |     |     | —   | _   | —     |

|                      | bit 7                                                                                                                                             |            |          |     |     |     |     | bit 0 |

| bit 7                | Unimpleme                                                                                                                                         | nted: Read | d as '0' |     |     |     |     |       |

| bit 6                | <b>CMIE</b> : Comparator Interrupt Enable bit<br>1 = Enables the Comparator interrupt<br>0 = Disables the Comparator interrupt                    |            |          |     |     |     |     |       |

| bit 5-0              | Unimpleme                                                                                                                                         | nted: Read | d as '0' |     |     |     |     |       |

|                      | Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'- n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown |            |          |     |     |     |     |       |

#### 4.2.2.5 PIR1 Register

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of |

|-------|--------------------------------------------------------------------------------------------|

|       | its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User               |

|       | software should ensure the appropriate                                                     |

|       | interrupt flag bits are clear prior to enabling                                            |

|       | an interrupt.                                                                              |

#### REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

| ER 4-5: | PIRT REGI                            | SIER (AL   | DRESS 0  | СН)          |              |           |                |        |  |

|---------|--------------------------------------|------------|----------|--------------|--------------|-----------|----------------|--------|--|

|         | U-0                                  | R/W-0      | U-0      | U-0          | U-0          | U-0       | U-0            | U-0    |  |

|         |                                      | CMIF       |          | —            | _            |           |                |        |  |

|         | bit 7                                |            |          |              |              |           |                | bit 0  |  |

|         |                                      |            |          |              |              |           |                |        |  |

| bit 7   | Unimpleme                            | ented: Rea | d as '0' |              |              |           |                |        |  |

| bit 6   | CMIF: Comparator Interrupt Flag bit  |            |          |              |              |           |                |        |  |

|         | 1 = Comparator input has changed     |            |          |              |              |           |                |        |  |

|         | 0 = Comparator input has not changed |            |          |              |              |           |                |        |  |

| bit 5-0 | Unimplemented: Read as '0'           |            |          |              |              |           |                |        |  |

|         |                                      |            |          |              |              |           |                |        |  |

|         | Legend:                              |            |          |              |              |           |                |        |  |

|         | R = Readab                           | ole bit    | W = W    | /ritable bit | U = Unim     | plemented | bit, read as ' | 0'     |  |

|         | - n = Value                          | at POR     | '1' = B  | it is set    | '0' = Bit is | s cleared | x = Bit is u   | nknown |  |

| Name    | Bit # | Buffer Type           | Function                                                                                                                |

|---------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0  | TTL/ST <sup>(1)</sup> | Input/output or external interrupt input. Internal software programmable weak pull-up.                                  |

| RB1     | bit1  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB2     | bit2  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB3     | bit3  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB4     | bit4  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB5     | bit5  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB6     | bit6  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock pin. |

| RB7     | bit7  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data pin.  |

#### TABLE 5-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h     | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX XXXX       | uuuu uuuu                       |

| 86h     | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h     | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

Legend: u = unchanged, x = unknown

Note 1: Shaded bits are not used by PORTB.

#### 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading the port register reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}\,,\ {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

|                                                       | = =                   |

|-------------------------------------------------------|-----------------------|

| ; Initial PORT settings:                              | PORTB<7:4> Inputs     |

| ;                                                     | PORTB<3:0> Outputs    |

| ; PORTB<7:6> have external ; connected to other circu |                       |

| ;                                                     |                       |

| ;                                                     | PORT latch PORT pins  |

| ;                                                     |                       |

|                                                       | -                     |

|                                                       |                       |

| BCF PORTB, 7                                          | ; 01pp pppp 11pp pppp |

| BCF PORTB, 6                                          | ; 10pp pppp 11pp pppp |

| BSF STATUS, RPO                                       | ;                     |

| BCF TRISB, 7                                          | ;10pp pppp 11pp pppp  |

| BCF TRISB, 6                                          | ;10pp pppp 10pp pppp  |

| ;                                                     |                       |

| ; Note that the user may h                            | nave expected the pin |

| ; values to be 00pp pppp.                             | The 2nd BCF caused    |

| ; RB7 to be latched as the                            | e pin value (High).   |

|                                                       |                       |

### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

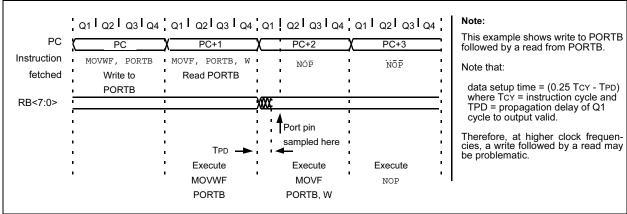

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-7). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 5-7: SUCCESSIVE I/O OPERATION

#### 7.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be RESET by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | If a change in the CMCON register          |

|-------|--------------------------------------------|

|       | (C1OUT or C2OUT) should occur when a       |

|       | read operation is being executed (start of |

|       | the Q2 cycle), then the CMIF (PIR1<6>)     |

|       | interrupt flag may not get set.            |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

### 7.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will

Vdd ∆Vt = 0.6V RIC Rs < 10K Δικ **I**LEAKAGE CPIN VT = 0.6V ±500 nA 5 pF Vss Input Capacitance Legend CPIN = Threshold Voltage Vт = Leakage Current at the pin due to various junctions ILEAKAGE = = Interconnect Resistance RIC Rs = Source Impedance Analog Voltage VA =

FIGURE 7-4: ANALOG INPUT MODEL

wake up the device from SLEEP mode when enabled. While the comparator is powered-up, higher SLEEP currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering SLEEP. If the device wakes up from SLEEP, the contents of the CMCON register are not affected.

#### 7.8 Effects of a RESET

A device RESET forces the CMCON register to its RESET state. This forces the comparator module to be in the comparator RESET mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at RESET time. The comparators will be powered-down during the RESET interval.

#### 7.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 7-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latchup may occur. A maximum source impedance of  $10 \ k\Omega$ is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

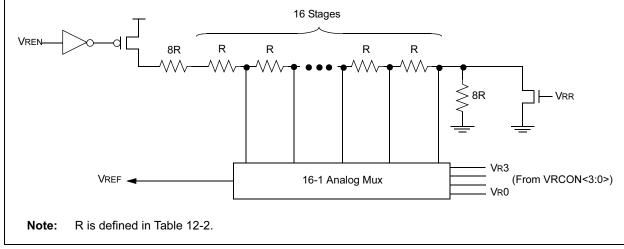

#### 8.0 **VOLTAGE REFERENCE** MODULE

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Register 8-1. The block diagram is given in Figure 8-1.

#### 8.1 **Configuring the Voltage Reference**

The Voltage Reference can output 16 distinct voltage levels for each range. The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 0: VREF = (VDD x 1/4) + (VR<3:0>/32) x VDD

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 12-1). Example 8-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

|                                                                             | R/W-0                                                                  | R/W-0                   | R/W-0                      | U-0                     | R/W-0       | R/W-0      | R/W-0        | R/W-0  |  |  |  |  |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------|----------------------------|-------------------------|-------------|------------|--------------|--------|--|--|--|--|

|                                                                             | VREN                                                                   | VROE                    | Vrr                        | —                       | VR3         | VR2        | VR1          | VR0    |  |  |  |  |

|                                                                             | bit 7                                                                  |                         |                            |                         |             |            |              | bit 0  |  |  |  |  |

|                                                                             |                                                                        |                         |                            |                         |             |            |              |        |  |  |  |  |

| bit 7                                                                       |                                                                        | Enable<br>ircuit powere | od on                      |                         |             |            |              |        |  |  |  |  |

|                                                                             |                                                                        | -                       | ed down, no                | IDD drain               |             |            |              |        |  |  |  |  |

| bit 6                                                                       |                                                                        | F Output En             |                            |                         |             |            |              |        |  |  |  |  |

|                                                                             | 1 = VREF is output on RA2 pin<br>0 = VREF is disconnected from RA2 pin |                         |                            |                         |             |            |              |        |  |  |  |  |

| bit 5                                                                       |                                                                        |                         |                            | 2 pm                    |             |            |              |        |  |  |  |  |

| bit o                                                                       | <b>VRR:</b> VREF Range selection<br>1 = Low Range                      |                         |                            |                         |             |            |              |        |  |  |  |  |

|                                                                             | 0 = High R                                                             | ange                    |                            |                         |             |            |              |        |  |  |  |  |

| bit 4                                                                       | Unimplem                                                               | ented: Rea              | d as '0'                   |                         |             |            |              |        |  |  |  |  |

| bit 3-0                                                                     |                                                                        |                         |                            | VR [3:0] ≤ 1            | 5           |            |              |        |  |  |  |  |

|                                                                             |                                                                        |                         | (VR<3:0>/ 2<br>1/4 * Voo + | 4) * VDD<br>(VR<3:0>/ 3 | 2) * \/חח   |            |              |        |  |  |  |  |

|                                                                             |                                                                        | - 0. VILLI -            |                            | (111-0.0-7-0            | 2) 100      |            |              |        |  |  |  |  |

|                                                                             | Legend:                                                                |                         |                            |                         |             |            |              |        |  |  |  |  |

|                                                                             | R = Reada                                                              | ble bit                 | W = W                      | /ritable bit            | U = Unim    | nplemented | bit, read as | '0'    |  |  |  |  |

|                                                                             | - n = Value                                                            | at POR                  | '1' = B                    | it is set               | '0' = Bit i | s cleared  | x = Bit is u | nknown |  |  |  |  |

| 8-1:                                                                        | VOLTAGE                                                                | REFERE                  |                            | K DIAGRA                | M           |            |              |        |  |  |  |  |

|                                                                             |                                                                        |                         | 16 \$                      | Stages                  |             |            |              |        |  |  |  |  |

| $\sim$                                                                      |                                                                        | _                       |                            |                         | _           | _          |              |        |  |  |  |  |

| $-\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | 에드 8R                                                                  | R                       | R                          | R                       | R           |            |              |        |  |  |  |  |

|                                                                             |                                                                        | <u>\</u>                |                            |                         |             | • •        |              |        |  |  |  |  |

#### **REGISTER 8-1:** VRCON REGISTER(ADDRESS 9Fh)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### **FIGURE 8-**

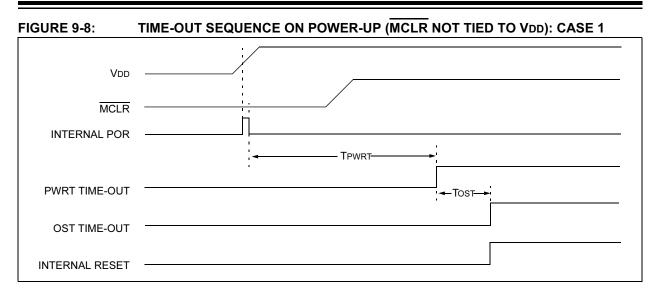

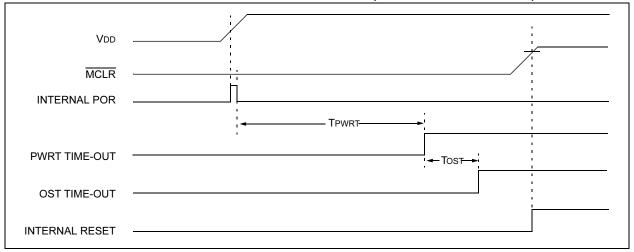

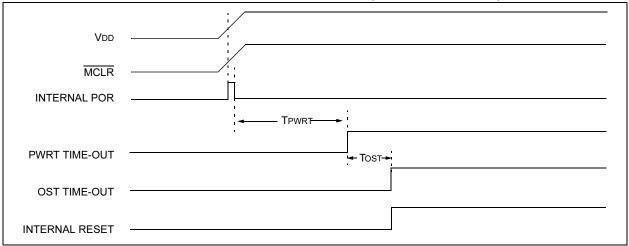

#### 9.4.5 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with <u>PWRTE</u> bit erased (<u>PWRT</u> disabled), there will be no time-out at all. Figure 9-8, Figure 9-9 and Figure 9-10 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 9-9). This is useful for testing purposes or to synchronize more than one PIC16C62X device operating in parallel.

Table 9-4 shows the RESET conditions for some special registers, while Table 9-5 shows the RESET conditions for all the registers.

#### 9.4.6 POWER CONTROL (PCON)/ STATUS REGISTER

The power control/STATUS register, PCON (address 8Eh), has two bits.

Bit0 is  $\overline{\text{BOR}}$  (Brown-out).  $\overline{\text{BOR}}$  is unknown on Poweron Reset. It must then be set by the user and checked on subsequent RESETS to see if  $\overline{\text{BOR}} = 0$ , indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$  STATUS bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent RESET, if POR is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe              | er-up     | Brown-out Reset   | Wake-up<br>from SLEEP |  |

|--------------------------|-------------------|-----------|-------------------|-----------------------|--|

|                          | PWRTE = 0         | PWRTE = 1 | Brown-out Reset   |                       |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc             |  |

| RC                       | 72 ms             | _         | 72 ms             | _                     |  |

#### TABLE 9-1: TIME-OUT IN VARIOUS SITUATIONS

| <b>TABLE 9-2</b> : | STATUS/PCON BITS AND THEIR SIGNIFICANCE |

|--------------------|-----------------------------------------|

|--------------------|-----------------------------------------|

| POR | BOR | то | PD |                                    |

|-----|-----|----|----|------------------------------------|

| 0   | Х   | 1  | 1  | Power-on Reset                     |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR          |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR          |

| 1   | 0   | Х  | Х  | Brown-out Reset                    |

| 1   | 1   | 0  | u  | WDT Reset                          |

| 1   | 1   | 0  | 0  | WDT Wake-up                        |

| 1   | 1   | u  | u  | MCLR Reset during normal operation |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP            |

Legend: u = unchanged, x = unknown

#### TABLE 9-3: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 83h     | STATUS |       |       |       | TO    | PD    |       |       |       | 0001 1xxx             | 000q quuu                                      |

| 8Eh     | PCON   | _     | _     |       | _     | _     | _     | POR   | BOR   | 0x                    | uq                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 9-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

### **10.0 INSTRUCTION SET SUMMARY**

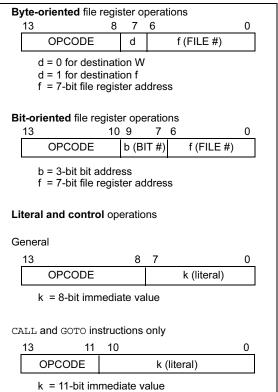

Each PIC16C62X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16C62X instruction set summary in Table 10-2 lists **byte-oriented**, **bitoriented**, and **literal and control** operations. Table 10-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 10-1: OPCODE FIELD DESCRIPTIONS

| DESCRIPTIONS  |                                                                                                                                                                                |  |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Field         | Description                                                                                                                                                                    |  |  |  |  |  |  |

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |  |  |  |  |  |  |

| W             | Working register (accumulator)                                                                                                                                                 |  |  |  |  |  |  |

| b             | Bit address within an 8-bit file register                                                                                                                                      |  |  |  |  |  |  |

| k             | Literal field, constant data or label                                                                                                                                          |  |  |  |  |  |  |

| х             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |  |  |  |  |  |  |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |  |  |  |  |  |  |

| label         | Label name                                                                                                                                                                     |  |  |  |  |  |  |

| TOS           | Top of Stack                                                                                                                                                                   |  |  |  |  |  |  |

| PC            | Program Counter                                                                                                                                                                |  |  |  |  |  |  |

| PCLAT<br>H    | Program Counter High Latch                                                                                                                                                     |  |  |  |  |  |  |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |  |  |  |  |  |  |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |  |  |  |  |  |  |

| то            | Time-out bit                                                                                                                                                                   |  |  |  |  |  |  |

| PD            | Power-down bit                                                                                                                                                                 |  |  |  |  |  |  |

| dest          | Destination either the W register or the specified regis-<br>ter file location                                                                                                 |  |  |  |  |  |  |

| []            | Options                                                                                                                                                                        |  |  |  |  |  |  |

| ()            | Contents                                                                                                                                                                       |  |  |  |  |  |  |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |  |  |  |  |  |  |

| < >           | Register bit field                                                                                                                                                             |  |  |  |  |  |  |

| ∈             | In the set of                                                                                                                                                                  |  |  |  |  |  |  |

| italics       | User defined term (font is courier)                                                                                                                                            |  |  |  |  |  |  |

|               |                                                                                                                                                                                |  |  |  |  |  |  |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- **Bit-oriented** operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 10-1 lists the instructions recognized by the MPASM  $^{\rm TM}$  assembler.

Figure 10-1 shows the three general formats that the instructions can have.

| Note: | To maintain upward compatibility with     |   |  |  |  |  |  |

|-------|-------------------------------------------|---|--|--|--|--|--|