Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 896B (512 x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 96 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c620a-04-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0     | General Description                 | . 5 |

|---------|-------------------------------------|-----|

| 2.0     | PIC16C62X Device Varieties          | . 7 |

|         | Architectural Overview              |     |

|         | Memory Organization                 |     |

| 5.0     | I/O Ports                           | 25  |

| 6.0     | Timer0 Module                       | 31  |

| 7.0     | Comparator Module                   | 37  |

| 8.0     | Voltage Reference Module            | 43  |

| 9.0     | Special Features of the CPU         | 45  |

| 10.0    | Instruction Set Summary             | 61  |

|         | Development Support                 |     |

| 12.0    | Electrical Specifications           | 81  |

| 13.0    | Device Characterization Information | 09  |

| 14.0    | Packaging Information 1             | 13  |

|         | Jix A: Enhancements 1               |     |

| Append  | Jix B: Compatibility                | 19  |

| Index   |                                     | 21  |

| On-Line | e Support 1                         | 23  |

| System  | Is Information and Upgrade Hot Line | 23  |

|         | Response 1                          |     |

| Product | t Identification System 1           | 25  |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

NOTES:

### 4.2 Data Memory Organization

The data memory (Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7) is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20-7Fh (Bank0) on the PIC16C620A/CR620A/621A and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16C622 and PIC16C622A are General Purpose Registers implemented as static RAM. Some Special Purpose Registers are mapped in Bank 1.

Addresses F0h-FFh of bank1 are implemented as common ram and mapped back to addresses 70h-7Fh in bank0 on the PIC16C620A/621A/622A/CR620A.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 80 x 8 in the PIC16C620/621, 96 x 8 in the PIC16C620A/621A/CR620A and 128 x 8 in the PIC16C622(A). Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

#### 4.2.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uuluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any STATUS bit. For other instructions not affecting any STATUS bits, see the "Instruction Set Summary".

- Note 1: The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16C62X and should be programmed as '0'. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The <u>C and DC bits</u> operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

#### REGISTER 4-1: STATUS REGISTER (ADDRESS 03H OR 83H)

|         | Reserved                                                                                                                                                                | Reserved                           | R/W-0          | R-1            | R-1            | R/W-x          | R/W-x        | R/W-x          |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|----------------|----------------|--------------|----------------|--|

|         | IRP                                                                                                                                                                     | RP1                                | RP0            | TO             | PD             | Z              | DC           | С              |  |

|         | bit 7                                                                                                                                                                   |                                    |                |                |                |                |              | bit 0          |  |

|         |                                                                                                                                                                         |                                    |                |                |                |                |              |                |  |

| bit 7   | -                                                                                                                                                                       | ter Bank Sel                       | -              | d for indirect | addressing     | )              |              |                |  |

|         |                                                                                                                                                                         | , 3 (100h - 1<br>, 1 (00h - FF     |                |                |                |                |              |                |  |

|         |                                                                                                                                                                         | t is reserved                      |                | 16C62X; alv    | /ays maintai   | n this bit cle | ar.          |                |  |

| bit 6-5 |                                                                                                                                                                         | Register Ban                       |                |                | -              |                |              |                |  |

|         |                                                                                                                                                                         | 1 (80h - FFh                       |                |                |                |                |              |                |  |

|         |                                                                                                                                                                         | 0 (00h - 7Fh                       |                |                |                |                |              |                |  |

|         | Each bank<br>clear.                                                                                                                                                     | is 128 bytes                       | . The RP1 t    | oit is reserve | ed on the PIC  | C16C62X; a     | lways mainta | ain this bit   |  |

| bit 4   | TO: Time-c                                                                                                                                                              | out bit                            |                |                |                |                |              |                |  |

|         |                                                                                                                                                                         | ower-up, CLI                       | RWDT instruc   | ction. or SLE  | EP instruction | on             |              |                |  |

|         |                                                                                                                                                                         | time-out oc                        |                | ,              |                |                |              |                |  |

| bit 3   | PD: Power                                                                                                                                                               | -down bit                          |                |                |                |                |              |                |  |

|         | -                                                                                                                                                                       | ower-up or b<br>cution of the      | -              |                | n              |                |              |                |  |

| bit 2   | Z: Zero bit                                                                                                                                                             |                                    |                |                |                |                |              |                |  |

|         |                                                                                                                                                                         | sult of an arit<br>sult of an arit |                |                |                | )              |              |                |  |

| bit 1   | 0 = The result of an arithmetic or logic operation is not zero<br><b>DC</b> : Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)(for borrow the polarity  |                                    |                |                |                |                |              |                |  |

|         | is reversed)                                                                                                                                                            |                                    |                |                |                |                |              |                |  |

|         | <ul> <li>1 = A carry-out from the 4th low order bit of the result occurred</li> <li>0 = No carry-out from the 4th low order bit of the result</li> </ul>                |                                    |                |                |                |                |              |                |  |

|         |                                                                                                                                                                         | -                                  |                |                |                |                |              |                |  |

| bit 0   | C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)                                                                                                           |                                    |                |                |                |                |              |                |  |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |                                    |                |                |                |                |              |                |  |

|         | <b>Note:</b> For borrow the polarity is reversed. A subtraction is executed by adding the two's                                                                         |                                    |                |                |                |                |              |                |  |

|         |                                                                                                                                                                         | complement                         |                |                |                |                |              | s, this bit is |  |

|         |                                                                                                                                                                         | loaded with e                      | either the hig | gh or low or   | der bit of the | source reg     | ister.       |                |  |

|         | Legend:                                                                                                                                                                 | L. L. 14                           |                |                |                |                | hit on all   | 0              |  |

|         | R = Reada                                                                                                                                                               |                                    |                | ritable bit    |                | •              | bit, read as |                |  |

|         | - n = Value                                                                                                                                                             | at POR                             | 1′ = Bi        | it is set      | '0' = Bit i    | scleared       | x = Bit is u | nknown         |  |

#### 4.2.2.4 PIE1 Register

This register contains the individual enable bit for the comparator interrupt.

| <b>REGISTER 4-4:</b> | PIE1 REGIS                                        | STER (AD   | DRESS 80       | CH)                       |     |                         |                                |       |

|----------------------|---------------------------------------------------|------------|----------------|---------------------------|-----|-------------------------|--------------------------------|-------|

|                      | U-0                                               | R/W-0      | U-0            | U-0                       | U-0 | U-0                     | U-0                            | U-0   |

|                      |                                                   | CMIE       | _              |                           |     | —                       | _                              | —     |

|                      | bit 7                                             |            |                |                           |     |                         |                                | bit 0 |

| bit 7                | Unimpleme                                         | nted: Read | d as '0'       |                           |     |                         |                                |       |

| bit 6                | <b>CMIE</b> : Comp<br>1 = Enables<br>0 = Disables | the Compa  | arator interru | upt                       |     |                         |                                |       |

| bit 5-0              | Unimpleme                                         | nted: Read | d as '0'       |                           |     |                         |                                |       |

|                      | Legend:<br>R = Readab<br>- n = Value a            |            |                | /ritable bit<br>it is set |     | nplemented<br>s cleared | bit, read as '<br>x = Bit is u |       |

### 4.2.2.5 PIR1 Register

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | its corresponding enable bit or the global<br>enable bit, GIE (INTCON<7>). User            |  |  |  |  |  |

|       | software should ensure the appropriate                                                     |  |  |  |  |  |

|       | interrupt flag bits are clear prior to enabling                                            |  |  |  |  |  |

|       | an interrupt.                                                                              |  |  |  |  |  |

## REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

| ER 4-5: | PIRT REGI   | SIER (AL      | DRESS 0       | СН)          |              |           |                |        |

|---------|-------------|---------------|---------------|--------------|--------------|-----------|----------------|--------|

|         | U-0         | R/W-0         | U-0           | U-0          | U-0          | U-0       | U-0            | U-0    |

|         |             | CMIF          |               | —            | _            |           |                |        |

|         | bit 7       |               |               |              |              |           |                | bit 0  |

|         |             |               |               |              |              |           |                |        |

| bit 7   | Unimpleme   | ented: Rea    | d as '0'      |              |              |           |                |        |

| bit 6   | CMIF: Com   | parator Inte  | errupt Flag b | it           |              |           |                |        |

|         | 1 = Compai  | rator input h | nas changed   | l            |              |           |                |        |

|         | 0 = Compai  | rator input h | nas not chan  | iged         |              |           |                |        |

| bit 5-0 | Unimpleme   | ented: Rea    | d as '0'      |              |              |           |                |        |

|         |             |               |               |              |              |           |                |        |

|         | Legend:     |               |               |              |              |           |                |        |

|         | R = Readab  | ole bit       | W = W         | /ritable bit | U = Unim     | plemented | bit, read as ' | 0'     |

|         | - n = Value | at POR        | '1' = B       | it is set    | '0' = Bit is | s cleared | x = Bit is u   | nknown |

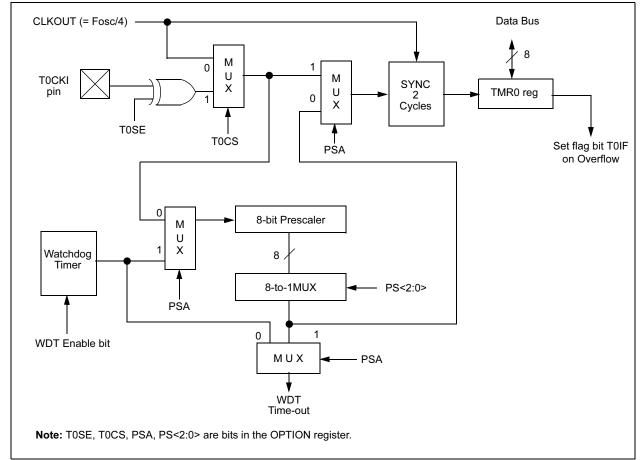

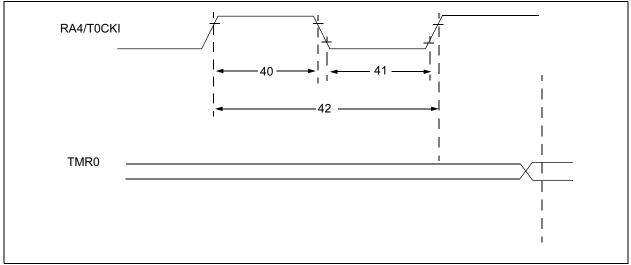

### 6.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 6-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

#### FIGURE 6-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to WDT.)

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

|          |              | ,                                             |

|----------|--------------|-----------------------------------------------|

| 1.BCF    | STATUS, RPO  | ;Skip if already in<br>;Bank 0                |

| 2.CLRWDT |              | ;Clear WDT                                    |

| 3.CLRF   | TMR0         | ;Clear TMR0 & Prescaler                       |

| 4.BSF    | STATUS, RPO  | ;Bank 1                                       |

| 5.MOVLW  | '00101111'b; | ;These 3 lines (5, 6, 7)                      |

| 6.MOVWF  | OPTION       | ;are required only if<br>;desired PS<2:0> are |

| 7.CLRWDT |              | ;000 or 001                                   |

| 8.MOVLW  | '00101xxx'b  | ;Set Postscaler to                            |

| 9.MOVWF  | OPTION       | ;desired WDT rate                             |

| 10.BCF   | STATUS, RPO  | ;Return to Bank 0                             |

|          |              |                                               |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 6-2. This precaution must be taken even if the WDT is disabled.

## EXAMPLE 6-2:

#### CHANGING PRESCALER (WDT→TIMER0)

|        | •           | ,                                        |

|--------|-------------|------------------------------------------|

| CLRWDT |             | ;Clear WDT and                           |

|        |             | ;prescaler                               |

| BSF    | STATUS, RPO |                                          |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new<br>;prescale value and |

|        |             | ;clock source                            |

| MOVWF  | OPTION REG  |                                          |

| BCF    | STATUS, RPO |                                          |

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6       | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|----------|-------------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 r | nodule regi | ster  |        |        |        |        |        | XXXX XXXX       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE      | PEIE        | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | RBPU     | INTEDG      | TOCS  | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _        |             | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

**Note:** Shaded bits are not used by TMR0 module.

### 9.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

#### 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

#### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

The Power-up Time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

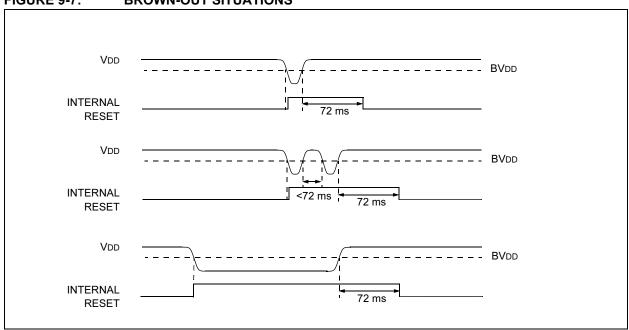

#### 9.4.4 BROWN-OUT RESET (BOR)

The PIC16C62X members have on-chip Brown-out Reset circuitry. A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V refer to VBOR parameter D005 (VBOR) for greater than parameter (TBOR) in Table 12-5. The brown-out situation will RESET the chip. A RESET won't occur if VDD falls below 4.0V for less than parameter (TBOR).

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 9-7 shows typical Brown-out situations.

#### FIGURE 9-7: BROWN-OUT SITUATIONS

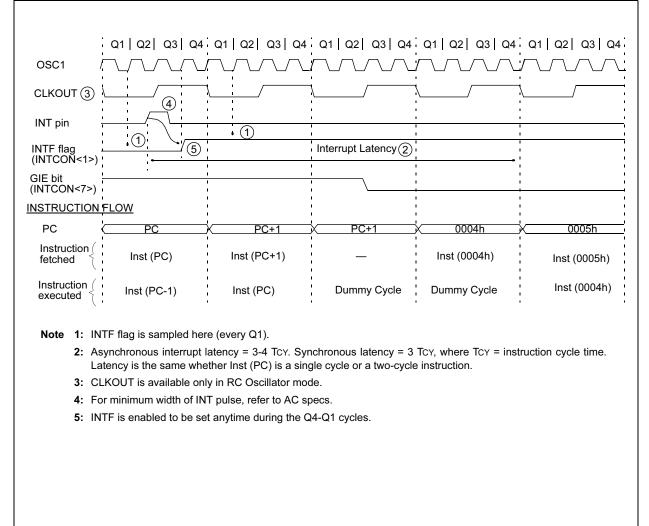

#### 9.5.1 RB0/INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered, either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP and Figure 9-18 for timing of wakeup from SLEEP through RB0/INT interrupt.

#### 9.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 6.0.

#### 9.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

| Note: | If a change on the I/O pin should occur   |

|-------|-------------------------------------------|

|       | when the read operation is being executed |

|       | (start of the Q2 cycle), then the RBIF    |

|       | interrupt flag may not get set.           |

#### 9.5.4 COMPARATOR INTERRUPT

See Section 7.6 for complete description of comparator interrupts.

#### FIGURE 9-16: INT PIN INTERRUPT TIMING

### 9.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs with no external circuitry drawing current from the I/O pin and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated      |

|-------|------------------------------------------------|

|       | by a WDT time-out does not drive MCLR pin low. |

|       |                                                |

#### 9.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device RESET. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. PD bit, which is set on power-up, is cleared when SLEEP is invoked. TO bit is cleared if WDT wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction after the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

**Note:** If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from SLEEP. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes up from SLEEP, regardless of the source of wake-up.

| Q1 Q2 Q                  | 3 Q4 Q1 Q2 Q3 Q4 Q | Q1                    | Q1 Q2 Q3 Q4      | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 0    | Q1 Q2 Q3 Q4 |

|--------------------------|--------------------|-----------------------|------------------|-------------|------------------|-------------|

| OSC1 //////              |                    | AAAAA                 |                  |             |                  |             |

| CLKOUT(4)                |                    | Tost(2)               | <u> </u>         |             | \ <u>`</u>       |             |

| INT pin                  | 1 I                |                       | 1<br>1           |             | 1                |             |

| NTF flag                 |                    |                       | Interrupt Latend | SV.         |                  |             |

| INTCON<1>)               |                    | <del>≉</del>          | (Note 2)         | ,           |                  |             |

| GIE bit<br>INTCON<7>)    |                    | Processor in<br>SLEEP | 1                |             |                  |             |

| INSTRUCTION FLOW         |                    |                       | 1<br>1<br>1      |             | 1                |             |

| PC X PC                  | <u>Υ PC+1 Χ</u>    | PC+2                  | X PC+2           | PC + 2      | <u>χ 0004h χ</u> | 0005h       |

| Instruction { Inst(PC) = | SLEEP Inst(PC + 1) |                       | Inst(PC + 2)     |             | Inst(0004h)      | Inst(0005h) |

| Instruction Inst(PC      | - 1) SLEEP         |                       | Inst(PC + 1)     | Dummy cycle | Dummy cycle      | Inst(0004h) |

#### FIGURE 9-18: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**3:** GIE = '1' assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these Osc modes, but shown here for timing reference.

## PIC16C62X

| CLRW                                                                               | Clear W                                                                                                                                                                                                                                                                                                                                                                                             | COMF                                                                                          | Complement f                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                            | [ <i>label</i> ] CLRW                                                                                                                                                                                                                                                                                                                                                                               | Syntax:                                                                                       | [ <i>label</i> ] COMF f,d                                                                                                                                                                                                                                                                           |

| Operands:                                                                          | None                                                                                                                                                                                                                                                                                                                                                                                                | Operands:                                                                                     | $0 \leq f \leq 127$                                                                                                                                                                                                                                                                                 |

| Operation:                                                                         | $00h \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                               |                                                                                               | d ∈ [0,1]                                                                                                                                                                                                                                                                                           |

|                                                                                    | $1 \rightarrow Z$                                                                                                                                                                                                                                                                                                                                                                                   | Operation:                                                                                    | $(\bar{f}) \rightarrow (dest)$                                                                                                                                                                                                                                                                      |

| Status Affected:                                                                   | Z                                                                                                                                                                                                                                                                                                                                                                                                   | Status Affected:                                                                              | Z                                                                                                                                                                                                                                                                                                   |

| Encoding:                                                                          | 00 0001 0000 0011                                                                                                                                                                                                                                                                                                                                                                                   | Encoding:                                                                                     | 00 1001 dfff ffff                                                                                                                                                                                                                                                                                   |

| Description:                                                                       | W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                         | Description:                                                                                  | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the                                                                                                                                                                                       |

| Words:                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                               | result is stored back in register 'f'.                                                                                                                                                                                                                                                              |

| Cycles:                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                   | Words:                                                                                        | 1                                                                                                                                                                                                                                                                                                   |

| Example                                                                            | CLRW                                                                                                                                                                                                                                                                                                                                                                                                | Cycles:                                                                                       | 1                                                                                                                                                                                                                                                                                                   |

|                                                                                    | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                  | Example                                                                                       | COMF REG1,0                                                                                                                                                                                                                                                                                         |

|                                                                                    | W = 0x5A<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                       | Example                                                                                       | Before Instruction                                                                                                                                                                                                                                                                                  |

|                                                                                    | W = 0x00 $Z = 1$                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                               | REG1 = 0x13 After Instruction $REG1 = 0x13$ $W = 0xEC$                                                                                                                                                                                                                                              |

| CLRWDT                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                                                                                                                                                                                                                                                                                     |

| Syntax:                                                                            | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               |                                                                                                                                                                                                                                                                                                     |

|                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                     | DECE                                                                                          | Decrement f                                                                                                                                                                                                                                                                                         |

| Operands:                                                                          | None                                                                                                                                                                                                                                                                                                                                                                                                | DECF<br>Syntax:                                                                               | Decrement f                                                                                                                                                                                                                                                                                         |

| -                                                                                  | None $00h \rightarrow WDT$                                                                                                                                                                                                                                                                                                                                                                          | Syntax:                                                                                       | [label] DECF f,d                                                                                                                                                                                                                                                                                    |

| Operands:                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow \underline{WD}T$ prescaler,                                                                                                                                                                                                                                                                                                                         | _                                                                                             |                                                                                                                                                                                                                                                                                                     |

| Operands:                                                                          | None $00h \rightarrow WDT$                                                                                                                                                                                                                                                                                                                                                                          | Syntax:                                                                                       | [ <i>label</i> ] DECF f,d<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                                            |

| Operands:                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow TO$                                                                                                                                                                                                                                                                                                               | Syntax:<br>Operands:                                                                          | [ <i>label</i> ] DECF f,d<br>0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                                                                               |

| Operands:<br>Operation:                                                            | None<br>$00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$                                                                                                                                                                                                                                                                    | Syntax:<br>Operands:<br>Operation:                                                            | $\begin{bmatrix} label \end{bmatrix} DECF f,d$<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest)                                                                                                                                                                                |

| Operands:<br>Operation:<br>Status Affected:                                        | None<br>$00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow PD$ $\overline{TO, PD}$                                                                                                                                                                                                                                                           | Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                        | [ <i>label</i> ] DECF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) - 1 → (dest)<br>Z                                                                                                                                                                                                            |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | None<br>$00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow PD$ $\overline{TO, PD}$ $00  0000  0110  0100$ CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>pres <u>caler</u> of the WDT. STATUS                                                                                                                        | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011 \qquad dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is                              |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | None<br>$\begin{array}{c} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow PD \\ \hline \overline{TO}, \overline{PD} \\ \hline \hline 00 & 0000 & 0110 & 0100 \\ \hline \\ CLRWDT \text{ instruction resets the} \\ Watchdog Timer. It also resets the \\ prescaler of the WDT. STATUS \\ bits TO and PD are set. \\ \hline \end{array}$ | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011 \qquad dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | None<br>$\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow PD \\ \hline TO, PD \\ \hline 00 & 0000 & 0110 & 0100 \\ \hline \end{array}$ CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. STATUS<br>bits TO and PD are set.<br>1                                              | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011  dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. 1     |

## 11.20 PICDEM 18R PIC18C601/801 Demonstration Board

The PICDEM 18R demonstration board serves to assist development of the PIC18C601/801 family of Microchip microcontrollers. It provides hardware implementation of both 8-bit Multiplexed/De-multiplexed and 16-bit Memory modes. The board includes 2 Mb external FLASH memory and 128 Kb SRAM memory, as well as serial EEPROM, allowing access to the wide range of memory types supported by the PIC18C601/801.

## 11.21 PICDEM LIN PIC16C43X Demonstration Board

The powerful LIN hardware and software kit includes a series of boards and three PICmicro microcontrollers. The small footprint PIC16C432 and PIC16C433 are used as slaves in the LIN communication and feature on-board LIN transceivers. A PIC16F874 FLASH microcontroller serves as the master. All three micro-controllers are programmed with firmware to provide LIN bus communication.

## 11.22 PICkit<sup>™</sup> 1 FLASH Starter Kit

A complete "development system in a box", the PICkit FLASH Starter Kit includes a convenient multi-section board for programming, evaluation, and development of 8/14-pin FLASH PIC<sup>®</sup> microcontrollers. Powered via USB, the board operates under a simple Windows GUI. The PICkit 1 Starter Kit includes the user's guide (on CD ROM), PICkit 1 tutorial software and code for various applications. Also included are MPLAB<sup>®</sup> IDE (Integrated Development Environment) software, software and hardware "Tips 'n Tricks for 8-pin FLASH PIC<sup>®</sup> Microcontrollers" Handbook and a USB Interface Cable. Supports all current 8/14-pin FLASH PIC microcontrollers, as well as many future planned devices.

## 11.23 PICDEM USB PIC16C7X5 Demonstration Board

The PICDEM USB Demonstration Board shows off the capabilities of the PIC16C745 and PIC16C765 USB microcontrollers. This board provides the basis for future USB products.

## 11.24 Evaluation and Programming Tools

In addition to the PICDEM series of circuits, Microchip has a line of evaluation kits and demonstration software for these products.

- KEELOQ evaluation and programming tools for Microchip's HCS Secure Data Products

- CAN developers kit for automotive network applications

- Analog design boards and filter design software

- PowerSmart battery charging evaluation/ calibration kits

- IrDA<sup>®</sup> development kit

- microID development and rfLab<sup>™</sup> development software

- SEEVAL<sup>®</sup> designer kit for memory evaluation and endurance calculations

- PICDEM MSC demo boards for Switching mode power supply, high power IR driver, delta sigma ADC, and flow rate sensor

Check the Microchip web page and the latest Product Line Card for the complete list of demonstration and evaluation kits.

## 12.0 ELECTRICAL SPECIFICATIONS

#### Absolute Maximum Ratings †

| Ambient Temperature under bias                                                                                                                    | 40° to +125°C     |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|

| Storage Temperature                                                                                                                               | 65° to +150°C     |  |  |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                                                      | 0.6V to VDD +0.6V |  |  |

| Voltage on VDD with respect to Vss                                                                                                                | 0 to +7.5V        |  |  |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                      | 0 to +14V         |  |  |

| Voltage on RA4 with respect to Vss                                                                                                                |                   |  |  |

| Total power Dissipation (Note 1)                                                                                                                  | 1.0W              |  |  |

| Maximum Current out of Vss pin                                                                                                                    | 300 mA            |  |  |

| Maximum Current into VDD pin                                                                                                                      | 250 mA            |  |  |

| Input Clamp Current, Iк (Vi <0 or Vi> VDD)                                                                                                        | ±20 mA            |  |  |

| Output Clamp Current, Iок (Vo <0 or Vo>VDD)                                                                                                       | ±20 mA            |  |  |

| Maximum Output Current sunk by any I/O pin                                                                                                        | 25 mA             |  |  |

| Maximum Output Current sourced by any I/O pin                                                                                                     | 25 mA             |  |  |

| Maximum Current sunk by PORTA and PORTB                                                                                                           | 200 mA            |  |  |

| Maximum Current sourced by PORTA and PORTB                                                                                                        | 200 mA            |  |  |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD-VOH) x IOH} + $\Sigma$ (VOI x IOL). |                   |  |  |

2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latchup. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

**† NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# PIC16C62X

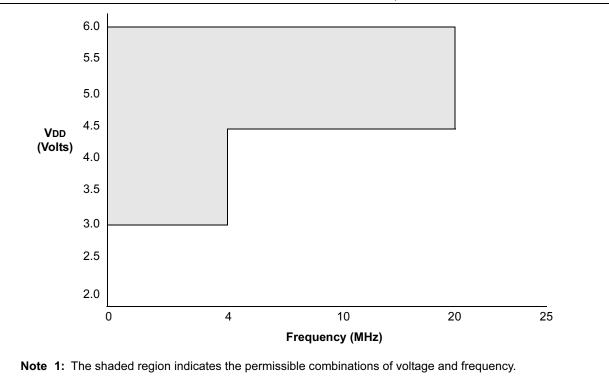

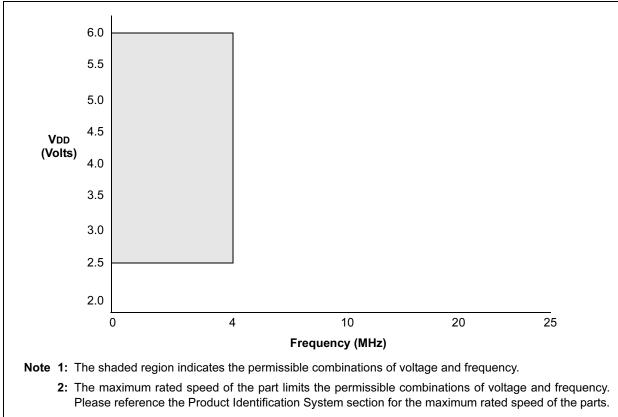

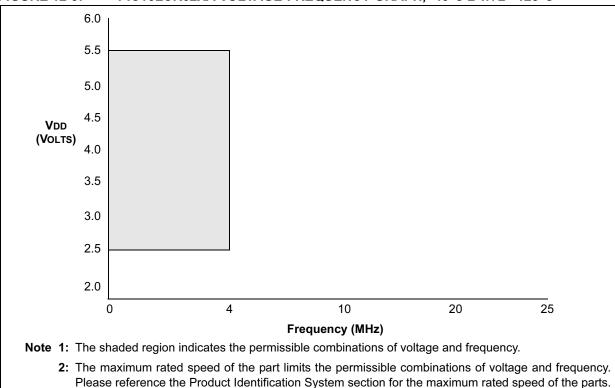

**2**: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

# PIC16C62X

#### 12.4 DC Characteristics: PIC16C62X/C62XA/CR62XA (Commercial, Industrial, Extended) PIC16LC62X/LC62XA/LCR62XA (Commercial, Industrial, Extended) (CONT.)

| PIC16C62X/C62XA/CR62XA    |           |                                            | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq$ Ta $\leq$ +85°C for industrial and $0^{\circ}$ C $\leq$ Ta $\leq$ +70°C for commercial and $-40^{\circ}$ C $\leq$ Ta $\leq$ +125°C for extended |                                                                                                                                                                                                                                                                       |             |        |                                                                                                |  |  |

|---------------------------|-----------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|------------------------------------------------------------------------------------------------|--|--|

| PIC16LC62X/LC62XA/LCR62XA |           |                                            |                                                                                                                                                                                                                                                     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq TA \leq +85^{\circ}$ C for industrial and $0^{\circ}$ C $\leq TA \leq +70^{\circ}$ C for commercial and $-40^{\circ}$ C $\leq TA \leq +125^{\circ}$ C for extended |             |        |                                                                                                |  |  |

| Param.<br>No.             | Sym       | Characteristic                             | Min                                                                                                                                                                                                                                                 | Тур†                                                                                                                                                                                                                                                                  | Мах         | Units  | Conditions                                                                                     |  |  |

|                           | Vol       | Output Low Voltage                         |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                       |             |        |                                                                                                |  |  |

| D080                      |           | I/O ports                                  | _                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                     | 0.6         | V      | IOL = 8.5 mA, VDD = 4.5V, -40° to +85°C                                                        |  |  |

|                           |           |                                            | _                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                     | 0.6         | V      | IOL = 7.0 mA, VDD = 4.5V, +125°C                                                               |  |  |

| D083                      |           | OSC2/CLKOUT (RC only)                      | _                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                     | 0.6         | V      | IOL = 1.6 mA, VDD = 4.5V, -40° to +85°C                                                        |  |  |

|                           |           |                                            | _                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                     | 0.6         | V      | IOL = 1.2 mA, VDD = 4.5V, +125°C                                                               |  |  |

|                           | Voн       | Output High Voltage <sup>(3)</sup>         | 1                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                       |             |        |                                                                                                |  |  |

| D090                      |           | I/O ports (Except RA4)                     | Vdd-0.7                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                     | _           | v      | ІОН = -3.0 mA, VDD = 4.5V, -40° to +85°С                                                       |  |  |

|                           |           |                                            | VDD-0.7                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                     | _           | V      | IOH = -2.5 mA, VDD = 4.5V, +125°C                                                              |  |  |

| D092                      |           | OSC2/CLKOUT (RC only)                      | VDD-0.7                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                     | -           | V      | IOH = -1.3 mA, VDD = 4.5V, -40° to +85°С                                                       |  |  |