Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 96 x 8                                                                     |

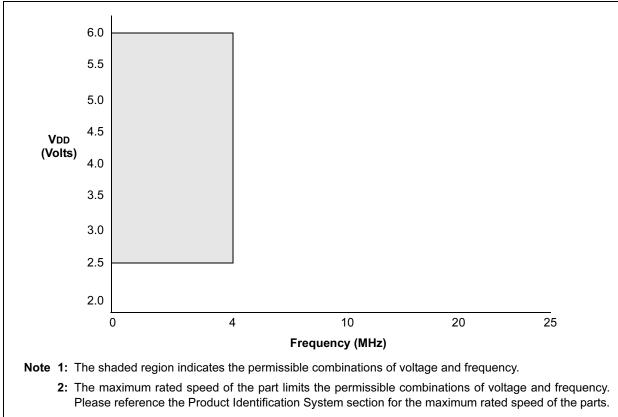

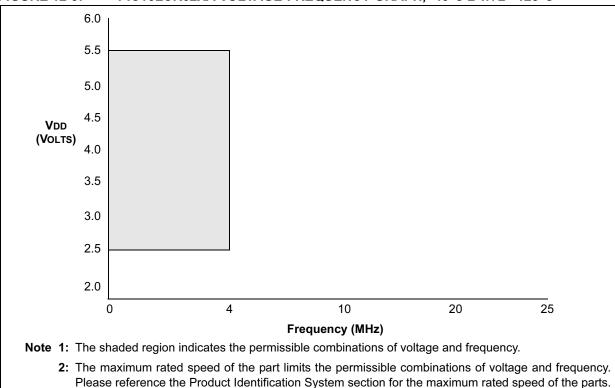

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

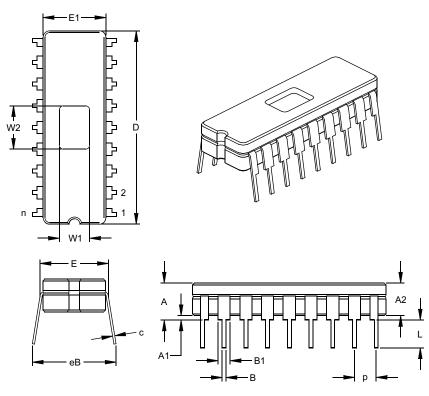

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c620a-04e-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

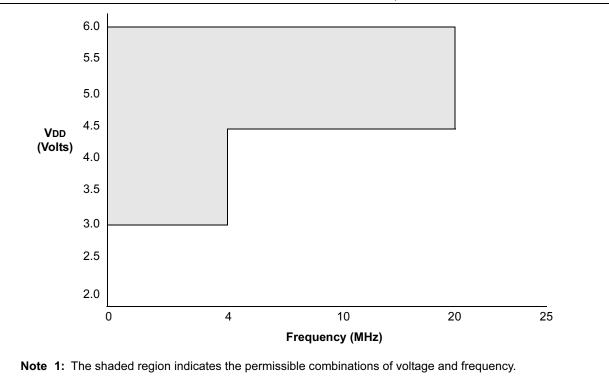

|             |                                        | PIC16C620 <sup>(3)</sup>            | PIC16C620A <sup>(1)(4)</sup>        | PIC16CR620A <sup>(2)</sup>          | PIC16C621 <sup>(3)</sup>            | PIC16C621A <sup>(1)(4)</sup>        | PIC16C622 <sup>(3)</sup>            | PIC16C622A <sup>(1)(4)</sup>        |

|-------------|----------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz)   | 20                                  | 40                                  | 20                                  | 20                                  | 40                                  | 20                                  | 40                                  |

| Memory      | EPROM Program<br>Memory<br>(x14 words) | 512                                 | 512                                 | 512                                 | 1K                                  | 1K                                  | 2К                                  | 2К                                  |

|             | Data Memory (bytes)                    | 80                                  | 96                                  | 96                                  | 80                                  | 96                                  | 128                                 | 128                                 |

| Peripherals | Timer Module(s)                        | TMR0                                | TMR0                                | TMRO                                | TMR0                                | TMR0                                | TMR0                                | TMR0                                |

|             | Comparators(s)                         | 2                                   | 2                                   | 2                                   | 2                                   | 2                                   | 2                                   | 2                                   |

|             | Internal Reference<br>Voltage          | Yes                                 |

| Features    | Interrupt Sources                      | 4                                   | 4                                   | 4                                   | 4                                   | 4                                   | 4                                   | 4                                   |

|             | I/O Pins                               | 13                                  | 13                                  | 13                                  | 13                                  | 13                                  | 13                                  | 13                                  |

|             | Voltage Range (Volts)                  | 2.5-6.0                             | 2.7-5.5                             | 2.5-5.5                             | 2.5-6.0                             | 2.7-5.5                             | 2.5-6.0                             | 2.7-5.5                             |

|             | Brown-out Reset                        | Yes                                 |

|             | Packages                               | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

### TABLE 1-1: PIC16C62X FAMILY OF DEVICES

All PICmicro<sup>®</sup> Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C62X Family devices use serial programming with clock pin RB6 and data pin RB7.

**Note 1:** If you change from this device to another device, please verify oscillator characteristics in your application.

2: For ROM parts, operation from 2.0V - 2.5V will require the PIC16LCR62XA parts.

**3:** For OTP parts, operation from 2.5V - 3.0V will require the PIC16LC62X part.

4: For OTP parts, operation from 2.7V - 3.0V will require the PIC16LC62XA part.

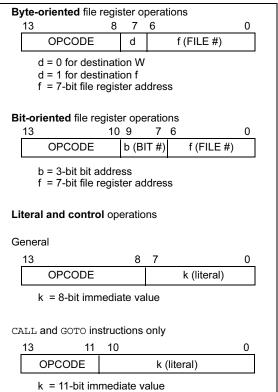

## 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C62X uses a Harvard architecture, in which, program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture, where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C620(A) and PIC16CR620A address 512 x 14 on-chip program memory. The PIC16C621(A) addresses 1K x 14 program memory. The PIC16C622(A) addresses 2K x 14 program memory. All program memory is internal.

The PIC16C62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16C62X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

### 4.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

| E PE<br>Global Internables all un<br>isables all in<br>Peripheral<br>nables all p<br>TMR0 Ove<br>nables the T<br>isables the | Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En                                                    | e bit<br>heral interrupt<br>pts                                                                                         | R/W-0<br>RBIE                                                                                                                                                                                                     | R/W-0<br>T0IF                                                                                                                                                                                                                                | R/W-0<br>INTF                                                                                                                                                                                                            | R/W-x<br>RBIF<br>bit 0                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          | bit 0                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| sables all in<br>Peripheral<br>nables all un<br>sables all p<br>TMR0 Ove<br>nables the T<br>isables the                      | nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                    | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| nables all u<br>sables all p<br>TMR0 Ove<br>nables the<br>sables the                                                         | n-masked periph<br>peripheral interru<br>rflow Interrupt Er<br>TMR0 interrupt                                                      | neral interrupt<br>pts                                                                                                  | S                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| sables all p<br>TMR0 Ove<br>nables the<br>sables the                                                                         | peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                        | pts                                                                                                                     | S                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| TMR0 Ove<br>nables the<br>sables the                                                                                         | rflow Interrupt Er<br>TMR0 interrupt                                                                                               |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| nables the<br>isables the                                                                                                    | TMR0 interrupt                                                                                                                     | nable bit                                                                                                               |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| sables the                                                                                                                   |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                                                                                                                              | I MRU interrupt                                                                                                                    |                                                                                                                         | 1 = Enables the TMR0 interrupt                                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                                                                                                                              |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| INTE: RB0/INT External Interrupt Enable bit                                                                                  |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 1 = Enables the RB0/INT external interrupt<br>0 = Disables the RB0/INT external interrupt                                    |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| <b>RBIE</b> : RB Port Change Interrupt Enable bit                                                                            |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                                                                                                                              | RB port change i                                                                                                                   |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                                                                                                                              | RB port change                                                                                                                     | •                                                                                                                       |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| TMR0 Ove                                                                                                                     | rflow Interrupt Fl                                                                                                                 | ag bit                                                                                                                  |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 1 = TMR0 register has overflowed (must be cleared in software)                                                               |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| MR0 registe                                                                                                                  | er did not overflov                                                                                                                | W                                                                                                                       |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| INTF: RB0/INT External Interrupt Flag bit                                                                                    |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                                                                                                                              |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   | red in softwa                                                                                                                                                                                                                                | are)                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| RB Port Cl                                                                                                                   | hange Interrupt F                                                                                                                  | Flag bit                                                                                                                |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 'hen at leas                                                                                                                 |                                                                                                                                    | •                                                                                                                       | -                                                                                                                                                                                                                 | (must be cle                                                                                                                                                                                                                                 | ared in softw                                                                                                                                                                                                            | ware)                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|                                                                                                                              | ne RB0/INT<br>ne RB0/INT<br>RB Port C<br>hen at leas                                                                               | ne RB0/INT external interrune<br>RB0/INT external interrun<br>RB Port Change Interrupt I<br>hen at least one of the RB< | ne RB0/INT external interrupt occurred (m<br>ne RB0/INT external interrupt did not occ<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins cha<br>one of the RB<7:4> pins have changed s | ne RB0/INT external interrupt occurred (must be clea<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state<br>one of the RB<7:4> pins have changed state | ne RB0/INT external interrupt occurred (must be cleared in softwa<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cle | ne RB0/INT external interrupt occurred (must be cleared in software)<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cleared in softwore)<br>one of the RB<7:4> pins have changed state |  |  |  |  |  |  |  |

| REGISTER 4-3: | INTCON REGISTER (ADDRESS 0BH OR 8BH) |

|---------------|--------------------------------------|

|---------------|--------------------------------------|

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 4.2.2.4 PIE1 Register

This register contains the individual enable bit for the comparator interrupt.

| <b>REGISTER 4-4:</b> | PIE1 REGISTER (ADDRESS 8CH)                                                                                                                       |                                   |          |  |  |   |   |   |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------|--|--|---|---|---|--|--|--|--|

|                      | U-0                                                                                                                                               | U-0 R/W-0 U-0 U-0 U-0 U-0 U-0 U-0 |          |  |  |   |   |   |  |  |  |  |

|                      |                                                                                                                                                   | CMIE                              | _        |  |  | — | _ | — |  |  |  |  |

|                      | bit 7                                                                                                                                             | bit 7 bit 0                       |          |  |  |   |   |   |  |  |  |  |

| bit 7                | Unimpleme                                                                                                                                         | Unimplemented: Read as '0'        |          |  |  |   |   |   |  |  |  |  |

| bit 6                | <b>CMIE</b> : Comparator Interrupt Enable bit<br>1 = Enables the Comparator interrupt<br>0 = Disables the Comparator interrupt                    |                                   |          |  |  |   |   |   |  |  |  |  |

| bit 5-0              | Unimpleme                                                                                                                                         | nted: Read                        | d as '0' |  |  |   |   |   |  |  |  |  |

|                      | Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'- n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown |                                   |          |  |  |   |   |   |  |  |  |  |

### 4.2.2.5 PIR1 Register

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of |

|-------|--------------------------------------------------------------------------------------------|

|       | its corresponding enable bit or the global<br>enable bit, GIE (INTCON<7>). User            |

|       | software should ensure the appropriate                                                     |

|       | interrupt flag bits are clear prior to enabling                                            |

|       | an interrupt.                                                                              |

### REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

| ER 4-5: | PIRT REGI                            | PIRT REGISTER (ADDRESS UCH) |          |              |              |           |                |        |  |  |  |  |  |

|---------|--------------------------------------|-----------------------------|----------|--------------|--------------|-----------|----------------|--------|--|--|--|--|--|

|         | U-0                                  | R/W-0                       | U-0      | U-0          | U-0          | U-0       | U-0            | U-0    |  |  |  |  |  |

|         |                                      | CMIF                        |          | —            | _            |           |                |        |  |  |  |  |  |

|         | bit 7                                |                             |          |              |              |           |                | bit 0  |  |  |  |  |  |

|         |                                      |                             |          |              |              |           |                |        |  |  |  |  |  |

| bit 7   | Unimplemented: Read as '0'           |                             |          |              |              |           |                |        |  |  |  |  |  |

| bit 6   | CMIF: Comparator Interrupt Flag bit  |                             |          |              |              |           |                |        |  |  |  |  |  |

|         | 1 = Comparator input has changed     |                             |          |              |              |           |                |        |  |  |  |  |  |

|         | 0 = Comparator input has not changed |                             |          |              |              |           |                |        |  |  |  |  |  |

| bit 5-0 | Unimpleme                            | ented: Rea                  | d as '0' |              |              |           |                |        |  |  |  |  |  |

|         |                                      |                             |          |              |              |           |                |        |  |  |  |  |  |

|         | Legend:                              |                             |          |              |              |           |                |        |  |  |  |  |  |

|         | R = Readab                           | ole bit                     | W = W    | /ritable bit | U = Unim     | plemented | bit, read as ' | 0'     |  |  |  |  |  |

|         | - n = Value                          | at POR                      | '1' = B  | it is set    | '0' = Bit is | s cleared | x = Bit is u   | nknown |  |  |  |  |  |

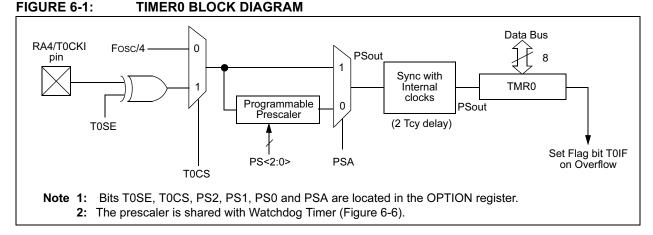

### 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- · Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

### 6.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP, since the timer is shut off during SLEEP. See Figure 6-4 for Timer0 interrupt timing.

### FIGURE 6-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

| (Program<br>Counter) | ( PC-1      | ) PC        | ( <u>PC+1</u> )        | PC+2                   | <u>PC+3</u> χ          | PC+4                   | PC+5 χ                     | PC+6                     |

|----------------------|-------------|-------------|------------------------|------------------------|------------------------|------------------------|----------------------------|--------------------------|

| Instruction<br>Fetch |             | MOVWF TMR   | 0MOVF TMR0,V           | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W                | 1                        |

|                      | i.          | 1           |                        |                        | i                      |                        | i                          |                          |

| TMR0                 | то х        | T0+1 )(     | T0+2 X                 | 1                      | NT0                    |                        | NT0+1 \                    | NT0+2 )                  |

| Instruction          | 1<br>1<br>1 | 1<br>1<br>1 | <b></b>                | <b>≜</b>               | <b>≜</b>               | <b>†</b>               | <b>†</b>                   | <b>≜</b>                 |

| Executed             | 1           | 1           | Write TMR0<br>executed | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1 | Read TMR0<br>reads NT0 + |

### 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-Chip Voltage Reference (Section 8.0) can also be an input to the comparators.

The CMCON register, shown in Register 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-1.

### REGISTER 7-1: CMCON REGISTER (ADDRESS 1Fh)

|         |                            |                                 | <b>(</b> | ,   |       |       |       |       |  |  |  |  |  |

|---------|----------------------------|---------------------------------|----------|-----|-------|-------|-------|-------|--|--|--|--|--|

|         | R-0                        | R-0                             | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|         | C2OUT                      | C10UT                           | —        | —   | CIS   | CM2   | CM1   | CM0   |  |  |  |  |  |

|         | bit 7                      |                                 |          |     |       |       |       | bit 0 |  |  |  |  |  |

|         |                            |                                 |          |     |       |       |       |       |  |  |  |  |  |

| bit 7   | <b>C2OUT</b> : Co          | C2OUT: Comparator 2 output      |          |     |       |       |       |       |  |  |  |  |  |

|         | 1 = C2 VIN                 | 1 = C2 VIN + > C2 VIN -         |          |     |       |       |       |       |  |  |  |  |  |

|         | 0 = C2 VIN                 | 0 = C2 VIN + < C2 VIN -         |          |     |       |       |       |       |  |  |  |  |  |

| bit 6   | <b>C1OUT</b> : Co          | C1OUT: Comparator 1 output      |          |     |       |       |       |       |  |  |  |  |  |

|         | 1 = C1 VIN                 | 1 = C1 Vin + > C1 Vin -         |          |     |       |       |       |       |  |  |  |  |  |

|         | 0 = C1 VIN+ < C1 VIN-      |                                 |          |     |       |       |       |       |  |  |  |  |  |

| bit 5-4 | Unimplemented: Read as '0' |                                 |          |     |       |       |       |       |  |  |  |  |  |

| bit 3   | CIS: Comp                  | arator Input                    | Switch   |     |       |       |       |       |  |  |  |  |  |

|         | When CM<                   | <2:0>: = 001                    | :        |     |       |       |       |       |  |  |  |  |  |

|         | 1 = C1 VIN-                | - connects to                   | o RA3    |     |       |       |       |       |  |  |  |  |  |

|         | 0 = C1 VIN                 | - connects to                   | o RA0    |     |       |       |       |       |  |  |  |  |  |

|         | When CM<                   | <2:0> = 010:                    |          |     |       |       |       |       |  |  |  |  |  |

|         |                            | <ul> <li>connects to</li> </ul> |          |     |       |       |       |       |  |  |  |  |  |

|         |                            | I- connects t                   |          |     |       |       |       |       |  |  |  |  |  |

|         |                            | - connects to                   |          |     |       |       |       |       |  |  |  |  |  |

|         | C2 VIN                     | I- connects t                   | 0 RA1    |     |       |       |       |       |  |  |  |  |  |

| bit 2-0 | CM<2:0>:                   | Comparator                      | mode.    |     |       |       |       |       |  |  |  |  |  |

|         |                            |                                 |          |     |       |       |       |       |  |  |  |  |  |

|         | Legend:                    |                                 |          |     |       |       |       |       |  |  |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 9.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

### REGISTER 9-1: CONFIGURATION WORD (ADDRESS 2007h)

| CP1              | CP0 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CP1                                                                                                                                    | CP0 <sup>(2)</sup>                                                                                                                                        | CP1                                                                                                                                                                | CP0 <sup>(2)</sup>                                                                                                         |                                                               | BODEN                     | CP1     | CP0 <sup>(2)</sup> | PWRTE       | WDTE      | F0SC1     | F0SC0 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------|---------|--------------------|-------------|-----------|-----------|-------|

| bit 13           | ļ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <u> </u>                                                                                                                               | ļļ                                                                                                                                                        |                                                                                                                                                                    | ļ                                                                                                                          |                                                               | <u> </u>                  | <u></u> | <u>I</u>           | <u></u>     | <u> </u>  | ļ         | bit 0 |

| bit 13-8<br>5-4: | Cod<br>11 =<br>10 =<br>01 =<br>00 =<br>Cod<br>11 =<br>00 =<br>00 =<br>Cod<br>11 =<br>10 =<br>01 =<br>01 =<br>01 =<br>01 =<br>01 =<br>01 =<br>01 =<br>00 =<br>01 =<br>00 =<br>01 =<br>00 | e protec<br>= Progra<br>= 0400h<br>= 0200h<br>= 0200h<br>= 0000h<br>= Progra<br>= 0200h<br>= 0000h<br>= protec<br>= Progra<br>= Progra | ode prote<br>ction for 2<br>m memo<br>-07FFh c<br>-07FFh c<br>-07FFh c<br>-07FFh c<br>-03FFh c<br>-03FFh c<br>-03FFh c<br>ction for 0<br>m memo<br>m memo | 2K progr<br>ry code<br>ode pro<br>ode pro<br>ode pro<br>ry code<br>ry code<br>ode pro<br>ode pro<br>ode pro<br>ode pro<br>ode pro<br>ode pro<br>ry code<br>ry code | am mem<br>protectic<br>tected<br>tected<br>tected<br>protectic<br>protectic<br>tected<br>gram me<br>protectic<br>protectic | ory<br>on off<br>on off<br>on off<br>mory<br>on off<br>on off |                           |         |                    |             |           |           |       |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul><li>01 = Program memory code protection off</li><li>00 = 0000h-01FFh code protected</li></ul>                                      |                                                                                                                                                           |                                                                                                                                                                    |                                                                                                                            |                                                               |                           |         |                    |             |           |           |       |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Unimplemented: Read as '0'                                                                                                             |                                                                                                                                                           |                                                                                                                                                                    |                                                                                                                            |                                                               |                           |         |                    |             |           |           |       |