Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 96 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

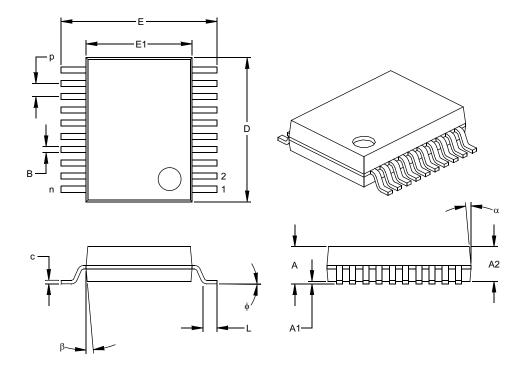

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c620a-20-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

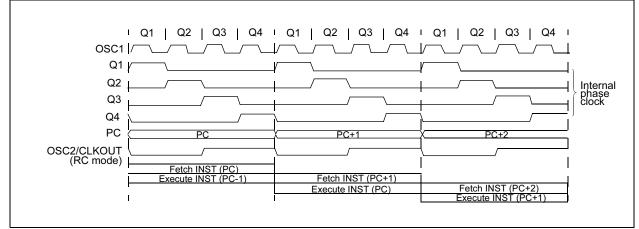

## 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

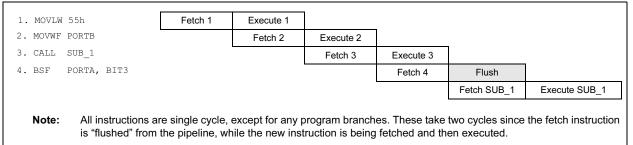

## 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

### 4.2.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uuluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any STATUS bit. For other instructions not affecting any STATUS bits, see the "Instruction Set Summary".

- Note 1: The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16C62X and should be programmed as '0'. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The <u>C and DC bits</u> operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

### REGISTER 4-1: STATUS REGISTER (ADDRESS 03H OR 83H)

|         | Reserved                                                                                           | Reserved                           | R/W-0          | R-1            | R-1            | R/W-x        | R/W-x        | R/W-x          |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|----------------|--------------|--------------|----------------|--|--|--|--|

|         | IRP                                                                                                | RP1                                | RP0            | TO             | PD             | Z            | DC           | С              |  |  |  |  |

|         | bit 7                                                                                              |                                    |                |                |                |              |              | bit 0          |  |  |  |  |

|         |                                                                                                    |                                    |                |                |                |              |              |                |  |  |  |  |

| bit 7   | -                                                                                                  | ter Bank Sel                       | -              | d for indirect | addressing     | )            |              |                |  |  |  |  |

|         | 1 = Bank 2, 3 (100h - 1FFh)<br>0 = Bank 0, 1 (00h - FFh)                                           |                                    |                |                |                |              |              |                |  |  |  |  |

|         | The IRP bit is reserved on the PIC16C62X; always maintain this bit clear.                          |                                    |                |                |                |              |              |                |  |  |  |  |

| bit 6-5 | RP<1:0>: Register Bank Select bits (used for direct addressing)                                    |                                    |                |                |                |              |              |                |  |  |  |  |

|         |                                                                                                    | 1 (80h - FFh                       |                |                |                |              |              |                |  |  |  |  |

|         |                                                                                                    | 0 (00h - 7Fh                       |                |                |                |              |              |                |  |  |  |  |

|         | Each bank is 128 bytes. The RP1 bit is reserved on the PIC16C62X; always maintain this t<br>clear. |                                    |                |                |                |              |              |                |  |  |  |  |

| bit 4   | TO: Time-c                                                                                         | out bit                            |                |                |                |              |              |                |  |  |  |  |

|         |                                                                                                    | ower-up, CLI                       | RWDT instruc   | ction. or SLE  | EP instruction | on           |              |                |  |  |  |  |

|         |                                                                                                    | time-out oc                        |                | ,              |                |              |              |                |  |  |  |  |

| bit 3   | PD: Power                                                                                          | -down bit                          |                |                |                |              |              |                |  |  |  |  |

|         | -                                                                                                  | ower-up or b<br>cution of the      | -              |                | n              |              |              |                |  |  |  |  |

| bit 2   | Z: Zero bit                                                                                        |                                    |                |                |                |              |              |                |  |  |  |  |

|         |                                                                                                    | sult of an arit<br>sult of an arit |                |                |                | )            |              |                |  |  |  |  |

| bit 1   |                                                                                                    | arry/borrow b                      |                | • •            |                |              | )(for borrow | the polarity   |  |  |  |  |

|         | is reversed                                                                                        | -                                  | ζ, ,           |                | ·              |              |              |                |  |  |  |  |

|         |                                                                                                    | -out from the                      |                |                |                | rred         |              |                |  |  |  |  |

|         |                                                                                                    | ry-out from th                     |                |                |                |              |              |                |  |  |  |  |

| bit 0   | •                                                                                                  | orrow bit (AD                      |                |                |                |              |              |                |  |  |  |  |

|         | •                                                                                                  | -out from the<br>ry-out from th    | -              |                |                |              |              |                |  |  |  |  |

|         | Note:                                                                                              | For borrow t                       | he polarity i  | s reversed.    | A subtraction  | on is execut | ed by addin  | g the two's    |  |  |  |  |

|         |                                                                                                    | complement                         |                |                |                |              |              | s, this bit is |  |  |  |  |

|         |                                                                                                    | loaded with e                      | either the hig | gh or low or   | der bit of the | source reg   | ister.       |                |  |  |  |  |

|         | Legend:                                                                                            | L. L. 14                           |                |                |                |              | hit on all   | 0              |  |  |  |  |

|         | R = Reada                                                                                          |                                    |                | ritable bit    |                | •            | bit, read as |                |  |  |  |  |

|         | - n = Value                                                                                        | at POR                             | 1′ = Bi        | it is set      | '0' = Bit i    | scleared     | x = Bit is u | nknown         |  |  |  |  |

#### 4.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

| E PE<br>Global Internables all un<br>isables all in<br>Peripheral<br>nables all p<br>TMR0 Ove<br>nables the T<br>isables the | Interrupt Enable<br>n-masked periph<br>peripheral interru                                                                          | e bit<br>heral interrupt<br>pts                                                                                         | R/W-0<br>RBIE                                                                                                                                                                                                     | R/W-0<br>T0IF                                                                                                                                                                                                                                | R/W-0<br>INTF                                                                                                                                                                                                            | R/W-x<br>RBIF<br>bit 0                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          | bit 0                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |  |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| sables all in<br>Peripheral<br>nables all un<br>sables all p<br>TMR0 Ove<br>nables the T<br>isables the                      | nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                    | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the                                                       | n-masked periph<br>peripheral interru<br>rflow Interrupt Er<br>TMR0 interrupt                                                      | neral interrupt<br>pts                                                                                                  | S                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| sables all p<br>TMR0 Ove<br>nables the<br>sables the                                                                         | peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                        | pts                                                                                                                     | S                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| TMR0 Ove<br>nables the<br>sables the                                                                                         | rflow Interrupt Er<br>TMR0 interrupt                                                                                               |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| nables the<br>isables the                                                                                                    | TMR0 interrupt                                                                                                                     | nable bit                                                                                                               |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| sables the                                                                                                                   |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          | T0IE: TMR0 Overflow Interrupt Enable bit                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                              | I MRU interrupt                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                              |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| INTE: RB0/INT External Interrupt Enable bit                                                                                  |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>1 = Enables the RB0/INT external interrupt</li> <li>0 = Disables the RB0/INT external interrupt</li> </ul>          |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                              |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| <b>RBIE</b> : RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt                                |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                              | RB port change                                                                                                                     | •                                                                                                                       |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| TMR0 Ove                                                                                                                     | rflow Interrupt Fl                                                                                                                 | ag bit                                                                                                                  |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| MR0 registe                                                                                                                  | er has overflowed                                                                                                                  | d (must be cle                                                                                                          | eared in soft                                                                                                                                                                                                     | ware)                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| MR0 registe                                                                                                                  | er did not overflov                                                                                                                | W                                                                                                                       |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| INTF: RB0/INT External Interrupt Flag bit                                                                                    |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                              |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                                                                   | red in softwa                                                                                                                                                                                                                                | are)                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| RB Port Cl                                                                                                                   | hange Interrupt F                                                                                                                  | Flag bit                                                                                                                |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| 'hen at leas                                                                                                                 |                                                                                                                                    | •                                                                                                                       | -                                                                                                                                                                                                                 | (must be cle                                                                                                                                                                                                                                 | ared in softw                                                                                                                                                                                                            | ware)                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                              | ne RB0/INT<br>ne RB0/INT<br>RB Port C<br>hen at leas                                                                               | ne RB0/INT external interrune<br>RB0/INT external interrun<br>RB Port Change Interrupt I<br>hen at least one of the RB< | ne RB0/INT external interrupt occurred (m<br>ne RB0/INT external interrupt did not occ<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins cha<br>one of the RB<7:4> pins have changed s | ne RB0/INT external interrupt occurred (must be clea<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state<br>one of the RB<7:4> pins have changed state | ne RB0/INT external interrupt occurred (must be cleared in softwa<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cle | ne RB0/INT external interrupt occurred (must be cleared in software)<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cleared in softwore)<br>one of the RB<7:4> pins have changed state |  |  |  |  |  |  |  |  |  |  |  |  |

| REGISTER 4-3: | INTCON REGISTER (ADDRESS 0BH OR 8BH) |

|---------------|--------------------------------------|

|---------------|--------------------------------------|

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Name    | Bit # | Buffer Type           | Function                                                                                                                |

|---------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0  | TTL/ST <sup>(1)</sup> | Input/output or external interrupt input. Internal software programmable weak pull-up.                                  |

| RB1     | bit1  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB2     | bit2  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB3     | bit3  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB4     | bit4  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB5     | bit5  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB6     | bit6  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock pin. |

| RB7     | bit7  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data pin.  |

### TABLE 5-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h     | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX XXXX       | uuuu uuuu                       |

| 86h     | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h     | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

Legend: u = unchanged, x = unknown

Note 1: Shaded bits are not used by PORTB.

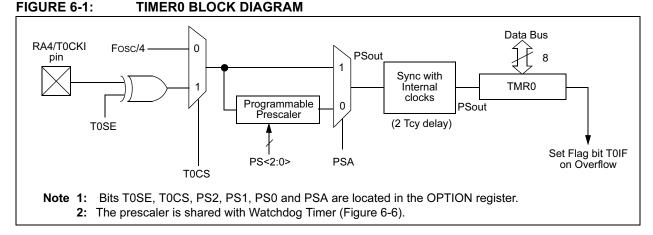

## 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- · Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- · Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

## 6.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP, since the timer is shut off during SLEEP. See Figure 6-4 for Timer0 interrupt timing.

### FIGURE 6-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

| (Program<br>Counter) | ( PC-1      | ) PC        | ( <u>PC+1</u> )        | PC+2                   | <u>PC+3</u> χ          | PC+4                   | PC+5 χ                     | PC+6                     |

|----------------------|-------------|-------------|------------------------|------------------------|------------------------|------------------------|----------------------------|--------------------------|

| Instruction<br>Fetch |             | MOVWF TMR   | 0MOVF TMR0,V           | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W                | 1                        |

|                      | i.          | 1           |                        |                        | i                      |                        | i                          |                          |

| TMR0                 | то х        | T0+1 )(     | T0+2 X                 | 1                      | NT0                    |                        | NT0+1 \                    | NT0+2 )                  |

| Instruction          | 1<br>1<br>1 | 1<br>1<br>1 | <b></b>                | <b>≜</b>               | <b>≜</b>               | <b>†</b>               | <b>†</b>                   | <b>≜</b>                 |

| Executed             | 1           | 1           | Write TMR0<br>executed | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1 | Read TMR0<br>reads NT0 + |

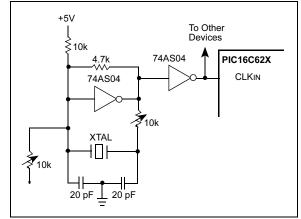

#### 9.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance or one with parallel resonance.

Figure 9-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 9-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

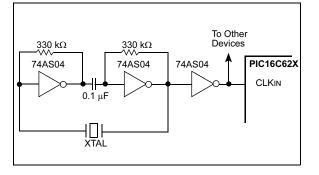

Figure 9-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a  $180^{\circ}$  phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 9-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

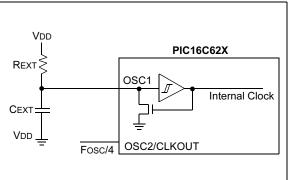

## 9.2.4 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 9-5 shows how the R/C combination is connected to the PIC16C62X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See Section 13.0 for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See Section 13.0 for variation of oscillator frequency due to VDD for given REXT/CEXT values, as well as frequency variation due to operating temperature for given R, C and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

## FIGURE 9-5: RC OSCILLATOR MODE

## 9.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

### 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

#### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

The Power-up Time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

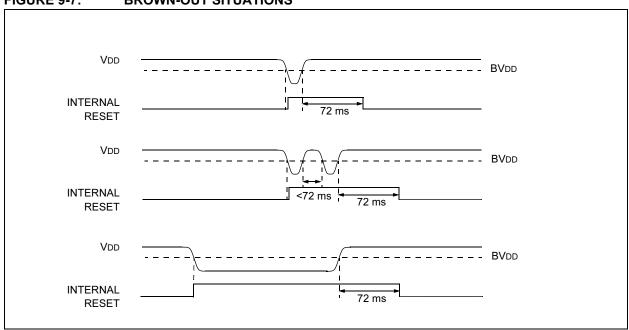

### 9.4.4 BROWN-OUT RESET (BOR)

The PIC16C62X members have on-chip Brown-out Reset circuitry. A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V refer to VBOR parameter D005 (VBOR) for greater than parameter (TBOR) in Table 12-5. The brown-out situation will RESET the chip. A RESET won't occur if VDD falls below 4.0V for less than parameter (TBOR).

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 9-7 shows typical Brown-out situations.

### FIGURE 9-7: BROWN-OUT SITUATIONS

### 9.4.5 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with <u>PWRTE</u> bit erased (<u>PWRT</u> disabled), there will be no time-out at all. Figure 9-8, Figure 9-9 and Figure 9-10 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 9-9). This is useful for testing purposes or to synchronize more than one PIC16C62X device operating in parallel.

Table 9-4 shows the RESET conditions for some special registers, while Table 9-5 shows the RESET conditions for all the registers.

## 9.4.6 POWER CONTROL (PCON)/ STATUS REGISTER

The power control/STATUS register, PCON (address 8Eh), has two bits.

Bit0 is  $\overline{\text{BOR}}$  (Brown-out).  $\overline{\text{BOR}}$  is unknown on Poweron Reset. It must then be set by the user and checked on subsequent RESETS to see if  $\overline{\text{BOR}} = 0$ , indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$  STATUS bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent RESET, if POR is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe              | er-up     | Brown-out Reset   | Wake-up    |

|--------------------------|-------------------|-----------|-------------------|------------|

|                          | PWRTE = 0         | PWRTE = 1 | Brown-out Reset   | from SLEEP |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc  |

| RC                       | 72 ms             | _         | 72 ms             | _          |

### TABLE 9-1: TIME-OUT IN VARIOUS SITUATIONS

| <b>TABLE 9-2</b> : | STATUS/PCON BITS AND THEIR SIGNIFICANCE |

|--------------------|-----------------------------------------|

|--------------------|-----------------------------------------|

| POR | BOR | то | PD |                                    |

|-----|-----|----|----|------------------------------------|

| 0   | Х   | 1  | 1  | Power-on Reset                     |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR          |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR          |

| 1   | 0   | Х  | Х  | Brown-out Reset                    |

| 1   | 1   | 0  | u  | WDT Reset                          |

| 1   | 1   | 0  | 0  | WDT Wake-up                        |

| 1   | 1   | u  | u  | MCLR Reset during normal operation |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP            |

Legend: u = unchanged, x = unknown

#### TABLE 9-3: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 83h     | STATUS |       |       |       | TO    | PD    |       |       |       | 0001 1xxx             | 000q quuu                                      |

| 8Eh     | PCON   | _     | _     |       | _     | _     | _     | POR   | BOR   | 0x                    | uq                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

### TABLE 9-4: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register | Address | Power-on Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during<br/>SLEEP</li> <li>WDT Reset</li> <li>Brown-out Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP<br/>through interrupt</li> <li>Wake-up from SLEEP<br/>through WDT time-out</li> </ul> |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W        | _       | xxxx xxxx      | นนนน นนนน                                                                                                                                                  | <u></u>                                                                                                           |

| INDF     | 00h     |                | _                                                                                                                                                          | _                                                                                                                 |

| TMR0     | 01h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | นนนน นนนน                                                                                                         |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                                                                                  | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                                                                                   | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR      | 04h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                                                                                     | u uuuu                                                                                                            |

| PORTB    | 06h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | uuuu uuuu                                                                                                         |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                                                                                    | uu uuuu                                                                                                           |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                                                                                     | u uuuu                                                                                                            |

| INTCON   | 0Bh     | 0000 000x      | 0000 000u                                                                                                                                                  | uuuu uqqq <sup>(2)</sup>                                                                                          |

| PIR1     | 0Ch     | -0             | -0                                                                                                                                                         | -q (2,5)                                                                                                          |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                                                                                     | u uuuu                                                                                                            |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PIE1     | 8Ch     | -0             | -0                                                                                                                                                         | -u                                                                                                                |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                                                                        | uu                                                                                                                |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                                                                                  | uuu- uuuu                                                                                                         |

### TABLE 9-5: INITIALIZATION CONDITION FOR REGISTERS

$\label{eq:legend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 9-4 for RESET value for specific condition.

5: If wake-up was due to comparator input changing, then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = u.

**6:** If RESET was due to brown-out, then bit 0 = 0. All other RESETS will cause bit 0 = u.

| BCF              | Bit Clear f                                                         | BTFSC            | Bit Test, Skip if Clear                                                   |

|------------------|---------------------------------------------------------------------|------------------|---------------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      | Syntax:          | [label]BTFSC f,b                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$       |

| Operation:       | $0 \rightarrow (f \le b >)$                                         | Operation:       | skip if (f <b>) = 0</b>                                                   |

| Status Affected: | None                                                                | Status Affected: | None                                                                      |

| Encoding:        | 01 00bb bfff ffff                                                   | Encoding:        | 01 10bb bfff ffff                                                         |

| Description:     | Bit 'b' in register 'f' is cleared.                                 | Description:     | If bit 'b' in register 'f' is '0', then the                               |

| Words:           | 1                                                                   |                  | next instruction is skipped.<br>If bit 'b' is '0', then the next instruc- |

| Cycles:          | 1                                                                   |                  | tion fetched during the current                                           |

| Example          | BCF FLAG_REG, 7                                                     |                  | instruction execution is discarded,                                       |

|                  | Before Instruction<br>FLAG_REG = 0xC7                               |                  | and a NOP is executed instead,<br>making this a two-cycle instruction.    |

|                  | After Instruction                                                   | Words:           | 1                                                                         |

|                  | FLAG_REG = 0x47                                                     | Cycles:          | 1(2)                                                                      |

|                  |                                                                     | Example          | here btfsc <b>FLAG,1</b><br>false goto <b>process co</b>                  |