Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | ·                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                |                                                                            |

| RAM Size                   | 96 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | ·                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c620a-20i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

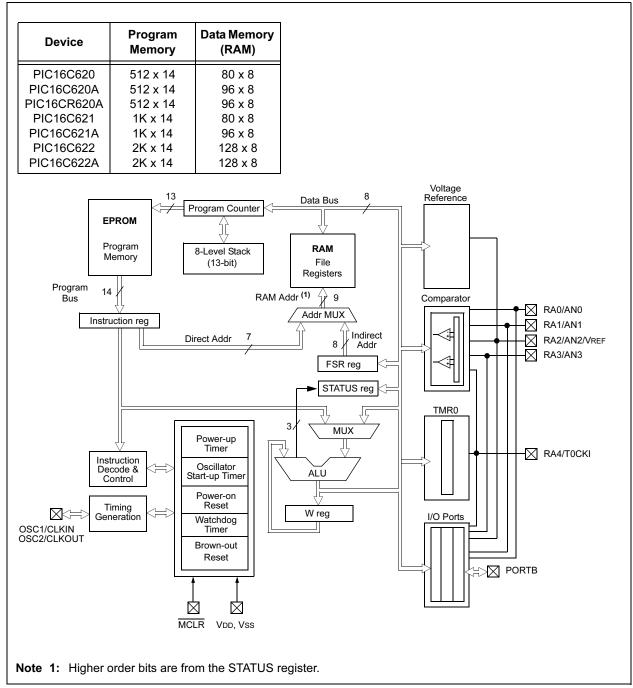

# 2.0 PIC16C62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C62X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

# 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the Oscillator modes.

Microchip's PICSTART<sup>®</sup> and PRO MATE<sup>®</sup> programmers both support programming of the PIC16C62X.

Note: Microchip does not recommend code protecting windowed devices.

#### 2.2 One-Time-Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

## 2.3 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who chose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices, but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

# 2.4 Serialized Quick-Turnaround-Production<sup>sm</sup> (SQTP<sup>sm</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry-code, password or ID number.

#### FIGURE 3-1: BLOCK DIAGRAM

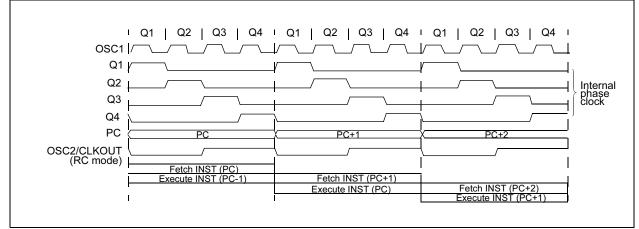

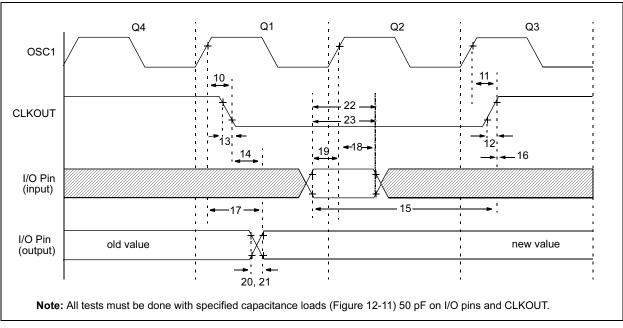

# 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

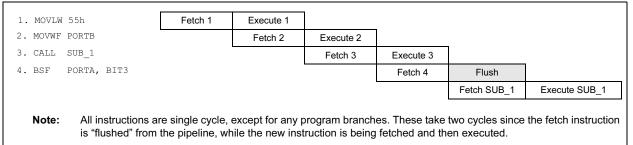

## 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

#### 4.2.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uuluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any STATUS bit. For other instructions not affecting any STATUS bits, see the "Instruction Set Summary".

- Note 1: The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16C62X and should be programmed as '0'. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The <u>C and DC bits</u> operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

#### REGISTER 4-1: STATUS REGISTER (ADDRESS 03H OR 83H)

|         | Reserved                                                                                                          | Reserved                           | R/W-0          | R-1            | R-1            | R/W-x          | R/W-x        | R/W-x          |  |

|---------|-------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|----------------|----------------|--------------|----------------|--|

|         | IRP                                                                                                               | RP1                                | RP0            | TO             | PD             | Z              | DC           | С              |  |

|         | bit 7                                                                                                             |                                    |                |                |                |                |              | bit 0          |  |

|         |                                                                                                                   |                                    |                |                |                |                |              |                |  |

| bit 7   | <b>IRP:</b> Register Bank Select bit (used for indirect addressing)                                               |                                    |                |                |                |                |              |                |  |

|         |                                                                                                                   | , 3 (100h - 1<br>, 1 (00h - FF     |                |                |                |                |              |                |  |

|         |                                                                                                                   | t is reserved                      |                | 16C62X; alv    | /ays maintai   | n this bit cle | ar.          |                |  |

| bit 6-5 |                                                                                                                   | Register Ban                       |                |                | -              |                |              |                |  |

|         |                                                                                                                   | 1 (80h - FFh                       |                |                |                |                |              |                |  |

|         |                                                                                                                   | 0 (00h - 7Fh                       |                |                |                |                |              |                |  |

|         | Each bank<br>clear.                                                                                               | is 128 bytes                       | 5. The RP1 t   | oit is reserve | ed on the PIC  | C16C62X; a     | lways mainta | ain this bit   |  |

| bit 4   | TO: Time-c                                                                                                        | out bit                            |                |                |                |                |              |                |  |

|         |                                                                                                                   | ower-up, CLI                       | RWDT instruc   | ction. or SLE  | EP instruction | on             |              |                |  |

|         |                                                                                                                   | time-out oc                        |                | ,              |                |                |              |                |  |

| bit 3   | PD: Power                                                                                                         | -down bit                          |                |                |                |                |              |                |  |

|         | -                                                                                                                 | ower-up or b<br>cution of the      | -              |                | n              |                |              |                |  |

| bit 2   | Z: Zero bit                                                                                                       |                                    |                |                |                |                |              |                |  |

|         |                                                                                                                   | sult of an arit<br>sult of an arit |                |                |                | )              |              |                |  |

| bit 1   |                                                                                                                   |                                    |                | • •            |                |                | )(for borrow | the polarity   |  |

|         | <b>DC</b> : Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)(for borrow the polarity is reversed) |                                    |                |                |                |                |              |                |  |

|         |                                                                                                                   | -out from the                      |                |                |                | rred           |              |                |  |

|         |                                                                                                                   | ry-out from th                     |                |                |                |                |              |                |  |

| bit 0   | •                                                                                                                 | orrow bit (AD                      |                |                |                |                |              |                |  |

|         | •                                                                                                                 | -out from the<br>ry-out from th    | -              |                |                |                |              |                |  |

|         | Note:                                                                                                             | For borrow t                       | he polarity i  | s reversed.    | A subtraction  | on is execut   | ed by addin  | g the two's    |  |

|         |                                                                                                                   | complement                         |                |                |                |                |              | s, this bit is |  |

|         |                                                                                                                   | loaded with e                      | either the hig | gh or low or   | der bit of the | source reg     | ister.       |                |  |

|         | Legend:                                                                                                           | L. L. 14                           |                |                |                |                | hit on all   | 0              |  |

|         | R = Reada                                                                                                         |                                    |                | ritable bit    |                | •              | bit, read as |                |  |

|         | - n = Value                                                                                                       | at POR                             | 1′ = Bi        | it is set      | '0' = Bit i    | scleared       | x = Bit is u | nknown         |  |

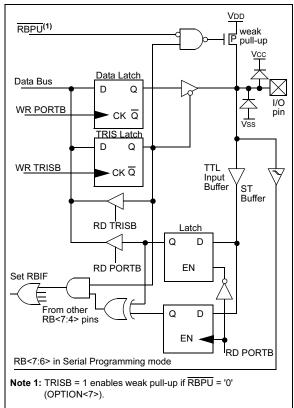

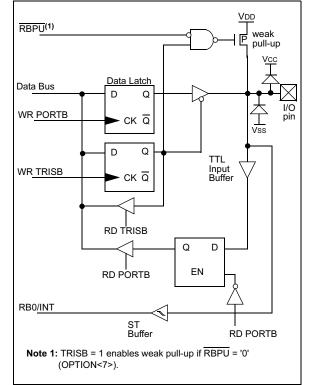

## 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a High Impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A \ typical$ ). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (e.g., any RB<7:4> pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

#### FIGURE 5-5: BLOCK DIAGRAM OF RB<7:4> PINS

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552, "Implementing Wake-Up on Key Strokes.)

| Note: | If a change on the I/O pin should occur       |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|

|       | when the read operation is being executed     |  |  |  |  |  |  |

|       | (start of the Q2 cycle), then the RBIF inter- |  |  |  |  |  |  |

|       | rupt flag may not get set.                    |  |  |  |  |  |  |

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

| Name    | Bit # | Buffer Type           | Function                                                                                                                |

|---------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0  | TTL/ST <sup>(1)</sup> | Input/output or external interrupt input. Internal software programmable weak pull-up.                                  |

| RB1     | bit1  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB2     | bit2  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB3     | bit3  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB4     | bit4  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB5     | bit5  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

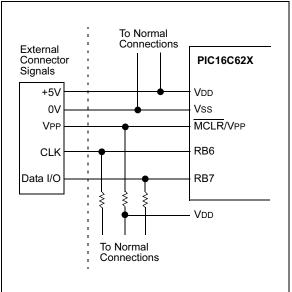

| RB6     | bit6  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock pin. |

| RB7     | bit7  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data pin.  |

#### TABLE 5-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h     | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX XXXX       | uuuu uuuu                       |

| 86h     | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h     | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

Legend: u = unchanged, x = unknown

Note 1: Shaded bits are not used by PORTB.

### 9.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs with no external circuitry drawing current from the I/O pin and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated      |

|-------|------------------------------------------------|

|       | by a WDT time-out does not drive MCLR pin low. |

|       |                                                |

#### 9.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device RESET. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. PD bit, which is set on power-up, is cleared when SLEEP is invoked. TO bit is cleared if WDT wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction after the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

**Note:** If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from SLEEP. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes up from SLEEP, regardless of the source of wake-up.

| Q1 Q2 Q                  | 3 Q4 Q1 Q2 Q3 Q4 Q | Q1                    | Q1 Q2 Q3 Q4      | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 0    | Q1 Q2 Q3 Q4 |

|--------------------------|--------------------|-----------------------|------------------|-------------|------------------|-------------|

| OSC1 //////              |                    | AAAAA                 |                  |             |                  |             |

| CLKOUT(4)                |                    | Tost(2)               | <u> </u>         |             | \ <u>`</u>       |             |

| INT pin                  | 1 I                |                       | 1<br>1           |             | 1                |             |

| NTF flag                 |                    |                       | Interrupt Latend | SV.         |                  |             |

| INTCON<1>)               |                    | <del>≉</del>          | (Note 2)         | ,           |                  |             |

| GIE bit<br>INTCON<7>)    |                    | Processor in<br>SLEEP | 1                |             |                  |             |

| INSTRUCTION FLOW         |                    |                       | 1<br>1<br>1      |             | 1                |             |

| PC X PC                  | <u>Υ PC+1 Χ</u>    | PC+2                  | X PC+2           | PC + 2      | <u>χ 0004h χ</u> | 0005h       |

| Instruction { Inst(PC) = | SLEEP Inst(PC + 1) |                       | Inst(PC + 2)     |             | Inst(0004h)      | Inst(0005h) |

| Instruction Inst(PC      | - 1) SLEEP         |                       | Inst(PC + 1)     | Dummy cycle | Dummy cycle      | Inst(0004h) |

#### FIGURE 9-18: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**3:** GIE = '1' assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these Osc modes, but shown here for timing reference.

#### 9.9 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip                    | does | not | recommend | code |  |  |  |

|-------|------------------------------|------|-----|-----------|------|--|--|--|

|       | protecting windowed devices. |      |     |           |      |  |  |  |

#### 9.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify. Only the Least Significant 4 bits of the ID locations are used.

# 9.11 In-Circuit Serial Programming™

The PIC16C62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X/9XX Programming Specification (DS30228).

A typical In-Circuit Serial Programming connection is shown in Figure 9-19.

# FIGURE 9-19:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

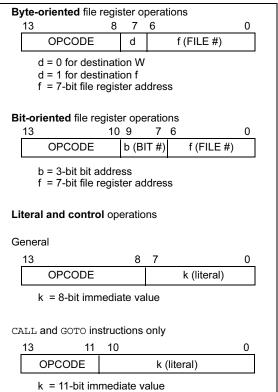

# **10.0 INSTRUCTION SET SUMMARY**

Each PIC16C62X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16C62X instruction set summary in Table 10-2 lists **byte-oriented**, **bitoriented**, and **literal and control** operations. Table 10-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 10-1: OPCODE FIELD DESCRIPTIONS

|               | DESCRIPTIONS                                                                                                                                                                   |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field         | Description                                                                                                                                                                    |

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| х             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLAT<br>H    | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| то            | Time-out bit                                                                                                                                                                   |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified regis-<br>ter file location                                                                                                 |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| < >           | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

|               |                                                                                                                                                                                |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- **Bit-oriented** operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 10-1 lists the instructions recognized by the MPASM  $^{\rm TM}$  assembler.

Figure 10-1 shows the three general formats that the instructions can have.

| Note: | To maintain upward compatibility with     |   |

|-------|-------------------------------------------|---|

|       | future PICmicro® products, do not use the | ÷ |

|       | OPTION and TRIS instructions.             |   |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

| MOVF             | Move f                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                    |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                             |

| Status Affected: | Z                                                                                                                                                                                                                                                                                    |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |

| Example          | MOVF FSR, <b>0</b>                                                                                                                                                                                                                                                                   |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |

| MOVWF            | Move W to f                                                                                                                                                                                                                                                                          |

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                    |

| Operation:       | $(W) \rightarrow (f)$                                                                                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                                                                 |

| Encoding:        | 00 0000 1fff ffff                                                                                                                                                                                                                                                                    |

| Description:     | Move data from W register to reg-<br>ister 'f'.                                                                                                                                                                                                                                      |

| Words:           | 1                                                                                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |

| Example          | MOVWF OPTION                                                                                                                                                                                                                                                                         |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F                                                                                                                                                                                                |

|                  | $\begin{array}{rcl} \text{OPTION} &= & 0x4F \\ \text{W} &= & 0x4F \end{array}$                                                                                                                                                                                                       |

| NOP              | No Operation |        |      |      |  |  |  |

|------------------|--------------|--------|------|------|--|--|--|

| Syntax:          | [ label ]    | NOP    |      |      |  |  |  |

| Operands:        | None         |        |      |      |  |  |  |

| Operation:       | No operation |        |      |      |  |  |  |

| Status Affected: | None         |        |      |      |  |  |  |

| Encoding:        | 00           | 0000   | 0xx0 | 0000 |  |  |  |

| Description:     | No opera     | ition. |      |      |  |  |  |

| Words:           | 1            |        |      |      |  |  |  |

| Cycles:          | 1            |        |      |      |  |  |  |

| Example          | NOP          |        |      |      |  |  |  |

| OPTION           | Load Option Register                                                                                                                                                                                                                               |      |      |      |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--|--|--|--|--|

| Syntax:          | [label] OPTION                                                                                                                                                                                                                                     |      |      |      |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                               |      |      |      |  |  |  |  |  |

| Operation:       | $(W) \rightarrow OPTION$                                                                                                                                                                                                                           |      |      |      |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                               |      |      |      |  |  |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                                                                 | 0000 | 0110 | 0010 |  |  |  |  |  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register.<br>This instruction is supported for<br>code compatibility with PIC16C5X<br>products. Since OPTION is a read-<br>able/writable register, the user can<br>directly address it. |      |      |      |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                  |      |      |      |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                  |      |      |      |  |  |  |  |  |

| Example          |                                                                                                                                                                                                                                                    |      |      |      |  |  |  |  |  |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup><br>products, do not use this<br>instruction.                                                                                                                               |      |      |      |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                    |      |      |      |  |  |  |  |  |

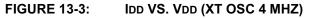

#### 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended)

|                                                                                                                                                          | dustrial and mmercial and |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|--|--|

|                                                                                                                                                          |                           |  |  |  |  |  |

| PIC16LC62X $0^{\circ}C \le TA \le +70^{\circ}C$ for con-<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for e                                                |                           |  |  |  |  |  |

| Param.         Sym         Characteristic         Min         Typ†         Max         Units         Conditio           No.                Conditio      | ons                       |  |  |  |  |  |

| D001         VDD         Supply Voltage         3.0         —         6.0         V         See Figures 12-1, 12-2, 12-3                                 | 3, 12-4, and 12-5         |  |  |  |  |  |

| D001         VDD         Supply Voltage         2.5         —         6.0         V         See Figures 12-1, 12-2, 12-3                                 | 3, 12-4, and 12-5         |  |  |  |  |  |

| D002 VDR RAM Data Retention Voltage <sup>(1)</sup> — 1.5* — V Device in SLEEP mode                                                                       |                           |  |  |  |  |  |

| D002 VDR RAM Data Retention Voltage <sup>(1)</sup> — 1.5* — V Device in SLEEP mode                                                                       |                           |  |  |  |  |  |

| D003         VPOR         VDD start voltage to ensure         —         Vss         —         V         See section on Power-on Report                   | eset for details          |  |  |  |  |  |

| D003         VPOR         VDD start voltage to<br>ensure Power-on Reset         —         Vss         —         V         See section on Power-on Reset  | eset for details          |  |  |  |  |  |

| D004         SVDD         VDD rise rate to ensure<br>Power-on Reset         0.05*         —         —         V/ms         See section on Power-on Reset | eset for details          |  |  |  |  |  |

| D004     SVDD     VDD rise rate to ensure     0.05*     —     —     V/ms     See section on Power-on Reset                                               | eset for details          |  |  |  |  |  |

| D005 VBOR Brown-out Detect Voltage 3.7 4.0 4.3 V BOREN configuration bit is a                                                                            | cleared                   |  |  |  |  |  |

| D005 VBOR Brown-out Detect Voltage 3.7 4.0 4.3 V BOREN configuration bit is a                                                                            | cleared                   |  |  |  |  |  |

| D010 IDD Supply Current <sup>(2)</sup> - 1.8 3.3 mA Fosc = 4 MHz, VDD = 5.5V, mode, (Note 4)*                                                            |                           |  |  |  |  |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                  | WD1 disabled, LP          |  |  |  |  |  |

| 9.0 20 mA Fosc = 20 MHz, VDD = 5.5V mode                                                                                                                 | , WDT disabled, HS        |  |  |  |  |  |

| D010 IDD Supply Current <sup>(2)</sup> $-$ 1.4 2.5 mA Fosc = 2.0 MHz, VDD = 3.0 V mode (Note 4)                                                          | /, WDT disabled, XT       |  |  |  |  |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                  | WDT disabled, LP          |  |  |  |  |  |

| D020 IPD Power-down Current <sup>(3)</sup> — 1.0 2.5 $\mu$ A VDD=4.0V, WDT disabled (125°C)                                                              |                           |  |  |  |  |  |

| D020 IPD Power-down Current <sup>(3)</sup> — 0.7 2 $\mu$ A VDD=3.0V, WDT disabled                                                                        |                           |  |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

$\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

### 12.3 DC CHARACTERISTICS: PIC16CR62XA-04 (Commercial, Industrial, Extended) PIC16CR62XA-20 (Commercial, Industrial, Extended) PIC16LCR62XA-04 (Commercial, Industrial, Extended)

| PIC16CR62XA-04<br>PIC16CR62XA-20 |      |                                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |            |            |          |                                                                                                                   |  |  |

|----------------------------------|------|------------------------------------------------------|------------------------------------------------------|------------|------------|----------|-------------------------------------------------------------------------------------------------------------------|--|--|

| PIC16LCR62XA-04                  |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                      |            |            |          |                                                                                                                   |  |  |

| Param.<br>No.                    | Sym  | Characteristic                                       | Min                                                  | Тур†       | Мах        | Units    | Conditions                                                                                                        |  |  |

| D001                             | Vdd  | Supply Voltage                                       | 3.0                                                  | —          | 5.5        | V        | See Figures 12-7, 12-8, 12-9                                                                                      |  |  |

| D001                             | Vdd  | Supply Voltage                                       | 2.5                                                  | —          | 5.5        | V        | See Figures 12-7, 12-8, 12-9                                                                                      |  |  |

| D002                             | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>         |                                                      | 1.5*       |            | V        | Device in SLEEP mode                                                                                              |  |  |

| D002                             | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>         | _                                                    | 1.5*       | —          | V        | Device in SLEEP mode                                                                                              |  |  |

| D003                             | VPOR | VDD start voltage to<br>ensure Power-on Reset        |                                                      | Vss        | _          | V        | See section on Power-on Reset for details                                                                         |  |  |

| D003                             | VPOR | VDD start voltage to<br>ensure Power-on Reset        | —                                                    | Vss        | —          | V        | See section on Power-on Reset for details                                                                         |  |  |

| D004                             | SVDD | VDD rise rate to ensure<br>Power-on Reset            | 0.05*                                                | —          | —          | V/ms     | See section on Power-on Reset for details                                                                         |  |  |

| D004                             | SVDD | VDD rise rate to ensure<br>Power-on Reset            | 0.05*                                                | —          | —          | V/ms     | See section on Power-on Reset for details                                                                         |  |  |

| D005                             | VBOR | Brown-out Detect Voltage                             | 3.7                                                  | 4.0        | 4.35       | V        | BOREN configuration bit is cleared                                                                                |  |  |

| D005                             | VBOR | Brown-out Detect Voltage                             | 3.7                                                  | 4.0        | 4.35       | V        | BOREN configuration bit is cleared                                                                                |  |  |

| D010                             | Idd  | Supply Current <sup>(2)</sup>                        | _                                                    | 1.2<br>500 | 1.7<br>900 | mA<br>μA | Fosc = 4 MHz, VDD = 5.5V, WDT disabled, XT mode,<br>(Note 4)*<br>Fosc = 4 MHz, VDD = 3.0V, WDT disabled, XT mode, |  |  |

|                                  |      |                                                      | _                                                    | 1.0        | 2.0        | mA       | (Note 4)<br>Fosc = 10 MHz, VDD = 3.0V, WDT disabled, HS mode,<br>(Note 6)                                         |  |  |

|                                  |      |                                                      | —                                                    | 4.0        | 7.0        | mA       | Fosc = 20 MHz, VDD = 5.5V, WDT disabled*, HS                                                                      |  |  |

|                                  |      |                                                      | —                                                    | 3.0        | 6.0        | mA       | mode                                                                                                              |  |  |

|                                  |      |                                                      |                                                      | 35         | 70         | μA       | Fosc = 20 MHz, VDD = 4.5V, WDT disabled, HS mode<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled, LP mode              |  |  |

| D010                             | IDD  | Supply Current <sup>(2)</sup>                        | —                                                    | 1.2        | 1.7        | mA       | Fosc = 4.0 MHz, VDD = 5.5V, WDT disabled, XT<br>mode, ( <b>Note 4</b> )*                                          |  |  |

|                                  |      |                                                      | —                                                    | 400        | 800        | μA       | Fosc = 4.0 MHz, VDD = 2.5V, WDT disabled, XT mode (Note 4)                                                        |  |  |

|                                  |      |                                                      | —                                                    | 35         | 70         | μA       | Fosc = 32 kHz, VDD = 2.5V, WDT disabled, LP mode                                                                  |  |  |

#### 12.4 DC Characteristics: PIC16C62X/C62XA/CR62XA (Commercial, Industrial, Extended) PIC16LC62X/LC62XA/LCR62XA (Commercial, Industrial, Extended) (CONT.)

| PIC16C                                                                               | 62X/C6 | 2XA/CR62XA                                                          | $ \begin{array}{ l l l l l l l l l l l l l l l l l l l$ |      |            |                                                                                                                                                        |                                                             |  |  |

|--------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------|---------------------------------------------------------|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|

| <b>PIC16LC62X/LC62XA/LCR62XA</b> $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commerce |        |                                                                     |                                                         |      |            | $ \begin{array}{ll} C & \leq TA \leq +85^{\circ}C \mbox{ for industrial and} \\ C & \leq TA \leq +70^{\circ}C \mbox{ for commercial and} \end{array} $ |                                                             |  |  |

| Param.<br>No.                                                                        | Sym    | Characteristic                                                      | Min                                                     | Тур† | Мах        | Units                                                                                                                                                  | Conditions                                                  |  |  |

|                                                                                      | Vih    | Input High Voltage                                                  |                                                         |      |            |                                                                                                                                                        |                                                             |  |  |

| D040                                                                                 |        | with TTL buffer                                                     | 2.0V<br>0.25 VDD<br>+ 0.8V                              | _    | Vdd<br>Vdd | V                                                                                                                                                      | VDD = 4.5V to 5.5V<br>otherwise                             |  |  |

| D041                                                                                 |        | with Schmitt Trigger input                                          | 0.8 Vdd                                                 | _    | VDD        |                                                                                                                                                        |                                                             |  |  |

| D042                                                                                 |        | MCLR RA4/T0CKI                                                      | 0.8 VDD                                                 | _    | Vdd        | V                                                                                                                                                      |                                                             |  |  |

| D043<br>D043A                                                                        |        | OSC1 (XT, HS and LP)<br>OSC1 (in RC mode)                           | 0.7 Vdd<br>0.9 Vdd                                      | -    | Vdd        | V                                                                                                                                                      | (Note 1)                                                    |  |  |

| D070                                                                                 | IPURB  | PORTB weak pull-up current                                          | 50                                                      | 200  | 400        | μA                                                                                                                                                     | VDD = 5.0V, VPIN = VSS                                      |  |  |

| D070                                                                                 | IPURB  | PORTB weak pull-up current                                          | 50                                                      | 200  | 400        | μA                                                                                                                                                     | VDD = 5.0V, VPIN = VSS                                      |  |  |

|                                                                                      | lı∟    | Input Leakage Current <sup>(2, 3)</sup><br>I/O ports (Except PORTA) |                                                         |      | ±1.0       | μA                                                                                                                                                     | Vss ≤ VPIN ≤ VDD, pin at hi-impedance                       |  |  |

| D060                                                                                 |        | PORTA                                                               | _                                                       | _    | ±0.5       | μΑ                                                                                                                                                     | $Vss \leq VPIN \leq VDD$ , pin at hi-impedance              |  |  |

| D061                                                                                 |        | RA4/T0CKI                                                           | _                                                       | _    | ±1.0       | μΑ                                                                                                                                                     | $Vss \leq VPIN \leq VDD$                                    |  |  |

| D063                                                                                 |        | OSC1, MCLR                                                          | _                                                       | _    | ±5.0       | μA                                                                                                                                                     | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration |  |  |

|                                                                                      | lı∟    | Input Leakage Current <sup>(2, 3)</sup>                             |                                                         |      |            |                                                                                                                                                        |                                                             |  |  |

|                                                                                      |        | I/O ports (Except PORTA)                                            |                                                         |      | ±1.0       | μA                                                                                                                                                     | Vss $\leq$ VPIN $\leq$ VDD, pin at hi-impedance             |  |  |

| D060                                                                                 |        | PORTA                                                               | -                                                       | —    | ±0.5       | μA                                                                                                                                                     | $Vss \le VPIN \le VDD$ , pin at hi-impedance                |  |  |

| D061                                                                                 |        | RA4/T0CKI                                                           | -                                                       | —    | ±1.0       | μA                                                                                                                                                     | $Vss \leq V \text{PIN} \leq V \text{DD}$                    |  |  |

| D063                                                                                 |        | OSC1, MCLR                                                          | —                                                       | —    | ±5.0       | μΑ                                                                                                                                                     | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration |  |  |

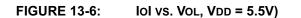

|                                                                                      | Vol    | Output Low Voltage                                                  |                                                         |      |            |                                                                                                                                                        |                                                             |  |  |

| D080                                                                                 |        | I/O ports                                                           | —                                                       | —    | 0.6        | V                                                                                                                                                      | IOL = 8.5 mA, VDD = 4.5V, $-40^{\circ}$ to $+85^{\circ}$ C  |  |  |

|                                                                                      |        |                                                                     | —                                                       | -    | 0.6        | V                                                                                                                                                      | IOL = 7.0 mA, VDD = 4.5V, +125°C                            |  |  |

| D083                                                                                 |        | OSC2/CLKOUT (RC only)                                               | —                                                       | -    | 0.6        | V                                                                                                                                                      | IOL = 1.6 mA, VDD = 4.5V, $-40^{\circ}$ to $+85^{\circ}$ C  |  |  |

|                                                                                      |        |                                                                     | —                                                       | —    | 0.6        | V                                                                                                                                                      | IOL = 1.2 mA, VDD = 4.5V, +125°C                            |  |  |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16C62X(A) be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as coming out of the pin.

# 12.8 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

2. TppS

| 2. Tpp3                                       |                        |     |              |  |  |  |

|-----------------------------------------------|------------------------|-----|--------------|--|--|--|

| т                                             |                        |     |              |  |  |  |

| F                                             | Frequency              | Т   | Time         |  |  |  |

| Lowercase subscripts (pp) and their meanings: |                        |     |              |  |  |  |

| рр                                            |                        |     |              |  |  |  |

| ck                                            | CLKOUT                 | osc | OSC1         |  |  |  |

| io                                            | I/O port               | t0  | ТОСКІ        |  |  |  |

| mc                                            | MCLR                   |     |              |  |  |  |

| Uppercase letters and their meanings:         |                        |     |              |  |  |  |

| S                                             |                        |     |              |  |  |  |

| F                                             | Fall                   | Р   | Period       |  |  |  |

| Н                                             | High                   | R   | Rise         |  |  |  |

| I                                             | Invalid (Hi-impedance) | V   | Valid        |  |  |  |

| L                                             | Low                    | Z   | Hi-Impedance |  |  |  |

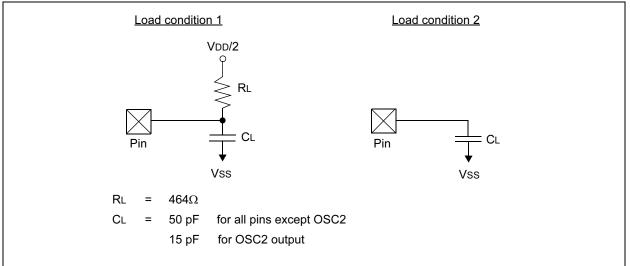

#### FIGURE 12-11: LOAD CONDITIONS

# PIC16C62X

# PIC16C62X

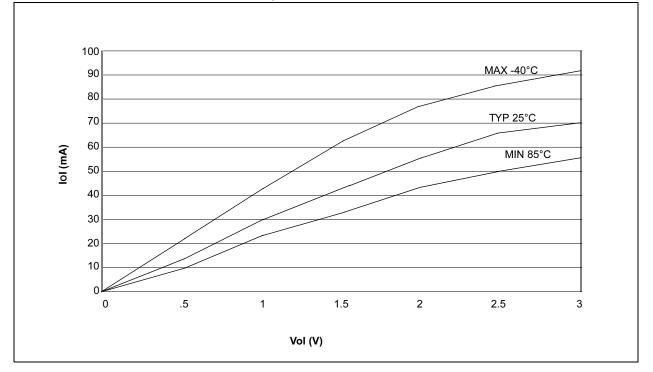

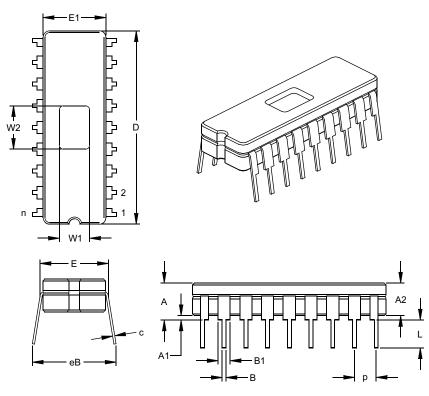

# 14.0 PACKAGING INFORMATION

18-Lead Ceramic Dual In-line with Window (JW) – 300 mil (CERDIP)

|                            | Units  | INCHES* |      |      | MILLIMETERS |       |       |  |

|----------------------------|--------|---------|------|------|-------------|-------|-------|--|

| Dimension                  | Limits | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |  |

| Number of Pins             | n      |         | 18   |      |             | 18    |       |  |

| Pitch                      | р      |         | .100 |      |             | 2.54  |       |  |

| Top to Seating Plane       | Α      | .170    | .183 | .195 | 4.32        | 4.64  | 4.95  |  |

| Ceramic Package Height     | A2     | .155    | .160 | .165 | 3.94        | 4.06  | 4.19  |  |

| Standoff                   | A1     | .015    | .023 | .030 | 0.38        | 0.57  | 0.76  |  |

| Shoulder to Shoulder Width | Е      | .300    | .313 | .325 | 7.62        | 7.94  | 8.26  |  |

| Ceramic Pkg. Width         | E1     | .285    | .290 | .295 | 7.24        | 7.37  | 7.49  |  |

| Overall Length             | D      | .880    | .900 | .920 | 22.35       | 22.86 | 23.37 |  |

| Tip to Seating Plane       | L      | .125    | .138 | .150 | 3.18        | 3.49  | 3.81  |  |

| Lead Thickness             | С      | .008    | .010 | .012 | 0.20        | 0.25  | 0.30  |  |

| Upper Lead Width           | B1     | .050    | .055 | .060 | 1.27        | 1.40  | 1.52  |  |

| Lower Lead Width           | В      | .016    | .019 | .021 | 0.41        | 0.47  | 0.53  |  |

| Overall Row Spacing §      | eB     | .345    | .385 | .425 | 8.76        | 9.78  | 10.80 |  |

| Window Width               | W1     | .130    | .140 | .150 | 3.30        | 3.56  | 3.81  |  |

| Window Length              | W2     | .190    | .200 | .210 | 4.83        | 5.08  | 5.33  |  |

\* Controlling Parameter

§ Significant Characteristic

JEDEC Equivalent: MO-036

Drawing No. C04-010

# **APPENDIX A: ENHANCEMENTS**

The following are the list of enhancements over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14 bits. This allows larger page sizes both in program memory (4K now as opposed to 512 before) and register file (up to 128 bytes now versus 32 bytes before).

- 2. A PC high latch register (PCLATH) is added to handle program memory paging. PA2, PA1, PA0 bits are removed from STATUS register.

- 3. Data memory paging is slightly redefined. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW.