Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 896B (512 x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 96 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c620a-20i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0     | General Description                 | . 5 |

|---------|-------------------------------------|-----|

| 2.0     | PIC16C62X Device Varieties          | . 7 |

|         | Architectural Overview              |     |

|         | Memory Organization                 |     |

| 5.0     | I/O Ports                           | 25  |

| 6.0     | Timer0 Module                       | 31  |

| 7.0     | Comparator Module                   | 37  |

| 8.0     | Voltage Reference Module            | 43  |

| 9.0     | Special Features of the CPU         | 45  |

| 10.0    | Instruction Set Summary             | 61  |

|         | Development Support                 |     |

| 12.0    | Electrical Specifications           | 81  |

| 13.0    | Device Characterization Information | 09  |

| 14.0    | Packaging Information 1             | 13  |

|         | Jix A: Enhancements 1               |     |

| Append  | Jix B: Compatibility                | 19  |

| Index   |                                     | 21  |

| On-Line | e Support 1                         | 23  |

| System  | Is Information and Upgrade Hot Line | 23  |

|         | Response 1                          |     |

| Product | t Identification System 1           | 25  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

# 4.0 MEMORY ORGANIZATION

# 4.1 Program Memory Organization

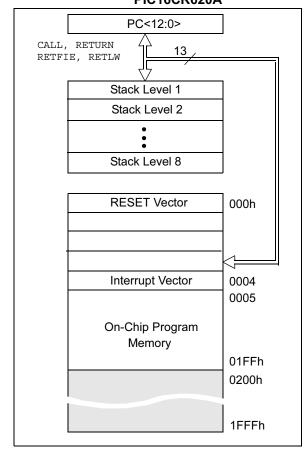

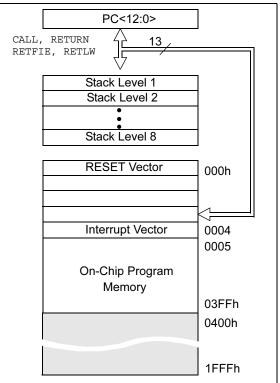

The PIC16C62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C620(A) and PIC16CR620, 1K x 14 (0000h - 03FFh) for the PIC16C621(A) and 2K x 14 (0000h - 07FFh) for the PIC16C622(A) are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16C(R)620(A)) or 1K x 14 space (PIC16C621(A)) or 2K x 14 space (PIC16C622(A)). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16C620/PIC16C620A/

PIC16C620/PIC16C620 PIC16CR620A

# FIGURE 4-2:

### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C621/PIC16C621A

FIGURE 4-3:

### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C622/PIC16C622A

# FIGURE 4-6: DATA MEMORY MAP FOR THE PIC16C620A/CR620A/621A

|                 | 11010002                       |                     | - 17 (          |

|-----------------|--------------------------------|---------------------|-----------------|

| File<br>Address | 3                              |                     | File<br>Address |

| 00h             | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup> | 80h             |

| 01h             | TMR0                           | OPTION              | 81h             |

| 02h             | PCL                            | PCL                 | 82h             |

| 03h             | STATUS                         | STATUS              | 83h             |

| 04h             | FSR                            | FSR                 | 84h             |

| 05h             | PORTA                          | TRISA               | 85h             |

| 06h             | PORTB                          | TRISB               | 86h             |

| 07h             |                                |                     | 87h             |

| 08h             |                                |                     | 88h             |

| 09h             |                                |                     | 89h             |

| 0Ah             | PCLATH                         | PCLATH              | 8Ah             |

| 0Bh             | INTCON                         | INTCON              | 8Bh             |

| 0Ch             | PIR1                           | PIE1                | 8Ch             |

| 0Dh             |                                |                     | 8Dh             |

| 0Eh             |                                | PCON                | 8Eh             |

| 0Fh             |                                |                     | 8Fh             |

| 10h             |                                |                     | 90h             |

| 11h             |                                |                     | 91h             |

| 12h             |                                |                     | 92h             |

| 13h             |                                |                     | 93h             |

| 14h             |                                |                     | 94h             |

| 15h             |                                |                     | 95h             |

| 16h             |                                |                     | 96h             |

| 17h             |                                |                     | 97h             |

| 18h             |                                |                     | 98h             |

| 19h             |                                |                     | 99h             |

| 1Ah             |                                |                     | 9Ah             |

| 1Bh             |                                |                     | 9Bh             |

| 1Ch             |                                |                     | 9Ch             |

| 1Dh             |                                |                     | 9Dh             |

| 1Eh             |                                |                     | 9Eh             |

| 1Fh             | CMCON                          | VRCON               | 9Fh             |

| 20h             | General<br>Purpose<br>Register |                     | A0h             |

| 6Fh             |                                |                     |                 |

| 70h             | General                        |                     | F0h             |

|                 | Purpose<br>Register            | Accesses<br>70h-7Fh |                 |

| 7Fh             | Bank 0                         | Bank 1              | 」 FFh           |

| Unimp           | lemented data mer              | mory locations, rea | ad as '0'.      |

| Note 1:         | Not a physical re              | gister.             |                 |

|                 |                                |                     |                 |

### FIGURE 4-7: DATA MEMORY MAP FOR THE PIC16C622A

|                   |                     | C10C022A            |                 |  |  |  |  |

|-------------------|---------------------|---------------------|-----------------|--|--|--|--|

| File<br>Address   | 3                   |                     | File<br>Address |  |  |  |  |

| 00h               | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |  |  |  |  |

| 01h               | TMR0                | OPTION              | 81h             |  |  |  |  |

| 02h               | PCL                 | PCL                 | 82h             |  |  |  |  |

| 03h               | STATUS              | STATUS              | 83h             |  |  |  |  |

| 04h               | FSR                 | FSR                 | 84h             |  |  |  |  |

| 05h               | PORTA               | TRISA               | 85h             |  |  |  |  |

| 06h               | PORTB               | TRISB               | 86h             |  |  |  |  |

| 07h               |                     |                     | 87h             |  |  |  |  |

| 08h               |                     |                     | 88h             |  |  |  |  |

| 09h               |                     |                     | 89h             |  |  |  |  |

| 0Ah               | PCLATH              | PCLATH              | 8Ah             |  |  |  |  |

| 0Bh               | INTCON              | INTCON              | 8Bh             |  |  |  |  |

| 0Ch               | PIR1                | PIE1                | 8Ch             |  |  |  |  |

| 0Dh               |                     |                     | 8Dh             |  |  |  |  |

| 0Eh               |                     | PCON                | 8Eh             |  |  |  |  |

| 0Fh               |                     |                     | 8Fh             |  |  |  |  |

| 10h               |                     |                     | 90h             |  |  |  |  |

| 11h               |                     |                     | 91h             |  |  |  |  |

| 12h               |                     |                     | 92h             |  |  |  |  |

| 13h               |                     |                     | 93h             |  |  |  |  |

| 14h               |                     |                     | 94h             |  |  |  |  |

| 15h               |                     |                     | 95h             |  |  |  |  |

| 16h               |                     |                     | 96h             |  |  |  |  |

| 17h               |                     |                     | 97h             |  |  |  |  |

| 18h               |                     |                     | 98h             |  |  |  |  |

| 19h               |                     |                     | 99h             |  |  |  |  |

| 1Ah               |                     |                     | 9Ah             |  |  |  |  |

| 1Bh               |                     |                     | 9Bh             |  |  |  |  |

| 1Ch               |                     |                     | 9Ch             |  |  |  |  |

| 1Dh               |                     |                     | 9Dh             |  |  |  |  |

| 1Eh               |                     |                     | 9Eh             |  |  |  |  |

| 1Fh               | CMCON               | VRCON               | 9Fh             |  |  |  |  |

| 20h               |                     |                     | A0h             |  |  |  |  |

|                   | General             | General             | Aon             |  |  |  |  |

|                   | Purpose<br>Register | Purpose<br>Register |                 |  |  |  |  |

|                   | rtegister           | rtegister           | BFh             |  |  |  |  |

|                   |                     |                     | C0h             |  |  |  |  |

| 0.51              |                     |                     |                 |  |  |  |  |

| 6Fh               | 0                   |                     | F0h             |  |  |  |  |

| 70h               | General<br>Purpose  | Accesses            |                 |  |  |  |  |

| 754               | Register            | 70h-7Fh             | FFh             |  |  |  |  |

| 7Fh Bank 0 Bank 1 |                     |                     |                 |  |  |  |  |

|                   |                     |                     |                 |  |  |  |  |

| Unimp             | plemented data me   | mory locations, re  | ad as '0'.      |  |  |  |  |

| Note 1:           | Not a physical re   | egister.            |                 |  |  |  |  |

## 4.2.2.4 PIE1 Register

This register contains the individual enable bit for the comparator interrupt.

| <b>REGISTER 4-4:</b>                                                                                                                 | PIE1 REGISTER (ADDRESS 8CH)                                                                                                    |             |          |     |     |     |                                |     |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------|----------|-----|-----|-----|--------------------------------|-----|--|--|

|                                                                                                                                      | U-0                                                                                                                            | R/W-0       | U-0      | U-0 | U-0 | U-0 | U-0                            | U-0 |  |  |

|                                                                                                                                      |                                                                                                                                | CMIE        | _        |     |     | —   | _                              | —   |  |  |

|                                                                                                                                      | bit 7                                                                                                                          | bit 7 bit 0 |          |     |     |     |                                |     |  |  |

| bit 7                                                                                                                                | bit 7 Unimplemented: Read as '0'                                                                                               |             |          |     |     |     |                                |     |  |  |

| bit 6                                                                                                                                | <b>CMIE</b> : Comparator Interrupt Enable bit<br>1 = Enables the Comparator interrupt<br>0 = Disables the Comparator interrupt |             |          |     |     |     |                                |     |  |  |

| bit 5-0                                                                                                                              | Unimpleme                                                                                                                      | nted: Read  | d as '0' |     |     |     |                                |     |  |  |

| Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read a- n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is |                                                                                                                                |             |          |     |     |     | bit, read as '<br>x = Bit is u |     |  |  |

## 4.2.2.5 PIR1 Register

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of |  |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User               |  |  |  |  |  |  |  |

|       | software should ensure the appropriate                                                     |  |  |  |  |  |  |  |

|       | interrupt flag bits are clear prior to enabling                                            |  |  |  |  |  |  |  |

|       | an interrupt.                                                                              |  |  |  |  |  |  |  |

# REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

| ER 4-5: | PIRT REGISTER (ADDRESS OCH)                                                                                                                |               |              |       |     |     |     |     |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|-------|-----|-----|-----|-----|--|--|--|

|         | U-0                                                                                                                                        | R/W-0         | U-0          | U-0   | U-0 | U-0 | U-0 | U-0 |  |  |  |

|         | — CMIF —                                                                                                                                   |               |              | —     | _   |     |     |     |  |  |  |

|         | bit 7                                                                                                                                      |               |              | bit 0 |     |     |     |     |  |  |  |

|         |                                                                                                                                            |               |              |       |     |     |     |     |  |  |  |

| bit 7   | Unimplemented: Read as '0'                                                                                                                 |               |              |       |     |     |     |     |  |  |  |

| bit 6   | CMIF: Comparator Interrupt Flag bit                                                                                                        |               |              |       |     |     |     |     |  |  |  |

|         | 1 = Compai                                                                                                                                 | rator input h | nas changed  | l     |     |     |     |     |  |  |  |

|         | 0 = Compai                                                                                                                                 | rator input h | nas not chan | iged  |     |     |     |     |  |  |  |

| bit 5-0 | Unimpleme                                                                                                                                  | ented: Rea    | d as '0'     |       |     |     |     |     |  |  |  |

|         |                                                                                                                                            |               |              |       |     |     |     |     |  |  |  |

|         | Legend:                                                                                                                                    |               |              |       |     |     |     |     |  |  |  |

|         | R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'- n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown |               |              |       |     |     |     |     |  |  |  |

|         |                                                                                                                                            |               |              |       |     |     |     |     |  |  |  |

### 4.2.2.6 PCON Register

The PCON register contains flag bits to differentiate between a Power-on Reset, an external MCLR Reset, WDT Reset or a Brown-out Reset.

| Note: | BOR is unknown on Power-on Reset. It        |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | must then be set by the user and checked    |  |  |  |  |  |  |  |  |  |

|       | on subsequent RESETS to see if BOR is       |  |  |  |  |  |  |  |  |  |

|       | cleared, indicating a brown-out has         |  |  |  |  |  |  |  |  |  |

|       | occurred. The BOR STATUS bit is a "don't    |  |  |  |  |  |  |  |  |  |

|       | care" and is not necessarily predictable if |  |  |  |  |  |  |  |  |  |

|       | the brown-out circuit is disabled (by       |  |  |  |  |  |  |  |  |  |

|       | programming BODEN bit in the                |  |  |  |  |  |  |  |  |  |

|       | Configuration word).                        |  |  |  |  |  |  |  |  |  |

### REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

|   | U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|---|-------|-----|-----|-----|-----|-----|-------|-------|

| ſ | —     | —   | —   | —   | —   | —   | POR   | BOR   |

| - | bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR**: Power-on Reset STATUS bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 **BOR**: Brown-out Reset STATUS bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Name    | Bit # | Buffer Type           | Function                                                                                                                |

|---------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0  | TTL/ST <sup>(1)</sup> | Input/output or external interrupt input. Internal software programmable weak pull-up.                                  |

| RB1     | bit1  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB2     | bit2  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB3     | bit3  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB4     | bit4  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB5     | bit5  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB6     | bit6  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock pin. |

| RB7     | bit7  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data pin.  |

### TABLE 5-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h     | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX XXXX       | uuuu uuuu                       |

| 86h     | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h     | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

Legend: u = unchanged, x = unknown

Note 1: Shaded bits are not used by PORTB.

# PIC16C62X

NOTES:

# 9.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

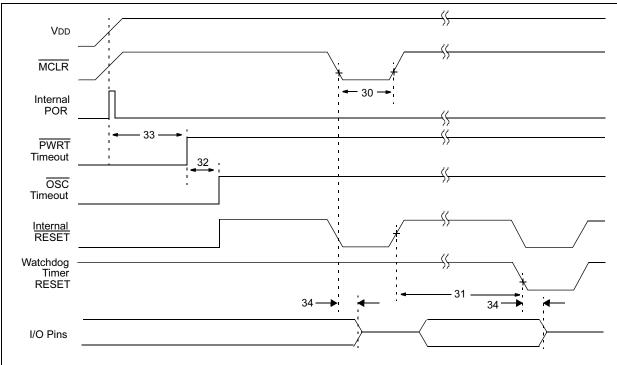

## 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

The Power-up Time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters for details.

### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

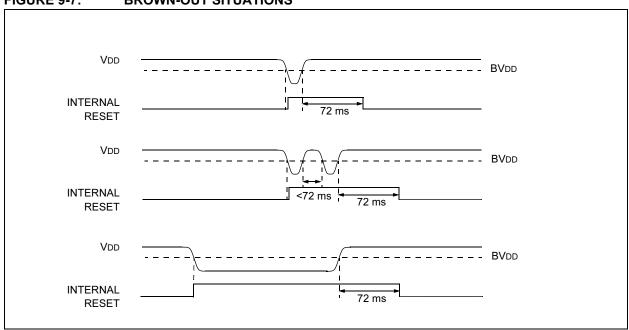

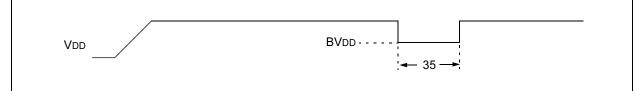

## 9.4.4 BROWN-OUT RESET (BOR)

The PIC16C62X members have on-chip Brown-out Reset circuitry. A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V refer to VBOR parameter D005 (VBOR) for greater than parameter (TBOR) in Table 12-5. The brown-out situation will RESET the chip. A RESET won't occur if VDD falls below 4.0V for less than parameter (TBOR).

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 9-7 shows typical Brown-out situations.

## FIGURE 9-7: BROWN-OUT SITUATIONS

# PIC16C62X

### **FIGURE 9-11: EXTERNAL POWER-ON RESET CIRCUIT (FOR** SLOW VDD POWER-UP) Vdd Vdd D R R1 MCLR PIC16C62X С Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down. **2:** < 40 k $\Omega$ is recommended to make sure that voltage drop across R does not violate the device's electrical specification. **3:** R1 = $100\Omega$ to 1 k $\Omega$ will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin

breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

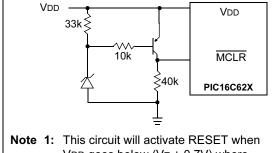

## FIGURE 9-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate RESET when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- **2:** Internal Brown-out Reset circuitry should be disabled when using this circuit.

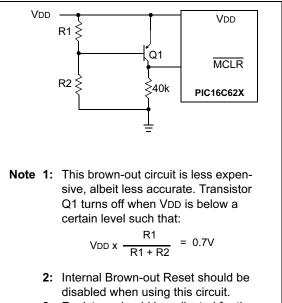

### FIGURE 9-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

**3:** Resistors should be adjusted for the characteristics of the transistor.

### FIGURE 9-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

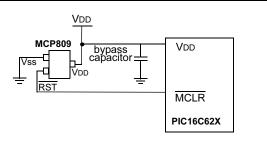

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active RESET pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

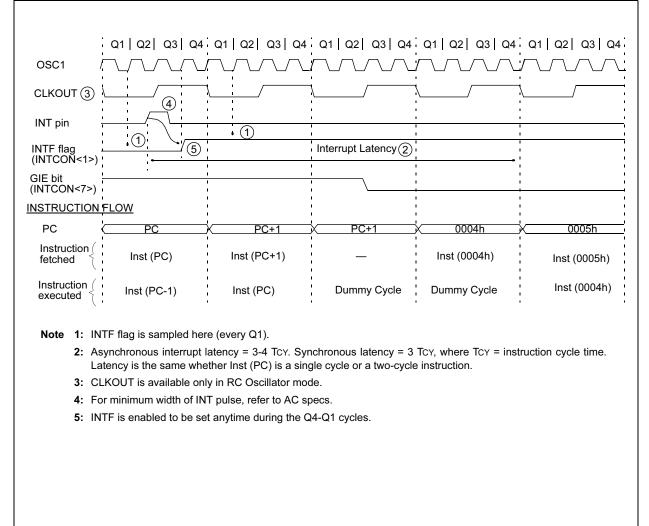

### 9.5.1 RB0/INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered, either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP and Figure 9-18 for timing of wakeup from SLEEP through RB0/INT interrupt.

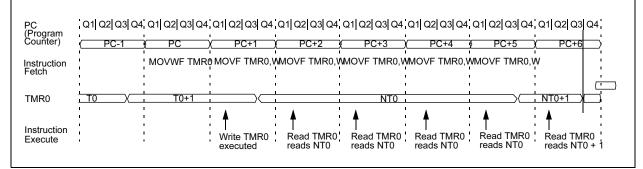

### 9.5.2 TMR0 INTERRUPT

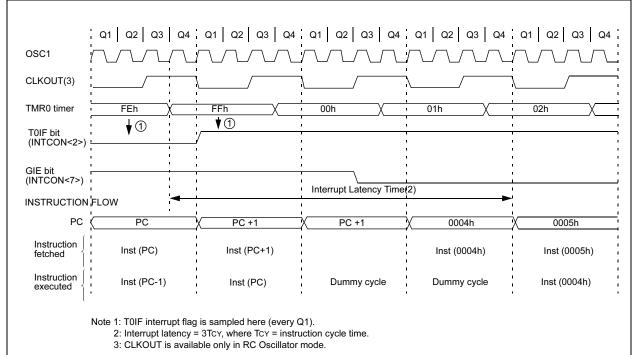

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 6.0.

### 9.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

| Note: | If a change on the I/O pin should occur   |

|-------|-------------------------------------------|

|       | when the read operation is being executed |

|       | (start of the Q2 cycle), then the RBIF    |

|       | interrupt flag may not get set.           |

### 9.5.4 COMPARATOR INTERRUPT

See Section 7.6 for complete description of comparator interrupts.

### FIGURE 9-16: INT PIN INTERRUPT TIMING

# **10.1** Instruction Descriptions

| ADDLW Add Literal and W |                                                                                                                            |  |  |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                 | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |  |  |

| Operands:               | $0 \le k \le 255$                                                                                                          |  |  |  |  |  |  |

| Operation:              | $(W) + k \to (W)$                                                                                                          |  |  |  |  |  |  |

| Status Affected:        | C, DC, Z                                                                                                                   |  |  |  |  |  |  |

| Encoding:               | 11 111x kkkk kkkk                                                                                                          |  |  |  |  |  |  |

| Description:            | The contents of the W register are<br>added to the eight bit literal 'k' and<br>the result is placed in the W<br>register. |  |  |  |  |  |  |

| Words:                  | 1                                                                                                                          |  |  |  |  |  |  |

| Cycles:                 | 1                                                                                                                          |  |  |  |  |  |  |

| Example                 | ADDLW 0x15                                                                                                                 |  |  |  |  |  |  |

|                         | Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25                                                            |  |  |  |  |  |  |

| ANDLW            | AND Literal with W                                                                                                     |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |  |  |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                      |  |  |  |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                      |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                      |  |  |  |  |  |  |  |

| Example          | ANDLW 0x5F                                                                                                             |  |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                        |  |  |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                           |  |  |  |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                    |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                              |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (dest)                                                                                                                                                 |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |  |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                              |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                              |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                              |  |  |  |  |  |

| Example          | ADDWF FSR, <b>O</b>                                                                                                                                                            |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                    |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                           |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |  |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                          |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |  |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                           |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                           |  |  |  |  |  |  |

| Example          | ANDWF FSR, <b>1</b>                                                                                                                                         |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                                 |  |  |  |  |  |  |

| RLF              | Rotate L                                                                                                                                                                                                         | eft f thro             | bugł        | n Carı            | ry   |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|-------------------|------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                         |                        |             |                   |      |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                               |                        |             |                   |      |  |  |  |  |

| Operation:       | See desc                                                                                                                                                                                                         | cription b             | elow        | v                 |      |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                |                        |             |                   |      |  |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                               | 1101                   | df          | ff                | ffff |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |                        |             |                   |      |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                |                        |             |                   | -    |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                |                        |             |                   |      |  |  |  |  |

| Example          | RLF                                                                                                                                                                                                              | REG1,(                 | h           |                   |      |  |  |  |  |

| лапро            | Before In                                                                                                                                                                                                        | struction<br>REG1<br>C |             | 1110<br>0         | 0110 |  |  |  |  |

|                  |                                                                                                                                                                                                                  | REG1<br>W<br>C         | =<br>=<br>= | 1110<br>1100<br>1 |      |  |  |  |  |

| RRF              | Rotate R                                                                                                                                                                                                          | ight f th      | nroug       | gh Ca             | arry     |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-------------------|----------|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                          |                |             |                   |          |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                 |                |             |                   |          |  |  |  |

| Operation:       | See desc                                                                                                                                                                                                          | ription b      | elow        | '                 |          |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |                |             |                   |          |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                                | 1100           | df          | ff                | ffff     |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |                |             |                   |          |  |  |  |

|                  |                                                                                                                                                                                                                   | ; _▶           | Regis       | ter f             | <b>}</b> |  |  |  |

| Words:           | 1                                                                                                                                                                                                                 |                |             |                   |          |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                 |                |             |                   |          |  |  |  |

| Example          | RRF REG1,<br>0                                                                                                                                                                                                    |                |             |                   |          |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                |                |             |                   |          |  |  |  |

|                  | REG1 = 1110 0110<br>C = 0                                                                                                                                                                                         |                |             |                   |          |  |  |  |

|                  | After Inst                                                                                                                                                                                                        |                |             |                   |          |  |  |  |

|                  | 1                                                                                                                                                                                                                 | REG1<br>W<br>C | =<br>=<br>= | 1110<br>0111<br>0 |          |  |  |  |

SLEEP

| <b>VIII</b>                                                                                                                                                                                                                                                          |                                                                                                                                                                         |       |      |      |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|--|--|--|

| Syntax:                                                                                                                                                                                                                                                              | [ label<br>]                                                                                                                                                            | SLEEF | D    |      |  |  |  |

| Operands:                                                                                                                                                                                                                                                            | None                                                                                                                                                                    |       |      |      |  |  |  |

| Operation:                                                                                                                                                                                                                                                           | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow \underline{WDT} \text{ prescaler}, \\ 1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$ |       |      |      |  |  |  |

| Status Affected:                                                                                                                                                                                                                                                     | TO, PD                                                                                                                                                                  |       |      |      |  |  |  |

| Encoding:                                                                                                                                                                                                                                                            | 00                                                                                                                                                                      | 0000  | 0110 | 0011 |  |  |  |

| Description:<br>The power-down STATUS bit,<br>PD is cleared. Time-out<br>STATUS bit, TO is set. Watch-<br>dog Timer and its prescaler are<br>cleared.<br>The processor is put into SLEE<br>mode with the oscillator<br>stopped. See Section 9.8 for<br>more details. |                                                                                                                                                                         |       |      |      |  |  |  |

| Words:                                                                                                                                                                                                                                                               | 1                                                                                                                                                                       |       |      |      |  |  |  |

| Cycles: 1                                                                                                                                                                                                                                                            |                                                                                                                                                                         |       |      |      |  |  |  |

| Example: SLEEP                                                                                                                                                                                                                                                       |                                                                                                                                                                         |       |      |      |  |  |  |

# 11.0 DEVELOPMENT SUPPORT

The PICmicro<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB C30 C Compiler

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- MPLAB dsPIC30 Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup> 1 Demonstration Board

- PICDEM.net<sup>™</sup> Demonstration Board

- PICDEM 2 Plus Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 4 Demonstration Board

- PICDEM 17 Demonstration Board

- PICDEM 18R Demonstration Board

- PICDEM LIN Demonstration Board

- PICDEM USB Demonstration Board

- Evaluation Kits

- KEELOQ®

- PICDEM MSC

- microID®

- CAN

- PowerSmart®

- Analog

# 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- · A full-featured editor with color coded context

- · A multiple project manager

- Customizable data windows with direct edit of contents

- · High level source code debugging

- Mouse over variable inspection

- Extensive on-line help

- The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PICmicro emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files (assembly or C)

- absolute listing file (mixed assembly and C)

- machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost effective simulators, through low cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increasing flexibility and power.

## 11.2 MPASM Assembler

The MPASM assembler is a full-featured, universal macro assembler for all PICmicro MCUs.

The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects

- · User defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

# 12.0 ELECTRICAL SPECIFICATIONS

## Absolute Maximum Ratings †

| Ambient Temperature under bias                                                                                 | 40° to +125°C                  |

|----------------------------------------------------------------------------------------------------------------|--------------------------------|

| Storage Temperature                                                                                            | 65° to +150°C                  |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                   | 0.6V to VDD +0.6V              |

| Voltage on VDD with respect to Vss                                                                             | 0 to +7.5V                     |

| Voltage on MCLR with respect to Vss (Note 2)                                                                   | 0 to +14V                      |

| Voltage on RA4 with respect to Vss                                                                             |                                |

| Total power Dissipation (Note 1)                                                                               | 1.0W                           |

| Maximum Current out of Vss pin                                                                                 | 300 mA                         |

| Maximum Current into VDD pin                                                                                   | 250 mA                         |

| Input Clamp Current, Iк (Vi <0 or Vi> VDD)                                                                     | ±20 mA                         |

| Output Clamp Current, Iок (Vo <0 or Vo>VoD)                                                                    | ±20 mA                         |

| Maximum Output Current sunk by any I/O pin                                                                     | 25 mA                          |

| Maximum Output Current sourced by any I/O pin                                                                  | 25 mA                          |

| Maximum Current sunk by PORTA and PORTB                                                                        | 200 mA                         |

| Maximum Current sourced by PORTA and PORTB                                                                     | 200 mA                         |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) | x IOH} + $\Sigma$ (VOI x IOL). |

2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latchup. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

**† NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| PIC16CR62XA-04<br>PIC16CR62XA-20 | $\begin{array}{l lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                    |  |  |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIC16LCR62XA-04                  | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq$ TA $\leq$ +85°C for industrial and0°C $\leq$ TA $\leq$ +70°C for commercial and $-40^{\circ}$ C $\leq$ TA $\leq$ +125°C for extended |  |  |  |  |

| Param. Sym Characteristic No.    | Min Typ† Max Units Conditions                                                                                                                                                                                                            |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in k $\Omega$ .

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

# 12.6 DC Characteristics:

# PIC16C620A/C621A/C622A-40<sup>(3)</sup> (Commercial) PIC16CR620A-40<sup>(3)</sup> (Commercial)

| DC CHARACTERISTICS<br>Power Supply Pins |      |        |                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |          |                                                                          |  |

|-----------------------------------------|------|--------|--------------------|------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------|--|

| Characteristic                          | Sym  | Min    | Typ <sup>(1)</sup> | Мах                                                                                                                                | Units    | Conditions                                                               |  |

| Supply Voltage                          | Vdd  | 4.5    | —                  | 5.5                                                                                                                                | V        | HS Option from 20 - 40 MHz                                               |  |

| Supply Current <sup>(2)</sup>           | IDD  | _      | 5.5<br>7.7         | 11.5<br>16                                                                                                                         | mA<br>mA | Fosc = 40 MHz, VDD = 4.5V, HS mode<br>Fosc = 40 MHz, VDD = 5.5V, HS mode |  |

| HS Oscillator Operating<br>Frequency    | Fosc | 20     | _                  | 40                                                                                                                                 | MHz      | OSC1 pin is externally driven,<br>OSC2 pin not connected                 |  |

| Input Low Voltage OSC1                  | VIL  | Vss    | —                  | 0.2Vdd                                                                                                                             | V        | HS mode, OSC1 externally driven                                          |  |

| Input High Voltage OSC1                 | Vih  | 0.8Vdd |                    | Vdd                                                                                                                                | V        | HS mode, OSC1 externally driven                                          |  |

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss,

T0CKI = VDD,  $\overline{MCLR}$  = VDD; WDT disabled, HS mode with OSC2 not connected.

**3:** For device operation between DC and 20 MHz. See Table 12-1 and Table 12-2.

# 12.7 AC Characteristics: PIC16C620A/C621A/C622A-40<sup>(2)</sup> (Commercial) PIC16CR620A-40<sup>(2)</sup> (Commercial)

|                                                              |            |    |                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercia |       |                                      |  |

|--------------------------------------------------------------|------------|----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------|--|

| Characteristic Sym Min                                       |            |    | Typ <sup>(1)</sup> | Max                                                                                                                               | Units | Conditions                           |  |

| External CLKIN Frequency                                     | Fosc       | 20 | —                  | 40                                                                                                                                | MHz   | HS mode, OSC1 externally driven      |  |

| External CLKIN Period                                        | Tosc       | 25 | _                  | 50                                                                                                                                | ns    | HS mode (40), OSC1 externally driven |  |

| Clock in (OSC1) Low or High Time                             | TosL, TosH | 6  | —                  |                                                                                                                                   | ns    | HS mode, OSC1 externally driven      |  |

| Clock in (OSC1) Rise or Fall Time                            | TosR, TosF |    | _                  | 6.5                                                                                                                               | ns    | HS mode, OSC1 externally driven      |  |

| OSC1↑ (Q1 cycle) to Port out valid                           | TosH2ıoV   |    | —                  | 100                                                                                                                               | ns    | _                                    |  |

| OSC1↑ (Q2 cycle) to Port input<br>invalid (I/O in hold time) | TosH2iol   | 50 | —                  | _                                                                                                                                 | ns    | —                                    |  |

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: For device operation between DC and 20 MHz. See Table 12-1 and Table 12-2.

# FIGURE 12-14: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

### FIGURE 12-15: BROWN-OUT RESET TIMING

# TABLE 12-5:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                | Min  | Тур†      | Max  | Units | Conditions                       |

|------------------|-------|-----------------------------------------------|------|-----------|------|-------|----------------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                        | 2000 | —         | _    | ns    | -40° to +85°C                    |

| 31               | Twdt  | Watchdog Timer Time-out Period (No Prescaler) | 7*   | 18        | 33*  | ms    | VDD = 5.0V, -40° to +85°C        |

| 32               | Tost  | Oscillation Start-up Timer Period             | _    | 1024 Tosc | _    |       | Tosc = OSC1 period               |

| 33               | Tpwrt | Power-up Timer Period                         | 28*  | 72        | 132* | ms    | VDD = 5.0V, -40° to +85°C        |

| 34               | Tioz  | I/O hi-impedance from MCLR low                |      | —         | 2.0  | μS    |                                  |

| 35               | TBOR  | Brown-out Reset Pulse Width                   | 100* | _         |      | μS    | $3.7V \leq V\text{DD} \leq 4.3V$ |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C62X

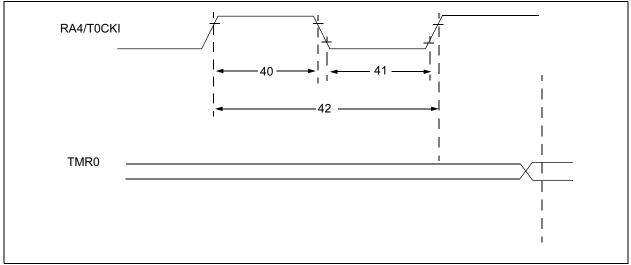

## FIGURE 12-16: TIMER0 CLOCK TIMING

| TABLE 12-6: | TIMER0 CLOCK REQUIREMENTS |

|-------------|---------------------------|

|-------------|---------------------------|

| Parameter<br>No. | Sym  | Characteristic         |                | Min                    | Тур† | Max | Units | Conditions                            |

|------------------|------|------------------------|----------------|------------------------|------|-----|-------|---------------------------------------|

| 40               | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5 Tcy + 20*          | —    | _   | ns    |                                       |

|                  |      |                        | With Prescaler | 10*                    | —    | —   | ns    |                                       |

| 41               | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5 Tcy + 20*          | —    | _   | ns    |                                       |

|                  |      |                        | With Prescaler | 10*                    | —    | _   | ns    |                                       |

| 42               | Tt0P | T0CKI Period           |                | <u>Tcy + 40</u> *<br>N | _    | _   | ns    | N = prescale value<br>(1, 2, 4,, 256) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

# WORLDWIDE SALES AND SERVICE

### AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

### Atlanta

3780 Mansell Road, Suite 130 Alpharetta, GA 30022 Tel: 770-640-0034 Fax: 770-640-0307

### Boston

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

### Chicago

333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

### Dallas

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

### Detroit

Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260

### Kokomo

2767 S. Albright Road Kokomo, Indiana 46902 Tel: 765-864-8360 Fax: 765-864-8387

### Los Angeles

18201 Von Karman, Suite 1090 Irvine, CA 92612 Tel: 949-263-1888 Fax: 949-263-1338

#### Phoenix

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-4338

### San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

#### Toronto