Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 896B (512 x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 96 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c620a-40-p |

#### **Table of Contents**

| 1.0    | General Description                 | 5    |

|--------|-------------------------------------|------|

| 2.0    | PIC16C62X Device Varieties          |      |

| 3.0    | Architectural Overview              | 9    |

| 4.0    | Memory Organization                 | . 13 |

| 5.0    | I/O Ports                           | 25   |

| 6.0    | Timer0 Module                       |      |

| 7.0    | Comparator Module                   |      |

| 8.0    | Voltage Reference Module            |      |

| 9.0    | Special Features of the CPU         |      |

| 10.0   | Instruction Set Summary             | . 61 |

| 11.0   | Development Support                 |      |

| 12.0   | Electrical Specifications           | . 81 |

| 13.0   | Device Characterization Information |      |

| 14.0   | Packaging Information               |      |

|        | dix A: Enhancements                 |      |

| Append | dix B: Compatibility                | 119  |

|        |                                     |      |

| On-Lin | e Support                           | 123  |

| System | ns Information and Upgrade Hot Line | 123  |

|        | r Response                          |      |

| Produc | t Identification System             | 125  |

|        |                                     |      |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

#### 1.0 GENERAL DESCRIPTION

The PIC16C62X devices are 18 and 20-Pin ROM/EPROM-based members of the versatile PICmicro® family of low cost, high performance, CMOS, fully-static, 8-bit microcontrollers.

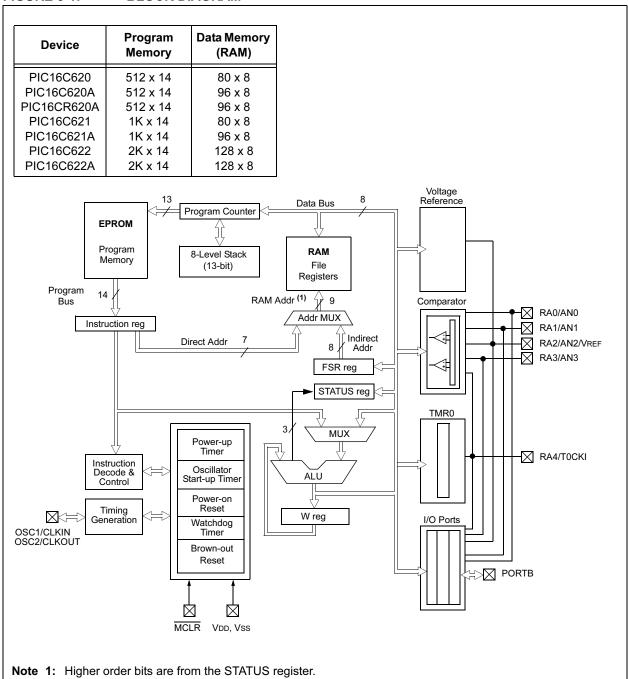

All PICmicro microcontrollers employ an advanced RISC architecture. The PIC16C62X devices have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16C62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC16C620A, PIC16C621A and PIC16CR620A have 96 bytes of RAM. The PIC16C622(A) has 128 bytes of RAM. Each device has 13 I/O pins and an 8-bit timer/counter with an 8-bit programmable prescaler. In addition, the PIC16C62X adds two analog comparators with a programmable on-chip voltage reference module. The comparator module is ideally suited for applications requiring a low cost analog interface (e.g., battery chargers, threshold detectors, white goods controllers, etc).

PIC16C62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (Power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external and internal interrupts and RESET.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock- up.

A UV-erasable CERDIP-packaged version is ideal for code development while the cost effective One-Time-Programmable (OTP) version is suitable for production in any volume.

Table 1-1 shows the features of the PIC16C62X midrange microcontroller families.

A simplified block diagram of the PIC16C62X is shown in Figure 3-1.

The PIC16C62X series fits perfectly in applications ranging from battery chargers to low power remote sensors. The EPROM technology makes

customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C62X very versatile.

## 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to PIC16C62X family of devices (Appendix B). The PIC16C62X family fills the niche for users wanting to migrate up from the PIC16C5X family and not needing various peripheral features of other members of the PIC16XX mid-range microcontroller family.

### 1.2 Development Support

The PIC16C62X family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low cost development programmer and a full-featured programmer. Third Party "C" compilers are also available.

FIGURE 3-1: BLOCK DIAGRAM

TABLE 3-1: PIC16C62X PINOUT DESCRIPTION

| Name         | DIP/SOIC<br>Pin # | SSOP<br>Pin# | I/O/P Type | Buffer<br>Type        | Description                                                                                                                                                                                              |

|--------------|-------------------|--------------|------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 16                | 18           | I          | ST/CMOS               | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT  | 15                | 17           | 0          | _                     | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. In RC mode, OSC2 pin outputs CLKOUT, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate. |

| MCLR/VPP     | 4                 | 4            | I/P        | ST                    | Master Clear (Reset) input/programming voltage input. This pin is an Active Low Reset to the device.                                                                                                     |

|              |                   |              |            |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0/AN0      | 17                | 19           | I/O        | ST                    | Analog comparator input                                                                                                                                                                                  |

| RA1/AN1      | 18                | 20           | I/O        | ST                    | Analog comparator input                                                                                                                                                                                  |

| RA2/AN2/VREF | 1                 | 1            | I/O        | ST                    | Analog comparator input or VREF output                                                                                                                                                                   |

| RA3/AN3      | 2                 | 2            | I/O        | ST                    | Analog comparator input /output                                                                                                                                                                          |

| RA4/T0CKI    | 3                 | 3            | I/O        | ST                    | Can be selected to be the clock input to the Timer0 timer/counter or a comparator output. Output is open drain type.                                                                                     |

|              |                   |              |            |                       | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                            |

| RB0/INT      | 6                 | 7            | I/O        | TTL/ST <sup>(1)</sup> | RB0/INT can also be selected as an external interrupt pin.                                                                                                                                               |

| RB1          | 7                 | 8            | I/O        | TTL                   |                                                                                                                                                                                                          |

| RB2          | 8                 | 9            | I/O        | TTL                   |                                                                                                                                                                                                          |

| RB3          | 9                 | 10           | I/O        | TTL                   |                                                                                                                                                                                                          |

| RB4          | 10                | 11           | I/O        | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                 |

| RB5          | 11                | 12           | I/O        | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                 |

| RB6          | 12                | 13           | I/O        | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming clock.                                                                                                                                                       |

| RB7          | 13                | 14           | I/O        | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming data.                                                                                                                                                        |

| Vss          | 5                 | 5,6          | Р          | _                     | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| VDD          | 14                | 15,16        | Р          | _                     | Positive supply for logic and I/O pins.                                                                                                                                                                  |

Legend:

O = output — = Not used TTL = TTL input I/O = input/output I = Input P = power

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

### 4.2.2.2 OPTION Register

The OPTION register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT (PSA = 1).

### REGISTER 4-2: OPTION REGISTER (ADDRESS 81H)

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

bit 5 **T0CS**: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/T0CKI pin

bit 3 **PSA**: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS<2:0>**: Prescaler Rate Select bits

| Bit Value | e TMR0 Rate | WDT Rate |

|-----------|-------------|----------|

| 000       | 1:2         | 1:1      |

| 001       | 1:4         | 1:2      |

| 010       | 1:8         | 1:4      |

| 011       | 1 : 16      | 1:8      |

| 100       | 1:32        | 1:16     |

| 101       | 1:64        | 1:32     |

| 110       | 1 : 128     | 1:64     |

| 111       | 1:256       | 1 : 128  |

| Legend:            |                  |                                           |  |

|--------------------|------------------|-------------------------------------------|--|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'        |  |

| - n = Value at POR | '1' = Rit is set | '0' = Rit is cleared $x = Rit$ is unknown |  |

### 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading the port register reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (ex., BCF, BSF, etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

# EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

```

; Initial PORT settings:

PORTB<7:4> Inputs

PORTB<3:0> Outputs

; PORTB<7:6> have external pull-up and are not

; connected to other circuitry

PORT latch PORT pins

BCF PORTB, 7

; 01pp pppp

11pp pppp

11pp

PORTB, 6

; 10pp

pppp

qqqq

BSF STATUS, RPO

TRISB, 7

; 10pp pppp

11pp pppp

BCF TRISB, 6

; 10pp pppp

10pp pppp

; Note that the user may have expected the pin

; values to be 00pp pppp. The 2nd BCF caused

; RB7 to be latched as the pin value (High).

```

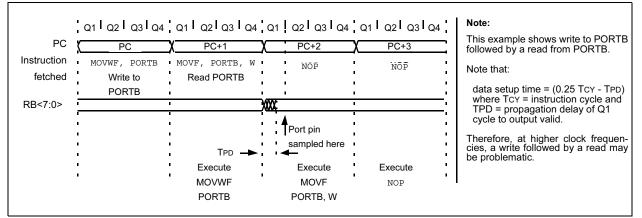

## 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-7). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

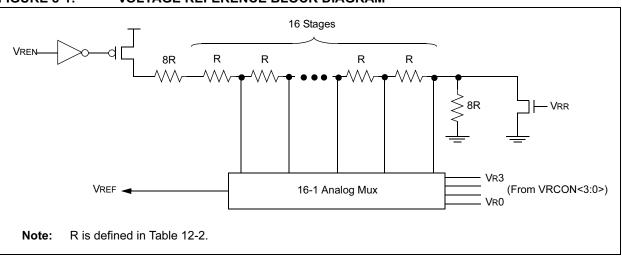

# 8.0 VOLTAGE REFERENCE MODULE

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Register 8-1. The block diagram is given in Figure 8-1.

### 8.1 Configuring the Voltage Reference

The Voltage Reference can output 16 distinct voltage levels for each range. The equations used to calculate the output of the Voltage Reference are as follows:

if

$$VRR = 0$$

:  $VREF = (VDD x 1/4) + (VR < 3:0 > /32) x VDD$

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 12-1). Example 8-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

### REGISTER 8-1: VRCON REGISTER(ADDRESS 9Fh)

| R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----|-------|-------|-------|-------|

| VREN  | VROE  | VRR   | _   | VR3   | VR2   | VR1   | VR0   |

| bit 7 |       |       |     |       |       |       | bit 0 |

bit 7 VREN: VREF Enable

1 = VREF circuit powered on

0 = VREF circuit powered down, no IDD drain

bit 6 **VROE:** VREF Output Enable

1 = VREF is output on RA2 pin

0 = VREF is disconnected from RA2 pin

bit 5 VRR: VREF Range selection

1 = Low Range

0 = High Range

bit 4 Unimplemented: Read as '0'

bit 3-0 **VR<3:0>**: VREF value selection  $0 \le VR$  [3:0]  $\le 15$

when VRR = 1: VREF = (VR<3:0>/ 24) \* VDD

when VRR = 0: VREF = 1/4 \* VDD + (VR<3:0>/ 32) \* VDD

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### FIGURE 8-1: VOLTAGE REFERENCE BLOCK DIAGRAM

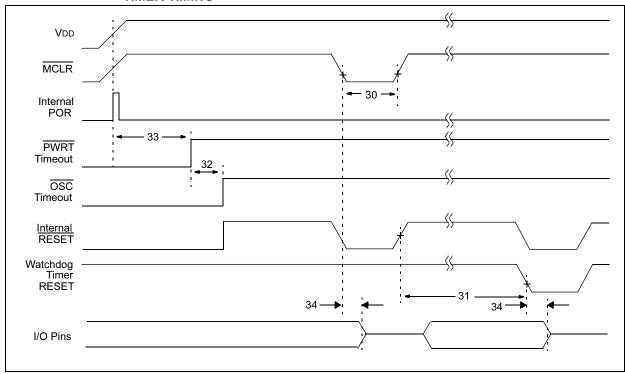

#### 9.3 RESET

The PIC16C62X differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) WDT Reset (normal operation)

- e) WDT wake-up (SLEEP)

- f) Brown-out Reset (BOR)

Some registers are not affected in any RESET condition Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset,

MCLR Reset, WDT Reset and MCLR Reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 9-2. These bits are used in software to determine the nature of the RESET. See Table 9-5 for a full description of RESET states of all registers.

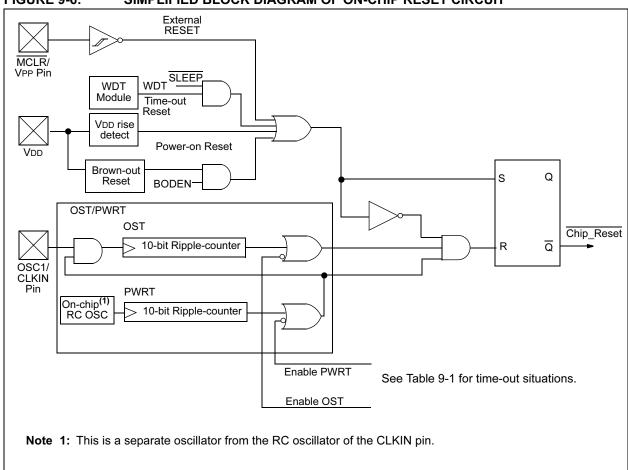

A simplified block diagram of the on-chip RESET circuit is shown in Figure 9-6.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See Table 12-5 for pulse width specification.

#### FIGURE 9-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

# **PIC16C62X**

| CLRW                                                                        | Clear W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | COMF                                                                                 | Complement f                                                                                                                |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                     | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Syntax:                                                                              | [ label ] COMF f,d                                                                                                          |

| Operands:                                                                   | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Operands:                                                                            | $0 \le f \le 127$                                                                                                           |

| Operation:                                                                  | $00h \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                      | d ∈ [0,1]                                                                                                                   |

|                                                                             | $1 \rightarrow Z$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Operation:                                                                           | $(\bar{f}) \rightarrow (dest)$                                                                                              |

| Status Affected:                                                            | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Status Affected:                                                                     | Z                                                                                                                           |

| Encoding:                                                                   | 00 0001 0000 0011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Encoding:                                                                            | 00 1001 dfff ffff                                                                                                           |

| Description:                                                                | W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description:                                                                         | The contents of register 'f' are complemented. If 'd' is 0, the                                                             |

| Words:                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                      | result is stored in W. If 'd' is 1, the result is stored back in register 'f'.                                              |

| Cycles:                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Words:                                                                               | 1                                                                                                                           |

| Example                                                                     | CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Cycles:                                                                              | 1                                                                                                                           |

|                                                                             | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                                                                    |                                                                                                                             |

|                                                                             | W = 0x5A<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Example                                                                              | ,                                                                                                                           |

|                                                                             | W = 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                      | Before Instruction<br>REG1 = 0x13                                                                                           |

|                                                                             | Z = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                      | After Instruction                                                                                                           |

|                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                      | REG1 = 0x13  W = 0xEC                                                                                                       |

| CLRWDT                                                                      | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                      | W OXES                                                                                                                      |

| Syntax:                                                                     | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                      |                                                                                                                             |

| - j · · · · · · ·                                                           | [1450] 02.1115.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DEAL                                                                                 | 5                                                                                                                           |

| Operands:                                                                   | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DECF                                                                                 | Decrement f                                                                                                                 |

| •                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Syntax:                                                                              | [label] DECF f,d                                                                                                            |

| Operands:                                                                   | None $00h \rightarrow WDT$ $0 \rightarrow \underline{WDT} \text{ prescaler,}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                      | [ label ] DECF f,d<br>0 ≤ f ≤ 127                                                                                           |

| Operands:                                                                   | None $00h \rightarrow WDT$ $0 \rightarrow \underline{WDT} \text{ prescaler,}$ $1 \rightarrow \underline{TO}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Syntax:<br>Operands:                                                                 | [ label ] DECF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$                                                                    |

| Operands: Operation:                                                        | None $00h \rightarrow WDT$ $0 \rightarrow \underline{WDT}$ prescaler, $1 \rightarrow \underline{TO}$ $1 \rightarrow PD$                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Syntax: Operands: Operation:                                                         | [ label ] DECF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest)                                    |

| Operands: Operation: Status Affected:                                       | None $00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$                                                                                                                                                                                                                                                                                                                                                                                                                       | Syntax: Operands: Operation: Status Affected:                                        | [ label ] DECF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest)                                    |

| Operands: Operation: Status Affected: Encoding:                             | None $00h \rightarrow WDT$ $0 \rightarrow \underline{WDT} \text{ prescaler,}$ $1 \rightarrow \underline{TO}$ $1 \rightarrow \underline{PD}$ $\overline{TO}, \overline{PD}$ $00 \qquad 0000 \qquad 0110 \qquad 0100$                                                                                                                                                                                                                                                                                                                                                                | Syntax: Operands: Operation: Status Affected: Encoding:                              | [ label ] DECF f,d $0 \le f \le 127$ $d \in [0,1]$ $(f) - 1 \rightarrow (dest)$ Z $00 \qquad 0011 \qquad dfff \qquad fffff$ |

| Operands: Operation: Status Affected:                                       | None $00h \rightarrow WDT$ $0 \rightarrow \underline{WDT} \text{ prescaler,}$ $1 \rightarrow \underline{TO}$ $1 \rightarrow \underline{PD}$ $\overline{TO}, \overline{PD}$ $00 \qquad 0000 \qquad 0110 \qquad 0100$ CLRWDT instruction resets the                                                                                                                                                                                                                                                                                                                                  | Syntax: Operands: Operation: Status Affected:                                        |                                                                                                                             |

| Operands: Operation: Status Affected: Encoding:                             | None $00h \rightarrow WDT$ $0 \rightarrow \underline{WDT} \text{ prescaler,}$ $1 \rightarrow \underline{TO}$ $1 \rightarrow \underline{PD}$ $\overline{TO}, \overline{PD}$ $00 \qquad 0000 \qquad 0110 \qquad 0100$                                                                                                                                                                                                                                                                                                                                                                | Syntax: Operands: Operation: Status Affected: Encoding:                              | [ label ] DECF f,d $0 \le f \le 127$ $d \in [0,1]$ $(f) - 1 \rightarrow (dest)$ Z $00 \qquad 0011 \qquad dfff \qquad fffff$ |

| Operands: Operation: Status Affected: Encoding:                             | None $00h \rightarrow WDT$ $0 \rightarrow \underline{W}DT \text{ prescaler,}$ $1 \rightarrow \underline{TO}$ $1 \rightarrow \underline{PD}$ $\overline{TO}, \overline{PD}$ $00 \qquad 0000 \qquad 0110 \qquad 0100$ $CLRWDT \text{ instruction resets the}$ $Watchdog Timer. It also resets the$                                                                                                                                                                                                                                                                                   | Syntax: Operands: Operation: Status Affected: Encoding:                              |                                                                                                                             |

| Operands: Operation: Status Affected: Encoding:                             | None $00h \rightarrow WDT$ $0 \rightarrow \underline{W}DT$ prescaler, $1 \rightarrow \overline{TO}$ $1 \rightarrow PD$ $\overline{TO}$ , $\overline{PD}$ $00  0000  0110  0100$ CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. STATUS                                                                                                                                                                                                                                                                                                      | Syntax: Operands: Operation: Status Affected: Encoding:                              |                                                                                                                             |

| Operands: Operation: Status Affected: Encoding: Description:                | None $00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$ $00 \qquad 0000 \qquad 0110 \qquad 0100$ $CLRWDT \text{ instruction resets the}$ $Watchdog Timer. \text{ It also resets the}$ $\text{prescaler of } \underline{\text{the}} \text{ WDT. STATUS}$ $\text{bits } \overline{TO} \text{ and } \overline{PD} \text{ are set.}$                                                                                                                                              | Syntax: Operands: Operation: Status Affected: Encoding: Description:                 |                                                                                                                             |

| Operands: Operation: Status Affected: Encoding: Description:                | None $00h \rightarrow WDT$ $0 \rightarrow \underline{WDT} \text{ prescaler,}$ $1 \rightarrow \underline{TO}$ $1 \rightarrow \underline{PD}$ $\overline{TO}, \overline{PD}$ $00 \qquad 0000 \qquad 0110 \qquad 0100$ $CLRWDT \text{ instruction resets the}$ $Watchdog Timer. \text{ It also resets the}$ $prescaler \text{ of the WDT. STATUS}$ $bits \overline{TO} \text{ and } \overline{PD} \text{ are set.}$ $1$                                                                                                                                                               | Syntax: Operands: Operation: Status Affected: Encoding: Description:                 |                                                                                                                             |

| Operands: Operation: Status Affected: Encoding: Description: Words: Cycles: | None $00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$ $00 \qquad 0000 \qquad 0110 \qquad 0100$ $CLRWDT \text{ instruction resets the}$ $Watchdog Timer. \text{ It also resets the}$ $PD \text{ prescaler of the WDT. STATUS}$ $Dits \overline{TO} \text{ and } \overline{PD} \text{ are set.}$ $1$ $1$ $CLRWDT$ $Defore Instruction$                                                                                                                                        | Syntax: Operands: Operation: Status Affected: Encoding: Description:  Words: Cycles: |                                                                                                                             |

| Operands: Operation: Status Affected: Encoding: Description: Words: Cycles: | None $00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$ $00 \qquad 0000 \qquad 0110 \qquad 0100$ $CLRWDT \text{ instruction resets the }$ $Watchdog Timer. \text{ It also resets the }$ $PD \text{ prescaler of the WDT. STATUS}$ $\text{bits } \overline{TO} \text{ and } \overline{PD} \text{ are set.}$ $1$ $1$ $CLRWDT$ $Before \text{ Instruction }$ $WDT \text{ counter } = ?$                                                                                          | Syntax: Operands: Operation: Status Affected: Encoding: Description:  Words: Cycles: |                                                                                                                             |

| Operands: Operation: Status Affected: Encoding: Description: Words: Cycles: | None $00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$ $00 \qquad 0000 \qquad 0110 \qquad 0100$ $CLRWDT \text{ instruction resets the}$ $Watchdog Timer. \text{ It also resets the}$ $PD \text{ prescaler of the WDT. STATUS}$ $Dits \overline{TO} \text{ and } \overline{PD} \text{ are set.}$ $1$ $1$ $CLRWDT$ $Defore Instruction$                                                                                                                                        | Syntax: Operands: Operation: Status Affected: Encoding: Description:  Words: Cycles: |                                                                                                                             |

| Operands: Operation: Status Affected: Encoding: Description: Words: Cycles: | None $00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$ $00 \qquad 0000 \qquad 0110 \qquad 0100$ $CLRWDT \text{ instruction resets the}$ $Watchdog Timer. \text{ It also resets the}$ $\text{prescaler of the WDT. STATUS}$ $\text{bits } \overline{TO} \text{ and } \overline{PD} \text{ are set.}$ $1$ $1$ $CLRWDT$ $\text{Before Instruction}$ $WDT \text{ counter } = ?$ $\text{After Instruction}$ $WDT \text{ counter } = 0x00$ $\underline{WDT} \text{ prescaler} = 0$ | Syntax: Operands: Operation: Status Affected: Encoding: Description:  Words: Cycles: |                                                                                                                             |

| Operands: Operation: Status Affected: Encoding: Description: Words: Cycles: | None $00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$ $00 \qquad 0000 \qquad 0110 \qquad 0100$ $CLRWDT \text{ instruction resets the}$ $Watchdog Timer. \text{ It also resets the}$ $prescaler of \underline{the} WDT. STATUS$ $bits \overline{TO} \text{ and } \overline{PD} \text{ are set.}$ $1$ $1$ $CLRWDT$ $Before Instruction$ $WDT counter = ?$ $After Instruction$ $WDT counter = 0x00$                                                                            | Syntax: Operands: Operation: Status Affected: Encoding: Description:  Words: Cycles: |                                                                                                                             |

| RLF              | Rotate Left f through Carry                                                                                                                                                                       |              |     |           |      |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|-----------|------|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                         | RLF          | f,d |           |      |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                |              |     |           |      |  |  |  |

| Operation:       | See description below                                                                                                                                                                             |              |     |           |      |  |  |  |

| Status Affected: | С                                                                                                                                                                                                 |              |     |           |      |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                | 1101         | df: | ff        | ffff |  |  |  |

| Description:     | The contents of register 'f' are rotated one bit to the left through the Carry Flag. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is stored back in register 'f'. |              |     |           |      |  |  |  |

| Words:           | 1                                                                                                                                                                                                 |              |     |           |      |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                 |              |     |           |      |  |  |  |

| Example          | RLF                                                                                                                                                                                               | REG1,        | )   |           |      |  |  |  |

|                  | Before In                                                                                                                                                                                         | struction    | 1   |           |      |  |  |  |

|                  |                                                                                                                                                                                                   | REG1         | =   | 1110      | 0110 |  |  |  |

|                  | After Inst                                                                                                                                                                                        | c<br>ruction | =   | 0         |      |  |  |  |

|                  |                                                                                                                                                                                                   | REG1         | =   | 1110      | 0110 |  |  |  |

|                  |                                                                                                                                                                                                   | W<br>C       | =   | 1100<br>1 | 1100 |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                       |                |             |         |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|---------|--|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                          | RRF f          | ,d          |         |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                 |                |             |         |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                              |                |             |         |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                  |                |             |         |  |  |  |  |

| Encoding:        | 00 1100 dfff ffff                                                                                                                                                                                  |                |             |         |  |  |  |  |

| Description:     | The contents of register 'f' are rotated one bit to the right through the Carry Flag. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |                |             |         |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                  |                |             |         |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                  |                |             |         |  |  |  |  |

| Example          | RRF                                                                                                                                                                                                |                | REG1,<br>0  |         |  |  |  |  |

|                  | Before In                                                                                                                                                                                          | struction      | 1           |         |  |  |  |  |

|                  |                                                                                                                                                                                                    | REG1<br>C      | = 11<br>= 0 | 10 0110 |  |  |  |  |

|                  | After Inst                                                                                                                                                                                         |                |             |         |  |  |  |  |

|                  |                                                                                                                                                                                                    | REG1<br>W<br>C |             | 10 0110 |  |  |  |  |

|                  |                                                                                                                                                                                                    |                |             |         |  |  |  |  |

## **SLEEP** Syntax:

|                  | j .                                                                                                                                                                                                                           |      |      |      |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--|--|--|--|

| Operands:        | None                                                                                                                                                                                                                          |      |      |      |  |  |  |  |

| Operation:       | 00h → WDT,<br>0 → WDT prescaler,                                                                                                                                                                                              |      |      |      |  |  |  |  |

|                  | $ \begin{array}{c} 1 \to \overline{\text{TO}}, \\ 0 \to \overline{\text{PD}} \end{array} $                                                                                                                                    |      |      |      |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                        |      |      |      |  |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                                            | 0000 | 0110 | 0011 |  |  |  |  |

| Description:     | The power-down STATUS bit, PD is cleared. Time-out STATUS bit, TO is set. Watch- dog Timer and its prescaler are cleared. The processor is put into SLEEP mode with the oscillator stopped. See Section 9.8 for more details. |      |      |      |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                             |      |      |      |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                             |      |      |      |  |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                         |      |      |      |  |  |  |  |

[ label

SLEEP

# 11.9 MPLAB ICE 2000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 2000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers. Software control of the MPLAB ICE 2000 in-circuit emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PICmicro microcontrollers.

The MPLAB ICE 2000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

# 11.10 MPLAB ICE 4000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 4000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for highend PICmicro microcontrollers. Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICD 4000 is a premium emulator system, providing the features of MPLAB ICE 2000, but with increased emulation memory and high speed performance for dsPIC30F and PIC18XXXX devices. Its advanced emulator features include complex triggering and timing, up to 2 Mb of emulation memory, and the ability to view variables in real-time.

The MPLAB ICE 4000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

### 11.11 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low cost, run-time development tool, connecting to the host PC via an RS-232 or high speed USB interface. This tool is based on the FLASH PICmicro MCUs and can be used to develop for these and other PICmicro microcontrollers. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming™ (ICSP™) protocol, offers cost effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single-stepping and watching variables, CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real-time. MPLAB ICD 2 also serves as a development programmer for selected PICmicro devices.

# 11.12 PRO MATE II Universal Device Programmer

The PRO MATE II is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features an LCD display for instructions and error messages and a modular detachable socket assembly to support various package types. In Stand-Alone mode, the PRO MATE II device programmer can read, verify, and program PICmicro devices without a PC connection. It can also set code protection in this mode.

# 11.13 PICSTART Plus Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus development programmer supports most PICmicro devices up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

# 11.20 PICDEM 18R PIC18C601/801 Demonstration Board

The PICDEM 18R demonstration board serves to assist development of the PIC18C601/801 family of Microchip microcontrollers. It provides hardware implementation of both 8-bit Multiplexed/De-multiplexed and 16-bit Memory modes. The board includes 2 Mb external FLASH memory and 128 Kb SRAM memory, as well as serial EEPROM, allowing access to the wide range of memory types supported by the PIC18C601/801.

# 11.21 PICDEM LIN PIC16C43X Demonstration Board

The powerful LIN hardware and software kit includes a series of boards and three PICmicro microcontrollers. The small footprint PIC16C432 and PIC16C433 are used as slaves in the LIN communication and feature on-board LIN transceivers. A PIC16F874 FLASH microcontroller serves as the master. All three microcontrollers are programmed with firmware to provide LIN bus communication.

### 11.22 PICkit<sup>™</sup> 1 FLASH Starter Kit

A complete "development system in a box", the PICkit FLASH Starter Kit includes a convenient multi-section board for programming, evaluation, and development of 8/14-pin FLASH PIC® microcontrollers. Powered via USB, the board operates under a simple Windows GUI. The PICkit 1 Starter Kit includes the user's guide (on CD ROM), PICkit 1 tutorial software and code for various applications. Also included are MPLAB® IDE (Integrated Development Environment) software, software and hardware "Tips 'n Tricks for 8-pin FLASH PIC® Microcontrollers" Handbook and a USB Interface Cable. Supports all current 8/14-pin FLASH PIC microcontrollers, as well as many future planned devices.

# 11.23 PICDEM USB PIC16C7X5 Demonstration Board

The PICDEM USB Demonstration Board shows off the capabilities of the PIC16C745 and PIC16C765 USB microcontrollers. This board provides the basis for future USB products.

## 11.24 Evaluation and Programming Tools

In addition to the PICDEM series of circuits, Microchip has a line of evaluation kits and demonstration software for these products.

- KEELOQ evaluation and programming tools for Microchip's HCS Secure Data Products

- CAN developers kit for automotive network applications

- · Analog design boards and filter design software

- PowerSmart battery charging evaluation/ calibration kits

- IrDA<sup>®</sup> development kit

- microID development and rfLab<sup>™</sup> development software

- SEEVAL® designer kit for memory evaluation and endurance calculations

- PICDEM MSC demo boards for Switching mode power supply, high power IR driver, delta sigma ADC, and flow rate sensor

Check the Microchip web page and the latest Product Line Card for the complete list of demonstration and evaluation kits.

# 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended) (CONT.)

|                                                                  |                                                           |                                                                                                                                                                                                                                                                                                         | Stan             | dard O                                                                                                                                                                                                                                                                                                                                                                  | perati                                                   | ng Con                                                                                                                                | ditions (unless otherwise stated)                                                                                       |  |  |