Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 96 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c620a-40-so |

NOTES:

NOTES:

### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C62X uses a Harvard architecture, in which, program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture, where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C620(A) and PIC16CR620A address 512 x 14 on-chip program memory. The PIC16C621(A) addresses 1K x 14 program memory. The PIC16C622(A) addresses 2K x 14 program memory. All program memory is internal.

The PIC16C62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16C62X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

TABLE 3-1: PIC16C62X PINOUT DESCRIPTION

| Name         | DIP/SOIC<br>Pin # | SSOP<br>Pin# | I/O/P Type | Buffer<br>Type        | Description                                                                                                                                                                                              |

|--------------|-------------------|--------------|------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 16                | 18           | I          | ST/CMOS               | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT  | 15                | 17           | 0          | _                     | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. In RC mode, OSC2 pin outputs CLKOUT, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate. |

| MCLR/VPP     | 4                 | 4            | I/P        | ST                    | Master Clear (Reset) input/programming voltage input. This pin is an Active Low Reset to the device.                                                                                                     |

|              |                   |              |            |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0/AN0      | 17                | 19           | I/O        | ST                    | Analog comparator input                                                                                                                                                                                  |

| RA1/AN1      | 18                | 20           | I/O        | ST                    | Analog comparator input                                                                                                                                                                                  |

| RA2/AN2/VREF | 1                 | 1            | I/O        | ST                    | Analog comparator input or VREF output                                                                                                                                                                   |

| RA3/AN3      | 2                 | 2            | I/O        | ST                    | Analog comparator input /output                                                                                                                                                                          |

| RA4/T0CKI    | 3                 | 3            | I/O        | ST                    | Can be selected to be the clock input to the Timer0 timer/counter or a comparator output. Output is open drain type.                                                                                     |

|              |                   |              |            |                       | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                            |

| RB0/INT      | 6                 | 7            | I/O        | TTL/ST <sup>(1)</sup> | RB0/INT can also be selected as an external interrupt pin.                                                                                                                                               |

| RB1          | 7                 | 8            | I/O        | TTL                   |                                                                                                                                                                                                          |

| RB2          | 8                 | 9            | I/O        | TTL                   |                                                                                                                                                                                                          |

| RB3          | 9                 | 10           | I/O        | TTL                   |                                                                                                                                                                                                          |

| RB4          | 10                | 11           | I/O        | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                 |

| RB5          | 11                | 12           | I/O        | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                 |

| RB6          | 12                | 13           | I/O        | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming clock.                                                                                                                                                       |

| RB7          | 13                | 14           | I/O        | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming data.                                                                                                                                                        |

| Vss          | 5                 | 5,6          | Р          | _                     | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| VDD          | 14                | 15,16        | Р          | _                     | Positive supply for logic and I/O pins.                                                                                                                                                                  |

Legend:

O = output — = Not used TTL = TTL input I/O = input/output I = Input P = power

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

FIGURE 4-6: DATA MEMORY MAP FOR THE PIC16C620A/CR620A/621A

| File<br>Address                                   | ;                              |                     | File<br>Address |  |

|---------------------------------------------------|--------------------------------|---------------------|-----------------|--|

| 00h                                               | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup> | 80h             |  |

| 01h                                               | TMR0                           | OPTION              | 81h             |  |

| 02h                                               | PCL                            | PCL                 | 82h             |  |

| 03h                                               | STATUS                         | STATUS              | 83h             |  |

| 04h                                               | FSR                            | FSR                 | 84h             |  |

| 05h                                               | PORTA                          | TRISA               | 85h             |  |

| 06h                                               | PORTB                          | TRISB               | 86h             |  |

| 07h                                               |                                |                     | 87h             |  |

| 08h                                               |                                |                     | 88h             |  |

| 09h                                               |                                |                     | 89h             |  |

| 0Ah                                               | PCLATH                         | PCLATH              | 8Ah             |  |

| 0Bh                                               | INTCON                         | INTCON              | 8Bh             |  |

| 0Ch                                               | PIR1                           | PIE1                | 8Ch             |  |

| 0Dh                                               |                                |                     | 8Dh             |  |

| 0Eh                                               |                                | PCON                | 8Eh             |  |

| 0Fh                                               |                                |                     | 8Fh             |  |

| 10h                                               |                                |                     | 90h             |  |

| 11h                                               |                                |                     | 91h             |  |

| 12h                                               |                                |                     | 92h             |  |

| 13h                                               |                                |                     | 93h             |  |

| 14h                                               |                                |                     | 94h             |  |

| 15h                                               |                                |                     | 95h             |  |

| 16h                                               |                                |                     | 96h             |  |

| 17h                                               |                                |                     | 97h             |  |

| 18h                                               |                                |                     | 98h             |  |

| 19h                                               |                                |                     | 99h             |  |

| 1Ah                                               |                                |                     | 9Ah             |  |

| 1Bh                                               |                                |                     | 9Bh             |  |

| 1Ch                                               |                                |                     | 9Ch             |  |

| 1Dh                                               |                                |                     | 9Dh             |  |

| 1Eh                                               |                                |                     | 9Eh             |  |

| 1Fh                                               | CMCON                          | VRCON               | 9Fh             |  |

| 20h                                               | General<br>Purpose<br>Register |                     | A0h             |  |

| 6Fh                                               |                                |                     |                 |  |

|                                                   | 0                              |                     | F0h             |  |

| 70h                                               | General<br>Purpose             | Accesses            | "               |  |

| 751-                                              | Register                       | 70h-7Fh             | FFh             |  |

| 7Fh <sup>[</sup>                                  | Bank 0                         | Bank 1              | <b>⊒</b> 1 FH   |  |

| Unimplemented data memory locations, read as '0'. |                                |                     |                 |  |

| Note 1:                                           | Not a physical re              | gister.             |                 |  |

FIGURE 4-7: DATA MEMORY MAP FOR THE PIC16C622A

|                                                   |                     | · · · · · · · · · · · · · · · · · · · |                 |  |  |

|---------------------------------------------------|---------------------|---------------------------------------|-----------------|--|--|

| File<br>Address                                   | ;                   |                                       | File<br>Address |  |  |

| 00h                                               | INDF <sup>(1)</sup> | INDF <sup>(1)</sup>                   | 80h             |  |  |

| 01h                                               | TMR0                | OPTION                                | 81h             |  |  |

| 0111<br>02h                                       | PCL                 | PCL                                   | 82h             |  |  |

| 02h                                               | STATUS              | STATUS                                | 83h             |  |  |

| 04h                                               | FSR                 | FSR                                   | 84h             |  |  |

| 05h                                               | PORTA               | TRISA                                 | 85h             |  |  |

| 06h                                               | PORTB               | TRISB                                 | 86h             |  |  |

| 07h                                               | TORTE               | TITIOD                                | 87h             |  |  |

| 0711<br>08h                                       |                     |                                       | 88h             |  |  |

| 09h                                               |                     |                                       | 89h             |  |  |

| 0Ah                                               | PCLATH              | PCLATH                                | 8Ah             |  |  |

| 0An<br>0Bh                                        | INTCON              | INTCON                                | 8Bh             |  |  |

| 0Ch                                               | PIR1                | PIE1                                  | 8Ch             |  |  |

| F                                                 | PIRI                | PIET                                  | 8Dh             |  |  |

| 0Dh                                               |                     | DCON                                  |                 |  |  |

| 0Eh                                               |                     | PCON                                  | 8Eh             |  |  |

| 0Fh                                               |                     |                                       | 8Fh             |  |  |

| 10h                                               |                     |                                       | 90h             |  |  |

| 11h                                               |                     |                                       | 91h             |  |  |

| 12h                                               |                     |                                       | 92h             |  |  |

| 13h                                               |                     |                                       | 93h             |  |  |

| 14h                                               |                     |                                       | 94h             |  |  |

| 15h                                               |                     |                                       | 95h             |  |  |

| 16h                                               |                     |                                       | 96h             |  |  |

| 17h                                               |                     |                                       | 97h             |  |  |

| 18h                                               |                     |                                       | 98h             |  |  |

| 19h                                               |                     |                                       | 99h             |  |  |

| 1Ah                                               |                     |                                       | 9Ah             |  |  |

| 1Bh                                               |                     |                                       | 9Bh             |  |  |

| 1Ch                                               |                     |                                       | 9Ch             |  |  |

| 1Dh                                               |                     |                                       | 9Dh             |  |  |

| 1Eh                                               |                     |                                       | 9Eh             |  |  |

| 1Fh                                               | CMCON               | VRCON                                 | 9Fh             |  |  |

| 20h                                               |                     |                                       | A0h             |  |  |

|                                                   | General<br>Purpose  | General<br>Purpose                    |                 |  |  |

|                                                   | Register            | Register                              |                 |  |  |

|                                                   | -                   |                                       | BFh             |  |  |

|                                                   |                     |                                       | C0h             |  |  |

| 6Fh                                               |                     |                                       |                 |  |  |

| 70h                                               | General             | _                                     | F0h             |  |  |

| 7011                                              | Purpose             | Accesses<br>70h-7Fh                   |                 |  |  |

| 7Fh                                               | Register            | / 011-/ [11                           | FFh             |  |  |

| 71115                                             | Bank 0              | Bank 1                                |                 |  |  |

|                                                   |                     |                                       |                 |  |  |

| Unimplemented data memory locations, read as '0'. |                     |                                       |                 |  |  |

| Note 1: Not a physical register.                  |                     |                                       |                 |  |  |

### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM. The Special Function Registers can be classified into two sets (core and peripheral). The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16C62X

| Address | Name          | Bit 7               | Bit 6                                                                                         | Bit 5       | Bit 4        | Bit 3        | Bit 2        | Bit 1       | Bit 0    | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|---------------|---------------------|-----------------------------------------------------------------------------------------------|-------------|--------------|--------------|--------------|-------------|----------|-----------------------|------------------------------------------------|

| Bank 0  |               |                     |                                                                                               |             |              |              |              |             |          |                       |                                                |

| 00h     | INDF          | Addressin register) | addressing this location uses contents of FSR to address data memory (not a physical egister) |             |              |              |              |             |          | xxxx xxxx             | xxxx xxxx                                      |

| 01h     | TMR0          | Timer0 Mo           | odule's Reg                                                                                   | ister       |              |              |              |             |          | xxxx xxxx             | uuuu uuuu                                      |

| 02h     | PCL           | Program C           | Counter's (F                                                                                  | PC) Least S | ignificant B | yte          |              |             |          | 0000 0000             | 0000 0000                                      |

| 03h     | STATUS        | IRP <sup>(2)</sup>  | RP1 <sup>(2)</sup>                                                                            | RP0         | TO           | PD           | Z            | DC          | С        | 0001 1xxx             | 000q quuu                                      |

| 04h     | FSR           | Indirect da         | ata memory                                                                                    | address po  | ointer       |              |              |             |          | xxxx xxxx             | uuuu uuuu                                      |

| 05h     | PORTA         | _                   | _                                                                                             | _           | RA4          | RA3          | RA2          | RA1         | RA0      | x 0000                | u 0000                                         |

| 06h     | PORTB         | RB7                 | RB6                                                                                           | RB5         | RB4          | RB3          | RB2          | RB1         | RB0      | xxxx xxxx             | uuuu uuuu                                      |

| 07h-09h | Unimplemented |                     |                                                                                               |             |              |              |              |             |          | _                     | _                                              |

| 0Ah     | PCLATH        | _                   | _                                                                                             | _           | Write buffe  | er for upper | 5 bits of pr | ogram cour  | nter     | 0 0000                | 0 0000                                         |

| 0Bh     | INTCON        | GIE                 | PEIE                                                                                          | TOIE        | INTE         | RBIE         | TOIF         | INTF        | RBIF     | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1          | _                   | CMIF                                                                                          | _           | _            | _            | _            | _           | _        | -0                    | -0                                             |

| 0Dh-1Eh | Unimplemented |                     |                                                                                               |             |              |              |              |             |          | _                     | _                                              |

| 1Fh     | CMCON         | C2OUT               | C10UT                                                                                         | _           | _            | CIS          | CM2          | CM1         | CM0      | 00 0000               | 00 0000                                        |

| Bank 1  |               |                     |                                                                                               |             |              |              |              |             |          |                       |                                                |

| 80h     | INDF          | Addressin register) | g this locati                                                                                 | on uses co  | ntents of FS | SR to addre  | ss data me   | mory (not a | physical | xxxx xxxx             | xxxx xxxx                                      |

| 81h     | OPTION        | RBPU                | INTEDG                                                                                        | T0CS        | T0SE         | PSA          | PS2          | PS1         | PS0      | 1111 1111             | 1111 1111                                      |

| 82h     | PCL           | Program C           | Counter's (F                                                                                  | PC) Least S | ignificant B | yte          |              |             |          | 0000 0000             | 0000 0000                                      |

| 83h     | STATUS        | IRP <sup>(2)</sup>  | RP1 <sup>(2)</sup>                                                                            | RP0         | TO           | PD           | Z            | DC          | С        | 0001 1xxx             | 000q quuu                                      |

| 84h     | FSR           | Indirect da         | ata memory                                                                                    | address po  | ointer       | •            | •            | •           |          | xxxx xxxx             | uuuu uuuu                                      |

| 85h     | TRISA         | _                   | _                                                                                             | _           | TRISA4       | TRISA3       | TRISA2       | TRISA1      | TRISA0   | 1 1111                | 1 1111                                         |

| 86h     | TRISB         | TRISB7              | TRISB6                                                                                        | TRISB5      | TRISB4       | TRISB3       | TRISB2       | TRISB1      | TRISB0   | 1111 1111             | 1111 1111                                      |

| 87h-89h | Unimplemented |                     |                                                                                               |             |              |              |              |             |          | _                     | _                                              |

| 8Ah     | PCLATH        | _                   | _                                                                                             | _           | Write buffe  | er for upper | 5 bits of pr | ogram cour  | nter     | 0 0000                | 0 0000                                         |

| 8Bh     | INTCON        | GIE                 | PEIE                                                                                          | TOIE        | INTE         | RBIE         | TOIF         | INTF        | RBIF     | 0000 000x             | 0000 000u                                      |

| 8Ch     | PIE1          | _                   | CMIE                                                                                          | _           | _            | _            | _            | _           | _        | -0                    | -0                                             |

| 8Dh     | Unimplemented |                     |                                                                                               |             |              |              |              |             |          | _                     | _                                              |

| 8Eh     | PCON          | _                   | _                                                                                             | _           | _            | _            | _            | POR         | BOR      | 0x                    | uq                                             |

| 8Fh-9Eh | Unimplemented |                     |                                                                                               |             |              |              |              |             |          | _                     |                                                |

| 9Fh     | VRCON         | VREN                | VROE                                                                                          | VRR         | _            | VR3          | VR2          | VR1         | VR0      | 000- 0000             | 000- 0000                                      |

Legend: — = Unimplemented locations read as '0',  ${\tt u}$  = unchanged,  ${\tt x}$  = unknown,

q = value depends on condition, shaded = unimplemented

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

<sup>2:</sup> IRP & RP1 bits are reserved; always maintain these bits clear.

### 4.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

### REGISTER 4-3: INTCON REGISTER (ADDRESS 0BH OR 8BH)

| R/W-0 | R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Note:

bit 7 GIE: Global Interrupt Enable bit 1 = Enables all un-masked interrupts 0 = Disables all interrupts bit 6 PEIE: Peripheral Interrupt Enable bit 1 = Enables all un-masked peripheral interrupts 0 = Disables all peripheral interrupts T0IE: TMR0 Overflow Interrupt Enable bit bit 5 1 = Enables the TMR0 interrupt 0 = Disables the TMR0 interrupt bit 4 INTE: RB0/INT External Interrupt Enable bit 1 = Enables the RB0/INT external interrupt 0 = Disables the RB0/INT external interrupt bit 3 RBIE: RB Port Change Interrupt Enable bit 1 = Enables the RB port change interrupt 0 = Disables the RB port change interrupt bit 2 T0IF: TMR0 Overflow Interrupt Flag bit 1 = TMR0 register has overflowed (must be cleared in software) 0 = TMR0 register did not overflow bit 1 INTF: RB0/INT External Interrupt Flag bit

The DDO/INT automatic approach

1 = The RB0/INT external interrupt occurred (must be cleared in software)

0 = The RB0/INT external interrupt did not occur

bit 0 RBIF: RB Port Change Interrupt Flag bit

1 = When at least one of the RB<7:4> pins changed state (must be cleared in software)

0 = None of the RB<7:4> pins have changed state

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### **5.0 I/O PORTS**

The PIC16C62X have two ports, PORTA and PORTB. Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

### 5.1 PORTA and TRISA Registers

PORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. Port RA4 is multiplexed with the T0CKI clock input. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers), which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

The PORTA pins are multiplexed with comparator and voltage reference functions. The operation of these pins are selected by control bits in the CMCON (comparator control register) register and the VRCON (voltage reference control register) register. When selected as a comparator input, these pins will read as '0's.

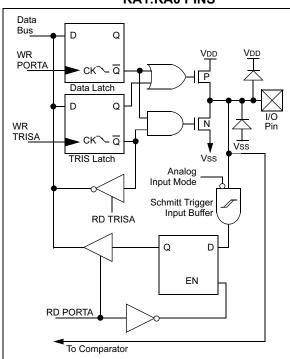

FIGURE 5-1: BLOCK DIAGRAM OF RA1:RA0 PINS

On RESET, the TRISA register is set to all inputs. The digital inputs are disabled and the comparator inputs are forced to ground to reduce excess current consumption.

TRISA controls the direction of the RA pins, even when they are being used as comparator inputs. The user must make sure to keep the pins configured as inputs when using them as comparator inputs.

Note:

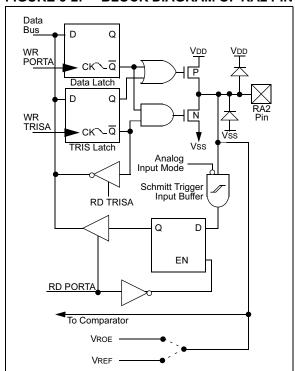

The RA2 pin will also function as the output for the voltage reference. When in this mode, the VREF pin is a very high impedance output and must be buffered prior to any external load. The user must configure TRISA<2> bit as an input and use high impedance loads

In one of the Comparator modes defined by the CMCON register, pins RA3 and RA4 become outputs of the comparators. The TRISA<4:3> bits must be cleared to enable outputs to use this function.

#### **EXAMPLE 5-1: INITIALIZING PORTA**

| CLRF  | PORTA       | ;Initialize PORTA by setting ;output data latches |

|-------|-------------|---------------------------------------------------|

| MOVLW | 0X07        | ;Turn comparators off and                         |

| MOVWF | CMCON       | <pre>;enable pins for I/O ;functions</pre>        |

| BSF   | STATUS, RPO | ;Select Bank1                                     |

| MOVLW | 0x1F        | ; Value used to initialize                        |

|       |             | ;data direction                                   |

| MOVWF | TRISA       | ;Set RA<4:0> as inputs                            |

|       |             | ;TRISA<7:5> are always                            |

|       |             | ;read as '0'.                                     |

#### FIGURE 5-2: BLOCK DIAGRAM OF RA2 PIN

### 5.2 PORTB and TRISB Registers

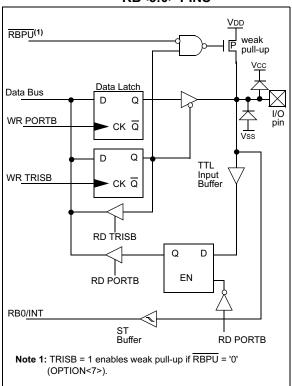

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a High Impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

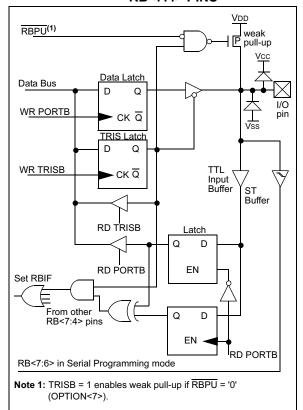

Each of the PORTB pins has a weak internal pull-up (\$\approx200 \mu A\$ typical). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (e.g., any RB<7:4> pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

FIGURE 5-5: BLOCK DIAGRAM OF RB<7:4> PINS

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552, "Implementing Wake-Up on Key Strokes.)

**Note:** If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

FIGURE 5-6: BLOCK DIAGRAM OF RB<3:0> PINS

### 9.2 Oscillator Configurations

### 9.2.1 OSCILLATOR TYPES

The PIC16C62X devices can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

LP Low Power Crystal

XT Crystal/Resonator

HS High Speed Crystal/Resonator

RC Resistor/Capacitor

### 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

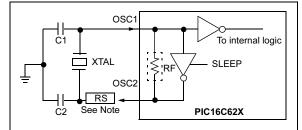

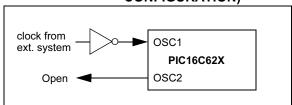

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 9-1). The PIC16C62X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 9-2).

FIGURE 9-1: CRYSTAL OPERATION

(OR CERAMIC

RESONATOR) (HS, XT OR

LP OSC

CONFIGURATION)

See Table 9-1 and Table 9-2 for recommended values of C1 and C2.

**Note:** A series resistor may be required for AT strip cut crystals.

FIGURE 9-2: EXTERNAL CLOCK INPUT

OPERATION (HS, XT OR

LP OSC

CONFIGURATION)

TABLE 9-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| R    | anges Chara                   |                           |                                         |

|------|-------------------------------|---------------------------|-----------------------------------------|

| Mode | Freq                          | OSC1(C1)                  | OS62(C2)                                |

| XT   | 455 kHz<br>2.0 MHz<br>4.0 MHz | 22 - 100 pF<br>15 - 68 pF | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |

| HS   | 8.0 MHz<br>16.0 MHz           | 10-22 pF                  | 10 - 68 pF<br>10 - 22 pF                |

Higher capacitance increases the stability of the oscillator but also increases the start-up time. These waltes are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode | Freq    | OSC1(C1)    | OSC2(C2)     |

|------|---------|-------------|--------------|

| LP   | 32 kHz  | 68 - 100 pF | 68 - 100 pF  |

|      | 200 kHz | 15 - 30 pF  | 15 - 30 pF   |

| XT   | 100 kHz | 68 - 150 pF | 150 - 200 pF |

|      | 2 MHz   | 15 - 30 pF  | 15 - 30 pF   |

|      | 4 MHz   | 15 - 30 pF  | 15 - 30 pF   |

| HS   | 8 MHz   | 15-30 pF    | 15 - 30 pF   |

|      | 10 MHz  | 15-30 pF    | 15 - 30 pF   |

|      | 20 MHz  | 15-30 pF    | 15 - 30 pF   |

Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

#### 9.9 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

**Note:** Microchip does not recommend code protecting windowed devices.

### 9.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify. Only the Least Significant 4 bits of the ID locations are used.

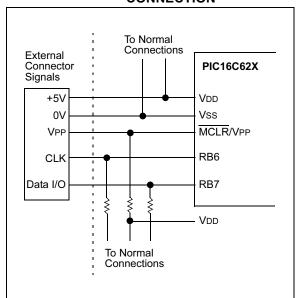

### 9.11 In-Circuit Serial Programming™

The PIC16C62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X/9XX Programming Specification (DS30228).

A typical In-Circuit Serial Programming connection is shown in Figure 9-19.

FIGURE 9-19: TYPICAL IN-CIRCUIT

SERIAL PROGRAMMING

CONNECTION

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                         |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                         |

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                       |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                          |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.  If the result is 0, the next instruction, which is already fetched, is discarded. A NOP is executed instead making it a two-cycle instruction. |

| Words:           | 1                                                                                                                                                                                                                                                                                                          |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                       |

| Example          | HERE DECFSZ CNT, 1 GOTO LOOP CONTINUE •                                                                                                                                                                                                                                                                    |

|                  | Before Instruction PC = address HERE  After Instruction CNT = CNT - 1 if CNT = 0, PC = address CONTINUE if CNT \neq 0, PC = address HERE+1                                                                                                                                                                 |

| INCF             | Increment f                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                           |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                         |

| Operation:       | $(f) + 1 \rightarrow (dest)$                                                                                                                               |

| Status Affected: | Z                                                                                                                                                          |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                          |

| Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |

| Words:           | 1                                                                                                                                                          |

| Cycles:          | 1                                                                                                                                                          |

| Example          | INCF CNT, 1                                                                                                                                                |

|                  | Before Instruction  CNT = 0xFF Z = 0  After Instruction  CNT = 0x00 Z = 1                                                                                  |

#### Syntax: [label] GOTO k Operands: $0 \le k \le 2047$ Operation: $k \rightarrow PC<10:0>$ $\mathsf{PCLATH} \mathord{<} 4:3 \mathord{>} \to \mathsf{PC} \mathord{<} 12:11 \mathord{>}$ Status Affected: None Encoding: 10 1kkk kkkk kkkk GOTO is an unconditional branch. Description: The eleven bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a twocycle instruction. Words: 1 Cycles: 2 Example GOTO THERE

After Instruction PC =

Address THERE

**Unconditional Branch**

**GOTO**

NOTES:

# 11.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 11.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 11.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command-line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities, and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping, and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high level source debugging with the MPLAB IDE.

### 11.6 MPLAB ASM30 Assembler, Linker, and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB IDE compatibility

### 11.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PICmicro series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break, or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

#### 11.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

# 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended) (CONT.)

|                                                                  |                                                           |                                                                                                                                                                                                                                                                                                         | Standard Operating Conditions (unless otherwise stated) |                                                                                                                                                                                                                                                                                                                           |                                                          |                                  |                                                                                                                         |  |  |

|------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| PIC16C62X                                                        |                                                           |                                                                                                                                                                                                                                                                                                         |                                                         | Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for industrial and $0^{\circ}\text{C} \le \text{Ta} \le +70^{\circ}\text{C}$ for commercial and $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for extended                                                               |                                                          |                                  |                                                                                                                         |  |  |

| PIC16LC62X                                                       |                                                           |                                                                                                                                                                                                                                                                                                         |                                                         | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C}$ $\leq$ TA $\leq$ +85°C for industrial and $0^{\circ}\text{C}$ $\leq$ TA $\leq$ +70°C for commercial an $-40^{\circ}\text{C}$ $\leq$ TA $\leq$ +125°C for extended Operating voltage VDD range is the PIC16C62X range. |                                                          |                                  |                                                                                                                         |  |  |

| Param . No.                                                      | Sym                                                       | Characteristic                                                                                                                                                                                                                                                                                          | Min                                                     | Тур†                                                                                                                                                                                                                                                                                                                      | Max                                                      | Units                            | Conditions                                                                                                              |  |  |

| D022<br>D022A<br>D023<br>D023A<br>D022<br>D022A<br>D023<br>D023A | ΔIWDT  ΔIBOR ΔICOM P  ΔIVREF  ΔIWDT ΔIBOR ΔICOM P  ΔIVREF | WDT Current <sup>(5)</sup> Brown-out Reset Current <sup>(5)</sup> Comparator Current for each Comparator <sup>(5)</sup> VREF Current <sup>(5)</sup> WDT Current <sup>(5)</sup> Brown-out Reset Current <sup>(5)</sup> Comparator Current for each Comparator <sup>(5)</sup> VREF Current <sup>(5)</sup> | _<br>_<br>_<br>_                                        | 6.0<br>350<br>—<br>6.0<br>350<br>—                                                                                                                                                                                                                                                                                        | 20<br>25<br>425<br>100<br>300<br>15<br>425<br>100<br>300 | µА<br>µА<br>µА<br>µА<br>µА<br>µА | VDD=4.0V (125°C) BOD enabled, VDD = 5.0V VDD = 4.0V  VDD = 4.0V  VDD=3.0V BOD enabled, VDD = 5.0V VDD = 3.0V VDD = 3.0V |  |  |

| 1A                                                               | Fosc                                                      | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency                                                                                                                                                        | 0<br>0<br>0<br>0                                        | _<br>_<br>_<br>_                                                                                                                                                                                                                                                                                                          | 200<br>4<br>4<br>20                                      | kHz<br>MHz<br>MHz<br>MHz         | All temperatures All temperatures All temperatures All temperatures                                                     |  |  |

| 1A                                                               | Fosc                                                      | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency                                                                                                                                                        | 0<br>0<br>0<br>0                                        | _<br>_<br>_<br>_                                                                                                                                                                                                                                                                                                          | 200<br>4<br>4<br>20                                      | kHz<br>MHz<br>MHz<br>MHz         | All temperatures All temperatures All temperatures All temperatures                                                     |  |  |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

### **TABLE 12-1: COMPARATOR SPECIFICATIONS**

Operating Conditions: VDD range as described in Table 12-1, -40°C<TA<+125°C. Current consumption is specified in Table 12-1.

| Characteristics                        | Sym | Min  | Тур   | Max          | Units    | Comments                   |

|----------------------------------------|-----|------|-------|--------------|----------|----------------------------|

| Input offset voltage                   |     |      | ± 5.0 | ± 10         | mV       |                            |

| Input common mode voltage              |     | 0    |       | VDD - 1.5    | V        |                            |

| CMRR                                   |     | +55* |       |              | δβ       |                            |

| Response Time <sup>(1)</sup>           |     |      | 150*  | 400*<br>600* | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X |

| Comparator mode change to output valid |     |      |       | 10*          | μS       |                            |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** Response time measured with one comparator input at (VDD - 1.5)/2, while the other input transitions from Vss to VDD.

### TABLE 12-2: VOLTAGE REFERENCE SPECIFICATIONS

Operating Conditions:VDD range as described in Table 12-1, -40°C<TA<+125°C. Current consumption is specified in Table 12-1.

| Characteristics              | Sym | Min | Тур              | Max                          | Units      | Comments                                |

|------------------------------|-----|-----|------------------|------------------------------|------------|-----------------------------------------|

| Resolution                   |     |     | VDD/24<br>VDD/32 |                              | LSB<br>LSB | Low Range (VRR=1)<br>High Range (VRR=0) |

| Absolute Accuracy            |     |     |                  | <u>+</u> 1/4<br><u>+</u> 1/2 | LSB<br>LSB | Low Range (VRR=1)<br>High Range (VRR=0) |

| Unit Resistor Value (R)      |     |     | 2K*              |                              | Ω          | Figure 8-1                              |

| Settling Time <sup>(1)</sup> |     |     |                  | 10*                          | μS         |                                         |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** Settling time measured while VRR = 1 and VR<3:0> transitions from 0000 to 1111.

### 18-Lead Plastic Dual In-line (P) - 300 mil (PDIP)

|                            |          | INCHES* |      | MILLIMETERS |       |       |       |

|----------------------------|----------|---------|------|-------------|-------|-------|-------|

| Dimension                  | n Limits | MIN     | MOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n        |         | 18   |             |       | 18    |       |

| Pitch                      | р        |         | .100 |             |       | 2.54  |       |

| Top to Seating Plane       | Α        | .140    | .155 | .170        | 3.56  | 3.94  | 4.32  |

| Molded Package Thickness   | A2       | .115    | .130 | .145        | 2.92  | 3.30  | 3.68  |

| Base to Seating Plane      | A1       | .015    |      |             | 0.38  |       |       |

| Shoulder to Shoulder Width | Е        | .300    | .313 | .325        | 7.62  | 7.94  | 8.26  |

| Molded Package Width       | E1       | .240    | .250 | .260        | 6.10  | 6.35  | 6.60  |

| Overall Length             | D        | .890    | .898 | .905        | 22.61 | 22.80 | 22.99 |

| Tip to Seating Plane       | L        | .125    | .130 | .135        | 3.18  | 3.30  | 3.43  |

| Lead Thickness             | С        | .008    | .012 | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1       | .045    | .058 | .070        | 1.14  | 1.46  | 1.78  |

| Lower Lead Width           | В        | .014    | .018 | .022        | 0.36  | 0.46  | 0.56  |

| Overall Row Spacing §      | eB       | .310    | .370 | .430        | 7.87  | 9.40  | 10.92 |

| Mold Draft Angle Top       | α        | 5       | 10   | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β        | 5       | 10   | 15          | 5     | 10    | 15    |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MS-001

Drawing No. C04-007

<sup>\*</sup> Controlling Parameter § Significant Characteristic

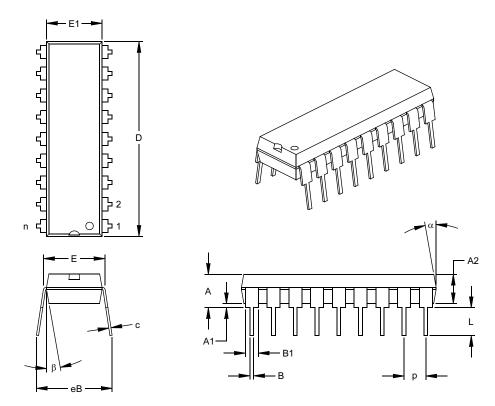

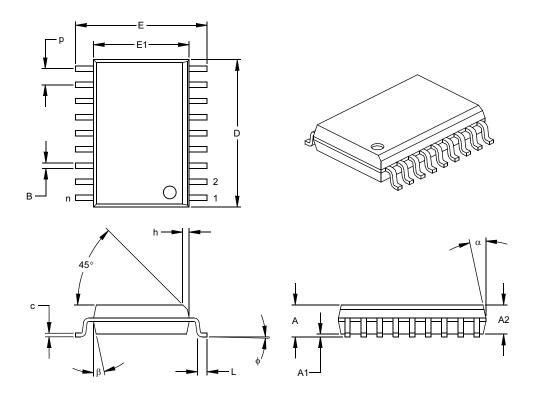

### 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

|                          |        | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|--------|---------|------|-------------|-------|-------|-------|

| Dimension                | Limits | MIN     | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins           | n      |         | 18   |             |       | 18    |       |

| Pitch                    | р      |         | .050 |             |       | 1.27  |       |

| Overall Height           | Α      | .093    | .099 | .104        | 2.36  | 2.50  | 2.64  |

| Molded Package Thickness | A2     | .088    | .091 | .094        | 2.24  | 2.31  | 2.39  |

| Standoff §               | A1     | .004    | .008 | .012        | 0.10  | 0.20  | 0.30  |

| Overall Width            | Е      | .394    | .407 | .420        | 10.01 | 10.34 | 10.67 |

| Molded Package Width     | E1     | .291    | .295 | .299        | 7.39  | 7.49  | 7.59  |

| Overall Length           | D      | .446    | .454 | .462        | 11.33 | 11.53 | 11.73 |

| Chamfer Distance         | h      | .010    | .020 | .029        | 0.25  | 0.50  | 0.74  |

| Foot Length              | L      | .016    | .033 | .050        | 0.41  | 0.84  | 1.27  |

| Foot Angle               | ф      | 0       | 4    | 8           | 0     | 4     | 8     |

| Lead Thickness           | С      | .009    | .011 | .012        | 0.23  | 0.27  | 0.30  |

| Lead Width               | В      | .014    | .017 | .020        | 0.36  | 0.42  | 0.51  |

| Mold Draft Angle Top     | α      | 0       | 12   | 15          | 0     | 12    | 15    |

| Mold Draft Angle Bottom  | β      | 0       | 12   | 15          | 0     | 12    | 15    |

### Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-051

<sup>\*</sup> Controlling Parameter § Significant Characteristic

| N                                                     |      |

|-------------------------------------------------------|------|

| NOP Instruction                                       | . 69 |

| 0                                                     |      |

| One-Time-Programmable (OTP) Devices                   | 7    |

| OPTION Instruction                                    | . 69 |

| OPTION Register                                       | . 19 |

| Oscillator Configurations                             | . 47 |

| Oscillator Start-up Timer (OST)                       | . 50 |

| P                                                     |      |

| Package Marking Information                           | 117  |

| Packaging Information                                 | 113  |

| PCL and PCLATH                                        |      |

| PCON Register                                         |      |

| PICkit 1 FLASH Starter Kit                            |      |

| PICSTART Plus Development Programmer                  |      |

| PIE1 RegisterPIR1 Register                            |      |

| Port RB Interrupt                                     |      |

| PORTA                                                 |      |

| PORTB                                                 |      |

| Power Control/Status Register (PCON)                  |      |

| Power-Down Mode (SLEEP)                               |      |

| Power-On Reset (POR)                                  |      |

| Power-up Timer (PWRT)                                 |      |

| Prescaler                                             |      |

| PRO MATE II Universal Device Programmer               |      |

| Program Memory Organization                           | . 13 |

| Q                                                     |      |

| Quick-Turnaround-Production (QTP) Devices             | 7    |

| R                                                     |      |

| RC Oscillator                                         | 10   |

| Reset                                                 |      |

| RETFIE Instruction                                    |      |