Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

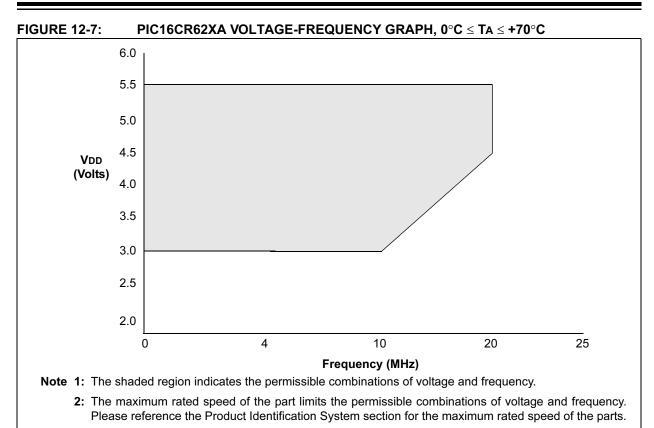

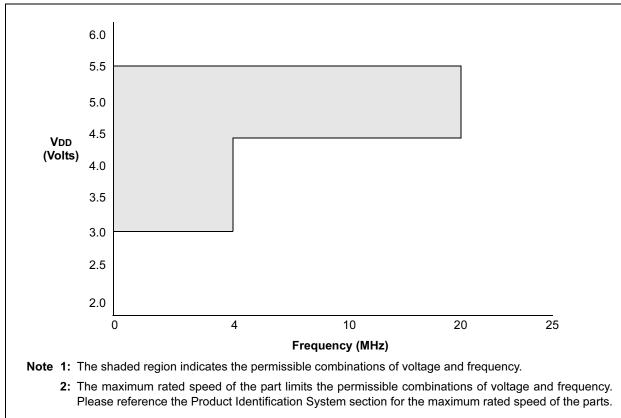

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 896B (512 x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 96 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c620at-04-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM. The Special Function Registers can be classified into two sets (core and peripheral). The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name          | Bit 7                                | Bit 6                                                  | Bit 5       | Bit 4        | Bit 3        | Bit 2        | Bit 1       | Bit 0      | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|---------------|--------------------------------------|--------------------------------------------------------|-------------|--------------|--------------|--------------|-------------|------------|-----------------------|------------------------------------------------|

| Bank 0  |               |                                      |                                                        |             |              |              |              |             |            |                       |                                                |

| 00h     | INDF          | Addressin register)                  | g this locati                                          | ion uses co | ntents of FS | SR to addre  | ess data me  | mory (not a | n physical | XXXX XXXX             | XXXX XXXX                                      |

| 01h     | TMR0          | Timer0 Mo                            | odule's Reg                                            | ister       |              |              |              |             |            | xxxx xxxx             | uuuu uuuu                                      |

| 02h     | PCL           | Program 0                            | Counter's (F                                           | PC) Least S | ignificant B | yte          |              |             |            | 0000 0000             | 0000 0000                                      |

| 03h     | STATUS        | IRP <sup>(2)</sup>                   | IRP <sup>(2)</sup> RP1 <sup>(2)</sup> RP0 TO PD Z DC C |             |              |              |              |             |            |                       | 000q quuu                                      |

| 04h     | FSR           | Indirect data memory address pointer |                                                        |             |              |              |              |             |            |                       | uuuu uuuu                                      |

| 05h     | PORTA         | —                                    | _                                                      | _           | RA4          | RA3          | RA2          | RA1         | RA0        | x 0000                | u 0000                                         |

| 06h     | PORTB         | RB7                                  | RB6                                                    | RB5         | RB4          | RB3          | RB2          | RB1         | RB0        | xxxx xxxx             | uuuu uuuu                                      |

| 07h-09h | Unimplemented |                                      |                                                        |             |              |              |              |             |            | _                     | _                                              |

| 0Ah     | PCLATH        | _                                    | _                                                      | _           | Write buffe  | er for upper | 5 bits of pr | ogram coui  | nter       | 0 0000                | 0 0000                                         |

| 0Bh     | INTCON        | GIE                                  | PEIE                                                   | T0IE        | INTE         | RBIE         | T0IF         | INTF        | RBIF       | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1          | _                                    | CMIF                                                   | —           | _            | —            | _            | —           | —          | -0                    | -0                                             |

| 0Dh-1Eh | Unimplemented |                                      |                                                        |             |              |              |              |             | _          | _                     |                                                |

| 1Fh     | CMCON         | C2OUT                                | C1OUT                                                  | —           | _            | CIS          | CM2          | CM1         | CM0        | 00 0000               | 00 0000                                        |

| Bank 1  |               |                                      |                                                        |             |              |              |              |             |            |                       |                                                |

| 80h     | INDF          | Addressin register)                  | g this locati                                          | on uses co  | ntents of FS | SR to addre  | ess data me  | mory (not a | ı physical | xxxx xxxx             | xxxx xxxx                                      |

| 81h     | OPTION        | RBPU                                 | INTEDG                                                 | TOCS        | TOSE         | PSA          | PS2          | PS1         | PS0        | 1111 1111             | 1111 1111                                      |

| 82h     | PCL           | Program 0                            | Counter's (F                                           | PC) Least S | ignificant B | yte          |              |             |            | 0000 0000             | 0000 0000                                      |

| 83h     | STATUS        | IRP <sup>(2)</sup>                   | RP1 <sup>(2)</sup>                                     | RP0         | TO           | PD           | Z            | DC          | С          | 0001 1xxx             | 000q quuu                                      |

| 84h     | FSR           | Indirect da                          | ata memory                                             | address po  | ointer       |              |              |             |            | xxxx xxxx             | uuuu uuuu                                      |

| 85h     | TRISA         | —                                    | _                                                      | _           | TRISA4       | TRISA3       | TRISA2       | TRISA1      | TRISA0     | 1 1111                | 1 1111                                         |

| 86h     | TRISB         | TRISB7                               | TRISB6                                                 | TRISB5      | TRISB4       | TRISB3       | TRISB2       | TRISB1      | TRISB0     | 1111 1111             | 1111 1111                                      |

| 87h-89h | Unimplemented |                                      |                                                        |             |              |              |              |             |            | _                     | _                                              |

| 8Ah     | PCLATH        | —                                    | _                                                      | _           | Write buffe  | er for upper | 5 bits of pr | ogram coui  | nter       | 0 0000                | 0 0000                                         |

| 8Bh     | INTCON        | GIE                                  | PEIE                                                   | T0IE        | INTE         | RBIE         | T0IF         | INTF        | RBIF       | 0000 000x             | 0000 000u                                      |

| 8Ch     | PIE1          | —                                    | CMIE                                                   | —           | —            | —            | —            | —           | —          | -0                    | -0                                             |

| 8Dh     | Unimplemented |                                      |                                                        |             |              |              |              |             |            | _                     | _                                              |

| 8Eh     | PCON          | —                                    |                                                        | _           |              | _            |              | POR         | BOR        | 0x                    | uq                                             |

| 8Fh-9Eh | Unimplemented |                                      |                                                        |             |              |              |              |             |            | _                     | _                                              |

| 9Fh     | VRCON         | VREN                                 | VROE                                                   | VRR         | —            | VR3          | VR2          | VR1         | VR0        | 000- 0000             | 000- 0000                                      |

TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16C62X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown,

${\rm q}$  = value depends on condition, shaded = unimplemented

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

2: IRP & RP1 bits are reserved; always maintain these bits clear.

#### 4.2.2.6 PCON Register

The PCON register contains flag bits to differentiate between a Power-on Reset, an external MCLR Reset, WDT Reset or a Brown-out Reset.

| Note: | BOR is unknown on Power-on Reset. It        |  |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | must then be set by the user and checked    |  |  |  |  |  |  |  |  |  |  |

|       | on subsequent RESETS to see if BOR is       |  |  |  |  |  |  |  |  |  |  |

|       | cleared, indicating a brown-out has         |  |  |  |  |  |  |  |  |  |  |

|       | occurred. The BOR STATUS bit is a "don't    |  |  |  |  |  |  |  |  |  |  |

|       | care" and is not necessarily predictable if |  |  |  |  |  |  |  |  |  |  |

|       | the brown-out circuit is disabled (by       |  |  |  |  |  |  |  |  |  |  |

|       | programming BODEN bit in the                |  |  |  |  |  |  |  |  |  |  |

|       | Configuration word).                        |  |  |  |  |  |  |  |  |  |  |

#### REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

|   | U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|---|-------|-----|-----|-----|-----|-----|-------|-------|

| ſ | _     | —   | —   | —   | —   | —   | POR   | BOR   |

| - | bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR**: Power-on Reset STATUS bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 **BOR**: Brown-out Reset STATUS bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### TABLE 5-1:PORTA FUNCTIONS

| Name         | Bit # | Buffer<br>Type | Function                                                                                          |

|--------------|-------|----------------|---------------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0  | ST             | Input/output or comparator input                                                                  |

| RA1/AN1      | bit1  | ST             | Input/output or comparator input                                                                  |

| RA2/AN2/VREF | bit2  | ST             | Input/output or comparator input or VREF output                                                   |

| RA3/AN3      | bit3  | ST             | Input/output or comparator input/output                                                           |

| RA4/T0CKI    | bit4  | ST             | Input/output or external clock input for TMR0 or comparator output.<br>Output is open drain type. |

Legend: ST = Schmitt Trigger input

## TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|------------|------------|------------|------------|------------|-----------------|---------------------------------|

| 05h     | PORTA |       |       |       | RA4        | RA3        | RA2        | RA1        | RA0        | x 0000          | u 0000                          |

| 85h     | TRISA |       |       | _     | TRISA<br>4 | TRISA<br>3 | TRISA<br>2 | TRISA<br>1 | TRISA<br>0 | 1 1111          | 1 1111                          |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | _          | CIS        | CM2        | CM1        | CM0        | 00 0000         | 00 0000                         |

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _          | VR3        | VR2        | VR1        | VR0        | 000- 0000       | 000- 0000                       |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

Note: Shaded bits are not used by PORTA.

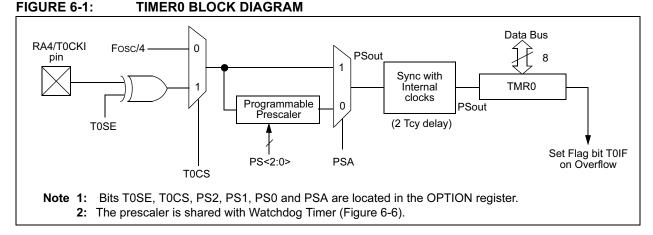

## 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- · Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

## 6.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP, since the timer is shut off during SLEEP. See Figure 6-4 for Timer0 interrupt timing.

## FIGURE 6-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

| (Program<br>Counter) | ( PC-1      | ) PC        | ( <u>PC+1</u> )        | PC+2                   | <u>PC+3</u> χ          | PC+4                   | PC+5 χ                     | PC+6                     |

|----------------------|-------------|-------------|------------------------|------------------------|------------------------|------------------------|----------------------------|--------------------------|

| Instruction<br>Fetch |             | MOVWF TMR   | 0MOVF TMR0,V           | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W                | 1                        |

|                      | i.          | 1           |                        |                        | i                      |                        | i                          |                          |

| TMR0                 | то х        | T0+1 )(     | T0+2 X                 | 1                      | NT0                    |                        | NT0+1 \                    | NT0+2 )                  |

| Instruction          | 1<br>1<br>1 | 1<br>1<br>1 | <b></b>                | <b>≜</b>               | <b>≜</b>               | <b>†</b>               | <b>†</b>                   | <b>≜</b>                 |

| Executed             | 1           | 1           | Write TMR0<br>executed | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1 | Read TMR0<br>reads NT0 + |

## 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-Chip Voltage Reference (Section 8.0) can also be an input to the comparators.

The CMCON register, shown in Register 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-1.

## REGISTER 7-1: CMCON REGISTER (ADDRESS 1Fh)

|         |                            |                                 | <b>(</b> | ,   |       |       |       |       |  |  |  |  |  |

|---------|----------------------------|---------------------------------|----------|-----|-------|-------|-------|-------|--|--|--|--|--|

|         | R-0                        | R-0                             | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|         | C2OUT                      | C10UT                           | —        | —   | CIS   | CM2   | CM1   | CM0   |  |  |  |  |  |

|         | bit 7                      |                                 |          |     |       |       |       | bit 0 |  |  |  |  |  |

|         |                            |                                 |          |     |       |       |       |       |  |  |  |  |  |

| bit 7   | <b>C2OUT</b> : Co          | omparator 2                     | output   |     |       |       |       |       |  |  |  |  |  |

|         | 1 = C2 VIN + > C2 VIN -    |                                 |          |     |       |       |       |       |  |  |  |  |  |

|         | 0 = C2 VIN                 | 0 = C2 VIN+ < C2 VIN-           |          |     |       |       |       |       |  |  |  |  |  |

| bit 6   | <b>C1OUT</b> : Co          | C1OUT: Comparator 1 output      |          |     |       |       |       |       |  |  |  |  |  |

|         | 1 = C1 VIN + > C1 VIN -    |                                 |          |     |       |       |       |       |  |  |  |  |  |

|         | 0 = C1 VIN+ < C1 VIN-      |                                 |          |     |       |       |       |       |  |  |  |  |  |

| bit 5-4 | Unimplemented: Read as '0' |                                 |          |     |       |       |       |       |  |  |  |  |  |

| bit 3   | CIS: Comp                  | CIS: Comparator Input Switch    |          |     |       |       |       |       |  |  |  |  |  |

|         | When CM<                   | <2:0>: = 001                    | :        |     |       |       |       |       |  |  |  |  |  |

|         | 1 = C1 VIN-                | - connects to                   | o RA3    |     |       |       |       |       |  |  |  |  |  |

|         | 0 = C1 VIN                 | - connects to                   | o RA0    |     |       |       |       |       |  |  |  |  |  |

|         | When CM<                   | <2:0> = 010:                    |          |     |       |       |       |       |  |  |  |  |  |

|         |                            | <ul> <li>connects to</li> </ul> |          |     |       |       |       |       |  |  |  |  |  |

|         |                            | I- connects t                   |          |     |       |       |       |       |  |  |  |  |  |

|         |                            | - connects to                   |          |     |       |       |       |       |  |  |  |  |  |

|         | C2 VIN                     | I- connects t                   | 0 RA1    |     |       |       |       |       |  |  |  |  |  |

| bit 2-0 | CM<2:0>:                   | Comparator                      | mode.    |     |       |       |       |       |  |  |  |  |  |

|         |                            |                                 |          |     |       |       |       |       |  |  |  |  |  |

|         | Legend:                    |                                 |          |     |       |       |       |       |  |  |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 9.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

## REGISTER 9-1: CONFIGURATION WORD (ADDRESS 2007h)

| CP1              | CP0 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CP1                                                                                                                                                                                                                                                                                                                                                                                                     | CP0 <sup>(2)</sup>                                                                                                                                        | CP1                                                                                                                                                                | CP0 <sup>(2)</sup>                                                                                                         |                                                               | BODEN                     | CP1     | CP0 (2)  | PWRTE       | WDTE      | F0SC1     | F0SC0 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------|---------|----------|-------------|-----------|-----------|-------|

| bit 13           | ļ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                | ļļ                                                                                                                                                        |                                                                                                                                                                    | ļ                                                                                                                          |                                                               | <u> </u>                  | <u></u> | <u> </u> | <u></u>     | <u> </u>  | ļ         | bit 0 |

| bit 13-8<br>5-4: | Cod<br>11 =<br>10 =<br>01 =<br>00 =<br>Cod<br>11 =<br>00 =<br>00 =<br>Cod<br>11 =<br>10 =<br>01 =<br>01 =<br>01 =<br>01 =<br>01 =<br>01 =<br>01 =<br>00 =<br>01 =<br>00 =<br>01 =<br>01 =<br>00 | e protec<br>= Progra<br>= 0400h<br>= 0200h<br>= 0200h<br>= 0000h<br>= Progra<br>= 0200h<br>= 0000h<br>= protec<br>= Progra<br>= Progra                                                                                                                                                                                                                                                                  | ode prote<br>ction for 2<br>m memo<br>-07FFh c<br>-07FFh c<br>-07FFh c<br>-07FFh c<br>-03FFh c<br>-03FFh c<br>-03FFh c<br>ction for 0<br>m memo<br>m memo | 2K progr<br>ry code<br>ode pro<br>ode pro<br>ode pro<br>ry code<br>ry code<br>ode pro<br>ode pro<br>ode pro<br>ode pro<br>ode pro<br>ode pro<br>ry code<br>ry code | am mem<br>protectic<br>tected<br>tected<br>tected<br>protectic<br>protectic<br>tected<br>gram me<br>protectic<br>protectic | ory<br>on off<br>on off<br>on off<br>mory<br>on off<br>on off |                           |         |          |             |           |           |       |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                       | m memo<br>-01FFh c                                                                                                                                        |                                                                                                                                                                    |                                                                                                                            | on off                                                        |                           |         |          |             |           |           |       |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 00 = 0000h-01FFh code protected<br>Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                           |                                                                                                                                                                    |                                                                                                                            |                                                               |                           |         |          |             |           |           |       |

| bit 6            | BOI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DEN: Br                                                                                                                                                                                                                                                                                                                                                                                                 | own-out l                                                                                                                                                 | Reset E                                                                                                                                                            | nable bit                                                                                                                  | (1)                                                           |                           |         |          |             |           |           |       |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BOR en<br>BOR dis                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                           |                                                                                                                                                                    |                                                                                                                            |                                                               |                           |         |          |             |           |           |       |

| bit 3            | 1 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>RTE</b> : Po<br>PWRT o<br>PWRT e                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                           | īmer Er                                                                                                                                                            | able bit <sup>(</sup>                                                                                                      | 1, 3)                                                         |                           |         |          |             |           |           |       |

| bit 2            | 1 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | WDT en                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                           | mer Ena                                                                                                                                                            | able bit                                                                                                                   |                                                               |                           |         |          |             |           |           |       |

| bit 1-0          | 11 =<br>10 =<br>01 =<br>00 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>0 = WDT disabled</li> <li>FOSC1:FOSC0: Oscillator Selection bits</li> <li>11 = RC oscillator</li> <li>10 = HS oscillator</li> <li>01 = XT oscillator</li> <li>00 = LP oscillator</li> <li>Note 1: Enabling Brown-out Reset automatically enables Power-up Timer (PWRT) regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled anytime Brown-out Detect Reset is</li> </ul> |                                                                                                                                                           |                                                                                                                                                                    |                                                                                                                            |                                                               |                           |         |          |             |           |           |       |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2: Al<br>lis                                                                                                                                                                                                                                                                                                                                                                                            | ted.                                                                                                                                                      |                                                                                                                                                                    | -                                                                                                                          |                                                               | e given the<br>Power-up T |         |          | nable the c | code prot | tection s | cheme |

| Legend<br>R = Re | l:<br>adable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | it                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                           | W =                                                                                                                                                                | Writable                                                                                                                   | bit                                                           | U =                       | Unimple | emented  | bit, read a | s '0'     |           |       |

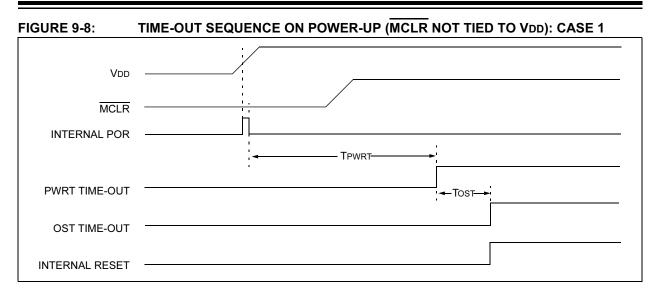

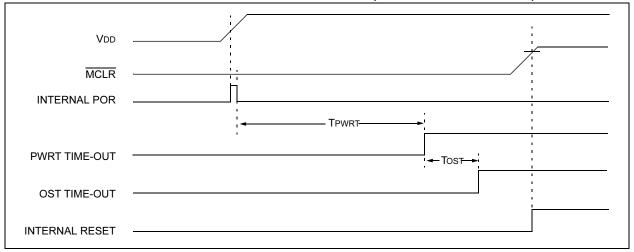

# PIC16C62X

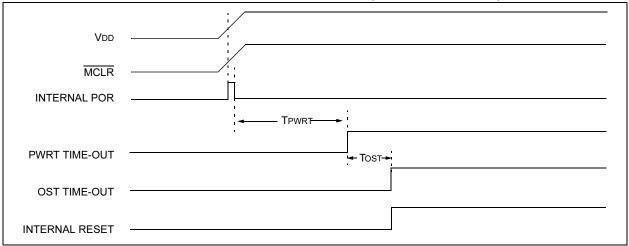

FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 9-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

TABLE 9-6: SUMMARY OF INTERRUPT REGISTERS

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on POR<br>Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 0Bh     | INTCON | GIE   | PEIE  | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1   | —     | CMIF  | —     | —     | —     | —     | —     | —     | -0                    | -0                                             |

| 8Ch     | PIE1   | _     | CMIE  | _     | _     | —     | _     | —     | _     | -0                    | -0                                             |

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

## 9.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and STATUS register). This will have to be implemented in software.

Example 9-3 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x20 in Bank 0 and it must also be defined at 0xA0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 9-3:

- · Stores the W register

- Stores the STATUS register in Bank 0

- Executes the ISR code

- Restores the STATUS (and bank select bit register)

- · Restores the W register

#### EXAMPLE 9-3: SAVING THE STATUS AND W REGISTERS IN RAM

| MOVWF | W_TEMP            | ;copy W to temp register,<br>;could be in either bank                       |

|-------|-------------------|-----------------------------------------------------------------------------|

| SWAPF | STATUS,W          | ;swap status to be saved<br>into W                                          |

| BCF   | STATUS, RPO       | ;change to bank 0 regardless<br>;of current bank                            |

| MOVWF | STATUS_TEMP       | ;save status to bank 0<br>;register                                         |

| :     |                   |                                                                             |

| :     | (ISR)             |                                                                             |

| :     |                   |                                                                             |

| SWAPF | STATUS_TEMP,<br>W | ;swap STATUS_TEMP register<br>;into W, sets bank to origi-<br>nal<br>;state |

| MOVWF | STATUS            | ;move W into STATUS register                                                |

| SWAPF | W_TEMP,F          | ;swap W_TEMP                                                                |

| SWAPF | W_TEMP,W          | ;swap W_TEMP into W                                                         |

## 9.7 Watchdog Timer (WDT)

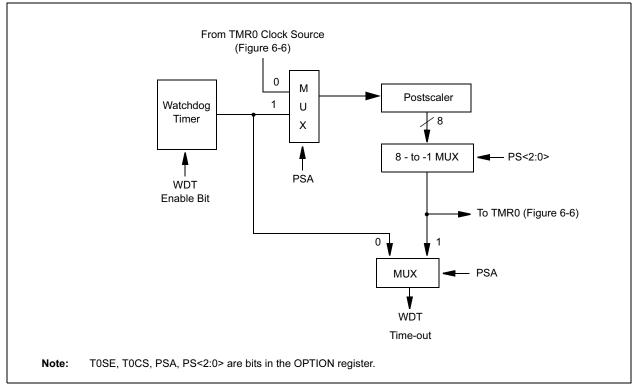

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the CLKIN pin. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET. If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the configuration bit WDTE as clear (Section 9.1).

## 9.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see

DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

#### 9.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

## FIGURE 9-17: WATCHDOG TIMER BLOCK DIAGRAM

| TABLE 9-7: SUMMARY OF WATCHDOG TIMER REGISTERS |

|------------------------------------------------|

|------------------------------------------------|

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 2007h   | Config. bits | —     | BODEN  | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 | —                     | —                               |

| 81h     | OPTION       | RBPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111             | 1111 1111                       |

Legend: Shaded cells are not used by the Watchdog Timer.

**Note:** – = Unimplemented location, read as "0"

+ = Reserved for future use

## 9.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs with no external circuitry drawing current from the I/O pin and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated      |

|-------|------------------------------------------------|

|       | by a WDT time-out does not drive MCLR pin low. |

|       |                                                |

#### 9.8.1 WAKE-UP FROM SLEEP