Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 896B (512 x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 80 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                     |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c620t-04i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART, PRO MATE and PowerSmart are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Accuron, Application Maestro, dsPIC, dsPICDEM, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICkit, PICDEM, PICDEM.net, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPIC, Select Mode, SmartSensor, SmartShunt, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

# **PIC16C62X**

## **EPROM-Based 8-Bit CMOS Microcontrollers**

#### Devices included in this data sheet:

Referred to collectively as PIC16C62X.

- PIC16C620 PIC16C620A

- PIC16C621 PIC16C621A

- PIC16C622 PIC16C622A

- PIC16CR620A

#### **High Performance RISC CPU:**

- Only 35 instructions to learn

- All single cycle instructions (200 ns), except for program branches which are two-cycle

- Operating speed:

- DC 40 MHz clock input

- DC 100 ns instruction cycle

| -           |                   |                |  |  |

|-------------|-------------------|----------------|--|--|

| Device      | Program<br>Memory | Data<br>Memory |  |  |

| PIC16C620   | 512               | 80             |  |  |

| PIC16C620A  | 512               | 96             |  |  |

| PIC16CR620A | 512               | 96             |  |  |

| PIC16C621   | 1K                | 80             |  |  |

| PIC16C621A  | 1K                | 96             |  |  |

| PIC16C622   | 2K                | 128            |  |  |

| PIC16C622A  | 2K                | 128            |  |  |

· Interrupt capability

- 16 special function hardware registers

- 8-level deep hardware stack

- Direct, Indirect and Relative addressing modes

#### **Peripheral Features:**

- 13 I/O pins with individual direction control

- High current sink/source for direct LED drive

- Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VREF) module

- Programmable input multiplexing from device inputs and internal voltage reference

- Comparator outputs can be output signals

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

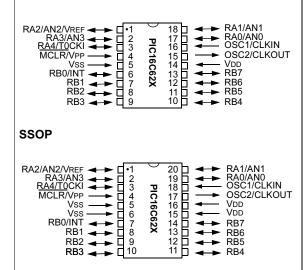

#### Pin Diagrams

#### PDIP, SOIC, Windowed CERDIP

#### **Special Microcontroller Features:**

- · Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- · Programmable code protection

- · Power saving SLEEP mode

- Selectable oscillator options

- Serial in-circuit programming (via two pins)

- Four user programmable ID locations

#### **CMOS Technology:**

- Low power, high speed CMOS EPROM technology

- Fully static design

- · Wide operating range

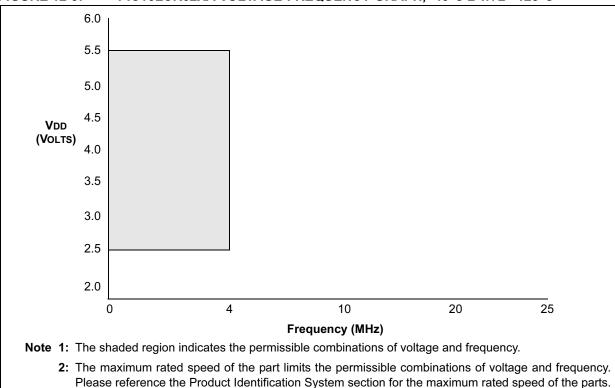

- 2.5V to 5.5V

- Commercial, industrial and extended temperature range

- Low power consumption

- < 2.0 mA @ 5.0V, 4.0 MHz

- 15 μA typical @ 3.0V, 32 kHz

- < 1.0 μA typical standby current @ 3.0V

#### 4.2.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uuluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any STATUS bit. For other instructions not affecting any STATUS bits, see the "Instruction Set Summary".

- Note 1: The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16C62X and should be programmed as '0'. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The <u>C and DC bits</u> operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

#### REGISTER 4-1: STATUS REGISTER (ADDRESS 03H OR 83H)

|         | Reserved                                                                                                                                                                                                                                                                  | Reserved                           | R/W-0          | R-1            | R-1            | R/W-x          | R/W-x        | R/W-x        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|----------------|----------------|--------------|--------------|

|         | IRP                                                                                                                                                                                                                                                                       | RP1                                | RP0            | TO             | PD             | Z              | DC           | С            |

|         | bit 7                                                                                                                                                                                                                                                                     |                                    |                |                |                |                |              | bit 0        |

|         |                                                                                                                                                                                                                                                                           |                                    |                |                |                |                |              |              |

| bit 7   | IRP: Register Bank Select bit (used for indirect addressing)                                                                                                                                                                                                              |                                    |                |                |                |                |              |              |

|         | 1 = Bank 2, 3 (100h - 1FFh)<br>0 = Bank 0, 1 (00h - FFh)                                                                                                                                                                                                                  |                                    |                |                |                |                |              |              |

|         |                                                                                                                                                                                                                                                                           | t is reserved                      |                | 16C62X; alv    | /ays maintai   | n this bit cle | ar.          |              |

| bit 6-5 |                                                                                                                                                                                                                                                                           | Register Ban                       |                |                | -              |                |              |              |

|         |                                                                                                                                                                                                                                                                           | 1 (80h - FFh                       |                |                |                |                |              |              |

|         |                                                                                                                                                                                                                                                                           | 0 (00h - 7Fh                       |                |                |                |                |              |              |

|         | Each bank<br>clear.                                                                                                                                                                                                                                                       | is 128 bytes                       | 5. The RP1 t   | oit is reserve | ed on the PIC  | C16C62X; a     | lways mainta | ain this bit |

| bit 4   | TO: Time-c                                                                                                                                                                                                                                                                | out bit                            |                |                |                |                |              |              |

|         |                                                                                                                                                                                                                                                                           | ower-up, CLI                       | RWDT instruc   | ction. or SLE  | EP instruction | on             |              |              |

|         |                                                                                                                                                                                                                                                                           | time-out oc                        |                | ,              |                |                |              |              |

| bit 3   | PD: Power                                                                                                                                                                                                                                                                 | -down bit                          |                |                |                |                |              |              |

|         | -                                                                                                                                                                                                                                                                         | ower-up or b<br>cution of the      | -              |                | n              |                |              |              |

| bit 2   | Z: Zero bit                                                                                                                                                                                                                                                               |                                    |                |                |                |                |              |              |

|         |                                                                                                                                                                                                                                                                           | sult of an arit<br>sult of an arit |                |                |                | )              |              |              |

| bit 1   |                                                                                                                                                                                                                                                                           | arry/borrow b                      |                | • •            |                |                | )(for borrow | the polarity |

|         | is reversed                                                                                                                                                                                                                                                               | -                                  | ζ ,            |                | ·              |                |              |              |

|         |                                                                                                                                                                                                                                                                           | -out from the                      |                |                |                | rred           |              |              |

|         |                                                                                                                                                                                                                                                                           | ry-out from th                     |                |                |                |                |              |              |

| bit 0   | •                                                                                                                                                                                                                                                                         | orrow bit (AD                      |                |                |                |                |              |              |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> <li>Note: For borrow the polarity is reversed. A subtraction is executed by adding the two's</li> </ul> |                                    |                |                |                |                |              |              |

|         |                                                                                                                                                                                                                                                                           |                                    |                |                |                |                |              |              |

|         | complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.                                                                                                                    |                                    |                |                |                |                |              |              |

|         |                                                                                                                                                                                                                                                                           | loaded with e                      | either the hig | gh or low or   | der bit of the | source reg     | ister.       |              |

|         | Legend:                                                                                                                                                                                                                                                                   | L. L. 14                           |                |                |                |                | hit on all   | 0            |

|         | R = Reada                                                                                                                                                                                                                                                                 |                                    |                | ritable bit    |                | •              | bit, read as |              |

|         | - n = Value                                                                                                                                                                                                                                                               | at POR                             | 1′ = Bi        | it is set      | '0' = Bit i    | scleared       | x = Bit is u | nknown       |

#### 4.2.2.6 PCON Register

The PCON register contains flag bits to differentiate between a Power-on Reset, an external MCLR Reset, WDT Reset or a Brown-out Reset.

| Note: | BOR is unknown on Power-on Reset. It        |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | must then be set by the user and checked    |  |  |  |  |  |

|       | on subsequent RESETS to see if BOR is       |  |  |  |  |  |

|       | cleared, indicating a brown-out has         |  |  |  |  |  |

|       | occurred. The BOR STATUS bit is a "don't    |  |  |  |  |  |

|       | care" and is not necessarily predictable if |  |  |  |  |  |

|       | the brown-out circuit is disabled (by       |  |  |  |  |  |

|       | programming BODEN bit in the                |  |  |  |  |  |

|       | Configuration word).                        |  |  |  |  |  |

#### REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

|   | U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|---|-------|-----|-----|-----|-----|-----|-------|-------|

| ſ | _     | —   | —   | —   | —   | —   | POR   | BOR   |

| - | bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR**: Power-on Reset STATUS bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 **BOR**: Brown-out Reset STATUS bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 4.3 PCL and PCLATH

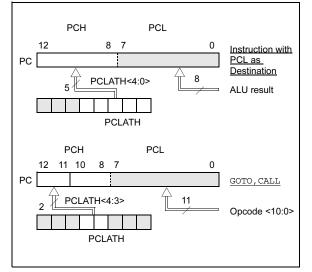

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any RESET, the PC is cleared. Figure 4-8 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-8: LOADING OF PC IN DIFFERENT SITUATIONS

### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

#### 4.3.2 STACK

The PIC16C62X family has an 8-level deep x 13-bit wide hardware stack (Figure 4-2 and Figure 4-3). The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no STATUS bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

#### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

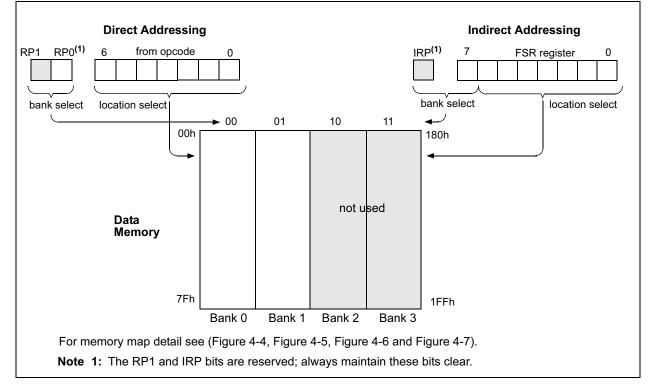

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-9. However, IRP is not used in the PIC16C62X.

A simple program to clear RAM location 20h-7Fh using indirect addressing is shown in Example 4-1.

| EXAMPLE 4-1: |       |       | DIRECT ADDRESSING    |

|--------------|-------|-------|----------------------|

|              | movlw | 0x20  | ;initialize pointer  |

|              | movwf | FSR   | ;to RAM              |

| NEXT         | clrf  | INDF  | ;clear INDF register |

|              | incf  | FSR   | ;inc pointer         |

|              | btfss | FSR,7 | ;all done?           |

|              | goto  | NEXT  | ;no clear next       |

|              |       |       | ;yes continue        |

| CONTI        | NUE:  |       |                      |

|              |       |       |                      |

#### FIGURE 4-9: DIRECT/INDIRECT ADDRESSING PIC16C62X

| Name    | Bit # | Buffer Type           | Function                                                                                                                |

|---------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0  | TTL/ST <sup>(1)</sup> | Input/output or external interrupt input. Internal software programmable weak pull-up.                                  |

| RB1     | bit1  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB2     | bit2  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB3     | bit3  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB4     | bit4  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB5     | bit5  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB6     | bit6  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock pin. |

| RB7     | bit7  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data pin.  |

#### TABLE 5-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h     | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX XXXX       | uuuu uuuu                       |

| 86h     | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h     | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

Legend: u = unchanged, x = unknown

Note 1: Shaded bits are not used by PORTB.

#### 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading the port register reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}\,,\ {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

|                                                       | = =                   |

|-------------------------------------------------------|-----------------------|

| ; Initial PORT settings:                              | PORTB<7:4> Inputs     |

| ;                                                     | PORTB<3:0> Outputs    |

| ; PORTB<7:6> have external ; connected to other circu |                       |

| ;                                                     |                       |

| ;                                                     | PORT latch PORT pins  |

| ;                                                     |                       |

|                                                       | -                     |

|                                                       |                       |

| BCF PORTB, 7                                          | ; 01pp pppp 11pp pppp |

| BCF PORTB, 6                                          | ; 10pp pppp 11pp pppp |

| BSF STATUS, RPO                                       | ;                     |

| BCF TRISB, 7                                          | ;10pp pppp 11pp pppp  |

| BCF TRISB, 6                                          | ;10pp pppp 10pp pppp  |

| ;                                                     |                       |

| ; Note that the user may h                            | nave expected the pin |

| ; values to be 00pp pppp.                             | The 2nd BCF caused    |

| ; RB7 to be latched as the                            | e pin value (High).   |

|                                                       |                       |

## 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

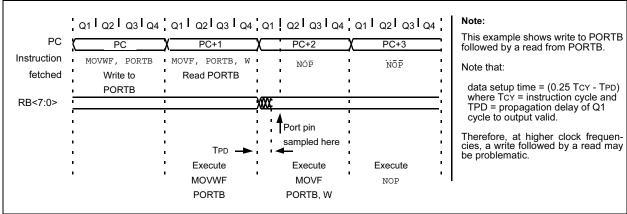

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-7). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 5-7: SUCCESSIVE I/O OPERATION

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to WDT.)

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

|          |              | ,                                             |

|----------|--------------|-----------------------------------------------|

| 1.BCF    | STATUS, RPO  | ;Skip if already in<br>;Bank 0                |

| 2.CLRWDT |              | ;Clear WDT                                    |

| 3.CLRF   | TMR0         | ;Clear TMR0 & Prescaler                       |

| 4.BSF    | STATUS, RPO  | ;Bank 1                                       |

| 5.MOVLW  | '00101111'b; | ;These 3 lines (5, 6, 7)                      |

| 6.MOVWF  | OPTION       | ;are required only if<br>;desired PS<2:0> are |

| 7.CLRWDT |              | ;000 or 001                                   |

| 8.MOVLW  | '00101xxx'b  | ;Set Postscaler to                            |

| 9.MOVWF  | OPTION       | ;desired WDT rate                             |

| 10.BCF   | STATUS, RPO  | ;Return to Bank 0                             |

|          |              |                                               |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 6-2. This precaution must be taken even if the WDT is disabled.

### EXAMPLE 6-2:

#### CHANGING PRESCALER (WDT→TIMER0)

|        | •           | ,                                        |

|--------|-------------|------------------------------------------|

| CLRWDT |             | ;Clear WDT and                           |

|        |             | ;prescaler                               |

| BSF    | STATUS, RPO |                                          |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new<br>;prescale value and |

|        |             | ;clock source                            |

| MOVWF  | OPTION REG  |                                          |

| BCF    | STATUS, RPO |                                          |

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6                 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|----------|-----------------------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 r | imer0 module register |       |        |        |        |        |        | XXXX XXXX       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE      | PEIE                  | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | RBPU     | INTEDG                | TOCS  | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _        |                       | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

**Note:** Shaded bits are not used by TMR0 module.

#### EXAMPLE 8-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; | 4 Inputs Muxed |

|-------|-------------|---|----------------|

| MOVWF | CMCON       | ; | to 2 comps.    |

| BSF   | STATUS, RPO | ; | go to Bank 1   |

| MOVLW | 0x0F        | ; | RA3-RA0 are    |

| MOVWF | TRISA       | ; | inputs         |

| MOVLW | 0xA6        | ; | enable VREF    |

| MOVWF | VRCON       | ; | low range      |

|       |             | ; | set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; | go to Bank O   |

| CALL  | DELAY10     | ; | 10µs delay     |

#### 8.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 8-1) keep VREF from approaching VSS or VDD. The voltage reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the voltage reference can be found in Table 12-2.

### 8.3 Operation During SLEEP

When the device wakes up from SLEEP through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the voltage reference should be disabled.

### 8.4 Effects of a RESET

A device RESET disables the voltage reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

#### 8.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the voltage reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the voltage reference output for external connections to VREF. Figure 8-2 shows an example buffering technique.

# FIGURE 8-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 8-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | -      | CIS    | CM2    | CM1    | CM0    | 00 0000         | 00 0000                         |

| 85h     | TRISA | _     |       |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

**Note:** - = Unimplemented, read as "0"

#### TABLE 9-4: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register | Address | Power-on Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during<br/>SLEEP</li> <li>WDT Reset</li> <li>Brown-out Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP<br/>through interrupt</li> <li>Wake-up from SLEEP<br/>through WDT time-out</li> </ul> |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W        | _       | xxxx xxxx      | นนนน นนนน                                                                                                                                                  | <u></u>                                                                                                           |

| INDF     | 00h     |                | _                                                                                                                                                          | _                                                                                                                 |

| TMR0     | 01h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | นนนน นนนน                                                                                                         |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                                                                                  | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                                                                                   | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR      | 04h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | <u>uuuu</u> uuuu                                                                                                  |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                                                                                     | u uuuu                                                                                                            |

| PORTB    | 06h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | uuuu uuuu                                                                                                         |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                                                                                    | uu uuuu                                                                                                           |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                                                                                     | u uuuu                                                                                                            |

| INTCON   | 0Bh     | 0000 000x      | 0000 000u                                                                                                                                                  | uuuu uqqq <sup>(2)</sup>                                                                                          |

| PIR1     | 0Ch     | -0             | -0                                                                                                                                                         | -q (2,5)                                                                                                          |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                                                                                     | u uuuu                                                                                                            |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PIE1     | 8Ch     | -0             | -0                                                                                                                                                         | -u                                                                                                                |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                                                                        | uu                                                                                                                |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                                                                                  | uuu- uuuu                                                                                                         |

#### TABLE 9-5: INITIALIZATION CONDITION FOR REGISTERS

$\label{eq:legend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 9-4 for RESET value for specific condition.

5: If wake-up was due to comparator input changing, then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = u.

**6:** If RESET was due to brown-out, then bit 0 = 0. All other RESETS will cause bit 0 = u.

## PIC16C62X

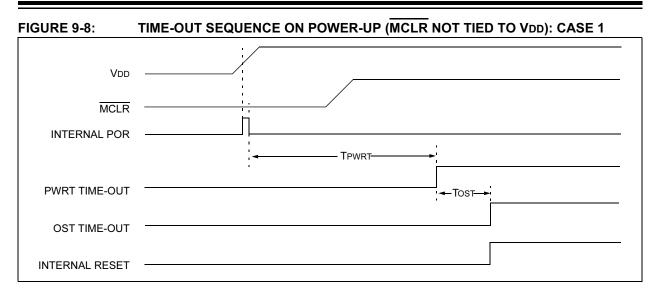

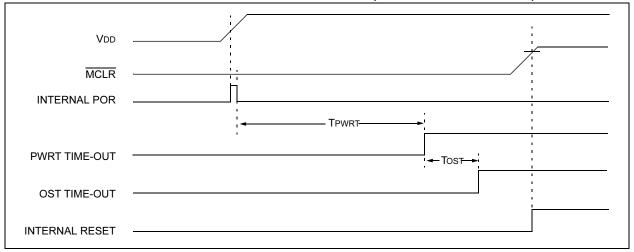

FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

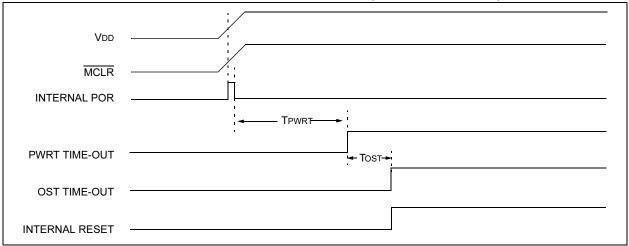

FIGURE 9-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

#### 9.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs with no external circuitry drawing current from the I/O pin and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: |                                                |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|

|       | by a WDT time-out does not drive MCLR pin low. |  |  |  |  |  |

|       |                                                |  |  |  |  |  |

#### 9.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device RESET. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. PD bit, which is set on power-up, is cleared when SLEEP is invoked. TO bit is cleared if WDT wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction after the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

**Note:** If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from SLEEP. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes up from SLEEP, regardless of the source of wake-up.

| Q1 Q2 Q                  | 3 Q4 Q1 Q2 Q3 Q4 Q | Q1                    | Q1 Q2 Q3 Q4      | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 0    | Q1 Q2 Q3 Q4 |

|--------------------------|--------------------|-----------------------|------------------|-------------|------------------|-------------|

| OSC1 //////              |                    | AAAAA                 |                  |             |                  |             |

| CLKOUT(4)                |                    | Tost(2)               | <u> </u>         |             | \ <u>`</u>       |             |

| INT pin                  | 1 I                |                       | 1<br>1           |             | 1                |             |

| NTF flag                 |                    |                       | Interrupt Latend | SV.         |                  |             |

| INTCON<1>)               |                    | <del>≉</del>          | (Note 2)         | ,           |                  |             |

| GIE bit<br>INTCON<7>)    |                    | Processor in<br>SLEEP | 1                |             |                  |             |

| INSTRUCTION FLOW         |                    |                       | 1<br>1<br>1      |             | 1                |             |

| РС Х РС                  | <u>Υ PC+1 Χ</u>    | PC+2                  | X PC+2           | PC + 2      | <u>χ 0004h χ</u> | 0005h       |

| Instruction { Inst(PC) = | SLEEP Inst(PC + 1) |                       | Inst(PC + 2)     |             | Inst(0004h)      | Inst(0005h) |

| Instruction Inst(PC      | - 1) SLEEP         |                       | Inst(PC + 1)     | Dummy cycle | Dummy cycle      | Inst(0004h) |

#### FIGURE 9-18: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**3:** GIE = '1' assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these Osc modes, but shown here for timing reference.

#### 11.14 PICDEM 1 PICmicro Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include analog input, push button switches and eight LEDs.

#### 11.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham

#### 11.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessary hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 FLASH microcontrollers.

#### 11.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

#### 11.18 PICDEM 4 8/14/18-Pin Demonstration Board

The PICDEM 4 can be used to demonstrate the capabilities of the 8-, 14-, and 18-pin PIC16XXXX and PIC18XXXX MCUs, including the PIC16F818/819, PIC16F87/88, PIC16F62XA and the PIC18F1320 family of microcontrollers. PICDEM 4 is intended to showcase the many features of these low pin count parts, including LIN and Motor Control using ECCP. Special provisions are made for low power operation with the supercapacitor circuit, and jumpers allow onboard hardware to be disabled to eliminate current draw in this mode. Included on the demo board are provisions for Crystal, RC or Canned Oscillator modes, a five volt regulator for use with a nine volt wall adapter or battery, DB-9 RS-232 interface, ICD connector for programming via ICSP and development with MPLAB ICD 2, 2x16 liquid crystal display, PCB footprints for H-Bridge motor driver, LIN transceiver and EEPROM. Also included are: header for expansion, eight LEDs, four potentiometers, three push buttons and a prototyping area. Included with the kit is a PIC16F627A and a PIC18F1320. Tutorial firmware is included along with the User's Guide.

### 11.19 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board FLASH memory. A generous prototype area is available for user hardware expansion. NOTES:

# PIC16C62X

#### 12.2 DC Characteristics: PIC16C62XA-04 (Commercial, Industrial, Extended) PIC16C62XA-20 (Commercial, Industrial, Extended) PIC16LC62XA-04 (Commercial, Industrial, Extended) (CONT.)

| PIC16C62XA<br>PIC16LC62XA |     |                                   | Oper<br>Stand<br>Oper | $\begin{array}{l lllllllllllllllllllllllllllllllllll$ |                         |                      |                                                                                                                                                                       |  |  |

|---------------------------|-----|-----------------------------------|-----------------------|-------------------------------------------------------|-------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param.<br>No.             | Sym | Characteristic                    | Min                   | Тур†                                                  | Мах                     | Units                | Conditions                                                                                                                                                            |  |  |

| D010                      | IDD | Supply Current <sup>(2, 4)</sup>  | _                     | 1.2<br>0.4<br>1.0                                     | 2.0<br>1.2<br>2.0       | mA<br>mA<br>mA       | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT mode, (Note 4)*<br>Fosc = 4 MHz, VDD = 3.0V, WDT disabled,<br>XT mode, (Note 4)*<br>Fosc = 10 MHz, VDD = 3.0V, WDT dis- |  |  |

|                           |     |                                   | _                     | 4.0                                                   | 6.0<br>7.0              | mA<br>mA             | abled, HS mode, (Note 6)<br>Fosc = 20 MHz, VDD = 4.5V, WDT dis-<br>abled, HS mode<br>Fosc = 20 MHz, VDD = 5.5V, WDT dis-                                              |  |  |

|                           |     |                                   | _                     | 35                                                    | 70                      | μA                   | abled*, HS mode<br>Fosc = 32 kHz, VDD = 3.0V, WDT dis-<br>abled, LP mode                                                                                              |  |  |

| D010                      | IDD | Supply Current <sup>(2)</sup>     | _                     | 1.2<br>—<br>35                                        | 2.0<br>1.1<br>70        | mA<br>mA<br>μA       | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT mode, (Note 4)*<br>Fosc = 4 MHz, VDD = 2.5V, WDT disabled,<br>XT mode, (Note 4)<br>Fosc = 32 kHz, VDD = 2.5V, WDT dis-  |  |  |

| D020                      | IPD | Power-down Current <sup>(3)</sup> |                       |                                                       | 2.2<br>5.0<br>9.0<br>15 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 3.0V           VDD = 4.5V*           VDD = 5.5V           VDD = 5.5V Extended Temp.                                                                             |  |  |

| D020                      | IPD | Power-down Current <sup>(3)</sup> |                       | <br>                                                  | 2.0<br>2.2<br>9.0<br>15 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 2.5V<br>VDD = 3.0V*<br>VDD = 5.5V<br>VDD = 5.5V Extended Temp.                                                                                                  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

| PIC16CR62XA-04<br>PIC16CR62XA-20 | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                  |  |  |  |  |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PIC16LCR62XA-04                  | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq$ TA $\leq$ +85°C for industrial and0°C $\leq$ TA $\leq$ +70°C for commercial and $-40^{\circ}$ C $<$ TA $\leq$ +125°C for extended |  |  |  |  |  |

| Param. Sym Characteristic No.    | Min Typ† Max Units Conditions                                                                                                                                                                                                         |  |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in k $\Omega$ .

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

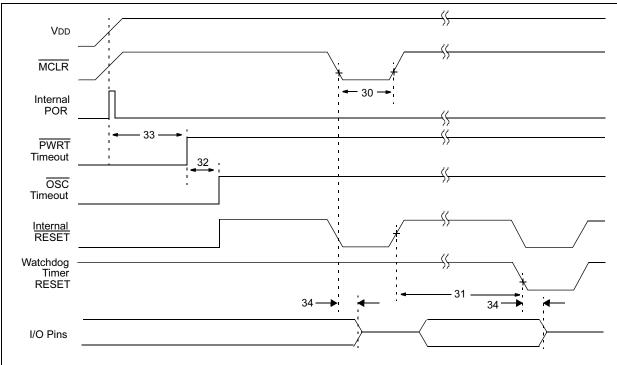

## FIGURE 12-14: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

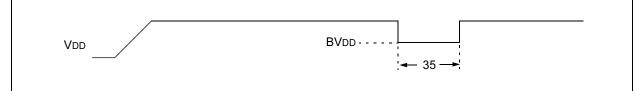

#### FIGURE 12-15: BROWN-OUT RESET TIMING

## TABLE 12-5:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                   | Min  | Тур†      | Max  | Units | Conditions                       |

|------------------|-------|--------------------------------------------------|------|-----------|------|-------|----------------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                           | 2000 | —         | _    | ns    | -40° to +85°C                    |

| 31               | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7*   | 18        | 33*  | ms    | VDD = 5.0V, -40° to +85°C        |

| 32               | Tost  | Oscillation Start-up Timer Period                | _    | 1024 Tosc | _    |       | Tosc = OSC1 period               |

| 33               | Tpwrt | Power-up Timer Period                            | 28*  | 72        | 132* | ms    | VDD = 5.0V, -40° to +85°C        |

| 34               | Tioz  | I/O hi-impedance from MCLR low                   |      | —         | 2.0  | μS    |                                  |

| 35               | TBOR  | Brown-out Reset Pulse Width                      | 100* | _         |      | μS    | $3.7V \leq V\text{DD} \leq 4.3V$ |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

## INDEX

| Α                      |    |

|------------------------|----|

| ADDLW Instruction      | 63 |

| ADDWF Instruction      | 63 |

| ANDLW Instruction      | 63 |

| ANDWF Instruction      | 63 |

| Architectural Overview | 9  |

| Assembler              |    |

| MPASM Assembler        | 75 |

| В                      |    |

| 8                                 |    |

|-----------------------------------|----|

| BCF Instruction                   | 64 |

| Block Diagram                     |    |

| TIMER0                            |    |

| TMR0/WDT PRESCALER                |    |

| Brown-Out Detect (BOD)            |    |

| BSF Instruction                   |    |

| BTFSC Instruction                 | 64 |

| BTFSS Instruction                 | 65 |

| С                                 |    |

| C Compilers                       |    |

| MPLAB C17                         | 76 |

| MPLAB C18                         | 76 |

| MPLAB C30                         | 76 |

| CALL Instruction                  | 65 |

| Clocking Scheme/Instruction Cycle |    |

| CLRF Instruction                  |    |

| CLRW Instruction                  |    |

| CLRWDT Instruction                |    |

|                                   |    |

| C Compilers                       |    |

|-----------------------------------|----|

| MPLAB C17                         | 76 |

| MPLAB C18                         | 76 |

| MPLAB C30                         | 76 |

| CALL Instruction                  | 65 |

| Clocking Scheme/Instruction Cycle |    |

| CLRF Instruction                  | 65 |

| CLRW Instruction                  |    |

| CLRWDT Instruction                |    |

| Code Protection                   | 60 |

| COMF Instruction                  |    |

| Comparator Configuration          |    |

| Comparator Interrupts             |    |

| Comparator Module                 |    |

| Comparator Operation              |    |

| Comparator Reference              |    |

| Configuration Bits                |    |

| Configuring the Voltage Reference |    |

| Crystal Operation                 |    |

| _                                 |    |

#### D

| Data Memory Organization14                   |

|----------------------------------------------|

| DC Characteristics                           |

| PIC16C717/770/771 88, 89, 90, 91, 96, 97, 98 |

| DECF Instruction                             |

| DECFSZ Instruction                           |

| Demonstration Boards                         |

| PICDEM 1                                     |

| PICDEM 17                                    |

| PICDEM 18R PIC18C601/80179                   |

| PICDEM 2 Plus                                |

| PICDEM 3 PIC16C92X                           |

| PICDEM 4                                     |

| PICDEM LIN PIC16C43X79                       |

| PICDEM USB PIC16C7X579                       |

| PICDEM.net Internet/Ethernet                 |

| Development Support75                        |

| E                                            |

| Errata                                       |

| Evaluation and Programming Tools             |

| External Crystal Oscillator Circuit          |

| G                                            |

| General purpose Register File                |

| GOTO Instruction                             |

| 1                                                                        |    |

|--------------------------------------------------------------------------|----|

| I/O Ports                                                                |    |

| I/O Programming Considerations                                           |    |

| ID Locations                                                             |    |

| INCF Instruction                                                         |    |

| INCFSZ Instruction<br>In-Circuit Serial Programming                      |    |

| Indirect Addressing, INDF and FSR Registers                              |    |

| Instruction Flow/Pipelining                                              |    |

| Instruction Set                                                          |    |

| ADDLW                                                                    | 63 |

| ADDWF                                                                    |    |

| ANDLW                                                                    |    |

| ANDWF                                                                    |    |

| BCF<br>BSF                                                               |    |

| BSF<br>BTFSC                                                             |    |

| BTFSS                                                                    |    |

| CALL                                                                     |    |

| CLRF                                                                     |    |

| CLRW                                                                     | 66 |

| CLRWDT                                                                   | 66 |

| COMF                                                                     |    |

| DECF                                                                     |    |

| DECFSZ                                                                   |    |

| GOTO                                                                     |    |

| INCFINCFSZ                                                               |    |

| INCI SZ                                                                  |    |

| IORWF                                                                    |    |

| MOVF                                                                     |    |

| MOVLW                                                                    | 68 |

| MOVWF                                                                    | 69 |

| NOP                                                                      |    |

| OPTION                                                                   |    |

| RETFIE                                                                   |    |

| RETLW<br>RETURN                                                          |    |

| RLF                                                                      |    |

| RRF                                                                      |    |

| SLEEP                                                                    |    |

| SUBLW                                                                    |    |

| SUBWF                                                                    | 72 |

| SWAPF                                                                    | 73 |

| TRIS                                                                     |    |

| XORLW                                                                    |    |

| XORWF                                                                    |    |

| Instruction Set Summary<br>INT Interrupt                                 |    |

| INTCON Register                                                          |    |

| Interrupts                                                               |    |

| IORLW Instruction                                                        |    |

| IORWF Instruction                                                        |    |

| Μ                                                                        |    |

| MOVF Instruction                                                         | 69 |

| MOVLW Instruction                                                        |    |

| MOVWF Instruction                                                        | 69 |

| MPLAB ASM30 Assembler, Linker, Librarian                                 | 76 |