Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

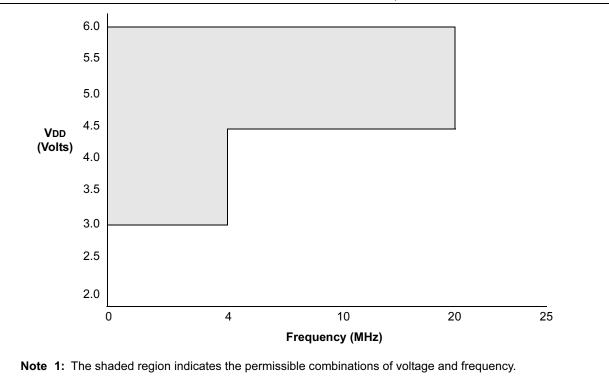

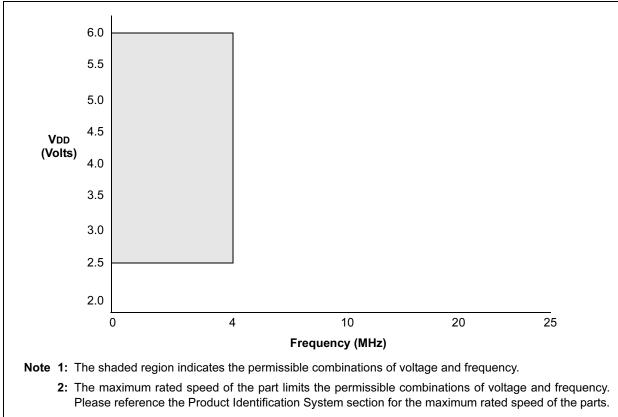

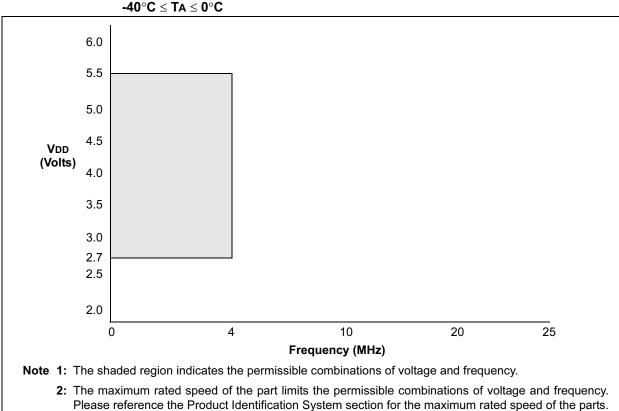

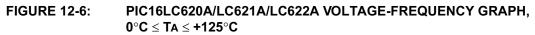

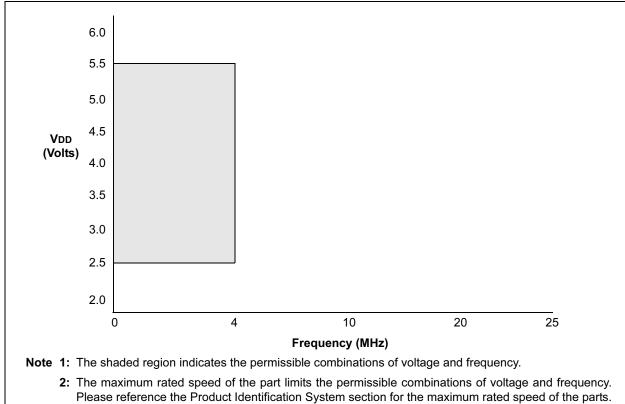

| Speed                      | 4MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 13                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 80 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621-04-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

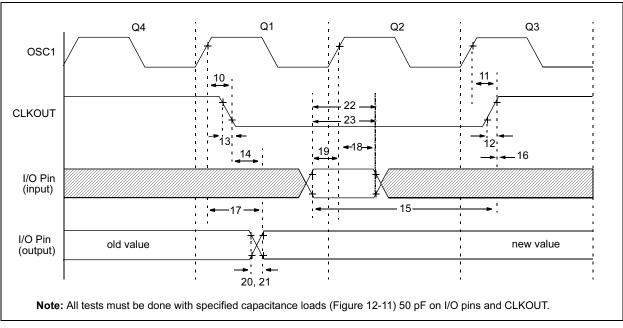

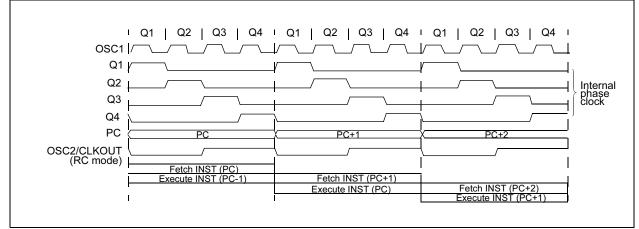

# 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

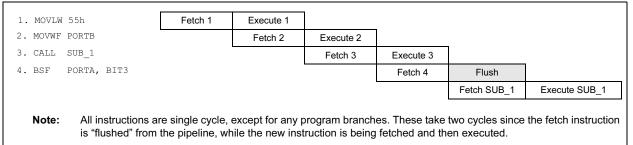

# 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

# FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

# EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

# FIGURE 4-4: DATA MEMORY MAP FOR THE PIC16C620/621

| File     |                     |                     | File        |

|----------|---------------------|---------------------|-------------|

| Address  | 3                   |                     | Address     |

| 00h      | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h         |

| 01h      | TMR0                | OPTION              | 81h         |

| 02h      | PCL                 | PCL                 | 82h         |

| 03h      | STATUS              | STATUS              | 83h         |

| 04h      | FSR                 | FSR                 | 84h         |

| 05h      | PORTA               | TRISA               | 85h         |

| 06h      | PORTB               | TRISB               | 86h         |

| 07h      |                     |                     | 87h         |

| 08h      |                     |                     | 88h         |

| 09h      |                     |                     | 89h         |

| 0Ah      | PCLATH              | PCLATH              | 8Ah         |

| 0Bh      | INTCON              | INTCON              | 8Bh         |

| 0Ch      | PIR1                | PIE1                | 8Ch         |

| 0Dh      |                     |                     | 8Dh         |

| 0Eh      |                     | PCON                | 8Eh         |

| 0Fh      |                     |                     | 8Fh         |

| 10h      |                     |                     | 90h         |

| 11h      |                     |                     | 91h         |

| 12h      |                     |                     | 92h         |

| 13h      |                     |                     | 93h         |

| 14h      |                     |                     | 94h         |

| 15h      |                     |                     | 95h         |

| 16h      |                     |                     | 96h         |

| 17h      |                     |                     | 97h         |

| 18h      |                     |                     | 98h         |

| 19h      |                     |                     | 99h         |

| 1Ah      |                     |                     | 9Ah         |

| 1Bh      |                     |                     | 9Bh         |

| 1Ch      |                     |                     | 9Ch         |

| 1Dh      |                     |                     | 9Dh         |

| 1Eh      |                     |                     | 9Eh         |

| 1Fh      | CMCON               | VRCON               | 9Fh         |

| 20h      |                     | _                   | A0h         |

|          | General             |                     |             |

|          | Purpose<br>Register |                     |             |

| 6Fh      | 5                   |                     |             |

| 70h      |                     |                     |             |

|          |                     |                     |             |

|          |                     |                     |             |

|          |                     |                     |             |

| 7Fh      |                     |                     | FFh         |

|          | Bank 0              | Bank 1              |             |

| <b>—</b> |                     | 1 4                 |             |

| Unimp    | plemented data me   | mory locations, r   | ead as '0'. |

| Note 1:  | Not a physical re   | egister.            |             |

|          |                     |                     |             |

|          |                     |                     |             |

# FIGURE 4-5:

# DATA MEMORY MAP FOR THE PIC16C622

|                 | 1116                |                     |                 |

|-----------------|---------------------|---------------------|-----------------|

| File<br>Address | 8                   |                     | File<br>Address |

| 00h             | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |

| 01h             | TMR0                | OPTION              | 81h             |

| 02h             | PCL                 | PCL                 | 82h             |

| 03h             | STATUS              | STATUS              | 83h             |

| 04h             | FSR                 | FSR                 | 84h             |

| 05h             | PORTA               | TRISA               | 85h             |

| 06h             | PORTB               | TRISB               | 86h             |

| 00h             | TOILID              | TRIOD               | 87h             |

| 07h<br>08h      |                     |                     | 88h             |

| 00h             |                     |                     | 89h             |

| 03h<br>0Ah      | PCLATH              | PCLATH              | 8Ah             |

| 0An<br>0Bh      | INTCON              | INTCON              | 8Bh             |

| 0Dh             | PIR1                | PIE1                | 8Ch             |

| 0Ch<br>0Dh      | PIRI                | PIEI                | 8Dh             |

|                 |                     | PCON                |                 |

| 0Eh<br>0Fh      |                     | PCON                | 8Eh             |

|                 |                     |                     | 8Fh             |

| 10h             |                     |                     | 90h             |

| 11h             |                     |                     | 91h             |

| 12h             |                     |                     | 92h             |

| 13h             |                     |                     | 93h             |

| 14h             |                     |                     | 94h             |

| 15h             |                     |                     | 95h             |

| 16h             |                     |                     | 96h             |

| 17h             |                     |                     | 97h             |

| 18h             |                     |                     | 98h             |

| 19h             |                     |                     | 99h             |

| 1Ah             |                     |                     | 9Ah             |

| 1Bh             |                     |                     | 9Bh             |

| 1Ch             |                     |                     | 9Ch             |

| 1Dh             |                     |                     | 9Dh             |

| 1Eh             |                     |                     | 9Eh             |

| 1Fh             | CMCON               | VRCON               | 9Fh             |

| 20h             |                     |                     | A0h             |

|                 | General<br>Purpose  | General<br>Purpose  |                 |

|                 | Register            | Register            |                 |

|                 | 0                   | 5                   | BFh             |

|                 |                     |                     | C0h             |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

| 7Fh             |                     |                     | FFh             |

| , , , , , ,     | Bank 0              | Bank 1              |                 |

|                 |                     |                     |                 |

| Unim            | plemented data me   | mory locations, re  | ad as '0'.      |

| Note 1:         | Not a physical re   | aister              |                 |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

# 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM. The Special Function Registers can be classified into two sets (core and peripheral). The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name          | Bit 7               | Bit 6              | Bit 5       | Bit 4        | Bit 3        | Bit 2        | Bit 1       | Bit 0      | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|---------------|---------------------|--------------------|-------------|--------------|--------------|--------------|-------------|------------|-----------------------|------------------------------------------------|

| Bank 0  |               |                     |                    |             |              |              |              |             |            |                       |                                                |

| 00h     | INDF          | Addressin register) | g this locati      | ion uses co | ntents of FS | SR to addre  | ess data me  | mory (not a | n physical | XXXX XXXX             | XXXX XXXX                                      |

| 01h     | TMR0          | Timer0 Mo           | odule's Reg        | ister       |              |              |              |             |            | xxxx xxxx             | uuuu uuuu                                      |

| 02h     | PCL           | Program 0           | Counter's (F       | PC) Least S | ignificant B | yte          |              |             |            | 0000 0000             | 0000 0000                                      |

| 03h     | STATUS        | IRP <sup>(2)</sup>  | RP1 <sup>(2)</sup> | RP0         | TO           | PD           | Z            | DC          | С          | 0001 1xxx             | 000q quuu                                      |

| 04h     | FSR           | Indirect da         | ata memory         | address po  | ointer       |              |              |             |            | xxxx xxxx             | uuuu uuuu                                      |

| 05h     | PORTA         | —                   | _                  | —           | RA4          | RA3          | RA2          | RA1         | RA0        | x 0000                | u 0000                                         |

| 06h     | PORTB         | RB7                 | RB6                | RB5         | RB4          | RB3          | RB2          | RB1         | RB0        | xxxx xxxx             | uuuu uuuu                                      |

| 07h-09h | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 0Ah     | PCLATH        | _                   | _                  | _           | Write buffe  | er for upper | 5 bits of pr | ogram coui  | nter       | 0 0000                | 0 0000                                         |

| 0Bh     | INTCON        | GIE                 | PEIE               | T0IE        | INTE         | RBIE         | T0IF         | INTF        | RBIF       | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1          | _                   | CMIF               | —           | _            | —            | _            | —           | —          | -0                    | -0                                             |

| 0Dh-1Eh | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 1Fh     | CMCON         | C2OUT               | C1OUT              | —           | _            | CIS          | CM2          | CM1         | CM0        | 00 0000               | 00 0000                                        |

| Bank 1  |               |                     |                    |             |              |              |              |             |            |                       |                                                |

| 80h     | INDF          | Addressin register) | g this locati      | on uses co  | ntents of FS | SR to addre  | ess data me  | mory (not a | ı physical | xxxx xxxx             | xxxx xxxx                                      |

| 81h     | OPTION        | RBPU                | INTEDG             | TOCS        | TOSE         | PSA          | PS2          | PS1         | PS0        | 1111 1111             | 1111 1111                                      |

| 82h     | PCL           | Program 0           | Counter's (F       | PC) Least S | ignificant B | yte          |              |             |            | 0000 0000             | 0000 0000                                      |

| 83h     | STATUS        | IRP <sup>(2)</sup>  | RP1 <sup>(2)</sup> | RP0         | TO           | PD           | Z            | DC          | С          | 0001 1xxx             | 000q quuu                                      |

| 84h     | FSR           | Indirect da         | ata memory         | address po  | ointer       |              |              |             |            | xxxx xxxx             | uuuu uuuu                                      |

| 85h     | TRISA         | —                   | _                  | _           | TRISA4       | TRISA3       | TRISA2       | TRISA1      | TRISA0     | 1 1111                | 1 1111                                         |

| 86h     | TRISB         | TRISB7              | TRISB6             | TRISB5      | TRISB4       | TRISB3       | TRISB2       | TRISB1      | TRISB0     | 1111 1111             | 1111 1111                                      |

| 87h-89h | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 8Ah     | PCLATH        | —                   | _                  | _           | Write buffe  | er for upper | 5 bits of pr | ogram coui  | nter       | 0 0000                | 0 0000                                         |

| 8Bh     | INTCON        | GIE                 | PEIE               | T0IE        | INTE         | RBIE         | T0IF         | INTF        | RBIF       | 0000 000x             | 0000 000u                                      |

| 8Ch     | PIE1          | —                   | CMIE               | —           | —            | —            | —            | —           | —          | -0                    | -0                                             |

| 8Dh     | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 8Eh     | PCON          | —                   |                    | _           |              | _            |              | POR         | BOR        | 0x                    | uq                                             |

| 8Fh-9Eh | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 9Fh     | VRCON         | VREN                | VROE               | VRR         | —            | VR3          | VR2          | VR1         | VR0        | 000- 0000             | 000- 0000                                      |

TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16C62X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown,

${\rm q}$  = value depends on condition, shaded = unimplemented

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

2: IRP & RP1 bits are reserved; always maintain these bits clear.

# 4.2.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uuluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any STATUS bit. For other instructions not affecting any STATUS bits, see the "Instruction Set Summary".

- Note 1: The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16C62X and should be programmed as '0'. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The <u>C and DC bits</u> operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

# REGISTER 4-1: STATUS REGISTER (ADDRESS 03H OR 83H)

|         | Reserved            | Reserved                           | R/W-0          | R-1            | R-1            | R/W-x          | R/W-x        | R/W-x          |

|---------|---------------------|------------------------------------|----------------|----------------|----------------|----------------|--------------|----------------|

|         | IRP                 | RP1                                | RP0            | TO             | PD             | Z              | DC           | С              |

|         | bit 7               |                                    |                |                |                |                |              | bit 0          |

|         |                     |                                    |                |                |                |                |              |                |

| bit 7   | -                   | ter Bank Sel                       | -              | d for indirect | addressing     | )              |              |                |

|         |                     | , 3 (100h - 1<br>, 1 (00h - FF     |                |                |                |                |              |                |

|         |                     | t is reserved                      |                | 16C62X; alv    | /ays maintai   | n this bit cle | ar.          |                |

| bit 6-5 |                     | Register Ban                       |                |                | -              |                |              |                |

|         |                     | 1 (80h - FFh                       |                |                |                |                |              |                |

|         |                     | 0 (00h - 7Fh                       |                |                |                |                |              |                |

|         | Each bank<br>clear. | is 128 bytes                       | . The RP1 t    | oit is reserve | ed on the PIC  | C16C62X; a     | lways mainta | ain this bit   |

| bit 4   | TO: Time-c          | out bit                            |                |                |                |                |              |                |

|         |                     | ower-up, CLI                       | RWDT instruc   | ction. or SLE  | EP instruction | on             |              |                |

|         |                     | time-out oc                        |                | ,              |                |                |              |                |

| bit 3   | PD: Power           | -down bit                          |                |                |                |                |              |                |

|         | -                   | ower-up or b<br>cution of the      | -              |                | n              |                |              |                |

| bit 2   | Z: Zero bit         |                                    |                |                |                |                |              |                |

|         |                     | sult of an arit<br>sult of an arit |                |                |                | )              |              |                |

| bit 1   |                     | arry/borrow b                      |                | • •            |                |                | )(for borrow | the polarity   |

|         | is reversed         | -                                  | ζ ,            |                | ·              |                |              |                |

|         |                     | -out from the                      |                |                |                | rred           |              |                |

|         |                     | ry-out from th                     |                |                |                |                |              |                |

| bit 0   | •                   | orrow bit (AD                      |                |                |                |                |              |                |

|         | •                   | -out from the<br>ry-out from th    | -              |                |                |                |              |                |

|         | Note:               | For borrow t                       | he polarity i  | s reversed.    | A subtraction  | on is execut   | ed by addin  | g the two's    |

|         |                     | complement                         |                |                |                |                |              | s, this bit is |

|         |                     | loaded with e                      | either the hig | gh or low or   | der bit of the | source reg     | ister.       |                |

|         | Legend:             | L. L. 14                           |                |                |                |                | hit as a d   | 0              |

|         | R = Reada           |                                    |                | ritable bit    |                | •              | bit, read as |                |

|         | - n = Value         | at POR                             | 1′ = Bi        | it is set      | '0' = Bit i    | scleared       | x = Bit is u | nknown         |

# 4.2.2.4 PIE1 Register

This register contains the individual enable bit for the comparator interrupt.

| <b>REGISTER 4-4:</b> | PIE1 REGIS                                                                                                                                        | PIE1 REGISTER (ADDRESS 8CH)       |                |     |  |   |   |       |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------|-----|--|---|---|-------|--|--|--|

|                      | U-0                                                                                                                                               | U-0 R/W-0 U-0 U-0 U-0 U-0 U-0 U-0 |                |     |  |   |   |       |  |  |  |

|                      |                                                                                                                                                   | CMIE                              | _              |     |  | — | _ | —     |  |  |  |

|                      | bit 7                                                                                                                                             |                                   |                |     |  |   |   | bit 0 |  |  |  |

| bit 7                | Unimpleme                                                                                                                                         | nted: Read                        | d as '0'       |     |  |   |   |       |  |  |  |

| bit 6                | <b>CMIE</b> : Comp<br>1 = Enables<br>0 = Disables                                                                                                 | the Compa                         | arator interru | upt |  |   |   |       |  |  |  |

| bit 5-0              | Unimpleme                                                                                                                                         | nted: Read                        | d as '0'       |     |  |   |   |       |  |  |  |

|                      | Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'- n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown |                                   |                |     |  |   |   |       |  |  |  |

# 4.2.2.5 PIR1 Register

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of |

|-------|--------------------------------------------------------------------------------------------|

|       | its corresponding enable bit or the global<br>enable bit, GIE (INTCON<7>). User            |

|       | software should ensure the appropriate                                                     |

|       | interrupt flag bits are clear prior to enabling                                            |

|       | an interrupt.                                                                              |

# REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

| ER 4-5: | PIRT REGI   | SIER (AL      | DRESS 0       | СН)          |              |           |                |        |

|---------|-------------|---------------|---------------|--------------|--------------|-----------|----------------|--------|

|         | U-0         | R/W-0         | U-0           | U-0          | U-0          | U-0       | U-0            | U-0    |

|         |             | CMIF          |               | —            | _            |           |                |        |

|         | bit 7       |               |               |              |              |           |                | bit 0  |

|         |             |               |               |              |              |           |                |        |

| bit 7   | Unimpleme   | ented: Rea    | d as '0'      |              |              |           |                |        |

| bit 6   | CMIF: Com   | parator Inte  | errupt Flag b | it           |              |           |                |        |

|         | 1 = Compai  | rator input h | nas changed   | l            |              |           |                |        |

|         | 0 = Compai  | rator input h | nas not chan  | iged         |              |           |                |        |

| bit 5-0 | Unimpleme   | ented: Rea    | d as '0'      |              |              |           |                |        |

|         |             |               |               |              |              |           |                |        |

|         | Legend:     |               |               |              |              |           |                |        |

|         | R = Readab  | ole bit       | W = W         | /ritable bit | U = Unim     | plemented | bit, read as ' | 0'     |

|         | - n = Value | at POR        | '1' = B       | it is set    | '0' = Bit is | s cleared | x = Bit is u   | nknown |

# EXAMPLE 8-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; | 4 Inputs Muxed |

|-------|-------------|---|----------------|

| MOVWF | CMCON       | ; | to 2 comps.    |

| BSF   | STATUS, RPO | ; | go to Bank 1   |

| MOVLW | 0x0F        | ; | RA3-RA0 are    |

| MOVWF | TRISA       | ; | inputs         |

| MOVLW | 0xA6        | ; | enable VREF    |

| MOVWF | VRCON       | ; | low range      |

|       |             | ; | set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; | go to Bank O   |

| CALL  | DELAY10     | ; | 10µs delay     |

# 8.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 8-1) keep VREF from approaching VSS or VDD. The voltage reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the voltage reference can be found in Table 12-2.

# 8.3 Operation During SLEEP

When the device wakes up from SLEEP through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the voltage reference should be disabled.

# 8.4 Effects of a RESET

A device RESET disables the voltage reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

# 8.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the voltage reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the voltage reference output for external connections to VREF. Figure 8-2 shows an example buffering technique.

# FIGURE 8-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

# TABLE 8-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | -      | CIS    | CM2    | CM1    | CM0    | 00 0000         | 00 0000                         |

| 85h     | TRISA | _     |       |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

**Note:** - = Unimplemented, read as "0"

# 9.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance or one with parallel resonance.

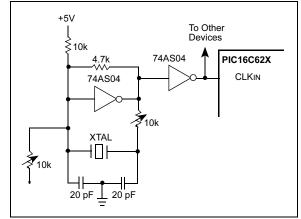

Figure 9-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

# FIGURE 9-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

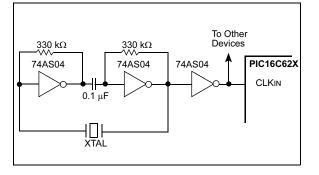

Figure 9-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a  $180^{\circ}$  phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

### FIGURE 9-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

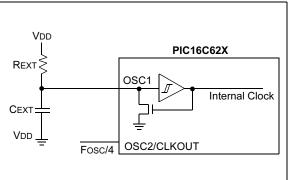

# 9.2.4 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 9-5 shows how the R/C combination is connected to the PIC16C62X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See Section 13.0 for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See Section 13.0 for variation of oscillator frequency due to VDD for given REXT/CEXT values, as well as frequency variation due to operating temperature for given R, C and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

# FIGURE 9-5: RC OSCILLATOR MODE

# TABLE 9-4: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register | Address | Power-on Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during<br/>SLEEP</li> <li>WDT Reset</li> <li>Brown-out Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP<br/>through interrupt</li> <li>Wake-up from SLEEP<br/>through WDT time-out</li> </ul> |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W        | _       | xxxx xxxx      | นนนน นนนน                                                                                                                                                  | <u></u>                                                                                                           |

| INDF     | 00h     |                | _                                                                                                                                                          | _                                                                                                                 |

| TMR0     | 01h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | นนนน นนนน                                                                                                         |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                                                                                  | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                                                                                   | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR      | 04h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                                                                                     | u uuuu                                                                                                            |

| PORTB    | 06h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | uuuu uuuu                                                                                                         |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                                                                                    | uu uuuu                                                                                                           |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                                                                                     | u uuuu                                                                                                            |

| INTCON   | 0Bh     | 0000 000x      | 0000 000u                                                                                                                                                  | uuuu uqqq <sup>(2)</sup>                                                                                          |

| PIR1     | 0Ch     | -0             | -0                                                                                                                                                         | -q (2,5)                                                                                                          |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                                                                                     | u uuuu                                                                                                            |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PIE1     | 8Ch     | -0             | -0                                                                                                                                                         | -u                                                                                                                |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                                                                        | uu                                                                                                                |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                                                                                  | uuu- uuuu                                                                                                         |

# TABLE 9-5: INITIALIZATION CONDITION FOR REGISTERS

$\label{eq:legend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 9-4 for RESET value for specific condition.

5: If wake-up was due to comparator input changing, then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = u.

**6:** If RESET was due to brown-out, then bit 0 = 0. All other RESETS will cause bit 0 = u.

# **FIGURE 9-11: EXTERNAL POWER-ON RESET CIRCUIT (FOR** SLOW VDD POWER-UP) Vdd Vdd D R R1 MCLR PIC16C62X С Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down. **2:** < 40 k $\Omega$ is recommended to make sure that voltage drop across R does not violate the device's electrical specification. **3:** R1 = $100\Omega$ to 1 k $\Omega$ will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin

breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

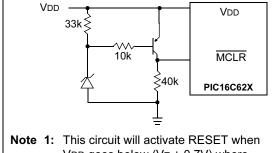

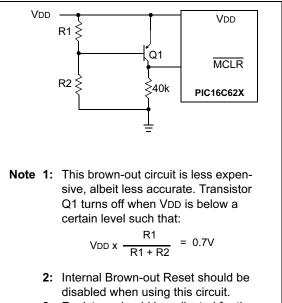

# FIGURE 9-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate RESET when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- **2:** Internal Brown-out Reset circuitry should be disabled when using this circuit.

### FIGURE 9-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

**3:** Resistors should be adjusted for the characteristics of the transistor.

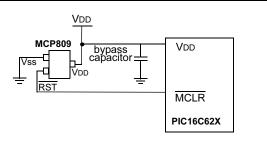

### FIGURE 9-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active RESET pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

| TABLE 10-2. FICTOCO2A INSTRUCTION SET | TABLE 10-2: | PIC16C62X INSTRUCTION SET |

|---------------------------------------|-------------|---------------------------|

|---------------------------------------|-------------|---------------------------|

| Mnemonic,<br>Operands                 |         | Description C                |       | 14-Bit Opcode |      |      |      | Status   | Notes |

|---------------------------------------|---------|------------------------------|-------|---------------|------|------|------|----------|-------|

|                                       |         |                              |       | MSb           |      |      | LSb  | Affected |       |

| BYTE-OR                               | ENTED I | FILE REGISTER OPERATIONS     |       |               |      |      |      |          |       |

| ADDWF                                 | f, d    | Add W and f                  | 1     | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |

| ANDWF                                 | f, d    | AND W with f                 | 1     | 00            | 0101 | dfff | ffff | Z        | 1,2   |

| CLRF                                  | f       | Clear f                      | 1     | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW                                  | -       | Clear W                      | 1     | 00            | 0001 | 0000 | 0011 | Z        |       |

| COMF                                  | f, d    | Complement f                 | 1     | 00            | 1001 | dfff | ffff | Z        | 1,2   |

| DECF                                  | f, d    | Decrement f                  | 1     | 00            | 0011 | dfff | ffff | Z        | 1,2   |

| DECFSZ                                | f, d    | Decrement f, Skip if 0       | 1(2)  | 00            | 1011 | dfff | ffff |          | 1,2,3 |

| INCF                                  | f, d    | Increment f                  | 1     | 00            | 1010 | dfff | ffff | Z        | 1,2   |

| INCFSZ                                | f, d    | Increment f, Skip if 0       | 1(2)  | 00            | 1111 | dfff | ffff |          | 1,2,3 |

| IORWF                                 | f, d    | Inclusive OR W with f        | 1     | 00            | 0100 | dfff | ffff | Z        | 1,2   |

| MOVF                                  | f, d    | Move f                       | 1     | 00            | 1000 | dfff | ffff | Z        | 1,2   |

| MOVWF                                 | f       | Move W to f                  | 1     | 00            | 0000 | lfff | ffff |          |       |

| NOP                                   | -       | No Operation                 | 1     | 00            | 0000 | 0xx0 | 0000 |          |       |

| RLF                                   | f, d    | Rotate Left f through Carry  | 1     | 00            | 1101 | dfff | ffff | С        | 1,2   |

| RRF                                   | f, d    | Rotate Right f through Carry | 1     | 00            | 1100 | dfff | ffff | С        | 1,2   |

| SUBWF                                 | f, d    | Subtract W from f            | 1     | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |

| SWAPF                                 | f, d    | Swap nibbles in f            | 1     | 00            | 1110 | dfff | ffff |          | 1,2   |

| XORWF                                 | f, d    | Exclusive OR W with f        | 1     | 00            | 0110 | dfff | ffff | Z        | 1,2   |

| BIT-ORIENTED FILE REGISTER OPERATIONS |         |                              |       |               |      |      |      |          |       |

| BCF                                   | f, b    | Bit Clear f                  | 1     | 01            | 00bb | bfff | ffff |          | 1,2   |

| BSF                                   | f, b    | Bit Set f                    | 1     | 01            | 01bb | bfff | ffff |          | 1,2   |

| BTFSC                                 | f, b    | Bit Test f, Skip if Clear    | 1 (2) | 01            | 10bb | bfff | ffff |          | 3     |

| BTFSS                                 | f, b    | Bit Test f, Skip if Set      | 1 (2) | 01            | 11bb | bfff | ffff |          | 3     |

| LITERAL                               | AND CO  | NTROL OPERATIONS             |       |               |      |      |      |          |       |

| ADDLW                                 | k       | Add literal and W            | 1     | 11            | 111x | kkkk | kkkk | C,DC,Z   |       |

| ANDLW                                 | k       | AND literal with W           | 1     | 11            | 1001 | kkkk | kkkk | Z        |       |

| CALL                                  | k       | Call subroutine              | 2     | 10            | 0kkk | kkkk | kkkk |          |       |

| CLRWDT                                | -       | Clear Watchdog Timer         | 1     | 00            | 0000 | 0110 | 0100 | TO,PD    |       |

| GOTO                                  | k       | Go to address                | 2     | 10            | 1kkk | kkkk | kkkk |          |       |

| IORLW                                 | k       | Inclusive OR literal with W  | 1     | 11            | 1000 | kkkk | kkkk | Z        |       |

| MOVLW                                 | k       | Move literal to W            | 1     | 11            | 00xx | kkkk | kkkk |          |       |

| RETFIE                                | -       | Return from interrupt        | 2     | 00            | 0000 | 0000 | 1001 |          |       |

| RETLW                                 | k       | Return with literal in W     | 2     | 11            | 01xx | kkkk | kkkk |          |       |

| RETURN                                | -       | Return from Subroutine       | 2     | 00            | 0000 | 0000 | 1000 |          |       |

| SLEEP                                 | -       | Go into Standby mode         | 1     | 00            | 0000 | 0110 | 0011 | TO,PD    |       |

| SUBLW                                 | k       | Subtract W from literal      | 1     | 11            | 110x | kkkk | kkkk | C,DC,Z   |       |

| XORLW                                 | k       | Exclusive OR literal with W  | 1     | 11            | 1010 | kkkk | kkkk | Z        |       |

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**2:** If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

# **10.1** Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |  |  |

| Encoding:        | 11 111x kkkk kkkk                                                                                                          |  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and<br>the result is placed in the W<br>register. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                          |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                          |  |  |  |  |  |  |

| Example          | ADDLW 0x15                                                                                                                 |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25                                                            |  |  |  |  |  |  |

| ANDLW            | AND Literal with W                                                                                                     |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                      |  |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |  |  |

| Words:           | 1                                                                                                                      |  |  |  |  |  |

| Cycles:          | 1                                                                                                                      |  |  |  |  |  |

| Example          | ANDLW 0x5F                                                                                                             |  |  |  |  |  |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                        |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                           |  |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                    |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                              |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (dest)                                                                                                                                                 |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |  |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                              |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                              |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                              |  |  |  |  |  |

| Example          | ADDWF FSR, <b>O</b>                                                                                                                                                            |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                    |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                          |  |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                          |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |  |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                           |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                           |  |  |  |  |  |  |

| Example          | ANDWF FSR, <b>1</b>                                                                                                                                         |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                                 |  |  |  |  |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                       |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$ ,<br>1 $\rightarrow GIE$                                                                                                                                                                        |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                    |  |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top of Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two-cycle<br>instruction. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                               |  |  |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                               |  |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                                                                  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                                                                  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                                                         |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                                                              |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                      |  |  |  |  |  |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                                                         |  |  |  |  |  |

| Description:     | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction.                                       |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                         |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                         |  |  |  |  |  |

| Example          | CALL TABLE;W contains table                                                                                                                                                                                               |  |  |  |  |  |

| TABLE            | ;offset value<br>;W now has table value<br>ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>RETLW k2 ;<br>RETLW kn ; End of table<br>Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8 |  |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                                                                                    |  |  |  |  |  |

| Syntax:          | [label] RETURN                                                                                                                                                                                                            |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                      |  |  |  |  |  |

| Operation:       | $TOS \to PC$                                                                                                                                                                                                              |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                      |  |  |  |  |  |

| Encoding:        | 00 0000 0000 1000                                                                                                                                                                                                         |  |  |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction.                                                                |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                         |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                         |  |  |  |  |  |

| Example          | RETURN                                                                                                                                                                                                                    |  |  |  |  |  |

|                  | After Interrupt<br>PC = TOS                                                                                                                                                                                               |  |  |  |  |  |

# 11.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 11.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 11.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command-line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities, and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping, and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high level source debugging with the MPLAB IDE.

# 11.6 MPLAB ASM30 Assembler, Linker, and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

# 11.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PICmicro series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break, or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

# 11.8 MPLAB SIM30 Software Simulator