Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 80 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

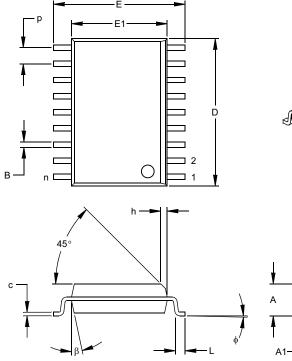

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621-04-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **PIC16C62X**

### **EPROM-Based 8-Bit CMOS Microcontrollers**

#### Devices included in this data sheet:

Referred to collectively as PIC16C62X.

- PIC16C620 PIC16C620A

- PIC16C621 PIC16C621A

- PIC16C622 PIC16C622A

- PIC16CR620A

#### **High Performance RISC CPU:**

- Only 35 instructions to learn

- All single cycle instructions (200 ns), except for program branches which are two-cycle

- Operating speed:

- DC 40 MHz clock input

- DC 100 ns instruction cycle

| Device      | Program<br>Memory | Data<br>Memory |

|-------------|-------------------|----------------|

| PIC16C620   | 512               | 80             |

| PIC16C620A  | 512               | 96             |

| PIC16CR620A | 512               | 96             |

| PIC16C621   | 1K                | 80             |

| PIC16C621A  | 1K                | 96             |

| PIC16C622   | 2K                | 128            |

| PIC16C622A  | 2K                | 128            |

· Interrupt capability

- 16 special function hardware registers

- 8-level deep hardware stack

- Direct, Indirect and Relative addressing modes

#### **Peripheral Features:**

- 13 I/O pins with individual direction control

- High current sink/source for direct LED drive

- Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VREF) module

- Programmable input multiplexing from device inputs and internal voltage reference

- Comparator outputs can be output signals

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

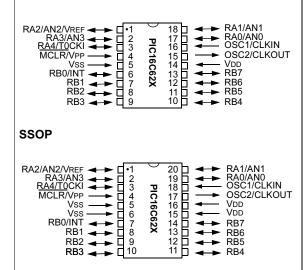

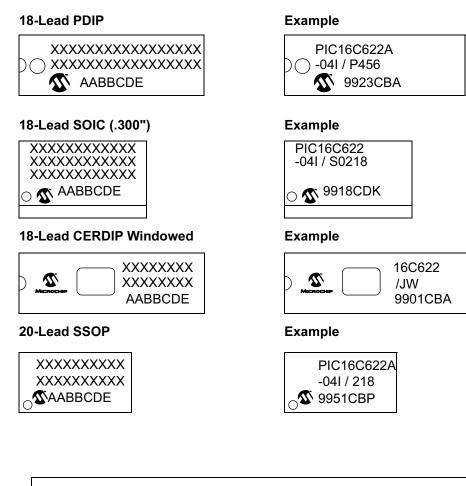

#### Pin Diagrams

#### PDIP, SOIC, Windowed CERDIP

#### **Special Microcontroller Features:**

- · Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- · Programmable code protection

- · Power saving SLEEP mode

- Selectable oscillator options

- Serial in-circuit programming (via two pins)

- Four user programmable ID locations

#### **CMOS Technology:**

- Low power, high speed CMOS EPROM technology

- Fully static design

- · Wide operating range

- 2.5V to 5.5V

- Commercial, industrial and extended temperature range

- Low power consumption

- < 2.0 mA @ 5.0V, 4.0 MHz

- 15 μA typical @ 3.0V, 32 kHz

- < 1.0 μA typical standby current @ 3.0V

|             |                                        | PIC16C620 <sup>(3)</sup>            | PIC16C620A <sup>(1)(4)</sup>        | PIC16CR620A <sup>(2)</sup>          | PIC16C621 <sup>(3)</sup>            | PIC16C621A <sup>(1)(4)</sup>        | PIC16C622 <sup>(3)</sup>            | PIC16C622A <sup>(1)(4)</sup>        |

|-------------|----------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz)   | 20                                  | 40                                  | 20                                  | 20                                  | 40                                  | 20                                  | 40                                  |

| Memory      | EPROM Program<br>Memory<br>(x14 words) | 512                                 | 512                                 | 512                                 | 1K                                  | 1K                                  | 2К                                  | 2К                                  |

|             | Data Memory (bytes)                    | 80                                  | 96                                  | 96                                  | 80                                  | 96                                  | 128                                 | 128                                 |

| Peripherals | Timer Module(s)                        | TMR0                                | TMR0                                | TMRO                                | TMR0                                | TMR0                                | TMR0                                | TMR0                                |

|             | Comparators(s)                         | 2                                   | 2                                   | 2                                   | 2                                   | 2                                   | 2                                   | 2                                   |

|             | Internal Reference<br>Voltage          | Yes                                 |

| Features    | Interrupt Sources                      | 4                                   | 4                                   | 4                                   | 4                                   | 4                                   | 4                                   | 4                                   |

|             | I/O Pins                               | 13                                  | 13                                  | 13                                  | 13                                  | 13                                  | 13                                  | 13                                  |

|             | Voltage Range (Volts)                  | 2.5-6.0                             | 2.7-5.5                             | 2.5-5.5                             | 2.5-6.0                             | 2.7-5.5                             | 2.5-6.0                             | 2.7-5.5                             |

|             | Brown-out Reset                        | Yes                                 |

|             | Packages                               | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

#### TABLE 1-1: PIC16C62X FAMILY OF DEVICES

All PICmicro<sup>®</sup> Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C62X Family devices use serial programming with clock pin RB6 and data pin RB7.

**Note 1:** If you change from this device to another device, please verify oscillator characteristics in your application.

2: For ROM parts, operation from 2.0V - 2.5V will require the PIC16LCR62XA parts.

**3:** For OTP parts, operation from 2.5V - 3.0V will require the PIC16LC62X part.

4: For OTP parts, operation from 2.7V - 3.0V will require the PIC16LC62XA part.

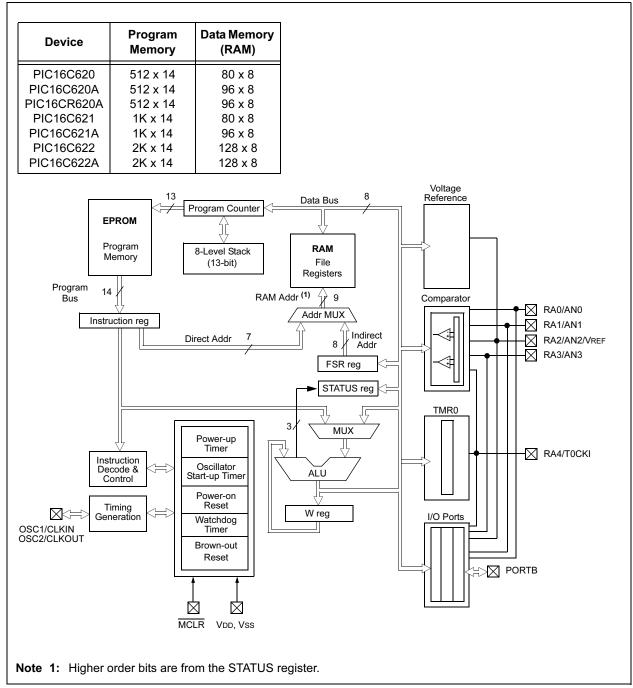

#### FIGURE 3-1: BLOCK DIAGRAM

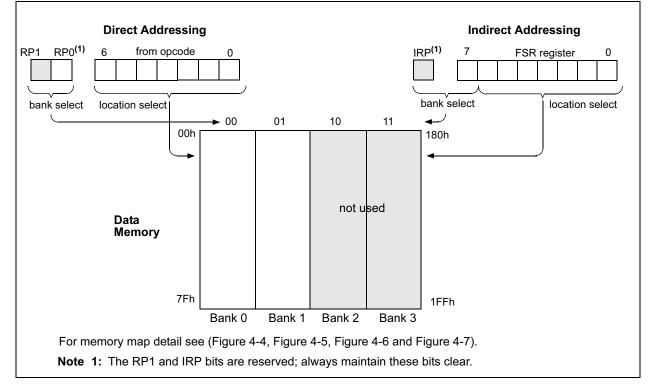

#### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-9. However, IRP is not used in the PIC16C62X.

A simple program to clear RAM location 20h-7Fh using indirect addressing is shown in Example 4-1.

| EXAN  | IPLE 4- | 1: INC | DIRECT ADDRESSING    |

|-------|---------|--------|----------------------|

|       | movlw   | 0x20   | ;initialize pointer  |

|       | movwf   | FSR    | ;to RAM              |

| NEXT  | clrf    | INDF   | ;clear INDF register |

|       | incf    | FSR    | ;inc pointer         |

|       | btfss   | FSR,7  | ;all done?           |

|       | goto    | NEXT   | ;no clear next       |

|       |         |        | ;yes continue        |

| CONTI | NUE:    |        |                      |

|       |         |        |                      |

#### FIGURE 4-9: DIRECT/INDIRECT ADDRESSING PIC16C62X

#### TABLE 5-1:PORTA FUNCTIONS

| Name         | Bit # | Buffer<br>Type | Function                                                                                          |

|--------------|-------|----------------|---------------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0  | ST             | Input/output or comparator input                                                                  |

| RA1/AN1      | bit1  | ST             | Input/output or comparator input                                                                  |

| RA2/AN2/VREF | bit2  | ST             | Input/output or comparator input or VREF output                                                   |

| RA3/AN3      | bit3  | ST             | Input/output or comparator input/output                                                           |

| RA4/T0CKI    | bit4  | ST             | Input/output or external clock input for TMR0 or comparator output.<br>Output is open drain type. |

Legend: ST = Schmitt Trigger input

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|------------|------------|------------|------------|------------|-----------------|---------------------------------|

| 05h     | PORTA |       |       |       | RA4        | RA3        | RA2        | RA1        | RA0        | x 0000          | u 0000                          |

| 85h     | TRISA |       |       | _     | TRISA<br>4 | TRISA<br>3 | TRISA<br>2 | TRISA<br>1 | TRISA<br>0 | 1 1111          | 1 1111                          |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | _          | CIS        | CM2        | CM1        | CM0        | 00 0000         | 00 0000                         |

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _          | VR3        | VR2        | VR1        | VR0        | 000- 0000       | 000- 0000                       |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

Note: Shaded bits are not used by PORTA.

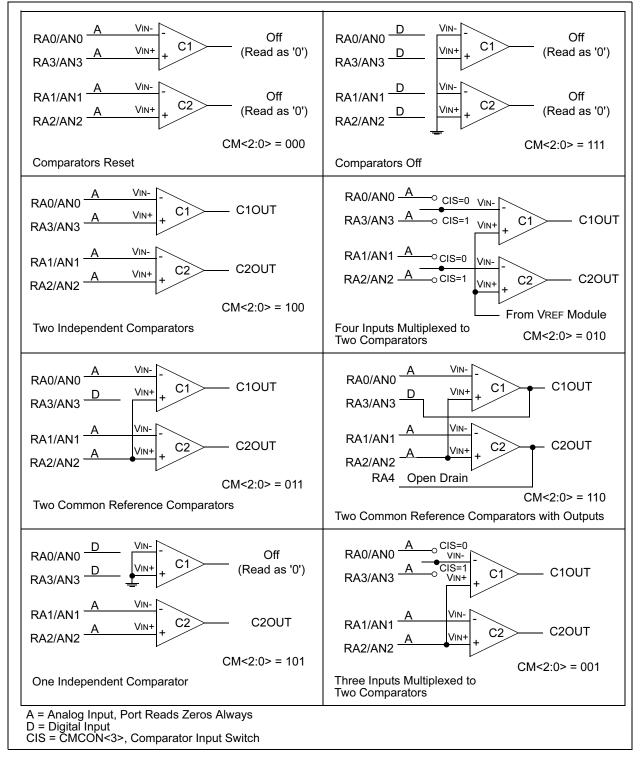

#### 7.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 7-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 12-2.

**Note:** Comparator interrupts should be disabled during a Comparator mode change otherwise a false interrupt may occur.

## PIC16C62X

#### **FIGURE 9-11: EXTERNAL POWER-ON RESET CIRCUIT (FOR** SLOW VDD POWER-UP) Vdd Vdd D R R1 MCLR PIC16C62X С Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down. **2:** < 40 k $\Omega$ is recommended to make sure that voltage drop across R does not violate the device's electrical specification. **3:** R1 = $100\Omega$ to 1 k $\Omega$ will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin

breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

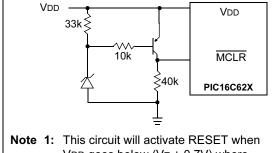

#### FIGURE 9-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate RESET when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- **2:** Internal Brown-out Reset circuitry should be disabled when using this circuit.

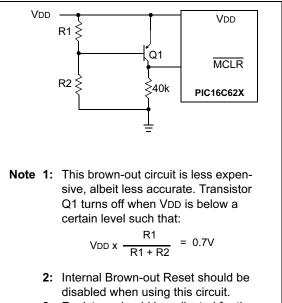

#### FIGURE 9-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

**3:** Resistors should be adjusted for the characteristics of the transistor.

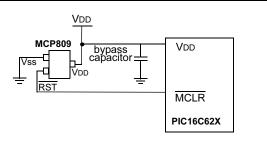

#### FIGURE 9-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active RESET pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

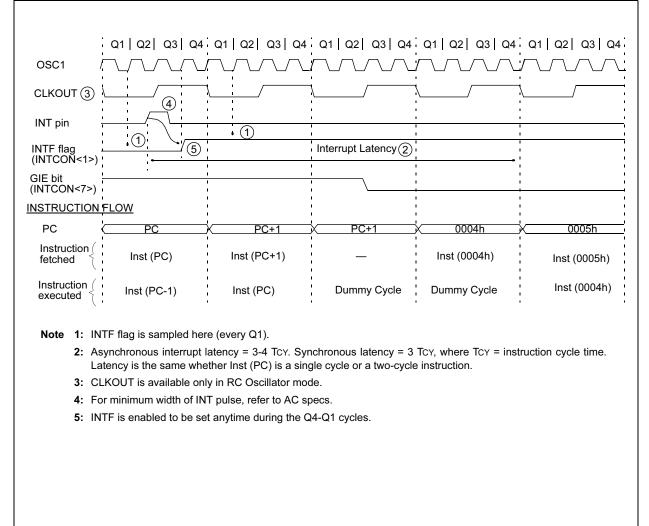

#### 9.5.1 RB0/INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered, either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP and Figure 9-18 for timing of wakeup from SLEEP through RB0/INT interrupt.

#### 9.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 6.0.

#### 9.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

| Note: | If a change on the I/O pin should occur   |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|

|       | when the read operation is being executed |  |  |  |  |  |  |

|       | (start of the Q2 cycle), then the RBIF    |  |  |  |  |  |  |

|       | interrupt flag may not get set.           |  |  |  |  |  |  |

#### 9.5.4 COMPARATOR INTERRUPT

See Section 7.6 for complete description of comparator interrupts.

#### FIGURE 9-16: INT PIN INTERRUPT TIMING

#### 9.9 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip                    | does | not | recommend | code |  |  |  |  |

|-------|------------------------------|------|-----|-----------|------|--|--|--|--|

|       | protecting windowed devices. |      |     |           |      |  |  |  |  |

#### 9.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify. Only the Least Significant 4 bits of the ID locations are used.

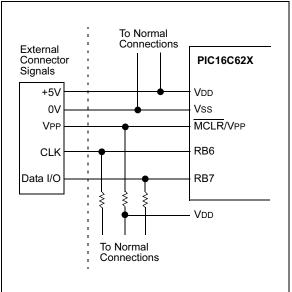

#### 9.11 In-Circuit Serial Programming™

The PIC16C62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X/9XX Programming Specification (DS30228).

A typical In-Circuit Serial Programming connection is shown in Figure 9-19.

## FIGURE 9-19:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| BTFSS            | Bit Test f, Skip if Set                                                                                                                          | CALL             | Call Subroutine                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                              | Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                    |

| Operands:        | $0 \le f \le 127$                                                                                                                                | Operands:        | $0 \leq k \leq 2047$                                                                                                                                                       |

|                  | $0 \le b < 7$                                                                                                                                    | Operation:       | $(PC)$ + 1 $\rightarrow$ TOS,                                                                                                                                              |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                          |                  | $k \rightarrow PC<10:0>$ ,<br>(PCLATH<4:3>) $\rightarrow PC<12:11>$                                                                                                        |

| Status Affected: | None                                                                                                                                             | Status Affected: | None                                                                                                                                                                       |

| Encoding:        | 01 11bb bfff ffff                                                                                                                                | Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next instruc-                         | Description:     | Call Subroutine. First, return<br>address (PC+1) is pushed onto                                                                                                            |

|                  | tion fetched during the current<br>instruction execution, is discarded<br>and a NOP is executed instead,<br>making this a two-cycle instruction. |                  | the stack. The eleven bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. |

| Words:           | 1                                                                                                                                                | Words:           | 1                                                                                                                                                                          |

| Cycles:          | 1(2)                                                                                                                                             | Cycles:          | 2                                                                                                                                                                          |

| Example          | here btfss <b>FLAG,1</b><br>false goto <b>PROCESS_CO</b>                                                                                         | Example          | HERE CALL                                                                                                                                                                  |

|                  | TRUE DE                                                                                                                                          | Example          | THER                                                                                                                                                                       |

|                  | Before Instruction<br>PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,<br>PC = address FALSE<br>if FLAG<1> = 1,                         |                  | Before Instruction<br>PC = Address HERE<br>After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                 |

|                  | PC = address TRUE                                                                                                                                | CLRF             | Clear f                                                                                                                                                                    |

|                  |                                                                                                                                                  | Syntax:          | [ <i>label</i> ] CLRF f                                                                                                                                                    |

|                  |                                                                                                                                                  | Operands:        | $0 \leq f \leq 127$                                                                                                                                                        |

|                  |                                                                                                                                                  | Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$                                                                                                      |

|                  |                                                                                                                                                  | Status Affected: | Z                                                                                                                                                                          |

|                  |                                                                                                                                                  | Encoding:        | 00 0001 1fff ffff                                                                                                                                                          |

|                  |                                                                                                                                                  | Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.                                                                                                          |

|                  |                                                                                                                                                  | Words:           | 1                                                                                                                                                                          |

|                  |                                                                                                                                                  | Cycles:          | 1                                                                                                                                                                          |

|                  |                                                                                                                                                  | Example          | CLRF FLAG_REG                                                                                                                                                              |

|                  |                                                                                                                                                  |                  | Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction                                                                                                                 |

|                  |                                                                                                                                                  |                  | $FLAG_REG = 0x00$<br>Z = 1                                                                                                                                                 |

| RLF              | Rotate                          | Left f thr                                       | oua                    | h Car                                | rv                             |

|------------------|---------------------------------|--------------------------------------------------|------------------------|--------------------------------------|--------------------------------|

| Syntax:          | [ label ]                       | RLF                                              | f,d                    |                                      |                                |

| Operands:        | 0 ≤ f ≤ 1<br>d ∈ [0,1           |                                                  |                        |                                      |                                |

| Operation:       | See des                         | scription I                                      | pelov                  | N                                    |                                |

| Status Affected: | С                               |                                                  |                        |                                      |                                |

| Encoding:        | 00                              | 1101                                             | df                     | ff                                   | ffff                           |

| escription:      | rotated<br>the Carr<br>is place |                                                  | the<br>'d' is<br>V reg | left th<br>0, the<br>jister.<br>back | rough<br>e result<br>If 'd' is |

| Vords:           | 1                               |                                                  |                        |                                      |                                |

| Cycles:          | 1                               |                                                  |                        |                                      |                                |

| xample           | RLF                             | REG1,                                            | 0                      |                                      |                                |

|                  | Before I<br>After Ins           | nstructio<br>REG1<br>C<br>struction<br>REG1<br>W | n<br>=<br>=<br>=       | 1110<br>0<br>1110<br>1100            |                                |

|                  |                                 | С                                                | =                      | 1                                    |                                |

| RRF              | Rotate R                                                                                                                                                                                                          | ight f th      | nroug       | gh Ca             | arry     |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-------------------|----------|--|

| Syntax:          | [ label ]                                                                                                                                                                                                         | RRF f          | ,d          |                   |          |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                 |                |             |                   |          |  |

| Operation:       | See desc                                                                                                                                                                                                          | ription b      | elow        | '                 |          |  |

| Status Affected: | С                                                                                                                                                                                                                 |                |             |                   |          |  |

| Encoding:        | 00                                                                                                                                                                                                                | 1100           | df          | ff                | ffff     |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |                |             |                   |          |  |

|                  |                                                                                                                                                                                                                   | ; _▶           | Regis       | ter f             | <b>}</b> |  |

| Words:           | 1                                                                                                                                                                                                                 |                |             |                   |          |  |

| Cycles:          | 1                                                                                                                                                                                                                 |                |             |                   |          |  |

| Example          | RRF                                                                                                                                                                                                               |                | REG<br>0    | 61,               |          |  |

|                  | Before In                                                                                                                                                                                                         | structior      | ı           |                   |          |  |

|                  |                                                                                                                                                                                                                   | REG1<br>C      | =<br>=      | 1110<br>0         | 0110     |  |

|                  | After Inst                                                                                                                                                                                                        |                |             |                   |          |  |

|                  | 1                                                                                                                                                                                                                 | REG1<br>W<br>C | =<br>=<br>= | 1110<br>0111<br>0 |          |  |

SLEEP

| <b>VIII</b>      |                                                                                                                                                                                                                                                       |       |      |      |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|--|--|--|

| Syntax:          | [ label<br>]                                                                                                                                                                                                                                          | SLEEF | D    |      |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                                  |       |      |      |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow \underline{W}DT \text{ prescaler,} \\ 1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                               |       |      |      |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                |       |      |      |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                                                                    | 0000  | 0110 | 0011 |  |  |  |

| Description:     | The power-down STATUS bit,<br>PD is cleared. Time-out<br>STATUS bit, TO is set. Watch-<br>dog Timer and its prescaler are<br>cleared.<br>The processor is put into SLEEP<br>mode with the oscillator<br>stopped. See Section 9.8 for<br>more details. |       |      |      |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                     |       |      |      |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                     |       |      |      |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                 |       |      |      |  |  |  |

#### 11.9 MPLAB ICE 2000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 2000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers. Software control of the MPLAB ICE 2000 in-circuit emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PICmicro microcontrollers.

The MPLAB ICE 2000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

#### 11.10 MPLAB ICE 4000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 4000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for highend PICmicro microcontrollers. Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICD 4000 is a premium emulator system, providing the features of MPLAB ICE 2000, but with increased emulation memory and high speed performance for dsPIC30F and PIC18XXXX devices. Its advanced emulator features include complex triggering and timing, up to 2 Mb of emulation memory, and the ability to view variables in real-time.

The MPLAB ICE 4000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

### 11.11 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low cost, run-time development tool, connecting to the host PC via an RS-232 or high speed USB interface. This tool is based on the FLASH PICmicro MCUs and can be used to develop for these and other PICmicro microcontrollers. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers cost effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single-stepping and watching variables, CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real-time. MPLAB ICD 2 also serves as a development programmer for selected PICmicro devices.

#### 11.12 PRO MATE II Universal Device Programmer

The PRO MATE II is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features an LCD display for instructions and error messages and a modular detachable socket assembly to support various package types. In Stand-Alone mode, the PRO MATE II device programmer can read, verify, and program PICmicro devices without a PC connection. It can also set code protection in this mode.

#### 11.13 PICSTART Plus Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus development programmer supports most PICmicro devices up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

#### 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended) (CONT.)

|                                         |                                                  |                                                                                                                                                                                               |                                                       | Standard Operating Conditions (unless otherwise stated) |                               |                            |                                                                                    |  |  |  |

|-----------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------|-------------------------------|----------------------------|------------------------------------------------------------------------------------|--|--|--|

| PIC16C                                  | 62X                                              |                                                                                                                                                                                               | $\begin{array}{rllllllllllllllllllllllllllllllllllll$ |                                                         |                               |                            |                                                                                    |  |  |  |

| PIC16LC62X                              |                                                  |                                                                                                                                                                                               | Opera<br>Opera                                        | $\begin{array}{llllllllllllllllllllllllllllllllllll$    |                               |                            |                                                                                    |  |  |  |

| Param<br>. No.                          | Sym                                              | Characteristic                                                                                                                                                                                | Min                                                   | Тур†                                                    | Мах                           | Units                      | Conditions                                                                         |  |  |  |

| D022<br>D022A<br>D023<br>D023A<br>D0222 | ΔIWDT<br>ΔIBOR<br>ΔICOM<br>P<br>ΔIVREF<br>ΔIVREF | WDT Current <sup>(5)</sup><br>Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each<br>Comparator <sup>(5)</sup><br>VREF Current <sup>(5)</sup><br>WDT Current <sup>(5)</sup> |                                                       | 6.0<br>350<br>—<br>6.0                                  | 20<br>25<br>425<br>100<br>300 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | VDD=4.0V $(125°C)$ BOD enabled, VDD = 5.0V<br>VDD = 4.0V<br>VDD = 4.0V<br>VDD=3.0V |  |  |  |

| D022A<br>D023<br>D023A                  | ΔIBOR<br>ΔICOM<br>P<br>ΔIVREF                    | Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each<br>Comparator <sup>(5)</sup><br>VREF Current <sup>(5)</sup>                                                             |                                                       | 350<br>—                                                | 425<br>100<br>300             | μΑ<br>μΑ<br>μΑ             | BOD enabled, VDD = 5.0V<br>VDD = 3.0V<br>VDD = 3.0V                                |  |  |  |

| 1A                                      | Fosc                                             | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency                                              | 0<br>0<br>0<br>0                                      |                                                         | 200<br>4<br>4<br>20           | kHz<br>MHz<br>MHz<br>MHz   | All temperatures<br>All temperatures<br>All temperatures<br>All temperatures       |  |  |  |

| 1A                                      | Fosc                                             | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency                                              | 0<br>0<br>0<br>0                                      |                                                         | 200<br>4<br>4<br>20           | kHz<br>MHz<br>MHz<br>MHz   | All temperatures<br>All temperatures<br>All temperatures<br>All temperatures       |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

## PIC16C62X

#### 12.2 DC Characteristics: PIC16C62XA-04 (Commercial, Industrial, Extended) PIC16C62XA-20 (Commercial, Industrial, Extended) PIC16LC62XA-04 (Commercial, Industrial, Extended (CONT.)

| PIC16C62XA            |                                 |                                                                                                                                                  |                  | $\begin{array}{l lllllllllllllllllllllllllllllllllll$ |                       |                          |                                                                              |  |  |

|-----------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------|-----------------------|--------------------------|------------------------------------------------------------------------------|--|--|

| PIC16LC62XA           |                                 |                                                                                                                                                  |                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$  |                       |                          |                                                                              |  |  |

| Param.<br>No.         | Sym                             | Characteristic                                                                                                                                   | Min              | Тур†                                                  | Max                   | Units                    | Conditions                                                                   |  |  |

| D022                  | ΔIWDT                           | WDT Current <sup>(5)</sup>                                                                                                                       | —                | 6.0                                                   | 10<br>12              | μA<br>μA                 | VDD = 4.0V<br>(125°C)                                                        |  |  |

| D022A<br>D023         | $\Delta$ IBOR<br>$\Delta$ ICOMP | Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each<br>Comparator <sup>(5)</sup>                                               | _                | 75<br>30                                              | 125<br>60             | μA<br>μA                 | BOD enabled, VDD = 5.0V<br>VDD = 4.0V                                        |  |  |

| D023A                 | $\Delta I V REF$                | VREF Current <sup>(5)</sup>                                                                                                                      | —                | 80                                                    | 135                   | μA                       | VDD = 4.0V                                                                   |  |  |

| D022<br>D022A<br>D023 | ΔIWDT<br>ΔIBOR<br>ΔICOMP        | WDT Current <sup>(5)</sup><br>Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each<br>Comparator <sup>(5)</sup>                 |                  | 6.0<br>75<br>30                                       | 10<br>12<br>125<br>60 | μΑ<br>μΑ<br>μΑ           | VDD=4.0V<br>(125°C)<br>BOD enabled, VDD = 5.0V<br>VDD = 4.0V                 |  |  |

| D023A                 | $\Delta$ IVREF                  | VREF Current <sup>(5)</sup>                                                                                                                      | _                | 80                                                    | 135                   | μA                       | VDD = 4.0V                                                                   |  |  |

| 1A                    | Fosc                            | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0<br>0<br>0<br>0 |                                                       | 200<br>4<br>4<br>20   | kHz<br>MHz<br>MHz<br>MHz | All temperatures<br>All temperatures<br>All temperatures<br>All temperatures |  |  |

| 1A                    | Fosc                            | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0<br>0<br>0<br>0 |                                                       | 200<br>4<br>4<br>20   | kHz<br>MHz<br>MHz<br>MHz | All temperatures<br>All temperatures<br>All temperatures<br>All temperatures |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

$\overline{\text{MCLR}}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

#### 12.3 DC CHARACTERISTICS: PIC16CR62XA-04 (Commercial, Industrial, Extended) PIC16CR62XA-20 (Commercial, Industrial, Extended) PIC16LCR62XA-04 (Commercial, Industrial, Extended)

| PIC16CR62XA-04<br>PIC16CR62XA-20 |      |                                               |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                |            |          |                                                                                                                   |  |  |  |

|----------------------------------|------|-----------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIC16LCR62XA-04                  |      |                                               |       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq$ TA $\leq$ +85°C for industrial and $0^{\circ}$ C $\leq$ TA $\leq$ +70°C for commercial and $-40^{\circ}$ C $\leq$ TA $\leq$ +125°C for extended |            |          |                                                                                                                   |  |  |  |

| Param.<br>No.                    | Sym  | Characteristic                                | Min   | Тур†                                                                                                                                                                                                                                                | Мах        | Units    | Conditions                                                                                                        |  |  |  |

| D001                             | Vdd  | Supply Voltage                                | 3.0   | —                                                                                                                                                                                                                                                   | 5.5        | V        | See Figures 12-7, 12-8, 12-9                                                                                      |  |  |  |

| D001                             | Vdd  | Supply Voltage                                | 2.5   | _                                                                                                                                                                                                                                                   | 5.5        | V        | See Figures 12-7, 12-8, 12-9                                                                                      |  |  |  |

| D002                             | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>  |       | 1.5*                                                                                                                                                                                                                                                | _          | V        | Device in SLEEP mode                                                                                              |  |  |  |

| D002                             | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>  | _     | 1.5*                                                                                                                                                                                                                                                |            | V        | Device in SLEEP mode                                                                                              |  |  |  |

| D003                             | VPOR | VDD start voltage to<br>ensure Power-on Reset |       | Vss                                                                                                                                                                                                                                                 |            | V        | See section on Power-on Reset for details                                                                         |  |  |  |

| D003                             | VPOR | VDD start voltage to<br>ensure Power-on Reset | —     | Vss                                                                                                                                                                                                                                                 | _          | V        | See section on Power-on Reset for details                                                                         |  |  |  |

| D004                             | SVDD | VDD rise rate to ensure<br>Power-on Reset     | 0.05* | —                                                                                                                                                                                                                                                   |            | V/ms     | See section on Power-on Reset for details                                                                         |  |  |  |

| D004                             | SVDD | VDD rise rate to ensure<br>Power-on Reset     | 0.05* | —                                                                                                                                                                                                                                                   | _          | V/ms     | See section on Power-on Reset for details                                                                         |  |  |  |

| D005                             | VBOR | Brown-out Detect Voltage                      | 3.7   | 4.0                                                                                                                                                                                                                                                 | 4.35       | V        | BOREN configuration bit is cleared                                                                                |  |  |  |

| D005                             | VBOR | Brown-out Detect Voltage                      | 3.7   | 4.0                                                                                                                                                                                                                                                 | 4.35       | V        | BOREN configuration bit is cleared                                                                                |  |  |  |

| D010                             | Idd  | Supply Current <sup>(2)</sup>                 | _     | 1.2<br>500                                                                                                                                                                                                                                          | 1.7<br>900 | mA<br>μA | Fosc = 4 MHz, VDD = 5.5V, WDT disabled, XT mode,<br>(Note 4)*<br>Fosc = 4 MHz, VDD = 3.0V, WDT disabled, XT mode, |  |  |  |

|                                  |      |                                               | _     | 1.0                                                                                                                                                                                                                                                 | 2.0        | mA       | (Note 4)<br>Fosc = 10 MHz, VDD = 3.0V, WDT disabled, HS mode,<br>(Note 6)                                         |  |  |  |

|                                  |      |                                               | —     | 4.0                                                                                                                                                                                                                                                 | 7.0        | mA       | Fosc = 20 MHz, VDD = 5.5V, WDT disabled*, HS                                                                      |  |  |  |

|                                  |      |                                               | —     | 3.0                                                                                                                                                                                                                                                 | 6.0        | mA       | mode                                                                                                              |  |  |  |

|                                  |      |                                               |       | 35                                                                                                                                                                                                                                                  | 70         | μA       | Fosc = 20 MHz, VDD = 4.5V, WDT disabled, HS mode<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled, LP mode              |  |  |  |

| D010                             | IDD  | Supply Current <sup>(2)</sup>                 | —     | 1.2                                                                                                                                                                                                                                                 | 1.7        | mA       | Fosc = 4.0 MHz, VDD = 5.5V, WDT disabled, XT<br>mode, ( <b>Note 4</b> )*                                          |  |  |  |

|                                  |      |                                               | —     | 400                                                                                                                                                                                                                                                 | 800        | μA       | Fosc = 4.0 MHz, VDD = 2.5V, WDT disabled, XT mode (Note 4)                                                        |  |  |  |

|                                  |      |                                               | —     | 35                                                                                                                                                                                                                                                  | 70         | μA       | Fosc = 32 kHz, VDD = 2.5V, WDT disabled, LP mode                                                                  |  |  |  |

#### 12.4 DC Characteristics: PIC16C62X/C62XA/CR62XA (Commercial, Industrial, Extended) PIC16LC62X/LC62XA/LCR62XA (Commercial, Industrial, Extended) (CONT.)

| PIC16C62X/C62XA/CR62XA    |           |                                            |         | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq$ TA $\leq$ +85°C for industrial and0°C $\leq$ TA $\leq$ +70°C for commercial and $-40^{\circ}$ C $\leq$ TA $\leq$ +125°C for extended |             |        |                                                                                                |  |  |

|---------------------------|-----------|--------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|------------------------------------------------------------------------------------------------|--|--|

| PIC16LC62X/LC62XA/LCR62XA |           |                                            |         | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                     |             |        |                                                                                                |  |  |

| Param.<br>No.             | Sym       | Characteristic                             | Min     | Тур†                                                                                                                                                                                                                                     | Мах         | Units  | Conditions                                                                                     |  |  |

|                           | Vol       | Output Low Voltage                         |         |                                                                                                                                                                                                                                          |             |        |                                                                                                |  |  |

| D080                      |           | I/O ports                                  | _       | —                                                                                                                                                                                                                                        | 0.6         | V      | IOL = 8.5 mA, VDD = 4.5V, -40° to +85°C                                                        |  |  |

|                           |           |                                            | _       | —                                                                                                                                                                                                                                        | 0.6         | V      | IOL = 7.0 mA, VDD = 4.5V, +125°C                                                               |  |  |

| D083                      |           | OSC2/CLKOUT (RC only)                      | _       | _                                                                                                                                                                                                                                        | 0.6         | V      | IOL = 1.6 mA, VDD = 4.5V, -40° to +85°C                                                        |  |  |

|                           |           |                                            | _       | _                                                                                                                                                                                                                                        | 0.6         | V      | IOL = 1.2 mA, VDD = 4.5V, +125°C                                                               |  |  |

|                           | Voн       | Output High Voltage <sup>(3)</sup>         | 1       |                                                                                                                                                                                                                                          |             |        |                                                                                                |  |  |

| D090                      |           | I/O ports (Except RA4)                     | Vdd-0.7 | _                                                                                                                                                                                                                                        | _           | v      | ІОН = -3.0 mA, VDD = 4.5V, -40° to +85°С                                                       |  |  |

|                           |           |                                            | VDD-0.7 | _                                                                                                                                                                                                                                        | _           | V      | IOH = -2.5 mA, VDD = 4.5V, +125°C                                                              |  |  |

| D092                      |           | OSC2/CLKOUT (RC only)                      | VDD-0.7 | —                                                                                                                                                                                                                                        | -           | V      | IOH = -1.3 mA, VDD = 4.5V, -40° to +85°С                                                       |  |  |

|                           |           |                                            | VDD-0.7 | _                                                                                                                                                                                                                                        | _           | V      | Iон = -1.0 mA, VDD = 4.5V, +125°С                                                              |  |  |

|                           | Vон       | Output High Voltage <sup>(3)</sup>         |         |                                                                                                                                                                                                                                          |             |        |                                                                                                |  |  |

| D090                      |           | I/O ports (Except RA4)                     | VDD-0.7 | —                                                                                                                                                                                                                                        | -           | V      | IOH = -3.0 mA, VDD = 4.5V, -40° to +85°C                                                       |  |  |

|                           |           |                                            | VDD-0.7 | —                                                                                                                                                                                                                                        | -           | V      | ЮН = -2.5 mA, VDD = 4.5V, +125°С                                                               |  |  |

| D092                      |           | OSC2/CLKOUT (RC only)                      | VDD-0.7 | -                                                                                                                                                                                                                                        | -           | V      | IOH = -1.3 mA, VDD = 4.5V, -40° to +85°C                                                       |  |  |

| *D450                     | 1/22      | On an Duain Llink Mattern                  | VDD-0.7 | _                                                                                                                                                                                                                                        |             | V<br>V | IOH = -1.0 mA, VDD = 4.5V, +125°C                                                              |  |  |

| *D150                     | Vod       | Open-Drain High Voltage                    |         |                                                                                                                                                                                                                                          | 10*<br>8.5* | V      | RA4 pin PIC16C62X, PIC16LC62X<br>RA4 pin PIC16C62XA, PIC16LC62XA,<br>PIC16CR62XA, PIC16LCR62XA |  |  |

| *D150                     | Vod       | Open-Drain High Voltage                    |         |                                                                                                                                                                                                                                          | 10*<br>8.5* | V      | RA4 pin PIC16C62X, PIC16LC62X<br>RA4 pin PIC16C62XA, PIC16LC62XA,<br>PIC16CR62XA, PIC16LCR62XA |  |  |

|                           |           | Capacitive Loading Specs on<br>Output Pins |         |                                                                                                                                                                                                                                          |             |        |                                                                                                |  |  |