#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 80 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621-04e-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART, PRO MATE and PowerSmart are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Accuron, Application Maestro, dsPIC, dsPICDEM, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICkit, PICDEM, PICDEM.net, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPIC, Select Mode, SmartSensor, SmartShunt, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

NOTES:

## 4.0 MEMORY ORGANIZATION

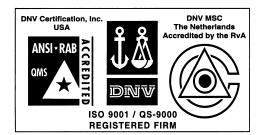

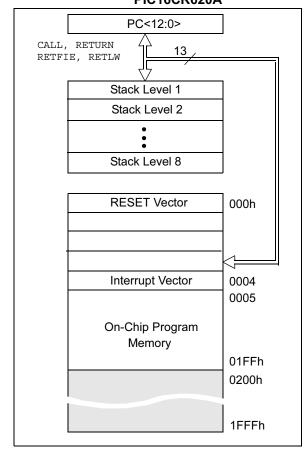

## 4.1 Program Memory Organization

The PIC16C62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C620(A) and PIC16CR620, 1K x 14 (0000h - 03FFh) for the PIC16C621(A) and 2K x 14 (0000h - 07FFh) for the PIC16C622(A) are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16C(R)620(A)) or 1K x 14 space (PIC16C621(A)) or 2K x 14 space (PIC16C622(A)). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16C620/PIC16C620A/

PIC16C620/PIC16C620 PIC16CR620A

## FIGURE 4-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C621/PIC16C621A

FIGURE 4-3:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C622/PIC16C622A

### FIGURE 4-4: DATA MEMORY MAP FOR THE PIC16C620/621

| File     |                     |                     | File        |

|----------|---------------------|---------------------|-------------|

| Address  | 3                   |                     | Address     |

| 00h      | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h         |

| 01h      | TMR0                | OPTION              | 81h         |

| 02h      | PCL                 | PCL                 | 82h         |

| 03h      | STATUS              | STATUS              | 83h         |

| 04h      | FSR                 | FSR                 | 84h         |

| 05h      | PORTA               | TRISA               | 85h         |

| 06h      | PORTB               | TRISB               | 86h         |

| 07h      |                     |                     | 87h         |

| 08h      |                     |                     | 88h         |

| 09h      |                     |                     | 89h         |

| 0Ah      | PCLATH              | PCLATH              | 8Ah         |

| 0Bh      | INTCON              | INTCON              | 8Bh         |

| 0Ch      | PIR1                | PIE1                | 8Ch         |

| 0Dh      |                     |                     | 8Dh         |

| 0Eh      |                     | PCON                | 8Eh         |

| 0Fh      |                     |                     | 8Fh         |

| 10h      |                     |                     | 90h         |

| 11h      |                     |                     | 91h         |

| 12h      |                     |                     | 92h         |

| 13h      |                     |                     | 93h         |

| 14h      |                     |                     | 94h         |

| 15h      |                     |                     | 95h         |

| 16h      |                     |                     | 96h         |

| 17h      |                     |                     | 97h         |

| 18h      |                     |                     | 98h         |

| 19h      |                     |                     | 99h         |

| 1Ah      |                     |                     | 9Ah         |

| 1Bh      |                     |                     | 9Bh         |

| 1Ch      |                     |                     | 9Ch         |

| 1Dh      |                     |                     | 9Dh         |

| 1Eh      |                     |                     | 9Eh         |

| 1Fh      | CMCON               | VRCON               | 9Fh         |

| 20h      |                     | _                   | A0h         |

|          | General             |                     |             |

|          | Purpose<br>Register |                     |             |

| 6Fh      | 5                   |                     |             |

| 70h      |                     |                     |             |

|          |                     |                     |             |

|          |                     |                     |             |

|          |                     |                     |             |

| 7Fh      |                     |                     | FFh         |

|          | Bank 0              | Bank 1              |             |

| <b>—</b> |                     | 1 4                 |             |

| Unimp    | plemented data me   | mory locations, r   | ead as '0'. |

| Note 1:  | Not a physical re   | egister.            |             |

|          |                     |                     |             |

|          |                     |                     |             |

## FIGURE 4-5:

### DATA MEMORY MAP FOR THE PIC16C622

|                 | 1116                |                     |                 |

|-----------------|---------------------|---------------------|-----------------|

| File<br>Address | 8                   |                     | File<br>Address |

| 00h             | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |

| 01h             | TMR0                | OPTION              | 81h             |

| 02h             | PCL                 | PCL                 | 82h             |

| 03h             | STATUS              | STATUS              | 83h             |

| 04h             | FSR                 | FSR                 | 84h             |

| 05h             | PORTA               | TRISA               | 85h             |

| 06h             | PORTB               | TRISB               | 86h             |

| 00h             | TOILID              | TRIOD               | 87h             |

| 07h<br>08h      |                     |                     | 88h             |

| 00h             |                     |                     | 89h             |

| 03h<br>0Ah      | PCLATH              | PCLATH              | 8Ah             |

| 0An<br>0Bh      | INTCON              | INTCON              | 8Bh             |

| 0Dh             | PIR1                | PIE1                | 8Ch             |

| 0Ch<br>0Dh      | PIRI                | PIEI                | 8Dh             |

|                 |                     | PCON                |                 |

| 0Eh<br>0Fh      |                     | PCON                | 8Eh             |

|                 |                     |                     | 8Fh             |

| 10h             |                     |                     | 90h             |

| 11h             |                     |                     | 91h             |

| 12h             |                     |                     | 92h             |

| 13h             |                     |                     | 93h             |

| 14h             |                     |                     | 94h             |

| 15h             |                     |                     | 95h             |

| 16h             |                     |                     | 96h             |

| 17h             |                     |                     | 97h             |

| 18h             |                     |                     | 98h             |

| 19h             |                     |                     | 99h             |

| 1Ah             |                     |                     | 9Ah             |

| 1Bh             |                     |                     | 9Bh             |

| 1Ch             |                     |                     | 9Ch             |

| 1Dh             |                     |                     | 9Dh             |

| 1Eh             |                     |                     | 9Eh             |

| 1Fh             | CMCON               | VRCON               | 9Fh             |

| 20h             |                     |                     | A0h             |

|                 | General<br>Purpose  | General<br>Purpose  |                 |

|                 | Register            | Register            |                 |

|                 | 0                   | 5                   | BFh             |

|                 |                     |                     | C0h             |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

| 7Fh             |                     |                     | FFh             |

| , , , , , ,     | Bank 0              | Bank 1              |                 |

|                 |                     |                     |                 |

| Unim            | plemented data me   | mory locations, re  | ad as '0'.      |

| Note 1:         | Not a physical re   | aister              |                 |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

#### **OPTION Register** 4.2.2.2

The OPTION register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | TMR0, assign the prescaler to the WDT     |  |  |  |  |  |  |  |

|       | (PSA = 1).                                |  |  |  |  |  |  |  |

|         | R/W-1                    | R/W-1                          | R/W-1                         | R/W-1                        | R/W-1         | R/W-1 | R/W-1 | R/W-1 |

|---------|--------------------------|--------------------------------|-------------------------------|------------------------------|---------------|-------|-------|-------|

|         | RBPU                     | INTEDG                         | TOCS                          | TOSE                         | PSA           | PS2   | PS1   | PS0   |

|         | bit 7                    |                                |                               |                              |               | •     |       | bit 0 |

| bit 7   | RBPU: PO                 | RTB Pull-u                     | p Enable bi                   | it                           |               |       |       |       |

|         |                          | 3 pull-ups ai<br>3 pull-ups ai |                               | y individual                 | port latch va | alues |       |       |

| bit 6   | INTEDG: I                | nterrupt Edg                   | e Select bit                  | -                            |               |       |       |       |

|         |                          |                                | edge of RB0<br>edge of RB0    |                              |               |       |       |       |

| bit 5   | TOCS: TMI                | R0 Clock Sc                    | ource Select                  | bit                          |               |       |       |       |

|         |                          | ion on RA4/<br>Il instruction  | T0CKI pin<br>cycle clock      | (CLKOUT)                     |               |       |       |       |

| bit 4   | TOSE: TM                 | R0 Source E                    | Edge Select                   | bit                          |               |       |       |       |

|         |                          |                                |                               | ition on RA4<br>ition on RA4 |               |       |       |       |

| bit 3   | PSA: Pres                | caler Assigr                   | ment bit                      |                              | -             |       |       |       |

|         |                          |                                | ned to the W<br>ned to the Ti | DT<br>mer0 module            | Э             |       |       |       |

| bit 2-0 | <b>PS&lt;2:0&gt;</b> : F | Prescaler Ra                   | ate Select bi                 | ts                           |               |       |       |       |

|         | E                        | Bit Value T                    | MR0 Rate                      | WDT Rate                     |               |       |       |       |

|         | -                        | 000<br>001                     | 1:2<br>1:4                    | 1:1<br>1:2                   |               |       |       |       |

|         |                          | 010<br>011                     | 1 : 8<br>1 : 16               | 1:4<br>1:8                   |               |       |       |       |

|         |                          | 100                            | 1:32                          | 1:16                         |               |       |       |       |

|         |                          | 101                            | 1:64                          | 1:32                         |               |       |       |       |

|         |                          | 110                            | 1:128                         | 1:64                         |               |       |       |       |

|         |                          | 111                            | 1:256                         | 1 : 128                      |               |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 4.2.2.4 PIE1 Register

This register contains the individual enable bit for the comparator interrupt.

| <b>REGISTER 4-4:</b> | PIE1 REGISTER (ADDRESS 8CH)                                                                                                    |                            |     |                           |     |                         |                                |     |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|---------------------------|-----|-------------------------|--------------------------------|-----|--|--|

|                      | U-0                                                                                                                            | R/W-0                      | U-0 | U-0                       | U-0 | U-0                     | U-0                            | U-0 |  |  |

|                      |                                                                                                                                | CMIE                       | _   |                           |     | —                       | _                              | —   |  |  |

|                      | bit 7                                                                                                                          | bit 7 bit 0                |     |                           |     |                         |                                |     |  |  |

| bit 7                | bit 7 Unimplemented: Read as '0'                                                                                               |                            |     |                           |     |                         |                                |     |  |  |

| bit 6                | <b>CMIE</b> : Comparator Interrupt Enable bit<br>1 = Enables the Comparator interrupt<br>0 = Disables the Comparator interrupt |                            |     |                           |     |                         |                                |     |  |  |

| bit 5-0              | Unimpleme                                                                                                                      | Unimplemented: Read as '0' |     |                           |     |                         |                                |     |  |  |

|                      | Legend:<br>R = Readab<br>- n = Value a                                                                                         |                            |     | /ritable bit<br>it is set |     | nplemented<br>s cleared | bit, read as '<br>x = Bit is u |     |  |  |

## 4.2.2.5 PIR1 Register

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of |  |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User               |  |  |  |  |  |  |  |

|       | software should ensure the appropriate                                                     |  |  |  |  |  |  |  |

|       | interrupt flag bits are clear prior to enabling                                            |  |  |  |  |  |  |  |

|       | an interrupt.                                                                              |  |  |  |  |  |  |  |

## REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

| ER 4-5: | 4-5: PIRT REGISTER (ADDRESS 0CH) |               |               |              |          |           |                |       |  |  |  |

|---------|----------------------------------|---------------|---------------|--------------|----------|-----------|----------------|-------|--|--|--|

|         | U-0                              | R/W-0         | U-0           | U-0          | U-0      | U-0       | U-0            | U-0   |  |  |  |

|         |                                  | CMIF          |               | —            | _        |           |                |       |  |  |  |

|         | bit 7                            |               |               |              |          |           |                | bit 0 |  |  |  |

|         |                                  |               |               |              |          |           |                |       |  |  |  |

| bit 7   | Unimplemented: Read as '0'       |               |               |              |          |           |                |       |  |  |  |

| bit 6   | CMIF: Com                        | parator Inte  | errupt Flag b | it           |          |           |                |       |  |  |  |

|         | 1 = Compai                       | rator input h | nas changed   | l            |          |           |                |       |  |  |  |

|         | 0 = Compai                       | rator input h | nas not chan  | iged         |          |           |                |       |  |  |  |

| bit 5-0 | Unimpleme                        | ented: Rea    | d as '0'      |              |          |           |                |       |  |  |  |

|         |                                  |               |               |              |          |           |                |       |  |  |  |

|         | Legend:                          |               |               |              |          |           |                |       |  |  |  |

|         | R = Readab                       | ole bit       | W = W         | /ritable bit | U = Unim | plemented | bit, read as ' | 0'    |  |  |  |

|         | x = Bit is u                     | nknown        |               |              |          |           |                |       |  |  |  |

## 9.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

### REGISTER 9-1: CONFIGURATION WORD (ADDRESS 2007h)

| CP1              | CP0 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CP1                                                                                                                                    | CP0 <sup>(2)</sup>                                                                                                                                        | CP1                                                                                                                                                                | CP0 <sup>(2)</sup>                                                                                                         |                                                               | BODEN                     | CP1     | CP0 <sup>(2)</sup> | PWRTE       | WDTE      | F0SC1     | F0SC0 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------|---------|--------------------|-------------|-----------|-----------|-------|

| bit 13           | ļ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <u> </u>                                                                                                                               | ļļ                                                                                                                                                        |                                                                                                                                                                    | ļ                                                                                                                          |                                                               | <u> </u>                  | <u></u> | <u>I</u>           | <u></u>     | <u> </u>  | ļ         | bit 0 |

| bit 13-8<br>5-4: | Cod<br>11 =<br>10 =<br>01 =<br>00 =<br>Cod<br>11 =<br>00 =<br>00 =<br>Cod<br>11 =<br>10 =<br>01 =<br>01 =<br>01 =<br>01 =<br>01 =<br>01 =<br>01 =<br>00 =<br>01 =<br>00 =<br>01 =<br>00 | e protec<br>= Progra<br>= 0400h<br>= 0200h<br>= 0200h<br>= 0000h<br>= Progra<br>= 0200h<br>= 0000h<br>= protec<br>= Progra<br>= Progra | ode prote<br>ction for 2<br>m memo<br>-07FFh c<br>-07FFh c<br>-07FFh c<br>-07FFh c<br>-03FFh c<br>-03FFh c<br>-03FFh c<br>ction for 0<br>m memo<br>m memo | 2K progr<br>ry code<br>ode pro<br>ode pro<br>ode pro<br>ry code<br>ry code<br>ode pro<br>ode pro<br>ode pro<br>ode pro<br>ode pro<br>ode pro<br>ry code<br>ry code | am mem<br>protectic<br>tected<br>tected<br>tected<br>protectic<br>protectic<br>tected<br>gram me<br>protectic<br>protectic | ory<br>on off<br>on off<br>on off<br>mory<br>on off<br>on off |                           |         |                    |             |           |           |       |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                      | m memo<br>-01FFh c                                                                                                                                        |                                                                                                                                                                    |                                                                                                                            | on off                                                        |                           |         |                    |             |           |           |       |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                        | nted: Re                                                                                                                                                  | -                                                                                                                                                                  |                                                                                                                            |                                                               |                           |         |                    |             |           |           |       |

| bit 6            | BO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DEN: Br                                                                                                                                | own-out l                                                                                                                                                 | Reset E                                                                                                                                                            | nable bit                                                                                                                  | (1)                                                           |                           |         |                    |             |           |           |       |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BOR en<br>BOR dis                                                                                                                      |                                                                                                                                                           |                                                                                                                                                                    |                                                                                                                            |                                                               |                           |         |                    |             |           |           |       |

| bit 3            | 1 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>RTE</b> : Po<br>PWRT o<br>PWRT e                                                                                                    |                                                                                                                                                           | īmer Er                                                                                                                                                            | able bit <sup>(</sup>                                                                                                      | 1, 3)                                                         |                           |         |                    |             |           |           |       |

| bit 2            | 1 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TE: Wat<br>WDT en<br>WDT dis                                                                                                           |                                                                                                                                                           | mer Ena                                                                                                                                                            | able bit                                                                                                                   |                                                               |                           |         |                    |             |           |           |       |

| bit 1-0          | 11 =<br>10 =<br>01 =<br>00 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | = RC ose<br>= HS ose<br>= XT ose<br>= LP ose<br>e 1: En<br>va                                                                          | cillator<br>cillator<br>cillator<br>nabling B                                                                                                             | rown-ou                                                                                                                                                            | ut Reset a                                                                                                                 | automa                                                        | tically ena<br>ower-up Ti |         |                    |             |           |           |       |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2: Al<br>lis                                                                                                                           | l of the C<br>ted.                                                                                                                                        |                                                                                                                                                                    | -                                                                                                                          |                                                               | e given the<br>Power-up T |         |                    | nable the c | code prot | tection s | cheme |

| Legend<br>R = Re | l:<br>adable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | it                                                                                                                                     |                                                                                                                                                           | W =                                                                                                                                                                | Writable                                                                                                                   | bit                                                           | U =                       | Unimple | emented            | bit, read a | s '0'     |           |       |

### 9.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance or one with parallel resonance.

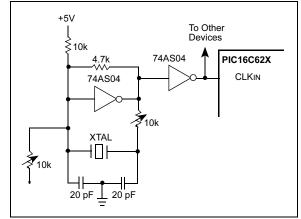

Figure 9-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

### FIGURE 9-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

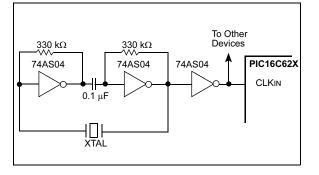

Figure 9-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a  $180^{\circ}$  phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 9-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

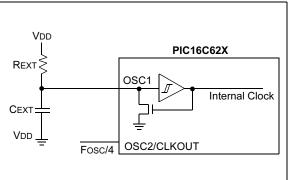

## 9.2.4 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 9-5 shows how the R/C combination is connected to the PIC16C62X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

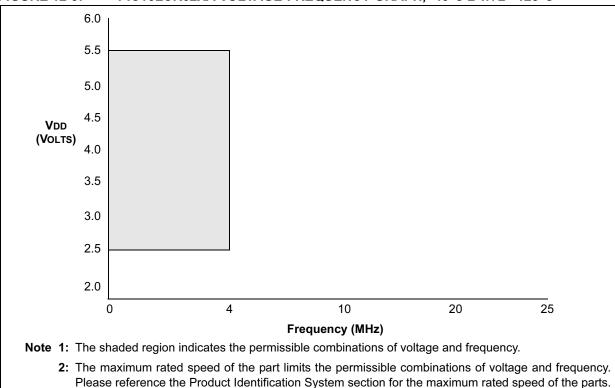

See Section 13.0 for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See Section 13.0 for variation of oscillator frequency due to VDD for given REXT/CEXT values, as well as frequency variation due to operating temperature for given R, C and VDD values.

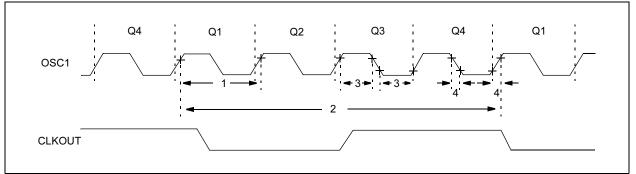

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

## FIGURE 9-5: RC OSCILLATOR MODE

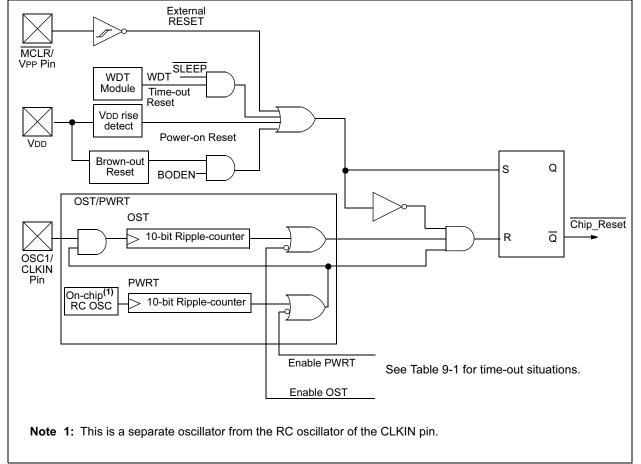

## 9.3 RESET

The PIC16C62X differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) WDT Reset (normal operation)

- e) WDT wake-up (SLEEP)

- f) Brown-out Reset (BOR)

Some registers are not affected in any RESET condition Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset,

MCLR Reset, WDT Reset and MCLR Reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 9-2. These bits are used in software to determine the nature of the RESET. See Table 9-5 for a full description of RESET states of all registers.

A simplified block diagram of the on-chip RESET circuit is shown in Figure 9-6.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 12-5 for pulse width specification.

## 9.9 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip                    | does | not | recommend | code |  |  |  |  |  |

|-------|------------------------------|------|-----|-----------|------|--|--|--|--|--|

|       | protecting windowed devices. |      |     |           |      |  |  |  |  |  |

## 9.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify. Only the Least Significant 4 bits of the ID locations are used.

## 9.11 In-Circuit Serial Programming™

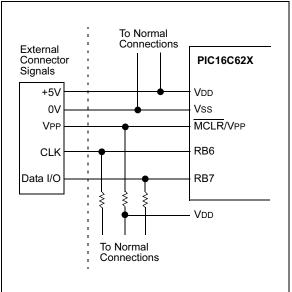

The PIC16C62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X/9XX Programming Specification (DS30228).

A typical In-Circuit Serial Programming connection is shown in Figure 9-19.

# FIGURE 9-19:

### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| TABLE 10-2. FICTOCO2A INSTRUCTION SET | TABLE 10-2: | PIC16C62X INSTRUCTION SET |

|---------------------------------------|-------------|---------------------------|

|---------------------------------------|-------------|---------------------------|

| Mnemonic, |          | Description                  |       | 14-Bit | Opcode | Status | Notes    |        |       |

|-----------|----------|------------------------------|-------|--------|--------|--------|----------|--------|-------|

| Operands  |          |                              |       | MSb    | Sb LSb |        | Affected |        |       |

| BYTE-OR   | ENTED I  | FILE REGISTER OPERATIONS     |       |        |        |        |          |        |       |

| ADDWF     | f, d     | Add W and f                  | 1     | 00     | 0111   | dfff   | ffff     | C,DC,Z | 1,2   |

| ANDWF     | f, d     | AND W with f                 | 1     | 00     | 0101   | dfff   | ffff     | Z      | 1,2   |

| CLRF      | f        | Clear f                      | 1     | 00     | 0001   | lfff   | ffff     | Z      | 2     |

| CLRW      | -        | Clear W                      | 1     | 00     | 0001   | 0000   | 0011     | Z      |       |

| COMF      | f, d     | Complement f                 | 1     | 00     | 1001   | dfff   | ffff     | Z      | 1,2   |

| DECF      | f, d     | Decrement f                  | 1     | 00     | 0011   | dfff   | ffff     | Z      | 1,2   |

| DECFSZ    | f, d     | Decrement f, Skip if 0       | 1(2)  | 00     | 1011   | dfff   | ffff     |        | 1,2,3 |

| INCF      | f, d     | Increment f                  | 1     | 00     | 1010   | dfff   | ffff     | Z      | 1,2   |

| INCFSZ    | f, d     | Increment f, Skip if 0       | 1(2)  | 00     | 1111   | dfff   | ffff     |        | 1,2,3 |

| IORWF     | f, d     | Inclusive OR W with f        | 1     | 00     | 0100   | dfff   | ffff     | Z      | 1,2   |

| MOVF      | f, d     | Move f                       | 1     | 00     | 1000   | dfff   | ffff     | Z      | 1,2   |

| MOVWF     | f        | Move W to f                  | 1     | 00     | 0000   | lfff   | ffff     |        |       |