Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | ·                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                |                                                                           |

| RAM Size                   | 80 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                   |

| Data Converters            | ·                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621-04i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Device Differences**

| Device                     | Voltage Range | Oscillator | Process Technology<br>(Microns) |

|----------------------------|---------------|------------|---------------------------------|

| PIC16C620 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C621 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C622 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C620A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

| PIC16CR620A <sup>(2)</sup> | 2.5 - 5.5     | See Note 1 | 0.7                             |

| PIC16C621A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

| PIC16C622A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

2: For ROM parts, operation from 2.5V - 3.0V will require the PIC16LCR62X parts.

**3:** For OTP parts, operation from 2.5V - 3.0V will require the PIC16LC62X parts.

4: For OTP parts, operations from 2.7V - 3.0V will require the PIC16LC62XA parts.

NOTES:

#### FIGURE 4-4: DATA MEMORY MAP FOR THE PIC16C620/621

| File     |                                  |                     | File        |  |  |

|----------|----------------------------------|---------------------|-------------|--|--|

| Address  | 3                                |                     | Address     |  |  |

| 00h      | INDF <sup>(1)</sup>              | INDF <sup>(1)</sup> | 80h         |  |  |

| 01h      | TMR0                             | OPTION              | 81h         |  |  |

| 02h      | PCL                              | PCL                 | 82h         |  |  |

| 03h      | STATUS                           | STATUS              | 83h         |  |  |

| 04h      | FSR                              | FSR                 | 84h         |  |  |

| 05h      | PORTA                            | TRISA               | 85h         |  |  |

| 06h      | PORTB                            | TRISB               | 86h         |  |  |

| 07h      |                                  |                     | 87h         |  |  |

| 08h      |                                  |                     | 88h         |  |  |

| 09h      |                                  |                     | 89h         |  |  |

| 0Ah      | PCLATH                           | PCLATH              | 8Ah         |  |  |

| 0Bh      | INTCON                           | INTCON              | 8Bh         |  |  |

| 0Ch      | PIR1                             | PIE1                | 8Ch         |  |  |

| 0Dh      |                                  |                     | 8Dh         |  |  |

| 0Eh      |                                  | PCON                | 8Eh         |  |  |

| 0Fh      |                                  |                     | 8Fh         |  |  |

| 10h      |                                  |                     | 90h         |  |  |

| 11h      |                                  |                     | 91h         |  |  |

| 12h      |                                  |                     | 92h         |  |  |

| 13h      |                                  |                     | 93h         |  |  |

| 14h      |                                  |                     | 94h         |  |  |

| 15h      |                                  |                     | 95h         |  |  |

| 16h      |                                  |                     | 96h         |  |  |

| 17h      |                                  |                     | 97h         |  |  |

| 18h      |                                  |                     | 98h         |  |  |

| 19h      |                                  |                     | 99h         |  |  |

| 1Ah      |                                  |                     | 9Ah         |  |  |

| 1Bh      |                                  |                     | 9Bh         |  |  |

| 1Ch      |                                  |                     | 9Ch         |  |  |

| 1Dh      |                                  |                     | 9Dh         |  |  |

| 1Eh      |                                  |                     | 9Eh         |  |  |

| 1Fh      | CMCON                            | VRCON               | 9Fh         |  |  |

| 20h      |                                  | _                   | A0h         |  |  |

|          | General                          |                     |             |  |  |

|          | Purpose<br>Register              |                     |             |  |  |

| 6Fh      | 5                                |                     |             |  |  |

| 70h      |                                  |                     |             |  |  |

|          |                                  |                     |             |  |  |

|          |                                  |                     |             |  |  |

|          |                                  |                     |             |  |  |

| 7Fh      |                                  |                     | FFh         |  |  |

|          | Bank 0                           | Bank 1              |             |  |  |

| <b>—</b> |                                  | 1 4                 |             |  |  |

| Unimp    | plemented data me                | mory locations, r   | ead as '0'. |  |  |

| Note 1:  | Note 1: Not a physical register. |                     |             |  |  |

|          |                                  |                     |             |  |  |

|          |                                  |                     |             |  |  |

# FIGURE 4-5:

#### DATA MEMORY MAP FOR THE PIC16C622

|                 | 1116                |                     |                 |

|-----------------|---------------------|---------------------|-----------------|

| File<br>Address | 8                   |                     | File<br>Address |

| 00h             | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |

| 01h             | TMR0                | OPTION              | 81h             |

| 02h             | PCL                 | PCL                 | 82h             |

| 03h             | STATUS              | STATUS              | 83h             |

| 04h             | FSR                 | FSR                 | 84h             |

| 05h             | PORTA               | TRISA               | 85h             |

| 06h             | PORTB               | TRISB               | 86h             |

| 00h             | TOILID              | TRIOD               | 87h             |

| 07h<br>08h      |                     |                     | 88h             |

| 00h             |                     |                     | 89h             |

| 03h<br>0Ah      | PCLATH              | PCLATH              | 8Ah             |

| 0An<br>0Bh      | INTCON              | INTCON              | 8Bh             |

| 0Dh             | PIR1                | PIE1                | 8Ch             |

| 0Ch<br>0Dh      | PIRI                | PIEI                | 8Dh             |

|                 |                     | PCON                |                 |

| 0Eh<br>0Fh      |                     | PCON                | 8Eh             |

|                 |                     |                     | 8Fh             |

| 10h             |                     |                     | 90h             |

| 11h             |                     |                     | 91h             |

| 12h             |                     |                     | 92h             |

| 13h             |                     |                     | 93h             |

| 14h             |                     |                     | 94h             |

| 15h             |                     |                     | 95h             |

| 16h             |                     |                     | 96h             |

| 17h             |                     |                     | 97h             |

| 18h             |                     |                     | 98h             |

| 19h             |                     |                     | 99h             |

| 1Ah             |                     |                     | 9Ah             |

| 1Bh             |                     |                     | 9Bh             |

| 1Ch             |                     |                     | 9Ch             |

| 1Dh             |                     |                     | 9Dh             |

| 1Eh             |                     |                     | 9Eh             |

| 1Fh             | CMCON               | VRCON               | 9Fh             |

| 20h             |                     |                     | A0h             |

|                 | General<br>Purpose  | General<br>Purpose  |                 |

|                 | Register            | Register            |                 |

|                 | 0                   | 5                   | BFh             |

|                 |                     |                     | C0h             |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

| 7Fh             |                     |                     | FFh             |

| , , , , , ,     | Bank 0              | Bank 1              |                 |

|                 |                     |                     |                 |

| Unim            | plemented data me   | mory locations, re  | ad as '0'.      |

| Note 1:         | Not a physical re   | aister              |                 |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

# FIGURE 4-6: DATA MEMORY MAP FOR THE PIC16C620A/CR620A/621A

|                                                   | 11010002                       |                     | - 17 (          |  |  |

|---------------------------------------------------|--------------------------------|---------------------|-----------------|--|--|

| File<br>Address                                   | 3                              |                     | File<br>Address |  |  |

| 00h                                               | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup> | 80h             |  |  |

| 01h                                               | TMR0                           | OPTION              | 81h             |  |  |

| 02h                                               | PCL                            | PCL                 | 82h             |  |  |

| 03h                                               | STATUS                         | STATUS              | 83h             |  |  |

| 04h                                               | FSR                            | FSR                 | 84h             |  |  |

| 05h                                               | PORTA                          | TRISA               | 85h             |  |  |

| 06h                                               | PORTB                          | TRISB               | 86h             |  |  |

| 07h                                               |                                |                     | 87h             |  |  |

| 08h                                               |                                |                     | 88h             |  |  |

| 09h                                               |                                |                     | 89h             |  |  |

| 0Ah                                               | PCLATH                         | PCLATH              | 8Ah             |  |  |

| 0Bh                                               | INTCON                         | INTCON              | 8Bh             |  |  |

| 0Ch                                               | PIR1                           | PIE1                | 8Ch             |  |  |

| 0Dh                                               |                                |                     | 8Dh             |  |  |

| 0Eh                                               |                                | PCON                | 8Eh             |  |  |

| 0Fh                                               |                                |                     | 8Fh             |  |  |

| 10h                                               |                                |                     | 90h             |  |  |

| 11h                                               |                                |                     | 91h             |  |  |

| 12h                                               |                                |                     | 92h             |  |  |

| 13h                                               |                                |                     | 93h             |  |  |

| 14h                                               |                                |                     | 94h             |  |  |

| 15h                                               |                                |                     | 95h             |  |  |

| 16h                                               |                                |                     | 96h             |  |  |

| 17h                                               |                                |                     | 97h             |  |  |

| 18h                                               |                                |                     | 98h             |  |  |

| 19h                                               |                                |                     | 99h             |  |  |

| 1Ah                                               |                                |                     | 9Ah             |  |  |

| 1Bh                                               |                                |                     | 9Bh             |  |  |

| 1Ch                                               |                                |                     | 9Ch             |  |  |

| 1Dh                                               |                                |                     | 9Dh             |  |  |

| 1Eh                                               |                                |                     | 9Eh             |  |  |

| 1Fh                                               | CMCON                          | VRCON               | 9Fh             |  |  |

| 20h                                               | General<br>Purpose<br>Register |                     | A0h             |  |  |

| 6Fh                                               |                                |                     |                 |  |  |

| 70h                                               | General                        |                     | F0h             |  |  |

|                                                   | Purpose<br>Register            | Accesses<br>70h-7Fh | FFh             |  |  |

| 7Fh Bank 0 Bank 1                                 |                                |                     |                 |  |  |

| Unimplemented data memory locations, read as '0'. |                                |                     |                 |  |  |

| Note 1:                                           | Not a physical re              | gister.             |                 |  |  |

|                                                   |                                |                     |                 |  |  |

#### FIGURE 4-7: DATA MEMORY MAP FOR THE PIC16C622A

|                                                   |                     | C10C022A            |                 |  |  |

|---------------------------------------------------|---------------------|---------------------|-----------------|--|--|

| File<br>Address                                   | 3                   |                     | File<br>Address |  |  |

| 00h                                               | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |  |  |

| 01h                                               | TMR0                | OPTION              | 81h             |  |  |

| 02h                                               | PCL                 | PCL                 | 82h             |  |  |

| 03h                                               | STATUS              | STATUS              | 83h             |  |  |

| 04h                                               | FSR                 | FSR                 | 84h             |  |  |

| 05h                                               | PORTA               | TRISA               | 85h             |  |  |

| 06h                                               | PORTB               | TRISB               | 86h             |  |  |

| 07h                                               |                     |                     | 87h             |  |  |

| 08h                                               |                     |                     | 88h             |  |  |

| 09h                                               |                     |                     | 89h             |  |  |

| 0Ah                                               | PCLATH              | PCLATH              | 8Ah             |  |  |

| 0Bh                                               | INTCON              | INTCON              | 8Bh             |  |  |

| 0Ch                                               | PIR1                | PIE1                | 8Ch             |  |  |

| 0Dh                                               |                     |                     | 8Dh             |  |  |

| 0Eh                                               |                     | PCON                | 8Eh             |  |  |

| 0Fh                                               |                     |                     | 8Fh             |  |  |

| 10h                                               |                     |                     | 90h             |  |  |

| 11h                                               |                     |                     | 91h             |  |  |

| 12h                                               |                     |                     | 92h             |  |  |

| 13h                                               |                     |                     | 93h             |  |  |

| 14h                                               |                     |                     | 94h             |  |  |

| 15h                                               |                     |                     | 95h             |  |  |

| 16h                                               |                     |                     | 96h             |  |  |

| 17h                                               |                     |                     | 97h             |  |  |

| 18h                                               |                     |                     | 98h             |  |  |

| 19h                                               |                     |                     | 99h             |  |  |

| 1Ah                                               |                     |                     | 9Ah             |  |  |

| 1Bh                                               |                     |                     | 9Bh             |  |  |

| 1Ch                                               |                     |                     | 9Ch             |  |  |

| 1Dh                                               |                     |                     | 9Dh             |  |  |

| 1Eh                                               |                     |                     | 9Eh             |  |  |

| 1Fh                                               | CMCON               | VRCON               | 9Fh             |  |  |

| 20h                                               |                     |                     | A0h             |  |  |

|                                                   | General             | General             | Aon             |  |  |

|                                                   | Purpose<br>Register | Purpose<br>Register |                 |  |  |

|                                                   | rtegister           | rtegister           | BFh             |  |  |

|                                                   |                     |                     | C0h             |  |  |

| 0.51                                              |                     |                     |                 |  |  |

| 6Fh                                               | 0                   |                     | F0h             |  |  |

| 70h                                               | General<br>Purpose  | Accesses            |                 |  |  |

| 754                                               | Register            | 70h-7Fh             | FFh             |  |  |

| 7Fh                                               | Bank 0              | Bank 1              | → FF11          |  |  |

|                                                   |                     |                     |                 |  |  |

| Unimplemented data memory locations, read as '0'. |                     |                     |                 |  |  |

| Note 1: Not a physical register.                  |                     |                     |                 |  |  |

### 4.2.2.4 PIE1 Register

This register contains the individual enable bit for the comparator interrupt.

| <b>REGISTER 4-4:</b> | PIE1 REGISTER (ADDRESS 8CH)                                                                                                                       |            |          |     |     |     |     |       |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|-----|-----|-----|-----|-------|

|                      | U-0                                                                                                                                               | R/W-0      | U-0      | U-0 | U-0 | U-0 | U-0 | U-0   |

|                      |                                                                                                                                                   | CMIE       | _        |     |     | —   | _   | —     |

|                      | bit 7                                                                                                                                             |            |          |     |     |     |     | bit 0 |

| bit 7                | Unimpleme                                                                                                                                         | nted: Read | d as '0' |     |     |     |     |       |

| bit 6                | <b>CMIE</b> : Comparator Interrupt Enable bit<br>1 = Enables the Comparator interrupt<br>0 = Disables the Comparator interrupt                    |            |          |     |     |     |     |       |

| bit 5-0              | Unimplemented: Read as '0'                                                                                                                        |            |          |     |     |     |     |       |

|                      | Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'- n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown |            |          |     |     |     |     |       |

# 4.2.2.5 PIR1 Register

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | its corresponding enable bit or the global<br>enable bit, GIE (INTCON<7>). User            |  |  |  |  |  |

|       | software should ensure the appropriate                                                     |  |  |  |  |  |

|       | interrupt flag bits are clear prior to enabling                                            |  |  |  |  |  |

|       | an interrupt.                                                                              |  |  |  |  |  |

# REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

| ER 4-5: | PIRT REGISTER (ADDRESS UCH)                                          |               |               |           |              |           |              |        |  |

|---------|----------------------------------------------------------------------|---------------|---------------|-----------|--------------|-----------|--------------|--------|--|

|         | U-0                                                                  | R/W-0         | U-0           | U-0       | U-0          | U-0       | U-0          | U-0    |  |

|         |                                                                      | CMIF          |               | —         | _            |           |              |        |  |

|         | bit 7                                                                |               |               |           |              |           |              | bit 0  |  |

|         |                                                                      |               |               |           |              |           |              |        |  |

| bit 7   | Unimplemented: Read as '0'                                           |               |               |           |              |           |              |        |  |

| bit 6   | CMIF: Com                                                            | parator Inte  | errupt Flag b | it        |              |           |              |        |  |

|         | 1 = Compai                                                           | rator input h | nas changed   | l         |              |           |              |        |  |

|         | 0 = Comparator input has not changed                                 |               |               |           |              |           |              |        |  |

| bit 5-0 | Unimplemented: Read as '0'                                           |               |               |           |              |           |              |        |  |

|         |                                                                      |               |               |           |              |           |              |        |  |

|         | Legend:                                                              |               |               |           |              |           |              |        |  |

|         | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |               |               |           |              |           |              |        |  |

|         | - n = Value                                                          | at POR        | '1' = B       | it is set | '0' = Bit is | s cleared | x = Bit is u | nknown |  |

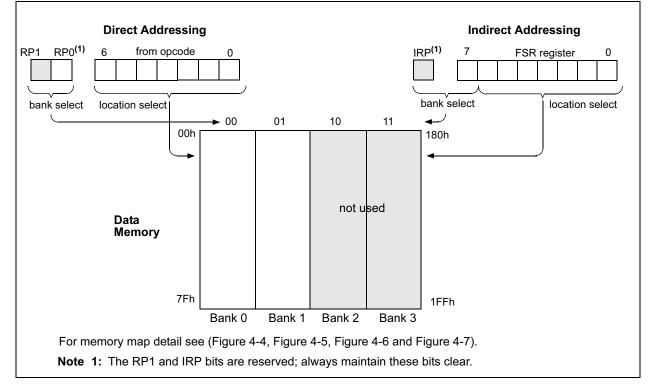

## 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-9. However, IRP is not used in the PIC16C62X.

A simple program to clear RAM location 20h-7Fh using indirect addressing is shown in Example 4-1.

| EXAN  | IPLE 4- | 1: INC | DIRECT ADDRESSING    |

|-------|---------|--------|----------------------|

|       | movlw   | 0x20   | ;initialize pointer  |

|       | movwf   | FSR    | ;to RAM              |

| NEXT  | clrf    | INDF   | ;clear INDF register |

|       | incf    | FSR    | ;inc pointer         |

|       | btfss   | FSR,7  | ;all done?           |

|       | goto    | NEXT   | ;no clear next       |

|       |         |        | ;yes continue        |

| CONTI | NUE:    |        |                      |

|       |         |        |                      |

# FIGURE 4-9: DIRECT/INDIRECT ADDRESSING PIC16C62X

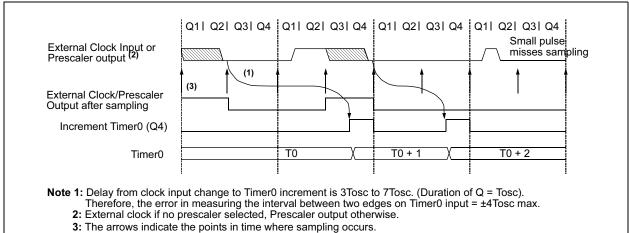

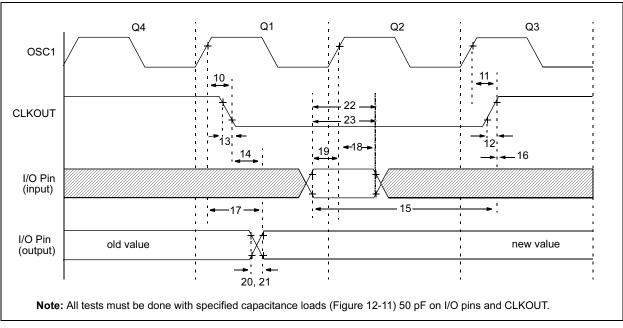

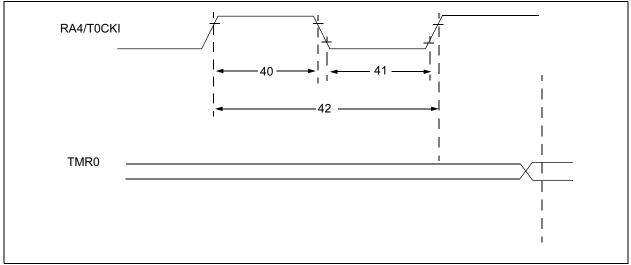

# 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

# 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

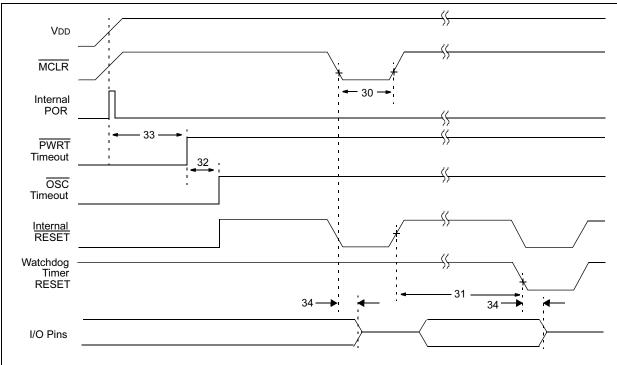

# 9.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

### 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

#### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

The Power-up Time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

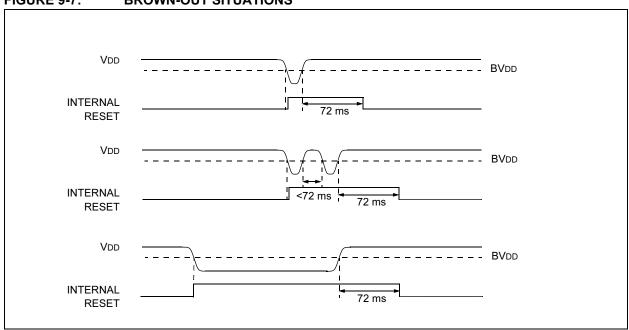

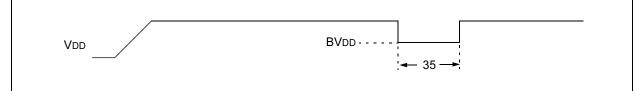

### 9.4.4 BROWN-OUT RESET (BOR)

The PIC16C62X members have on-chip Brown-out Reset circuitry. A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V refer to VBOR parameter D005 (VBOR) for greater than parameter (TBOR) in Table 12-5. The brown-out situation will RESET the chip. A RESET won't occur if VDD falls below 4.0V for less than parameter (TBOR).

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 9-7 shows typical Brown-out situations.

### FIGURE 9-7: BROWN-OUT SITUATIONS

| SUBLW        | Subtract W from Literal                                                       | SUBWF               | Subtract W from f                                                              |

|--------------|-------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------|

| Syntax:      | [ <i>label</i> ] SUBLW k                                                      | Syntax:             | [ <i>label</i> ] SUBWF f,d                                                     |

| Operands:    | $0 \le k \le 255$                                                             | Operands:           | $0 \le f \le 127$                                                              |

| Operation:   | $k - (W) \to (W)$                                                             |                     | d ∈ [0,1]                                                                      |

| Status       | C, DC, Z                                                                      | Operation:          | (f) - (W) $\rightarrow$ (dest)                                                 |

| Affected:    |                                                                               | Status<br>Affected: | C, DC, Z                                                                       |

| Encoding:    | 11 110x kkkk kkkk                                                             |                     |                                                                                |

| Description: | The W register is subtracted (2's                                             | Encoding:           | 00 0010 dfff ffff                                                              |

|              | complement method) from the eight<br>bit literal 'k'. The result is placed in | Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0, |

|              | the W register.                                                               |                     | the result is stored in the W register.                                        |

| Words:       | 1                                                                             |                     | If 'd' is 1, the result is stored back in                                      |

| Cycles:      | 1                                                                             |                     | register 'f'.                                                                  |

| Example 1:   | SUBLW 0x02                                                                    | Words:              | 1                                                                              |

| ·            | Before Instruction                                                            | Cycles:             | 1                                                                              |

|              | W = 1                                                                         | Example 1:          | SUBWF REG1,1                                                                   |

|              | C = ?                                                                         |                     | Before Instruction                                                             |

|              | After Instruction                                                             |                     | REG1= 3<br>W = 2                                                               |

|              | W = 1<br>C = 1; result is positive                                            |                     | C = ?                                                                          |

| Example 2:   | Before Instruction                                                            |                     | After Instruction                                                              |

| Example 2.   | W = 2                                                                         |                     | REG1= 1                                                                        |

|              | C = ?                                                                         |                     | W = 2<br>C = 1; result is positive                                             |

|              | After Instruction                                                             | Example 2:          | Before Instruction                                                             |

|              | W = 0                                                                         | ·                   | REG1= 2                                                                        |

|              | C = 1; result is zero                                                         |                     | W = 2                                                                          |

| Example 3:   | Before Instruction                                                            |                     | C = ?                                                                          |

|              | W = 3<br>C = ?                                                                |                     | After Instruction                                                              |

|              | After Instruction                                                             |                     | REG1= 0<br>W = 2                                                               |

|              | W = 0 x F F                                                                   |                     | C = 1; result is zero                                                          |

|              | C = 0; result is negative                                                     | Example 3:          | Before Instruction                                                             |

|              |                                                                               |                     | REG1= 1<br>W = 2                                                               |

|              |                                                                               |                     | W = 2<br>C = ?                                                                 |

|              |                                                                               |                     | After Instruction                                                              |

|              |                                                                               |                     | REG1= 0xFF                                                                     |

|              |                                                                               |                     | W = 2                                                                          |

|              |                                                                               |                     | C = 0; result is negative                                                      |

| SWAPF            | Swap Ni                                                                                                                                                                    | bbles in                   | f     |              |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------|--------------|--|--|

| Syntax:          | [label]                                                                                                                                                                    | [ <i>label</i> ] SWAPF f,d |       |              |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 12\\ d\in \left[0,1\right] \end{array}$                                                                                                      | 27                         |       |              |  |  |

| Operation:       | (f<3:0>) -<br>(f<7:4>) -                                                                                                                                                   |                            | · · · |              |  |  |

| Status Affected: | None                                                                                                                                                                       |                            |       |              |  |  |

| Encoding:        | 00                                                                                                                                                                         | 1110                       | dfff  | ffff         |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in W<br>register. If 'd' is 1, the result is<br>placed in register 'f'. |                            |       |              |  |  |

| Words:           | 1                                                                                                                                                                          |                            |       |              |  |  |

| Cycles:          | 1                                                                                                                                                                          |                            |       |              |  |  |

| Example          | SWAPF                                                                                                                                                                      | REG,                       | 0     |              |  |  |

|                  | Before Instruction                                                                                                                                                         |                            |       |              |  |  |

|                  |                                                                                                                                                                            | REG1                       | = (   | DxA5         |  |  |

|                  | After Inst                                                                                                                                                                 | ruction                    |       |              |  |  |

|                  |                                                                                                                                                                            | REG1<br>W                  |       | 0xA5<br>0x5A |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [label] TRIS f                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 0110 Offf                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Description:     | The instruction is supported for<br>code compatibility with the<br>PIC16C5X products. Since TRIS<br>registers are readable and<br>writable, the user can directly<br>address them. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Example          |                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup> prod-<br>ucts, do not use this<br>instruction.                                                             |  |  |  |  |  |  |  |  |

| XORLW                                                                                                    | Exclusive OR Literal with W                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:                                                                                                  | [ <i>label</i> XORLW k<br>]                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| Operands:                                                                                                | 0 ≤ k ≤ 255                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| Operation:                                                                                               | (W) .XOR. $k \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Encoding:                                                                                                | 11 1010 kkkk kkkk                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Description:                                                                                             | The contents of the W register<br>are XOR'ed with the eight bit<br>literal 'k'. The result is placed in<br>the W register.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Example:                                                                                                 | XORLW 0xAF                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

|                                                                                                          | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

|                                                                                                          | W = 0xB5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

|                                                                                                          | After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

|                                                                                                          | W = 0x1A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| XORWF                                                                                                    | Evolucius OD W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|                                                                                                          | Exclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Syntax:                                                                                                  | [ <i>label</i> ] XORWF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| Syntax:                                                                                                  | [ <i>label</i> ] XORWF f,d $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:                                                                                     | $ \begin{array}{ll} \textit{[label]} & XORWF & f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \end{array} $                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:                                                                       | $ \begin{array}{ll} \textit{[label]} & \text{XORWF} & \textit{f,d} \\ 0 \leq \textit{f} \leq 127 \\ d \in [0,1] \\ (W) & \text{XOR.} & (\textit{f}) \rightarrow (\textit{dest}) \end{array} $                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] XORWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{array}{c c} \textit{[label]} & \text{XORWF} & \textit{f,d} \\ 0 \leq \textit{f} \leq 127 \\ d \in [0,1] \\ (W) . \text{XOR.} (\textit{f}) \rightarrow (\text{dest}) \\ \hline Z \\ \hline \hline 00 & 0110 & \text{dfff} & \text{ffff} \\ \hline \text{Exclusive OR the contents of the} \\ W \text{ register with register 'f'. If 'd' is} \\ 0, \text{ the result is stored in the W} \\ \text{register. If 'd' is 1, the result is} \end{array}$                             |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d$ $0 \le f \le 127$ $d \in [0,1]$ (W) .XOR. (f) $\rightarrow$ (dest) Z $\boxed{00 \qquad 0110 \qquad dfff \qquad ffff}$ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'.                                                                                                                              |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $[label] XORWF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (W) .XOR. (f) $\rightarrow$ (dest) Z $\boxed{00  0110  dfff  ffff}$ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. 1                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | [ <i>label</i> ] XORWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)<br>Z<br>00 0110 dfff ffff<br>Exclusive OR the contents of the<br>W register with register 'f'. If 'd' is<br>0, the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'.<br>1<br>1                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \\ XORWF REG 1 \\ \end{bmatrix}$                                                                                          |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \\ XORWF & REG & 1 \\ \hline Before Instruction \\ REG & = 0xAF \\ \end{bmatrix}$                            |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF}  f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W \\ register. If 'd' is 1, the result is \\ stored back in register 'f'. \\ 1 \\ 1 \\ XORWF & REG & 1 \\ \hline Before Instruction \\ \hline REG &= 0xAF \\ W &= 0xB5 \\ \end{bmatrix}$ |  |  |  |  |  |  |  |  |  |

# 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended) (CONT.)

|                                         |                                                  |                                                                                                                                                                                               | Stand                                                                                                                                                                                                                                                                                                                                                                                                    | dard O                 | perati                        | ng Con                                                                                                                                                                                                                                 | ditions (unless otherwise stated)                                                  |

|-----------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                                         |                                                  |                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                          | empera                 |                               | $\begin{array}{ll} 0^{\circ}C & \leq TA \leq +85^{\circ}C \text{ for industrial and} \\ 0^{\circ}C & \leq TA \leq +70^{\circ}C \text{ for commercial and} \\ 0^{\circ}C & \leq TA \leq +125^{\circ}C \text{ for extended} \end{array}$ |                                                                                    |

| PIC16L                                  |                                                  |                                                                                                                                                                                               | $\begin{array}{ c c c c c c } \hline Standard Operating Conditions (unless otherwise stated) \\ Operating temperature & -40^{\circ}C & \leq TA \leq +85^{\circ}C \text{ for industrial and} \\ & 0^{\circ}C & \leq TA \leq +70^{\circ}C \text{ for commercial a} \\ & -40^{\circ}C & \leq TA \leq +125^{\circ}C \text{ for extended} \\ Operating voltage VDD range is the PIC16C62X range. \end{array}$ |                        |                               |                                                                                                                                                                                                                                        |                                                                                    |

| Param<br>. No.                          | Sym                                              | Characteristic                                                                                                                                                                                | Min                                                                                                                                                                                                                                                                                                                                                                                                      | Тур†                   | Мах                           | Units                                                                                                                                                                                                                                  | Conditions                                                                         |

| D022<br>D022A<br>D023<br>D023A<br>D0222 | ΔIWDT<br>ΔIBOR<br>ΔICOM<br>P<br>ΔIVREF<br>ΔIVREF | WDT Current <sup>(5)</sup><br>Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each<br>Comparator <sup>(5)</sup><br>VREF Current <sup>(5)</sup><br>WDT Current <sup>(5)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                          | 6.0<br>350<br>—<br>6.0 | 20<br>25<br>425<br>100<br>300 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ                                                                                                                                                                                                             | VDD=4.0V $(125°C)$ BOD enabled, VDD = 5.0V<br>VDD = 4.0V<br>VDD = 4.0V<br>VDD=3.0V |

| D022A<br>D023<br>D023A                  | ΔIBOR<br>ΔICOM<br>P<br>ΔIVREF                    | Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each<br>Comparator <sup>(5)</sup><br>VREF Current <sup>(5)</sup>                                                             |                                                                                                                                                                                                                                                                                                                                                                                                          | 350<br>—               | 425<br>100<br>300             | μΑ<br>μΑ<br>μΑ                                                                                                                                                                                                                         | BOD enabled, VDD = 5.0V<br>VDD = 3.0V<br>VDD = 3.0V                                |