Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | ·                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | ·                                                                         |

| RAM Size                   | 80 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                   |

| Data Converters            | ·                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

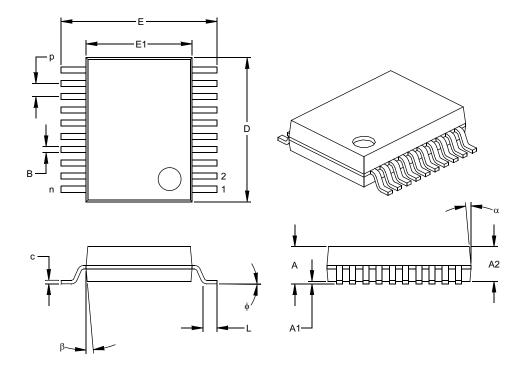

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621-20-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART, PRO MATE and PowerSmart are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Accuron, Application Maestro, dsPIC, dsPICDEM, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICkit, PICDEM, PICDEM.net, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPIC, Select Mode, SmartSensor, SmartShunt, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

#### **Device Differences**

| Device                     | Voltage Range | Oscillator | Process Technology<br>(Microns) |

|----------------------------|---------------|------------|---------------------------------|

| PIC16C620 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C621 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C622 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C620A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

| PIC16CR620A <sup>(2)</sup> | 2.5 - 5.5     | See Note 1 | 0.7                             |

| PIC16C621A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

| PIC16C622A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

2: For ROM parts, operation from 2.5V - 3.0V will require the PIC16LCR62X parts.

**3:** For OTP parts, operation from 2.5V - 3.0V will require the PIC16LC62X parts.

4: For OTP parts, operations from 2.7V - 3.0V will require the PIC16LC62XA parts.

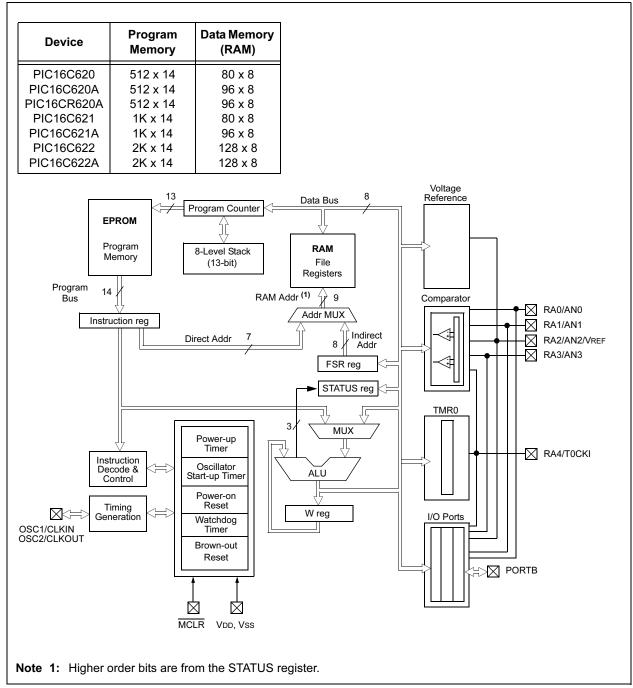

### 1.0 GENERAL DESCRIPTION

The PIC16C62X devices are 18 and 20-Pin ROM/ EPROM-based members of the versatile PICmicro<sup>®</sup> family of low cost, high performance, CMOS, fullystatic, 8-bit microcontrollers.

All PICmicro microcontrollers employ an advanced RISC architecture. The PIC16C62X devices have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16C62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC16C620A, PIC16C621A and PIC16CR620A have 96 bytes of RAM. The PIC16C622(A) has 128 bytes of RAM. Each device has 13 I/O pins and an 8-bit timer/counter with an 8-bit programmable prescaler. In addition, the PIC16C62X adds two analog comparators with a programmable on-chip voltage reference module. The comparator module is ideally suited for applications requiring a low cost analog interface (e.g., battery chargers, threshold detectors, white goods controllers, etc).

PIC16C62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (Power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external and internal interrupts and RESET.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock- up.

A UV-erasable CERDIP-packaged version is ideal for code development while the cost effective One-Time-Programmable (OTP) version is suitable for production in any volume.

Table 1-1 shows the features of the PIC16C62X midrange microcontroller families.

A simplified block diagram of the PIC16C62X is shown in Figure 3-1.

The PIC16C62X series fits perfectly in applications ranging from battery chargers to low power remote sensors. The EPROM technology makes

customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C62X very versatile.

### 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to PIC16C62X family of devices (Appendix B). The PIC16C62X family fills the niche for users wanting to migrate up from the PIC16C5X family and not needing various peripheral features of other members of the PIC16XX mid-range microcontroller family.

### 1.2 Development Support

The PIC16C62X family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low cost development programmer and a full-featured programmer. Third Party "C" compilers are also available.

## 2.0 PIC16C62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C62X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the Oscillator modes.

Microchip's PICSTART<sup>®</sup> and PRO MATE<sup>®</sup> programmers both support programming of the PIC16C62X.

Note: Microchip does not recommend code protecting windowed devices.

#### 2.2 One-Time-Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

### 2.3 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who chose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices, but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

### 2.4 Serialized Quick-Turnaround-Production<sup>sm</sup> (SQTP<sup>sm</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry-code, password or ID number.

#### FIGURE 3-1: BLOCK DIAGRAM

# 3.1 Clocking Scheme/Instruction Cycle

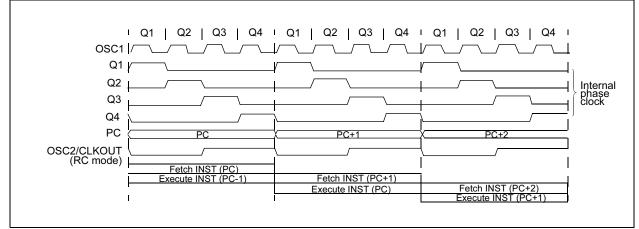

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

### 3.2 Instruction Flow/Pipelining

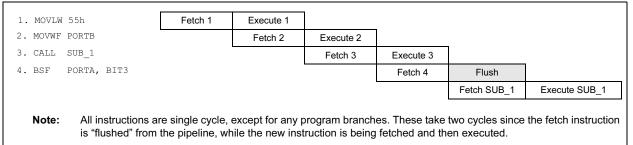

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

### 4.2 Data Memory Organization

The data memory (Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7) is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20-7Fh (Bank0) on the PIC16C620A/CR620A/621A and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16C622 and PIC16C622A are General Purpose Registers implemented as static RAM. Some Special Purpose Registers are mapped in Bank 1.

Addresses F0h-FFh of bank1 are implemented as common ram and mapped back to addresses 70h-7Fh in bank0 on the PIC16C620A/621A/622A/CR620A.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 80 x 8 in the PIC16C620/621, 96 x 8 in the PIC16C620A/621A/CR620A and 128 x 8 in the PIC16C622(A). Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

### 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-Chip Voltage Reference (Section 8.0) can also be an input to the comparators.

The CMCON register, shown in Register 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-1.

### REGISTER 7-1: CMCON REGISTER (ADDRESS 1Fh)

|         |                   |                                 | <b>(</b> | ,   |       |       |       |       |

|---------|-------------------|---------------------------------|----------|-----|-------|-------|-------|-------|

|         | R-0               | R-0                             | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|         | C2OUT             | C10UT                           | —        | —   | CIS   | CM2   | CM1   | CM0   |

|         | bit 7             |                                 |          |     |       |       |       | bit 0 |

|         |                   |                                 |          |     |       |       |       |       |

| bit 7   | <b>C2OUT</b> : Co | omparator 2                     | output   |     |       |       |       |       |

|         | 1 = C2 VIN        | + > C2 VIN-                     |          |     |       |       |       |       |

|         | 0 = C2 VIN        | + < C2 VIN-                     |          |     |       |       |       |       |

| bit 6   | <b>C1OUT</b> : Co | omparator 1                     | output   |     |       |       |       |       |

|         | 1 = C1 VIN        | + > C1 VIN-                     |          |     |       |       |       |       |

|         | 0 = C1 VIN        | + < C1 VIN-                     |          |     |       |       |       |       |

| bit 5-4 | Unimplem          | ented: Read                     | d as '0' |     |       |       |       |       |

| bit 3   | CIS: Comp         | arator Input                    | Switch   |     |       |       |       |       |

|         | When CM<          | <2:0>: = 001                    | :        |     |       |       |       |       |

|         | 1 = C1 VIN-       | - connects to                   | o RA3    |     |       |       |       |       |

|         | 0 = C1 VIN        | - connects to                   | o RA0    |     |       |       |       |       |

|         | When CM<          | <2:0> = 010:                    |          |     |       |       |       |       |

|         |                   | <ul> <li>connects to</li> </ul> |          |     |       |       |       |       |

|         |                   | I- connects t                   |          |     |       |       |       |       |

|         |                   | - connects to                   |          |     |       |       |       |       |

|         | C2 VIN            | I- connects t                   | 0 RA1    |     |       |       |       |       |

| bit 2-0 | CM<2:0>:          | Comparator                      | mode.    |     |       |       |       |       |

|         |                   |                                 |          |     |       |       |       |       |

|         | Legend:           |                                 |          |     |       |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### TABLE 9-4: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register | Address | Power-on Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during<br/>SLEEP</li> <li>WDT Reset</li> <li>Brown-out Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP<br/>through interrupt</li> <li>Wake-up from SLEEP<br/>through WDT time-out</li> </ul> |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W        | _       | xxxx xxxx      | <u>uuuu</u> uuuu                                                                                                                                           | <u></u>                                                                                                           |

| INDF     | 00h     |                | _                                                                                                                                                          | _                                                                                                                 |

| TMR0     | 01h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | นนนน นนนน                                                                                                         |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                                                                                  | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                                                                                   | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR      | 04h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | <u>uuuu</u> uuuu                                                                                                  |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                                                                                     | u uuuu                                                                                                            |

| PORTB    | 06h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | uuuu uuuu                                                                                                         |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                                                                                    | uu uuuu                                                                                                           |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                                                                                     | u uuuu                                                                                                            |

| INTCON   | 0Bh     | 0000 000x      | 0000 000u                                                                                                                                                  | uuuu uqqq <sup>(2)</sup>                                                                                          |

| PIR1     | 0Ch     | -0             | -0                                                                                                                                                         | -q (2,5)                                                                                                          |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                                                                                     | u uuuu                                                                                                            |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PIE1     | 8Ch     | -0             | -0                                                                                                                                                         | -u                                                                                                                |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                                                                        | uu                                                                                                                |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                                                                                  | uuu- uuuu                                                                                                         |

#### TABLE 9-5: INITIALIZATION CONDITION FOR REGISTERS

$\label{eq:legend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 9-4 for RESET value for specific condition.

5: If wake-up was due to comparator input changing, then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = u.

**6:** If RESET was due to brown-out, then bit 0 = 0. All other RESETS will cause bit 0 = u.

#### 9.5 Interrupts

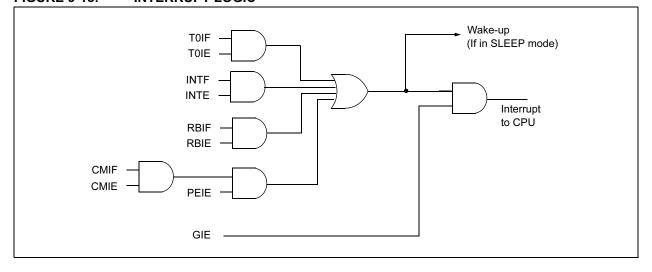

The PIC16C62X has 4 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB<7:4>)

- · Comparator interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which reenable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h.

FIGURE 9-15: INTERRUPT LOGIC

Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/ INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 9-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

| TABLE 10-2: PIC16C62X INSTRUCTION SET |

|---------------------------------------|

|---------------------------------------|

| Mnemonic, Descr<br>Operands |          | Description                  | Cycles | 14-Bit Opcode |      |      |      | Status   | Notes |

|-----------------------------|----------|------------------------------|--------|---------------|------|------|------|----------|-------|

|                             |          |                              |        | MSb           |      | LSb  |      | Affected |       |

| BYTE-OR                     | IENTED I | FILE REGISTER OPERATIONS     |        |               |      |      |      |          |       |

| ADDWF                       | f, d     | Add W and f                  | 1      | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |

| ANDWF                       | f, d     | AND W with f                 | 1      | 00            | 0101 | dfff | ffff | Z        | 1,2   |

| CLRF                        | f        | Clear f                      | 1      | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW                        | -        | Clear W                      | 1      | 00            | 0001 | 0000 | 0011 | Z        |       |

| COMF                        | f, d     | Complement f                 | 1      | 00            | 1001 | dfff | ffff | Z        | 1,2   |

| DECF                        | f, d     | Decrement f                  | 1      | 00            | 0011 | dfff | ffff | Z        | 1,2   |

| DECFSZ                      | f, d     | Decrement f, Skip if 0       | 1(2)   | 00            | 1011 | dfff | ffff |          | 1,2,3 |

| INCF                        | f, d     | Increment f                  | 1      | 00            | 1010 | dfff | ffff | Z        | 1,2   |

| INCFSZ                      | f, d     | Increment f, Skip if 0       | 1(2)   | 00            | 1111 | dfff | ffff |          | 1,2,3 |

| IORWF                       | f, d     | Inclusive OR W with f        | 1      | 00            | 0100 | dfff | ffff | Z        | 1,2   |

| MOVF                        | f, d     | Move f                       | 1      | 00            | 1000 | dfff | ffff | Z        | 1,2   |

| MOVWF                       | f        | Move W to f                  | 1      | 00            | 0000 | lfff | ffff |          |       |

| NOP                         | -        | No Operation                 | 1      | 00            | 0000 | 0xx0 | 0000 |          |       |

| RLF                         | f, d     | Rotate Left f through Carry  | 1      | 00            | 1101 | dfff | ffff | С        | 1,2   |

| RRF                         | f, d     | Rotate Right f through Carry | 1      | 00            | 1100 | dfff | ffff | С        | 1,2   |

| SUBWF                       | f, d     | Subtract W from f            | 1      | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |

| SWAPF                       | f, d     | Swap nibbles in f            | 1      | 00            | 1110 | dfff | ffff |          | 1,2   |

| XORWF                       | f, d     | Exclusive OR W with f        | 1      | 00            | 0110 | dfff | ffff | Z        | 1,2   |

| BIT-ORIEN                   | NTED FIL | E REGISTER OPERATIONS        |        |               |      |      |      | •        |       |

| BCF                         | f, b     | Bit Clear f                  | 1      | 01            | 00bb | bfff | ffff |          | 1,2   |

| BSF                         | f, b     | Bit Set f                    | 1      | 01            | 01bb | bfff | ffff |          | 1,2   |

| BTFSC                       | f, b     | Bit Test f, Skip if Clear    | 1 (2)  | 01            | 10bb | bfff | ffff |          | 3     |

| BTFSS                       | f, b     | Bit Test f, Skip if Set      | 1 (2)  | 01            | 11bb | bfff | ffff |          | 3     |

| LITERAL                     | AND CO   | NTROL OPERATIONS             |        |               |      |      |      |          |       |

| ADDLW                       | k        | Add literal and W            | 1      | 11            | 111x | kkkk | kkkk | C,DC,Z   |       |

| ANDLW                       | k        | AND literal with W           | 1      | 11            | 1001 | kkkk | kkkk | Z        |       |

| CALL                        | k        | Call subroutine              | 2      | 10            | 0kkk | kkkk | kkkk |          |       |

| CLRWDT                      | -        | Clear Watchdog Timer         | 1      | 00            | 0000 | 0110 | 0100 | TO,PD    |       |

| GOTO                        | k        | Go to address                | 2      | 10            | 1kkk | kkkk | kkkk |          |       |

| IORLW                       | k        | Inclusive OR literal with W  | 1      | 11            | 1000 | kkkk | kkkk | Z        |       |

| MOVLW                       | k        | Move literal to W            | 1      | 11            | 00xx | kkkk | kkkk |          |       |

| RETFIE                      | -        | Return from interrupt        | 2      | 00            | 0000 | 0000 | 1001 |          |       |

| RETLW                       | k        | Return with literal in W     | 2      | 11            | 01xx | kkkk | kkkk |          |       |

| RETURN                      | -        | Return from Subroutine       | 2      | 00            | 0000 | 0000 | 1000 |          |       |

| SLEEP                       | -        | Go into Standby mode         | 1      | 00            | 0000 | 0110 | 0011 | TO,PD    |       |

| SUBLW                       | k        | Subtract W from literal      | 1      | 11            | 110x | kkkk | kkkk | C,DC,Z   |       |

| XORLW                       | k        | Exclusive OR literal with W  | 1      | 11            | 1010 | kkkk | kkkk | Z        |       |

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**2:** If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| CLRW                                                                               | Clear W                                                                                                                                                                                                                                                                                                                                                                                             | COMF                                                                                          | Complement f                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                            | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                        | Syntax:                                                                                       | [ <i>label</i> ] COMF f,d                                                                                                                                                                                                                                                                           |

| Operands:                                                                          | None                                                                                                                                                                                                                                                                                                                                                                                                | Operands:                                                                                     | $0 \leq f \leq 127$                                                                                                                                                                                                                                                                                 |

| Operation:                                                                         | $00h \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                               |                                                                                               | d ∈ [0,1]                                                                                                                                                                                                                                                                                           |

|                                                                                    | $1 \rightarrow Z$                                                                                                                                                                                                                                                                                                                                                                                   | Operation:                                                                                    | $(\bar{f}) \rightarrow (dest)$                                                                                                                                                                                                                                                                      |

| Status Affected:                                                                   | Z                                                                                                                                                                                                                                                                                                                                                                                                   | Status Affected:                                                                              | Z                                                                                                                                                                                                                                                                                                   |

| Encoding:                                                                          | 00 0001 0000 0011                                                                                                                                                                                                                                                                                                                                                                                   | Encoding:                                                                                     | 00 1001 dfff ffff                                                                                                                                                                                                                                                                                   |

| Description:                                                                       | W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                         | Description:                                                                                  | The contents of register 'f' are<br>complemented. If 'd' is 0, the                                                                                                                                                                                                                                  |

| Words:                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                               | result is stored in W. If 'd' is 1, the result is stored back in register 'f'.                                                                                                                                                                                                                      |

| Cycles:                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                   | Words:                                                                                        | 1                                                                                                                                                                                                                                                                                                   |

| Example                                                                            | CLRW                                                                                                                                                                                                                                                                                                                                                                                                | Cycles:                                                                                       | 1                                                                                                                                                                                                                                                                                                   |

|                                                                                    | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                  | Example                                                                                       | COMF REG1,0                                                                                                                                                                                                                                                                                         |

|                                                                                    | W = 0x5A<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                       | Example                                                                                       | Before Instruction                                                                                                                                                                                                                                                                                  |

|                                                                                    | W = 0x00 $Z = 1$                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                               | REG1 = 0x13<br>After Instruction<br>REG1 = 0x13<br>W = 0xEC                                                                                                                                                                                                                                         |

| CLRWDT                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                                                                                                                                                                                                                                                                                     |

| Syntax:                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                               |                                                                                                                                                                                                                                                                                                     |

| Cyntax.                                                                            | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                      | DECF                                                                                          | Decrement f                                                                                                                                                                                                                                                                                         |

| Operands:                                                                          | None                                                                                                                                                                                                                                                                                                                                                                                                | DECF<br>Syntax:                                                                               | Decrement f                                                                                                                                                                                                                                                                                         |

|                                                                                    | None $00h \rightarrow WDT$                                                                                                                                                                                                                                                                                                                                                                          | Syntax:                                                                                       | <b>Decrement f</b><br>[ <i>label</i> ] DECF f,d<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                      |

| Operands:                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow \underline{WD}T$ prescaler,                                                                                                                                                                                                                                                                                                                         | -                                                                                             | [label] DECF f,d                                                                                                                                                                                                                                                                                    |

| Operands:                                                                          | None $00h \rightarrow WDT$                                                                                                                                                                                                                                                                                                                                                                          | Syntax:                                                                                       | [ <i>label</i> ] DECF f,d<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                                            |

| Operands:                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow \overline{TO}$                                                                                                                                                                                                                                                                                                    | Syntax:<br>Operands:                                                                          | $ \begin{bmatrix} \textit{label} \end{bmatrix} \text{ DECF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] $                                                                                                                                                                                                |

| Operands:<br>Operation:                                                            | None<br>$00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$                                                                                                                                                                                                                                                                    | Syntax:<br>Operands:<br>Operation:                                                            | $\begin{bmatrix} label \end{bmatrix} DECF f,d$<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>$(f) - 1 \rightarrow (dest)$                                                                                                                                                                                |

| Operands:<br>Operation:<br>Status Affected:                                        | None<br>$00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$ $\overline{TO, PD}$                                                                                                                                                                                                                                                | Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                        | [ <i>label</i> ] DECF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | None<br>$00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$ $\overline{TO, PD}$ $00  000  0110  0100$ CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>pres <u>caler</u> of the WDT. STATUS                                                                                                              | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011  dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is                                    |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | None<br>$\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow PD \\ \hline \overline{TO}, \overline{PD} \\ \hline \hline 00 & 0000 & 0110 & 0100 \\ \hline \\ CLRWDT \text{ instruction resets the} \\ Watchdog Timer. It also resets the \\ prescaler of the WDT. STATUS \\ bits TO and PD are set. \\ \hline \end{array}$ | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011 \qquad dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | None<br>$\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \hline \overline{TO}, \overline{PD} \\ \hline \hline 00 & 0000 & 0110 & 0100 \\ \hline \end{array}$ CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. STATUS<br>bits TO and PD are set.<br>1      | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011  dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. 1     |

### 12.2 DC Characteristics: PIC16C62XA-04 (Commercial, Industrial, Extended) PIC16C62XA-20 (Commercial, Industrial, Extended) PIC16LC62XA-04 (Commercial, Industrial, Extended (CONT.)

| PIC16C62XA            |                                 |                                                                                                                                                  | Oper             | ating te        | mpera                 | ature -4<br>-4           | ditions (unless otherwise stated)<br>$40^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and<br>$0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial and<br>$40^{\circ}C \leq TA \leq +125^{\circ}C$ for extended                                                                                           |

|-----------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-----------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIC16LC62XA           |                                 |                                                                                                                                                  |                  |                 |                       | ature -4                 | $\begin{array}{ll} \mbox{ditions (unless otherwise stated)} \\ \mbox{H} 0^{\circ} C &\leq T A \leq +85^{\circ} C \mbox{ for industrial and} \\ \mbox{0}^{\circ} C &\leq T A \leq +70^{\circ} C \mbox{ for commercial and} \\ \mbox{0}^{\circ} C &\leq T A \leq +125^{\circ} C \mbox{ for extended} \end{array}$ |

| Param.<br>No.         | Sym                             | Characteristic                                                                                                                                   | Min              | Тур†            | Max                   | Units                    | Conditions                                                                                                                                                                                                                                                                                                      |

| D022                  | ΔIWDT                           | WDT Current <sup>(5)</sup>                                                                                                                       | —                | 6.0             | 10<br>12              | μA<br>μA                 | VDD = 4.0V<br>(125°C)                                                                                                                                                                                                                                                                                           |

| D022A<br>D023         | $\Delta$ IBOR<br>$\Delta$ ICOMP | Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each<br>Comparator <sup>(5)</sup>                                               | _                | 75<br>30        | 125<br>60             | μA<br>μA                 | BOD enabled, VDD = 5.0V<br>VDD = 4.0V                                                                                                                                                                                                                                                                           |

| D023A                 | $\Delta I V REF$                | VREF Current <sup>(5)</sup>                                                                                                                      | —                | 80              | 135                   | μA                       | VDD = 4.0V                                                                                                                                                                                                                                                                                                      |

| D022<br>D022A<br>D023 | ΔIWDT<br>ΔIBOR<br>ΔICOMP        | WDT Current <sup>(5)</sup><br>Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each<br>Comparator <sup>(5)</sup>                 |                  | 6.0<br>75<br>30 | 10<br>12<br>125<br>60 | μΑ<br>μΑ<br>μΑ           | VDD=4.0V<br>(125°C)<br>BOD enabled, VDD = 5.0V<br>VDD = 4.0V                                                                                                                                                                                                                                                    |

| D023A                 | $\Delta$ IVREF                  | VREF Current <sup>(5)</sup>                                                                                                                      | _                | 80              | 135                   | μA                       | VDD = 4.0V                                                                                                                                                                                                                                                                                                      |

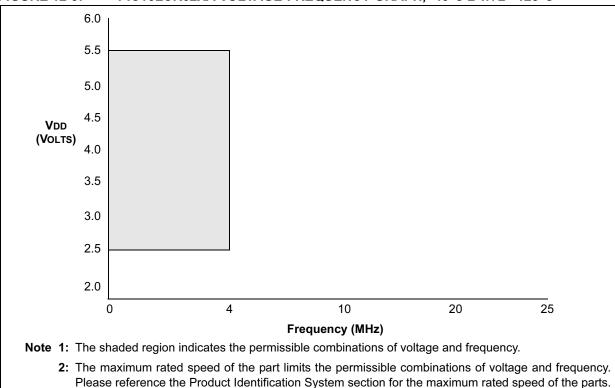

| 1A                    | Fosc                            | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0<br>0<br>0<br>0 |                 | 200<br>4<br>4<br>20   | kHz<br>MHz<br>MHz<br>MHz | All temperatures<br>All temperatures<br>All temperatures<br>All temperatures                                                                                                                                                                                                                                    |

| 1A                    | Fosc                            | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0<br>0<br>0<br>0 |                 | 200<br>4<br>4<br>20   | kHz<br>MHz<br>MHz<br>MHz | All temperatures<br>All temperatures<br>All temperatures<br>All temperatures                                                                                                                                                                                                                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

$\overline{\text{MCLR}}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

## 12.5 DC CHARACTERISTICS: PIC16C620A/C621A/C622A-40<sup>(7)</sup> (Commercial) PIC16CR620A-40<sup>(7)</sup> (Commercial)

| DC CHARACTERISTICS |                                   |                                                                        | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |          |           |            |                                                                            |  |

|--------------------|-----------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|------------|----------------------------------------------------------------------------|--|

| Param<br>No.       | Sym                               | Characteristic                                                         | Min                                                                                                                                | Тур†     | Max       | Units      | Conditions                                                                 |  |

| D001               | Vdd                               | Supply Voltage                                                         | 3.0                                                                                                                                | _        | 5.5       | V          | Fosc = DC to 20 MHz                                                        |  |

| D002               | Vdr                               | RAM Data Retention Voltage <sup>(1)</sup>                              |                                                                                                                                    | 1.5*     |           | V          | Device in SLEEP mode                                                       |  |

| D003               | VPOR                              | VDD start voltage to ensure<br>Power-on Reset                          | —                                                                                                                                  | Vss      | _         | V          | See section on Power-on Reset for details                                  |  |

| D004               | SVDD                              | VDD rise rate to ensure Power-on<br>Reset                              | 0.05<br>*                                                                                                                          | —        | _         | V/ms       | See section on Power-on Reset for details                                  |  |

| D005               | VBOR                              | Brown-out Detect Voltage                                               | 3.65                                                                                                                               | 4.0      | 4.35      | V          | BOREN configuration bit is cleared                                         |  |

| D010               | IDD                               | Supply Current <sup>(2,4)</sup>                                        | —                                                                                                                                  | 1.2      | 2.0       | mA         | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT Osc mode, ( <b>Note 4</b> )* |  |

|                    |                                   |                                                                        | —                                                                                                                                  | 0.4      | 1.2       | mA         | Fosc = 4 MHz, VDD = 3.0V, WDT disabled,<br>XT Osc mode, (Note 4)           |  |

|                    |                                   |                                                                        | —                                                                                                                                  | 1.0      | 2.0       | mA         | Fosc = 10 MHz, VDD = 3.0V, WDT disabled,<br>HS Osc mode, ( <b>Note 6</b> ) |  |

|                    |                                   |                                                                        | —                                                                                                                                  | 4.0      | 6.0       | mA         | Fosc = 20 MHz, VDD = 4.5V, WDT disabled,<br>HS Osc mode                    |  |

|                    |                                   |                                                                        | —                                                                                                                                  | 4.0      | 7.0       | mA         | Fosc = 20 MHz, VDD = 5.5V, WDT disabled*,<br>HS Osc mode                   |  |

|                    |                                   |                                                                        | —                                                                                                                                  | 35       | 70        | μA         | Fosc = 32 kHz, VDD = 3.0V, WDT disabled,<br>LP Osc mode                    |  |

| D020               | IPD                               | Power Down Current <sup>(3)</sup>                                      | _                                                                                                                                  | _        | 2.2       | μA         | VDD = 3.0V                                                                 |  |

|                    |                                   |                                                                        | —                                                                                                                                  | —        | 5.0       | μA         | VDD = 4.5V*                                                                |  |

|                    |                                   |                                                                        | —                                                                                                                                  | —        | 9.0       | μA         | VDD = 5.5V                                                                 |  |

|                    |                                   | (5)                                                                    | —                                                                                                                                  | —        | 15        | μA         | VDD = 5.5V Extended                                                        |  |

| D022               | $\Delta$ IWDT                     | WDT Current <sup>(5)</sup>                                             | —                                                                                                                                  | 6.0      | 10        | μA         | VDD = 4.0V                                                                 |  |

| D022A              |                                   | Brown-out Reset Current <sup>(5)</sup>                                 |                                                                                                                                    | 75       | 12        | μA         | $(125^{\circ}C)$                                                           |  |

| D022A<br>D023      | $\Delta$ IBOR<br>$\Delta$ ICOMP   | Comparator Current for each                                            | _                                                                                                                                  | 75<br>30 | 125<br>60 | μA<br>μA   | BOD enabled, VDD = 5.0V<br>VDD = 4.0V                                      |  |

|                    |                                   | Comparator <sup>(5)</sup>                                              |                                                                                                                                    |          |           |            |                                                                            |  |