Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 80 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621-20-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

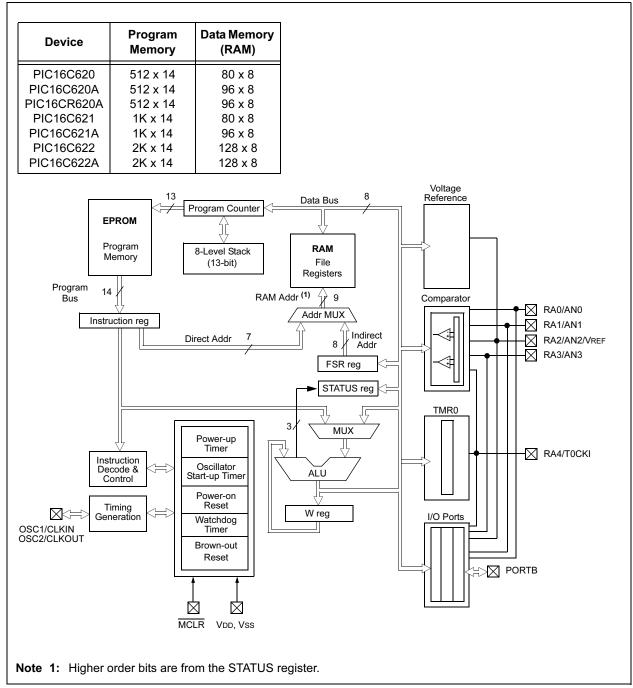

#### FIGURE 3-1: BLOCK DIAGRAM

### 4.2 Data Memory Organization

The data memory (Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7) is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20-7Fh (Bank0) on the PIC16C620A/CR620A/621A and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16C622 and PIC16C622A are General Purpose Registers implemented as static RAM. Some Special Purpose Registers are mapped in Bank 1.

Addresses F0h-FFh of bank1 are implemented as common ram and mapped back to addresses 70h-7Fh in bank0 on the PIC16C620A/621A/622A/CR620A.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 80 x 8 in the PIC16C620/621, 96 x 8 in the PIC16C620A/621A/CR620A and 128 x 8 in the PIC16C622(A). Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

# FIGURE 4-6: DATA MEMORY MAP FOR THE PIC16C620A/CR620A/621A

|                 | 11010002                       |                     | - 17 (          |

|-----------------|--------------------------------|---------------------|-----------------|

| File<br>Address | 3                              |                     | File<br>Address |

| 00h             | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup> | 80h             |

| 01h             | TMR0                           | OPTION              | 81h             |

| 02h             | PCL                            | PCL                 | 82h             |

| 03h             | STATUS                         | STATUS              | 83h             |

| 04h             | FSR                            | FSR                 | 84h             |

| 05h             | PORTA                          | TRISA               | 85h             |

| 06h             | PORTB                          | TRISB               | 86h             |

| 07h             |                                |                     | 87h             |

| 08h             |                                |                     | 88h             |

| 09h             |                                |                     | 89h             |

| 0Ah             | PCLATH                         | PCLATH              | 8Ah             |

| 0Bh             | INTCON                         | INTCON              | 8Bh             |

| 0Ch             | PIR1                           | PIE1                | 8Ch             |

| 0Dh             |                                |                     | 8Dh             |

| 0Eh             |                                | PCON                | 8Eh             |

| 0Fh             |                                |                     | 8Fh             |

| 10h             |                                |                     | 90h             |

| 11h             |                                |                     | 91h             |

| 12h             |                                |                     | 92h             |

| 13h             |                                |                     | 93h             |

| 14h             |                                |                     | 94h             |

| 15h             |                                |                     | 95h             |

| 16h             |                                |                     | 96h             |

| 17h             |                                |                     | 97h             |

| 18h             |                                |                     | 98h             |

| 19h             |                                |                     | 99h             |

| 1Ah             |                                |                     | 9Ah             |

| 1Bh             |                                |                     | 9Bh             |

| 1Ch             |                                |                     | 9Ch             |

| 1Dh             |                                |                     | 9Dh             |

| 1Eh             |                                |                     | 9Eh             |

| 1Fh             | CMCON                          | VRCON               | 9Fh             |

| 20h             | General<br>Purpose<br>Register |                     | A0h             |

| 6Fh             |                                |                     |                 |

| 70h             | General                        |                     | F0h             |

|                 | Purpose<br>Register            | Accesses<br>70h-7Fh |                 |

| 7Fh             | Bank 0                         | Bank 1              | 」 FFh           |

| Unimp           | lemented data mer              | mory locations, rea | ad as '0'.      |

| Note 1:         | Not a physical re              | gister.             |                 |

|                 |                                |                     |                 |

#### FIGURE 4-7: DATA MEMORY MAP FOR THE PIC16C622A

|                                  |                     | C10C022A            |                 |  |  |  |  |

|----------------------------------|---------------------|---------------------|-----------------|--|--|--|--|

| File<br>Address                  | 3                   |                     | File<br>Address |  |  |  |  |

| 00h                              | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |  |  |  |  |

| 01h                              | TMR0                | OPTION              | 81h             |  |  |  |  |

| 02h                              | PCL                 | PCL                 | 82h             |  |  |  |  |

| 03h                              | STATUS              | STATUS              | 83h             |  |  |  |  |

| 04h                              | FSR                 | FSR                 | 84h             |  |  |  |  |

| 05h                              | PORTA               | TRISA               | 85h             |  |  |  |  |

| 06h                              | PORTB               | TRISB               | 86h             |  |  |  |  |

| 07h                              |                     |                     | 87h             |  |  |  |  |

| 08h                              |                     |                     | 88h             |  |  |  |  |

| 09h                              |                     |                     | 89h             |  |  |  |  |

| 0Ah                              | PCLATH              | PCLATH              | 8Ah             |  |  |  |  |

| 0Bh                              | INTCON              | INTCON              | 8Bh             |  |  |  |  |

| 0Ch                              | PIR1                | PIE1                | 8Ch             |  |  |  |  |

| 0Dh                              |                     |                     | 8Dh             |  |  |  |  |

| 0Eh                              |                     | PCON                | 8Eh             |  |  |  |  |

| 0Fh                              |                     |                     | 8Fh             |  |  |  |  |

| 10h                              |                     |                     | 90h             |  |  |  |  |

| 11h                              |                     |                     | 91h             |  |  |  |  |

| 12h                              |                     |                     | 92h             |  |  |  |  |

| 13h                              |                     |                     | 93h             |  |  |  |  |

| 14h                              |                     |                     | 94h             |  |  |  |  |

| 15h                              |                     |                     | 95h             |  |  |  |  |

| 16h                              |                     |                     | 96h             |  |  |  |  |

| 17h                              |                     |                     | 97h             |  |  |  |  |

| 18h                              |                     |                     | 98h             |  |  |  |  |

| 19h                              |                     |                     | 99h             |  |  |  |  |

| 1Ah                              |                     |                     | 9Ah             |  |  |  |  |

| 1Bh                              |                     |                     | 9Bh             |  |  |  |  |

| 1Ch                              |                     |                     | 9Ch             |  |  |  |  |

| 1Dh                              |                     |                     | 9Dh             |  |  |  |  |

| 1Eh                              |                     |                     | 9Eh             |  |  |  |  |

| 1Fh                              | CMCON               | VRCON               | 9Fh             |  |  |  |  |

| 20h                              |                     |                     | A0h             |  |  |  |  |

|                                  | General             | General             | Aon             |  |  |  |  |

|                                  | Purpose<br>Register | Purpose<br>Register |                 |  |  |  |  |

|                                  | rtegister           | rtegister           | BFh             |  |  |  |  |

|                                  |                     |                     | C0h             |  |  |  |  |

| 0.51                             |                     |                     |                 |  |  |  |  |

| 6Fh                              | 0                   |                     | F0h             |  |  |  |  |

| 70h                              | General<br>Purpose  | Accesses            |                 |  |  |  |  |

| 754                              | Register            | 70h-7Fh             | FFh             |  |  |  |  |

| 7Fh                              | Bank 0              | Bank 1              | → FF11          |  |  |  |  |

|                                  |                     |                     |                 |  |  |  |  |

| Unimp                            | plemented data me   | mory locations, re  | ad as '0'.      |  |  |  |  |

| Note 1: Not a physical register. |                     |                     |                 |  |  |  |  |

#### **OPTION Register** 4.2.2.2

The OPTION register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | TMR0, assign the prescaler to the WDT     |  |  |  |  |  |  |  |

|       | (PSA = 1).                                |  |  |  |  |  |  |  |

|         | R/W-1                    | R/W-1                          | R/W-1                         | R/W-1                        | R/W-1         | R/W-1 | R/W-1 | R/W-1 |

|---------|--------------------------|--------------------------------|-------------------------------|------------------------------|---------------|-------|-------|-------|

|         | RBPU                     | INTEDG                         | TOCS                          | TOSE                         | PSA           | PS2   | PS1   | PS0   |

|         | bit 7                    |                                |                               |                              |               | •     |       | bit 0 |

| bit 7   | RBPU: PO                 | RTB Pull-u                     | p Enable bi                   | it                           |               |       |       |       |

|         |                          | 3 pull-ups ai<br>3 pull-ups ai |                               | y individual                 | port latch va | alues |       |       |

| bit 6   | INTEDG: I                | nterrupt Edg                   | e Select bit                  | -                            |               |       |       |       |

|         |                          |                                | edge of RB0<br>edge of RB0    |                              |               |       |       |       |

| bit 5   | TOCS: TMI                | R0 Clock Sc                    | ource Select                  | bit                          |               |       |       |       |

|         |                          | ion on RA4/<br>Il instruction  | T0CKI pin<br>cycle clock      | (CLKOUT)                     |               |       |       |       |

| bit 4   | TOSE: TM                 | R0 Source E                    | Edge Select                   | bit                          |               |       |       |       |

|         |                          |                                |                               | ition on RA4<br>ition on RA4 |               |       |       |       |

| bit 3   | PSA: Pres                | caler Assigr                   | iment bit                     |                              | -             |       |       |       |

|         |                          |                                | ned to the W<br>ned to the Ti | DT<br>mer0 module            | Э             |       |       |       |

| bit 2-0 | <b>PS&lt;2:0&gt;</b> : [ | Prescaler Ra                   | ate Select bi                 | ts                           |               |       |       |       |

|         | E                        | Bit Value T                    | MR0 Rate                      | WDT Rate                     |               |       |       |       |

|         | -                        | 0000001                        | 1:2<br>1:4                    | 1:1<br>1:2                   |               |       |       |       |

|         |                          | 010<br>011                     | 1 : 8<br>1 : 16               | 1:4<br>1:8                   |               |       |       |       |

|         |                          | 100                            | 1:32                          | 1:16                         |               |       |       |       |

|         |                          | 101                            | 1:64                          | 1:32                         |               |       |       |       |

|         |                          | 110                            | 1:128                         | 1:64                         |               |       |       |       |

|         |                          | 111                            | 1:256                         | 1 : 128                      |               |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

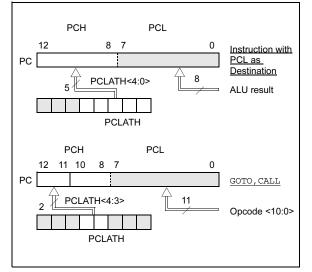

### 4.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any RESET, the PC is cleared. Figure 4-8 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-8: LOADING OF PC IN DIFFERENT SITUATIONS

### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

### 4.3.2 STACK

The PIC16C62X family has an 8-level deep x 13-bit wide hardware stack (Figure 4-2 and Figure 4-3). The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no STATUS bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

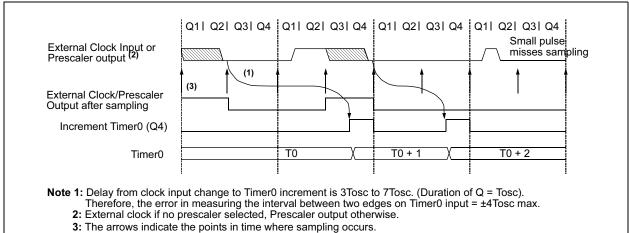

### 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to WDT.)

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

|          |              | ,                                             |

|----------|--------------|-----------------------------------------------|

| 1.BCF    | STATUS, RPO  | ;Skip if already in<br>;Bank 0                |

| 2.CLRWDT |              | ;Clear WDT                                    |

| 3.CLRF   | TMR0         | ;Clear TMR0 & Prescaler                       |

| 4.BSF    | STATUS, RPO  | ;Bank 1                                       |

| 5.MOVLW  | '00101111'b; | ;These 3 lines (5, 6, 7)                      |

| 6.MOVWF  | OPTION       | ;are required only if<br>;desired PS<2:0> are |

| 7.CLRWDT |              | ;000 or 001                                   |

| 8.MOVLW  | '00101xxx'b  | ;Set Postscaler to                            |

| 9.MOVWF  | OPTION       | ;desired WDT rate                             |

| 10.BCF   | STATUS, RPO  | ;Return to Bank 0                             |

|          |              |                                               |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 6-2. This precaution must be taken even if the WDT is disabled.

### EXAMPLE 6-2:

#### CHANGING PRESCALER (WDT→TIMER0)

|        | •           | ,                                        |

|--------|-------------|------------------------------------------|

| CLRWDT |             | ;Clear WDT and                           |

|        |             | ;prescaler                               |

| BSF    | STATUS, RPO |                                          |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new<br>;prescale value and |

|        |             | ;clock source                            |

| MOVWF  | OPTION REG  |                                          |

| BCF    | STATUS, RPO |                                          |

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6       | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|----------|-------------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 r | nodule regi | ster  |        |        |        |        |        | XXXX XXXX       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE      | PEIE        | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | RBPU     | INTEDG      | TOCS  | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _        |             | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

**Note:** Shaded bits are not used by TMR0 module.

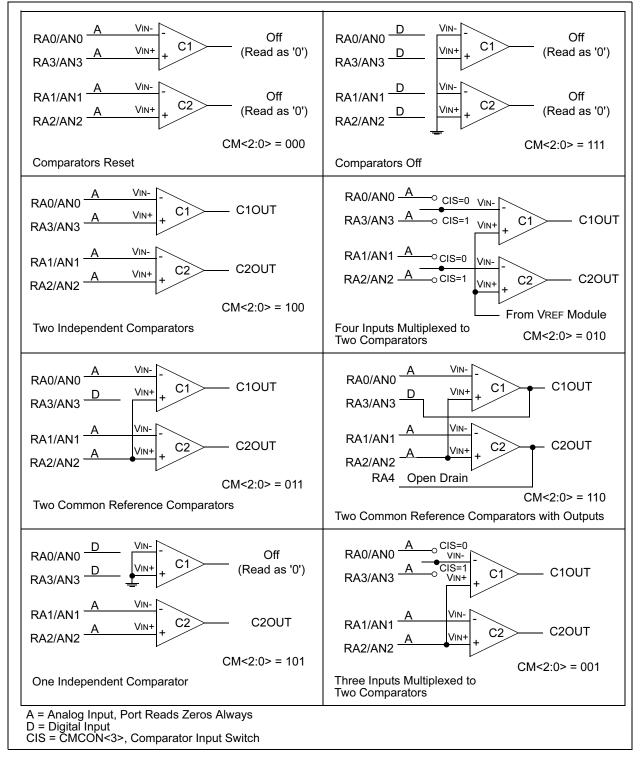

#### 7.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 7-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 12-2.

**Note:** Comparator interrupts should be disabled during a Comparator mode change otherwise a false interrupt may occur.

#### 7.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be RESET by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | If a change in the CMCON register          |

|-------|--------------------------------------------|

|       | (C1OUT or C2OUT) should occur when a       |

|       | read operation is being executed (start of |

|       | the Q2 cycle), then the CMIF (PIR1<6>)     |

|       | interrupt flag may not get set.            |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

# 7.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will

Vdd ∆Vt = 0.6V RIC Rs < 10K Δικ **I**LEAKAGE CPIN VT = 0.6V ±500 nA 5 pF Vss Input Capacitance Legend CPIN = Threshold Voltage Vт = Leakage Current at the pin due to various junctions ILEAKAGE = = Interconnect Resistance RIC Rs = Source Impedance Analog Voltage VA =

FIGURE 7-4: ANALOG INPUT MODEL

wake up the device from SLEEP mode when enabled. While the comparator is powered-up, higher SLEEP currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering SLEEP. If the device wakes up from SLEEP, the contents of the CMCON register are not affected.

#### 7.8 Effects of a RESET

A device RESET forces the CMCON register to its RESET state. This forces the comparator module to be in the comparator RESET mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at RESET time. The comparators will be powered-down during the RESET interval.

#### 7.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 7-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latchup may occur. A maximum source impedance of  $10 \ k\Omega$ is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### 9.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

#### 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

#### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

The Power-up Time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

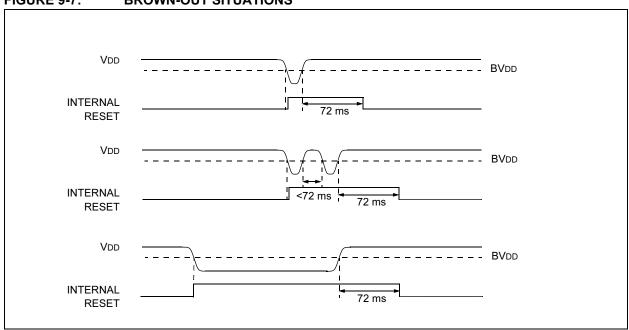

#### 9.4.4 BROWN-OUT RESET (BOR)

The PIC16C62X members have on-chip Brown-out Reset circuitry. A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V refer to VBOR parameter D005 (VBOR) for greater than parameter (TBOR) in Table 12-5. The brown-out situation will RESET the chip. A RESET won't occur if VDD falls below 4.0V for less than parameter (TBOR).

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 9-7 shows typical Brown-out situations.

#### FIGURE 9-7: BROWN-OUT SITUATIONS

#### 9.4.5 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with <u>PWRTE</u> bit erased (<u>PWRT</u> disabled), there will be no time-out at all. Figure 9-8, Figure 9-9 and Figure 9-10 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 9-9). This is useful for testing purposes or to synchronize more than one PIC16C62X device operating in parallel.

Table 9-4 shows the RESET conditions for some special registers, while Table 9-5 shows the RESET conditions for all the registers.

#### 9.4.6 POWER CONTROL (PCON)/ STATUS REGISTER

The power control/STATUS register, PCON (address 8Eh), has two bits.

Bit0 is  $\overline{\text{BOR}}$  (Brown-out).  $\overline{\text{BOR}}$  is unknown on Poweron Reset. It must then be set by the user and checked on subsequent RESETS to see if  $\overline{\text{BOR}} = 0$ , indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$  STATUS bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent RESET, if POR is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe              | er-up     | Brown-out Reset   | Wake-up    |  |

|--------------------------|-------------------|-----------|-------------------|------------|--|

|                          | PWRTE = 0         | PWRTE = 1 | Brown-out Reset   | from SLEEP |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc  |  |

| RC                       | 72 ms             | _         | 72 ms             | _          |  |

#### TABLE 9-1: TIME-OUT IN VARIOUS SITUATIONS

| <b>TABLE 9-2</b> : | STATUS/PCON BITS AND THEIR SIGNIFICANCE |

|--------------------|-----------------------------------------|

|--------------------|-----------------------------------------|

| POR | BOR | то | PD |                                    |  |  |  |

|-----|-----|----|----|------------------------------------|--|--|--|

| 0   | Х   | 1  | 1  | Power-on Reset                     |  |  |  |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR          |  |  |  |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR          |  |  |  |

| 1   | 0   | Х  | Х  | Brown-out Reset                    |  |  |  |

| 1   | 1   | 0  | u  | WDT Reset                          |  |  |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                        |  |  |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation |  |  |  |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP            |  |  |  |

Legend: u = unchanged, x = unknown

#### TABLE 9-3: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 83h     | STATUS |       |       |       | TO    | PD    |       |       |       | 0001 1xxx             | 000q quuu                                      |

| 8Eh     | PCON   | _     | _     |       | _     | _     | _     | POR   | BOR   | 0x                    | uq                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

| TABLE 10-2: PIC16C62X INSTRUCTION SET |

|---------------------------------------|

|---------------------------------------|

| Mnemonic,<br>Operands |          | Description                  | Cycles |     | 14-Bit | Opcode | Status | Notes    |       |

|-----------------------|----------|------------------------------|--------|-----|--------|--------|--------|----------|-------|

|                       |          |                              |        | MSb | )      |        | LSb    | Affected |       |

| BYTE-ORI              | IENTED I | FILE REGISTER OPERATIONS     |        |     |        |        |        |          |       |

| ADDWF                 | f, d     | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff   | C,DC,Z   | 1,2   |

| ANDWF                 | f, d     | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff   | Z        | 1,2   |

| CLRF                  | f        | Clear f                      | 1      | 00  | 0001   | lfff   | ffff   | Z        | 2     |

| CLRW                  | -        | Clear W                      | 1      | 00  | 0001   | 0000   | 0011   | Z        |       |

| COMF                  | f, d     | Complement f                 | 1      | 00  | 1001   | dfff   | ffff   | Z        | 1,2   |

| DECF                  | f, d     | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff   | Z        | 1,2   |

| DECFSZ                | f, d     | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff   |          | 1,2,3 |

| INCF                  | f, d     | Increment f                  | 1      | 00  | 1010   | dfff   | ffff   | Z        | 1,2   |

| INCFSZ                | f, d     | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff   |          | 1,2,3 |

| IORWF                 | f, d     | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff   | Z        | 1,2   |

| MOVF                  | f, d     | Move f                       | 1      | 00  | 1000   | dfff   | ffff   | Z        | 1,2   |

| MOVWF                 | f        | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff   |          |       |

| NOP                   | -        | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000   |          |       |

| RLF                   | f, d     | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff   | С        | 1,2   |

| RRF                   | f, d     | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff   | С        | 1,2   |

| SUBWF                 | f, d     | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff   | C,DC,Z   | 1,2   |

| SWAPF                 | f, d     | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff   |          | 1,2   |

| XORWF                 | f, d     | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff   | Z        | 1,2   |

| BIT-ORIEN             | NTED FIL | E REGISTER OPERATIONS        |        |     |        |        |        |          |       |

| BCF                   | f, b     | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff   |          | 1,2   |

| BSF                   | f, b     | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff   |          | 1,2   |

| BTFSC                 | f, b     | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff   |          | 3     |

| BTFSS                 | f, b     | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff   |          | 3     |

| LITERAL /             | AND COI  | NTROL OPERATIONS             |        |     |        |        |        |          |       |

| ADDLW                 | k        | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk   | C,DC,Z   |       |

| ANDLW                 | k        | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk   | Z        |       |

| CALL                  | k        | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk   |          |       |

| CLRWDT                | -        | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100   | TO,PD    |       |

| GOTO                  | k        | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk   |          |       |

| IORLW                 | k        | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk   | Z        |       |

| MOVLW                 | k        | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk   |          |       |

| RETFIE                | -        | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001   |          |       |

| RETLW                 | k        | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk   |          |       |

| RETURN                | -        | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000   |          |       |

| SLEEP                 | -        | Go into Standby mode         | 1      | 00  | 0000   | 0110   | 0011   | TO,PD    |       |

| SUBLW                 | k        | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk   | C,DC,Z   |       |

| XORLW                 | k        | Exclusive OR literal with W  | 1      | 11  | 1010   | kkkk   | kkkk   | Z        |       |

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**2:** If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

## **10.1** Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |  |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |  |  |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |  |  |  |  |

| Encoding:        | 11 111x kkkk kkkk                                                                                                          |  |  |  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and<br>the result is placed in the W<br>register. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                          |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                          |  |  |  |  |  |  |  |  |

| Example          | ADDLW 0x15                                                                                                                 |  |  |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25                                                            |  |  |  |  |  |  |  |  |

| ANDLW            | AND Literal with W                                                                                                     |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                      |  |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |  |  |

| Words:           | 1                                                                                                                      |  |  |  |  |  |

| Cycles:          | 1                                                                                                                      |  |  |  |  |  |

| Example          | ANDLW 0x5F                                                                                                             |  |  |  |  |  |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                        |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                           |  |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                    |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                              |  |  |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (dest)                                                                                                                                                 |  |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |  |  |  |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                              |  |  |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                              |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                              |  |  |  |  |  |  |  |

| Example          | ADDWF FSR, <b>O</b>                                                                                                                                                            |  |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                    |  |  |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |  |  |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                          |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |  |  |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                           |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                           |  |  |  |  |  |  |  |

| Example          | ANDWF FSR, <b>1</b>                                                                                                                                         |  |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                                 |  |  |  |  |  |  |  |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two-cycle<br>instruction. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Example          | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                  | $\begin{array}{rcl} PC &=& address\ here \\ After\ Instruction \\ CNT &=& CNT-1 \\ if\ CNT &=& 0, \\ PC &=& address\ CONTINUE \\ if\ CNT \neq& 0, \\ PC &=& address\ here+1 \end{array}$                                                                                                                                               |  |  |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Encoding:        | 10 1kkk kkkk kkkk                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction.                                                                                                                                      |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Example          | GOTO THERE                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                  | After Instruction<br>PC = Address THERE                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                            |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                              |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                      |  |  |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                           |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                      |  |  |  |  |  |  |  |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                      |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                      |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                      |  |  |  |  |  |  |  |

| Example          | INCF CNT, 1                                                                                                                                                            |  |  |  |  |  |  |  |

|                  | Before Instruction $CNT$ =0xFFZ=0After Instruction $CNT$ =0x00Z=1                                                                                                      |  |  |  |  |  |  |  |

NOTES:

#### 12.4 DC Characteristics: PIC16C62X/C62XA/CR62XA (Commercial, Industrial, Extended) PIC16LC62X/LC62XA/LCR62XA (Commercial, Industrial, Extended)

|                           |     |                                           | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq$ TA $\leq$ +85°C for industrial and $0^{\circ}$ C $\leq$ TA $\leq$ +70°C for commercial and |                    |                  |       |                                                                                                                                                         |  |  |

|---------------------------|-----|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                           |     |                                           |                                                                                                                                                                                                |                    |                  | -40°C | $\leq TA \leq +125^{\circ}C$ for extended                                                                                                               |  |  |

| PIC16LC62X/LC62XA/LCR62XA |     |                                           | Operating temperature -40°0<br>0°0                                                                                                                                                             |                    |                  |       | $\leq$ TA ≤ +85°C for industrial and<br>$\leq$ TA ≤ +70°C for commercial and<br>$\leq$ TA ≤ +70°C for commercial and<br>$\leq$ TA ≤ +125°C for extended |  |  |

| Param.<br>No.             | Sym | Characteristic                            | Min                                                                                                                                                                                            | Min Typ† Max Units |                  |       | Conditions                                                                                                                                              |  |  |

|                           | VIL | Input Low Voltage                         |                                                                                                                                                                                                |                    |                  |       |                                                                                                                                                         |  |  |

|                           |     | I/O ports                                 |                                                                                                                                                                                                |                    |                  |       |                                                                                                                                                         |  |  |

| D030                      |     | with TTL buffer                           | Vss                                                                                                                                                                                            | —                  | 0.8V<br>0.15 Vdd | V     | VDD = 4.5V to 5.5V<br>otherwise                                                                                                                         |  |  |

| D031                      |     | with Schmitt Trigger input                | Vss                                                                                                                                                                                            | —                  | 0.2 VDD          | V     |                                                                                                                                                         |  |  |

| D032                      |     | MCLR, RA4/T0CKI,OSC1 (in RC mode)         | Vss                                                                                                                                                                                            | —                  | 0.2 VDD          | V     | (Note 1)                                                                                                                                                |  |  |

| D033                      |     | OSC1 (in XT and HS)                       | Vss                                                                                                                                                                                            | _                  | 0.3 VDD          | V     |                                                                                                                                                         |  |  |

|                           |     | OSC1 (in LP)                              | Vss                                                                                                                                                                                            | —                  | 0.6 Vdd-<br>1.0  | V     |                                                                                                                                                         |  |  |

|                           | VIL | Input Low Voltage                         |                                                                                                                                                                                                |                    |                  |       |                                                                                                                                                         |  |  |

|                           |     | I/O ports                                 |                                                                                                                                                                                                |                    |                  |       |                                                                                                                                                         |  |  |

| D030                      |     | with TTL buffer                           | Vss                                                                                                                                                                                            | -                  | 0.8V<br>0.15 VDD | V     | VDD = 4.5V to 5.5V<br>otherwise                                                                                                                         |  |  |

| D031                      |     | with Schmitt Trigger input                | Vss                                                                                                                                                                                            | —                  | 0.2 VDD          | V     |                                                                                                                                                         |  |  |

| D032                      |     | MCLR, RA4/T0CKI,OSC1 (in RC mode)         | Vss                                                                                                                                                                                            | —                  | 0.2 VDD          | V     | (Note 1)                                                                                                                                                |  |  |

| D033                      |     | OSC1 (in XT and HS)                       | Vss                                                                                                                                                                                            | —                  | 0.3 VDD          | V     |                                                                                                                                                         |  |  |

|                           |     | OSC1 (in LP)                              | Vss                                                                                                                                                                                            | —                  | 0.6 Vdd-<br>1.0  | V     |                                                                                                                                                         |  |  |

|                           | VIH | Input High Voltage                        |                                                                                                                                                                                                |                    |                  |       |                                                                                                                                                         |  |  |

|                           |     | I/O ports                                 |                                                                                                                                                                                                |                    |                  |       |                                                                                                                                                         |  |  |

| D040                      |     | with TTL buffer                           | 2.0V<br>0.25 VDD<br>+ 0.8V                                                                                                                                                                     | _                  | Vdd<br>Vdd       | V     | V <sub>DD</sub> = 4.5V to 5.5V<br>otherwise                                                                                                             |  |  |

| D041                      |     | with Schmitt Trigger input                | 0.8 Vdd                                                                                                                                                                                        | _                  | VDD              |       |                                                                                                                                                         |  |  |

| D042                      |     | MCLR RA4/T0CKI                            | 0.8 VDD                                                                                                                                                                                        | _                  | VDD              | V     |                                                                                                                                                         |  |  |

| D043<br>D043A             |     | OSC1 (XT, HS and LP)<br>OSC1 (in RC mode) | 0.7 Vdd<br>0.9 Vdd                                                                                                                                                                             | _                  | VDD              | V     | (Note 1)                                                                                                                                                |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16C62X(A) be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

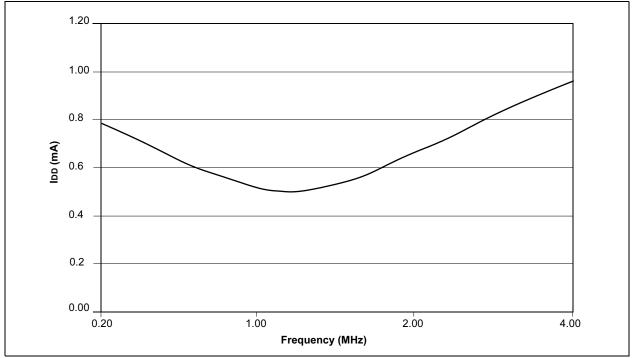

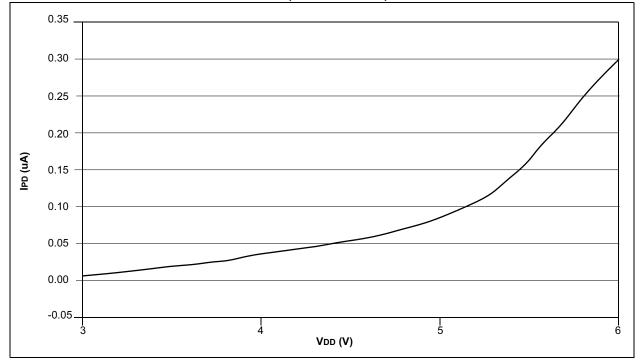

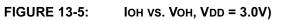

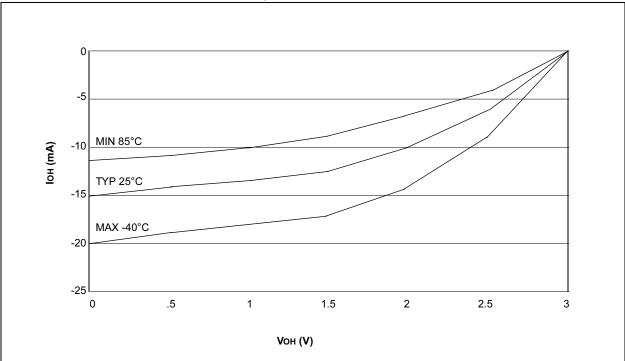

### 13.0 DEVICE CHARACTERIZATION INFORMATION

The graphs and tables provided in this section are for design guidance and are not tested. In some graphs or tables, the data presented is outside specified operating range (e.g., outside specified VDD range). This is for information only and devices will operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution, while "max" or "min" represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation.

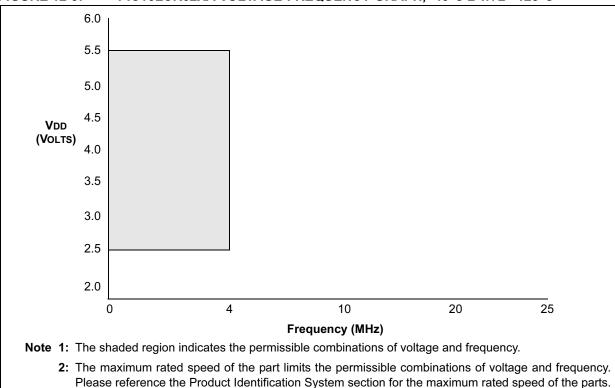

FIGURE 13-1: IDD VS. FREQUENCY (XT MODE, VDD = 5.5V)

FIGURE 13-2: PIC16C622A IPD VS. VDD (WDT DISABLE)

© 2003 Microchip Technology Inc.

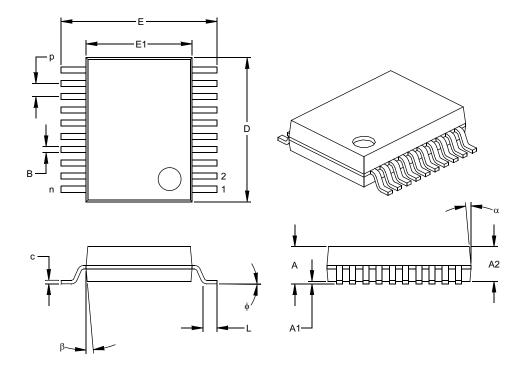

20-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

|                          | Units |      | INCHES* |      |      | MILLIMETERS |        |  |

|--------------------------|-------|------|---------|------|------|-------------|--------|--|

| Dimension Limits         |       | MIN  | NOM     | MAX  | MIN  | NOM         | MAX    |  |

| Number of Pins           | n     |      | 20      |      |      | 20          |        |  |

| Pitch                    | р     |      | .026    |      |      | 0.65        |        |  |

| Overall Height           | Α     | .068 | .073    | .078 | 1.73 | 1.85        | 1.98   |  |

| Molded Package Thickness | A2    | .064 | .068    | .072 | 1.63 | 1.73        | 1.83   |  |

| Standoff §               | A1    | .002 | .006    | .010 | 0.05 | 0.15        | 0.25   |  |

| Overall Width            | E     | .299 | .309    | .322 | 7.59 | 7.85        | 8.18   |  |

| Molded Package Width     | E1    | .201 | .207    | .212 | 5.11 | 5.25        | 5.38   |  |

| Overall Length           | D     | .278 | .284    | .289 | 7.06 | 7.20        | 7.34   |  |