#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 80 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621-20e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

| E PE<br>Global Internables all un<br>isables all in<br>Peripheral<br>nables all p<br>TMR0 Ove<br>nables the T<br>isables the | N-0     R/W-0       EIE     TOIE       rrupt Enable bit       n-masked interrunts       Interrupt Enable       n-masked periphoreripheral interrupt       erflow Interrupt Entrupt       TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | R/W-0<br>RBIE                                                                                                                                                        | R/W-0<br>T0IF                                                                                                                                                                                                                                | R/W-0<br>INTF                                                                                                                                                                                                            | R/W-x<br>RBIF<br>bit 0                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                      | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          | bit 0                                                                                                                                                                                                                                                                                      |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                      | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                      | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| sables all in<br>Peripheral<br>nables all un<br>sables all p<br>TMR0 Ove<br>nables the T<br>isables the                      | nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                                         | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| nables all u<br>sables all p<br>TMR0 Ove<br>nables the<br>sables the                                                         | n-masked periph<br>peripheral interru<br>rflow Interrupt Er<br>TMR0 interrupt                                                                                                                           | neral interrupt<br>pts                                                                                                  | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| sables all p<br>TMR0 Ove<br>nables the<br>sables the                                                                         | peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                                                                                             | pts                                                                                                                     | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| TMR0 Ove<br>nables the<br>sables the                                                                                         | rflow Interrupt Er<br>TMR0 interrupt                                                                                                                                                                    |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| nables the<br>isables the                                                                                                    | TMR0 interrupt                                                                                                                                                                                          | nable bit                                                                                                               |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| sables the                                                                                                                   |                                                                                                                                                                                                         |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | I MRU interrupt                                                                                                                                                                                         |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              |                                                                                                                                                                                                         |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | External Interrupt                                                                                                                                                                                      |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | RB0/INT externa<br>RB0/INT externa                                                                                                                                                                      |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | hange Interrupt E                                                                                                                                                                                       |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | RB port change i                                                                                                                                                                                        |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | RB port change                                                                                                                                                                                          | •                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| TMR0 Ove                                                                                                                     | rflow Interrupt Fl                                                                                                                                                                                      | ag bit                                                                                                                  |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| MR0 registe                                                                                                                  | er has overflowed                                                                                                                                                                                       | d (must be cle                                                                                                          | eared in soft                                                                                                                                                        | ware)                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| MR0 registe                                                                                                                  | er did not overflov                                                                                                                                                                                     | W                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| RB0/INT E                                                                                                                    | xternal Interrupt                                                                                                                                                                                       | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              |                                                                                                                                                                                                         |                                                                                                                         |                                                                                                                                                                      | red in softwa                                                                                                                                                                                                                                | are)                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                            |

| RB Port Cl                                                                                                                   | hange Interrupt F                                                                                                                                                                                       | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| 'hen at leas                                                                                                                 |                                                                                                                                                                                                         | •                                                                                                                       | -                                                                                                                                                                    | (must be cle                                                                                                                                                                                                                                 | ared in softw                                                                                                                                                                                                            | ware)                                                                                                                                                                                                                                                                                      |

|                                                                                                                              | ne RB0/INT<br>ne RB0/INT<br>RB Port C<br>hen at leas                                                                                                                                                    | ne RB0/INT external interrune<br>RB0/INT external interrun<br>RB Port Change Interrupt I<br>hen at least one of the RB< | ne RB0/INT external interrupt did not occ<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins cha<br>one of the RB<7:4> pins have changed s | ne RB0/INT external interrupt occurred (must be clea<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state<br>one of the RB<7:4> pins have changed state | ne RB0/INT external interrupt occurred (must be cleared in softwa<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cle | ne RB0/INT external interrupt occurred (must be cleared in software)<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cleared in softwore)<br>one of the RB<7:4> pins have changed state |

| REGISTER 4-3: | INTCON REGISTER (ADDRESS 0BH OR 8BH) |

|---------------|--------------------------------------|

|---------------|--------------------------------------|

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

NOTES:

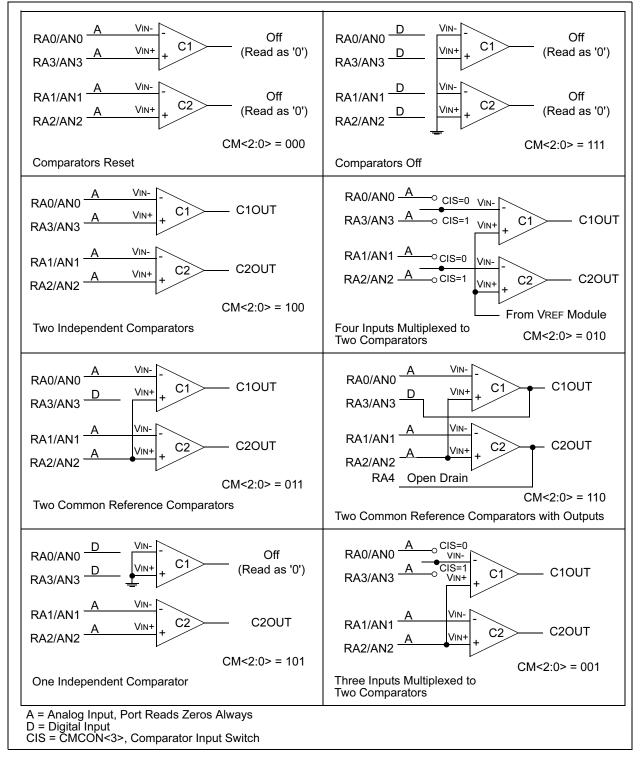

## 7.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 7-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 12-2.

**Note:** Comparator interrupts should be disabled during a Comparator mode change otherwise a false interrupt may occur.

| TABLE 7-1: | REGISTERS ASSOCIATED WITH COMPARATOR MODULE |

|------------|---------------------------------------------|

|------------|---------------------------------------------|

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 1Fh     | CMCON  | C2OUT | C10UT |       | _      | CIS    | CM2    | CM1    | CM0    | 00 0000         | 00 0000                         |

| 9Fh     | VRCON  | VREN  | VROE  | VRR   |        | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 0Bh     | INTCON | GIE   | PEIE  | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 0Ch     | PIR1   | _     | CMIF  | _     | _      | _      | _      | _      | _      | -0              | -0                              |

| 8Ch     | PIE1   | _     | CMIE  | _     | _      | _      | _      | _      | _      | -0              | -0                              |

| 85h     | TRISA  |       |       |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: x = unknown, u = unchanged, - = unimplemented, read as "0"

-

## EXAMPLE 8-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; | 4 Inputs Muxed |

|-------|-------------|---|----------------|

| MOVWF | CMCON       | ; | to 2 comps.    |

| BSF   | STATUS, RPO | ; | go to Bank 1   |

| MOVLW | 0x0F        | ; | RA3-RA0 are    |

| MOVWF | TRISA       | ; | inputs         |

| MOVLW | 0xA6        | ; | enable VREF    |

| MOVWF | VRCON       | ; | low range      |

|       |             | ; | set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; | go to Bank O   |

| CALL  | DELAY10     | ; | 10µs delay     |

## 8.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 8-1) keep VREF from approaching VSS or VDD. The voltage reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the voltage reference can be found in Table 12-2.

# 8.3 Operation During SLEEP

When the device wakes up from SLEEP through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the voltage reference should be disabled.

# 8.4 Effects of a RESET

A device RESET disables the voltage reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

# 8.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the voltage reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the voltage reference output for external connections to VREF. Figure 8-2 shows an example buffering technique.

# FIGURE 8-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

## TABLE 8-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | -      | CIS    | CM2    | CM1    | CM0    | 00 0000         | 00 0000                         |

| 85h     | TRISA | _     |       |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

**Note:** - = Unimplemented, read as "0"

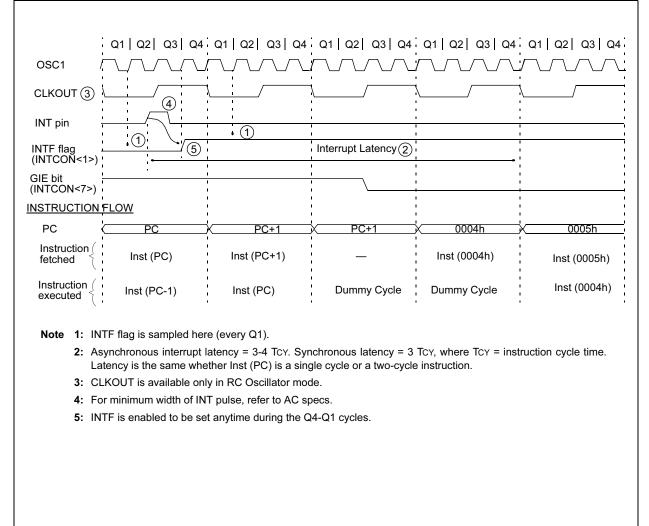

## 9.5.1 RB0/INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered, either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP and Figure 9-18 for timing of wakeup from SLEEP through RB0/INT interrupt.

## 9.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 6.0.

## 9.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

| Note: | If a change on the I/O pin should occur   |

|-------|-------------------------------------------|

|       | when the read operation is being executed |

|       | (start of the Q2 cycle), then the RBIF    |

|       | interrupt flag may not get set.           |

### 9.5.4 COMPARATOR INTERRUPT

See Section 7.6 for complete description of comparator interrupts.

## FIGURE 9-16: INT PIN INTERRUPT TIMING

| BCF              | Bit Clear f                                                         | BTFSC            | Bit Test, Skip if Clear                                                   |

|------------------|---------------------------------------------------------------------|------------------|---------------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      | Syntax:          | [label]BTFSC f,b                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$       |

| Operation:       | $0 \rightarrow (f \le b >)$                                         | Operation:       | skip if (f <b>) = 0</b>                                                   |

| Status Affected: | None                                                                | Status Affected: | None                                                                      |

| Encoding:        | 01 00bb bfff ffff                                                   | Encoding:        | 01 10bb bfff ffff                                                         |

| Description:     | Bit 'b' in register 'f' is cleared.                                 | Description:     | If bit 'b' in register 'f' is '0', then the                               |

| Words:           | 1                                                                   |                  | next instruction is skipped.<br>If bit 'b' is '0', then the next instruc- |

| Cycles:          | 1                                                                   |                  | tion fetched during the current                                           |

| Example          | BCF FLAG_REG, 7                                                     |                  | instruction execution is discarded,                                       |

|                  | Before Instruction<br>FLAG_REG = 0xC7                               |                  | and a NOP is executed instead,<br>making this a two-cycle instruction.    |

|                  | After Instruction                                                   | Words:           | 1                                                                         |

|                  | FLAG_REG = 0x47                                                     | Cycles:          | 1(2)                                                                      |

|                  |                                                                     | Example          | here btfsc <b>FLAG,1</b><br>false goto <b>process co</b>                  |

| BSF              | Bit Set f                                                           |                  | TRUE DE                                                                   |

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |                  | •                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                  | Before Instruction<br>PC = address HERE                                   |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |                  | After Instruction<br>if FLAG<1> = 0.                                      |

| Status Affected: | None                                                                |                  | PC = address TRUE                                                         |

| Encoding:        | 01 01bb bfff ffff                                                   |                  | if FLAG<1>=1,<br>PC = address FALSE                                       |

| Description:     | Bit 'b' in register 'f' is set.                                     |                  | PC = address FALSE                                                        |

| Words:           | 1                                                                   |                  |                                                                           |

| Cycles:          | 1                                                                   |                  |                                                                           |

| Example          | BSF FLAG_REG, 7                                                     |                  |                                                                           |

Before Instruction FLAG\_REG = 0x0A After Instruction

FLAG\_REG = 0x8A

| CLRW                                                                               | Clear W                                                                                                                                                                                                                                                                                                                                                | COMF                                                                                          | Complement f                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                            | [ <i>label</i> ] CLRW                                                                                                                                                                                                                                                                                                                                  | Syntax:                                                                                       | [ <i>label</i> ] COMF f,d                                                                                                                                                                                                                                                                           |

| Operands:                                                                          | None                                                                                                                                                                                                                                                                                                                                                   | Operands:                                                                                     | $0 \leq f \leq 127$                                                                                                                                                                                                                                                                                 |

| Operation:                                                                         | $00h \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                  |                                                                                               | d ∈ [0,1]                                                                                                                                                                                                                                                                                           |

|                                                                                    | $1 \rightarrow Z$                                                                                                                                                                                                                                                                                                                                      | Operation:                                                                                    | $(\overline{f}) \rightarrow (dest)$                                                                                                                                                                                                                                                                 |

| Status Affected:                                                                   | Z                                                                                                                                                                                                                                                                                                                                                      | Status Affected:                                                                              | Z                                                                                                                                                                                                                                                                                                   |

| Encoding:                                                                          | 00 0001 0000 0011                                                                                                                                                                                                                                                                                                                                      | Encoding:                                                                                     | 00 1001 dfff ffff                                                                                                                                                                                                                                                                                   |

| Description:                                                                       | W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                            | Description:                                                                                  | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the                                                                                                                                                                                       |

| Words:                                                                             | 1                                                                                                                                                                                                                                                                                                                                                      |                                                                                               | result is stored back in register 'f'.                                                                                                                                                                                                                                                              |

| Cycles:                                                                            | 1                                                                                                                                                                                                                                                                                                                                                      | Words:                                                                                        | 1                                                                                                                                                                                                                                                                                                   |

| Example                                                                            | CLRW                                                                                                                                                                                                                                                                                                                                                   | Cycles:                                                                                       | 1                                                                                                                                                                                                                                                                                                   |

|                                                                                    | Before Instruction<br>W = 0x5A                                                                                                                                                                                                                                                                                                                         | Example                                                                                       | COMF REG1,0                                                                                                                                                                                                                                                                                         |

|                                                                                    | W = 0x5A<br>After Instruction                                                                                                                                                                                                                                                                                                                          |                                                                                               | Before Instruction                                                                                                                                                                                                                                                                                  |

|                                                                                    | W = 0x00 $Z = 1$                                                                                                                                                                                                                                                                                                                                       |                                                                                               | REG1 = 0x13 After Instruction $REG1 = 0x13$ $W = 0xEC$                                                                                                                                                                                                                                              |

| CLRWDT                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                   |                                                                                               |                                                                                                                                                                                                                                                                                                     |

| Syntax:                                                                            | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                         |                                                                                               |                                                                                                                                                                                                                                                                                                     |

| <b>-j</b>                                                                          |                                                                                                                                                                                                                                                                                                                                                        | DECF                                                                                          | Decrement f                                                                                                                                                                                                                                                                                         |

| Operands:                                                                          | None                                                                                                                                                                                                                                                                                                                                                   | DECF<br>Svntax:                                                                               | Decrement f                                                                                                                                                                                                                                                                                         |

| -                                                                                  | None $00h \rightarrow WDT$                                                                                                                                                                                                                                                                                                                             | Syntax:                                                                                       | [label] DECF f,d                                                                                                                                                                                                                                                                                    |

| Operands:                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow \underline{WD}T$ prescaler,                                                                                                                                                                                                                                                                            | _                                                                                             |                                                                                                                                                                                                                                                                                                     |

| Operands:                                                                          | None $00h \rightarrow WDT$                                                                                                                                                                                                                                                                                                                             | Syntax:                                                                                       | [ <i>label</i> ] DECF f,d<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                                            |

| Operands:                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow TO$                                                                                                                                                                                                                                                                  | Syntax:<br>Operands:                                                                          | [ <i>label</i> ] DECF f,d<br>0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                                                                               |

| Operands:<br>Operation:                                                            | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow \overline{PD}$                                                                                                                                                                                                                      | Syntax:<br>Operands:<br>Operation:                                                            | $\begin{bmatrix} label \end{bmatrix} DECF f,d$<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest)                                                                                                                                                                                |

| Operands:<br>Operation:<br>Status Affected:                                        | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow PD$<br>$\overline{TO}, PD$                                                                                                                                                                                                          | Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                        | [ <i>label</i> ] DECF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow PD$<br>$\overline{TO}, PD$<br>00  0000  0110  0100<br>CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>pres <u>caler</u> of <u>the</u> WDT. STATUS                                                            | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011  dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is                                    |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow TO$<br>$1 \rightarrow PD$<br>TO, PD<br>OUDIMIC OTIO<br>CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. STATUS<br>bits TO and PD are set.                                                                                | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011 \qquad dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | None<br>$\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow PD \\ \hline TO, PD \\ \hline 00 & 0000 & 0110 & 0100 \\ \hline \end{array}$ CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. STATUS<br>bits TO and PD are set.<br>1 | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011  dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. 1     |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                                 |

| Operation:       | $TOS \rightarrow PC$ ,<br>1 $\rightarrow GIE$                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                 |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                    |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top of Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                                    |

| Cycles:          | 2                                                                                                                                                                                                                    |

| Example          | RETFIE                                                                                                                                                                                                               |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                               |

| RETLW            | Return with Literal in W                                                                                                                                                                                                  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                                                                  |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                                       |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                                                              |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                                                         |  |  |  |  |  |  |