Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 80 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621-20i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **EPROM-Based 8-Bit CMOS Microcontrollers**

### Devices included in this data sheet:

Referred to collectively as PIC16C62X.

- PIC16C620 PIC16C620A

- PIC16C621 PIC16C621A

- PIC16C622 PIC16C622A

- PIC16CR620A

### **High Performance RISC CPU:**

- Only 35 instructions to learn

- All single cycle instructions (200 ns), except for program branches which are two-cycle

- Operating speed:

- DC 40 MHz clock input

- DC 100 ns instruction cycle

| Device      | Program<br>Memory | Data<br>Memory |

|-------------|-------------------|----------------|

| PIC16C620   | 512               | 80             |

| PIC16C620A  | 512               | 96             |

| PIC16CR620A | 512               | 96             |

| PIC16C621   | 1K                | 80             |

| PIC16C621A  | 1K                | 96             |

| PIC16C622   | 2K                | 128            |

| PIC16C622A  | 2K                | 128            |

· Interrupt capability

- 16 special function hardware registers

- 8-level deep hardware stack

- Direct, Indirect and Relative addressing modes

### **Peripheral Features:**

- 13 I/O pins with individual direction control

- High current sink/source for direct LED drive

- Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VREF) module

- Programmable input multiplexing from device inputs and internal voltage reference

- Comparator outputs can be output signals

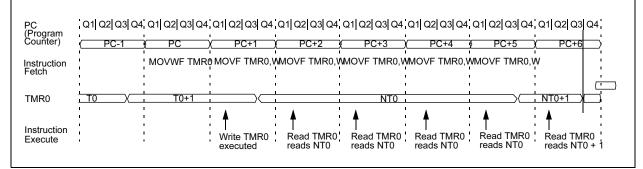

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

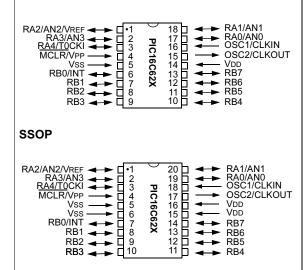

### Pin Diagrams

### PDIP, SOIC, Windowed CERDIP

### **Special Microcontroller Features:**

- · Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- · Programmable code protection

- · Power saving SLEEP mode

- Selectable oscillator options

- Serial in-circuit programming (via two pins)

- Four user programmable ID locations

### **CMOS Technology:**

- Low power, high speed CMOS EPROM technology

- Fully static design

- · Wide operating range

- 2.5V to 5.5V

- Commercial, industrial and extended temperature range

- Low power consumption

- < 2.0 mA @ 5.0V, 4.0 MHz

- 15 μA typical @ 3.0V, 32 kHz

- < 1.0 μA typical standby current @ 3.0V

# FIGURE 4-6: DATA MEMORY MAP FOR THE PIC16C620A/CR620A/621A

|                   | 11010002                       |                     | - 17 (     |  |  |  |  |  |  |

|-------------------|--------------------------------|---------------------|------------|--|--|--|--|--|--|

| File<br>Address   | File File Address Address      |                     |            |  |  |  |  |  |  |

| 00h               | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup> | 80h        |  |  |  |  |  |  |

| 01h               | TMR0                           | OPTION              | 81h        |  |  |  |  |  |  |

| 02h               | PCL                            | PCL                 | 82h        |  |  |  |  |  |  |

| 03h               | STATUS                         | STATUS              | 83h        |  |  |  |  |  |  |

| 04h               | FSR                            | FSR                 | 84h        |  |  |  |  |  |  |

| 05h               | PORTA                          | TRISA               | 85h        |  |  |  |  |  |  |

| 06h               | PORTB                          | TRISB               | 86h        |  |  |  |  |  |  |

| 07h               |                                |                     | 87h        |  |  |  |  |  |  |

| 08h               |                                |                     | 88h        |  |  |  |  |  |  |

| 09h               |                                |                     | 89h        |  |  |  |  |  |  |

| 0Ah               | PCLATH                         | PCLATH              | 8Ah        |  |  |  |  |  |  |

| 0Bh               | INTCON                         | INTCON              | 8Bh        |  |  |  |  |  |  |

| 0Ch               | PIR1                           | PIE1                | 8Ch        |  |  |  |  |  |  |

| 0Dh               |                                |                     | 8Dh        |  |  |  |  |  |  |

| 0Eh               |                                | PCON                | 8Eh        |  |  |  |  |  |  |

| 0Fh               |                                |                     | 8Fh        |  |  |  |  |  |  |

| 10h               |                                |                     | 90h        |  |  |  |  |  |  |

| 11h               |                                |                     | 91h        |  |  |  |  |  |  |

| 12h               |                                |                     | 92h        |  |  |  |  |  |  |

| 13h               |                                |                     | 93h        |  |  |  |  |  |  |

| 14h               |                                |                     | 94h        |  |  |  |  |  |  |

| 15h               |                                |                     | 95h        |  |  |  |  |  |  |

| 16h               |                                |                     | 96h        |  |  |  |  |  |  |

| 17h               |                                |                     | 97h        |  |  |  |  |  |  |

| 18h               |                                |                     | 98h        |  |  |  |  |  |  |

| 19h               |                                |                     | 99h        |  |  |  |  |  |  |

| 1Ah               |                                |                     | 9Ah        |  |  |  |  |  |  |

| 1Bh               |                                |                     | 9Bh        |  |  |  |  |  |  |

| 1Ch               |                                |                     | 9Ch        |  |  |  |  |  |  |

| 1Dh               |                                |                     | 9Dh        |  |  |  |  |  |  |

| 1Eh               |                                |                     | 9Eh        |  |  |  |  |  |  |

| 1Fh               | CMCON                          | VRCON               | 9Fh        |  |  |  |  |  |  |

| 20h               | General<br>Purpose<br>Register |                     | A0h        |  |  |  |  |  |  |

| 6Fh               |                                |                     |            |  |  |  |  |  |  |

| 70h               | General                        |                     | F0h        |  |  |  |  |  |  |

|                   | Purpose<br>Register            | Accesses<br>70h-7Fh |            |  |  |  |  |  |  |

| 7Fh Bank 0 Bank 1 |                                |                     |            |  |  |  |  |  |  |

| Unimp             | lemented data mer              | mory locations, rea | ad as '0'. |  |  |  |  |  |  |

| Note 1:           | Not a physical re              | gister.             |            |  |  |  |  |  |  |

|                   |                                |                     |            |  |  |  |  |  |  |

### FIGURE 4-7: DATA MEMORY MAP FOR THE PIC16C622A

|                                  |                     | C10C022A            |                 |  |  |  |  |  |

|----------------------------------|---------------------|---------------------|-----------------|--|--|--|--|--|

| File<br>Address                  | 3                   |                     | File<br>Address |  |  |  |  |  |

| 00h                              | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |  |  |  |  |  |

| 01h                              | TMR0                | OPTION              | 81h             |  |  |  |  |  |

| 02h                              | PCL                 | PCL                 | 82h             |  |  |  |  |  |

| 03h                              | STATUS              | STATUS              | 83h             |  |  |  |  |  |

| 04h                              | FSR                 | FSR                 | 84h             |  |  |  |  |  |

| 05h                              | PORTA               | TRISA               | 85h             |  |  |  |  |  |

| 06h                              | PORTB               | TRISB               | 86h             |  |  |  |  |  |

| 07h                              |                     |                     | 87h             |  |  |  |  |  |

| 08h                              |                     |                     | 88h             |  |  |  |  |  |

| 09h                              |                     |                     | 89h             |  |  |  |  |  |

| 0Ah                              | PCLATH              | PCLATH              | 8Ah             |  |  |  |  |  |

| 0Bh                              | INTCON              | INTCON              | 8Bh             |  |  |  |  |  |

| 0Ch                              | PIR1                | PIE1                | 8Ch             |  |  |  |  |  |

| 0Dh                              |                     |                     | 8Dh             |  |  |  |  |  |

| 0Eh                              |                     | PCON                | 8Eh             |  |  |  |  |  |

| 0Fh                              |                     |                     | 8Fh             |  |  |  |  |  |

| 10h                              |                     |                     | 90h             |  |  |  |  |  |

| 11h                              |                     |                     | 91h             |  |  |  |  |  |

| 12h                              |                     |                     | 92h             |  |  |  |  |  |

| 13h                              |                     |                     | 93h             |  |  |  |  |  |

| 14h                              |                     |                     | 94h             |  |  |  |  |  |

| 15h                              |                     |                     | 95h             |  |  |  |  |  |

| 16h                              |                     |                     | 96h             |  |  |  |  |  |

| 17h                              |                     |                     | 97h             |  |  |  |  |  |

| 18h                              |                     |                     | 98h             |  |  |  |  |  |

| 19h                              |                     |                     | 99h             |  |  |  |  |  |

| 1Ah                              |                     |                     | 9Ah             |  |  |  |  |  |

| 1Bh                              |                     |                     | 9Bh             |  |  |  |  |  |

| 1Ch                              |                     |                     | 9Ch             |  |  |  |  |  |

| 1Dh                              |                     |                     | 9Dh             |  |  |  |  |  |

| 1Eh                              |                     |                     | 9Eh             |  |  |  |  |  |

| 1Fh                              | CMCON               | VRCON               | 9Fh             |  |  |  |  |  |

| 20h                              |                     |                     | A0h             |  |  |  |  |  |

|                                  | General             | General             | Aon             |  |  |  |  |  |

|                                  | Purpose<br>Register | Purpose<br>Register |                 |  |  |  |  |  |

|                                  | rtegister           | rtegister           | BFh             |  |  |  |  |  |

|                                  |                     |                     | C0h             |  |  |  |  |  |

| 0.51                             |                     |                     |                 |  |  |  |  |  |

| 6Fh                              | 0                   |                     | F0h             |  |  |  |  |  |

| 70h                              | General<br>Purpose  | Accesses            |                 |  |  |  |  |  |

| 754                              | Register            | 70h-7Fh             | FFh             |  |  |  |  |  |

| 7Fh Bank 0 Bank 1                |                     |                     |                 |  |  |  |  |  |

|                                  |                     |                     |                 |  |  |  |  |  |

| Unimp                            | plemented data me   | mory locations, re  | ad as '0'.      |  |  |  |  |  |

| Note 1: Not a physical register. |                     |                     |                 |  |  |  |  |  |

### 5.3 I/O Programming Considerations

### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading the port register reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}\,,\ {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

|                                                       | = =                   |

|-------------------------------------------------------|-----------------------|

| ; Initial PORT settings:                              | PORTB<7:4> Inputs     |

| ;                                                     | PORTB<3:0> Outputs    |

| ; PORTB<7:6> have external ; connected to other circu |                       |

| ;                                                     |                       |

| ;                                                     | PORT latch PORT pins  |

| ;                                                     |                       |

|                                                       | -                     |

|                                                       |                       |

| BCF PORTB, 7                                          | ; 01pp pppp 11pp pppp |

| BCF PORTB, 6                                          | ; 10pp pppp 11pp pppp |

| BSF STATUS, RPO                                       | ;                     |

| BCF TRISB, 7                                          | ;10pp pppp 11pp pppp  |

| BCF TRISB, 6                                          | ;10pp pppp 10pp pppp  |

| ;                                                     |                       |

| ; Note that the user may h                            | nave expected the pin |

| ; values to be 00pp pppp.                             | The 2nd BCF caused    |

| ; RB7 to be latched as the                            | e pin value (High).   |

|                                                       |                       |

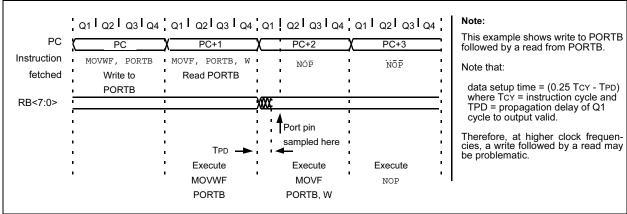

# 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-7). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

### FIGURE 5-7: SUCCESSIVE I/O OPERATION

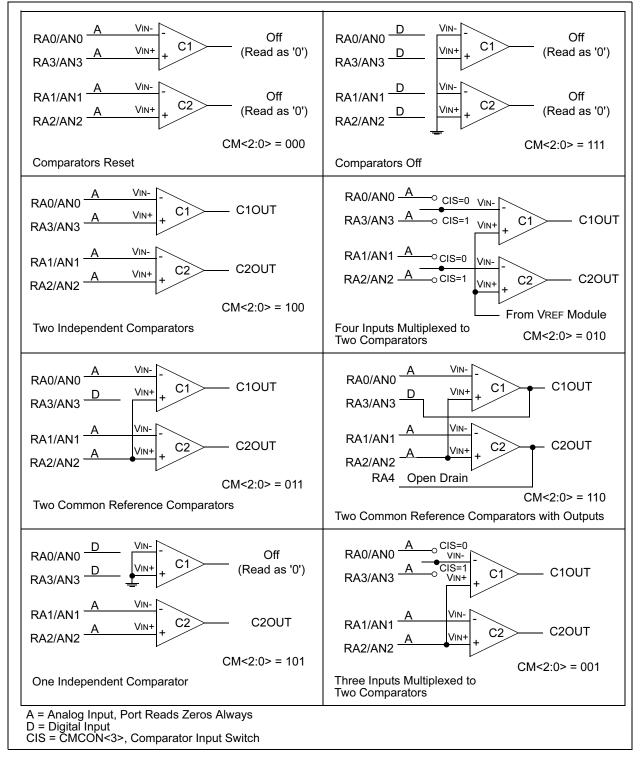

### 7.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 7-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 12-2.

**Note:** Comparator interrupts should be disabled during a Comparator mode change otherwise a false interrupt may occur.

The code example in Example 7-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

### EXAMPLE 7-1: INITIALIZING COMPARATOR MODULE

| MOVLW | 0x03         | ;Init comparator mode             |

|-------|--------------|-----------------------------------|

| MOVWF | CMCON        | ;CM<2:0> = 011                    |

| CLRF  | PORTA        | ;Init PORTA                       |

| BSF   | STATUS, RPO  | ;Select Bank1                     |

| MOVLW | 0x07         | ;Initialize data direction        |

| MOVWF | TRISA        | ;Set RA<2:0> as inputs            |

|       |              | ;RA<4:3> as outputs               |

|       |              | ;TRISA<7:5> always read `0'       |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| CALL  | DELAY 10     | ;10µs delay                       |

| MOVF  | CMCON,F      | ;Read CMCONtoend change condition |

| BCF   | PIR1,CMIF    | ;Clear pending interrupts         |

| BSF   | STATUS, RPO  | ;Select Bank 1                    |

| BSF   | PIE1,CMIE    | ;Enable comparator interrupts     |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| BSF   | INTCON, PEIE | ;Enable peripheral interrupts     |

| BSF   | INTCON, GIE  | ;Global interrupt enable          |

### 7.2 Comparator Operation

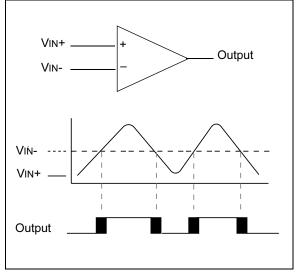

A single comparator is shown in Figure 7-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 7-2 represent the uncertainty due to input offsets and response time.

### 7.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator Operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 7-2).

### 7.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSs and VDD, and can be applied to either pin of the comparator(s).

### 7.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 10, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 7-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

### EXAMPLE 8-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; | 4 Inputs Muxed |

|-------|-------------|---|----------------|

| MOVWF | CMCON       | ; | to 2 comps.    |

| BSF   | STATUS, RPO | ; | go to Bank 1   |

| MOVLW | 0x0F        | ; | RA3-RA0 are    |

| MOVWF | TRISA       | ; | inputs         |

| MOVLW | 0xA6        | ; | enable VREF    |

| MOVWF | VRCON       | ; | low range      |

|       |             | ; | set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; | go to Bank O   |

| CALL  | DELAY10     | ; | 10µs delay     |

### 8.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 8-1) keep VREF from approaching VSS or VDD. The voltage reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the voltage reference can be found in Table 12-2.

### 8.3 Operation During SLEEP

When the device wakes up from SLEEP through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the voltage reference should be disabled.

### 8.4 Effects of a RESET

A device RESET disables the voltage reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

### 8.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the voltage reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the voltage reference output for external connections to VREF. Figure 8-2 shows an example buffering technique.

# FIGURE 8-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

### TABLE 8-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | -      | CIS    | CM2    | CM1    | CM0    | 00 0000         | 00 0000                         |

| 85h     | TRISA | _     |       |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

**Note:** - = Unimplemented, read as "0"

### 9.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

### REGISTER 9-1: CONFIGURATION WORD (ADDRESS 2007h)

| CP1              | CP0 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                            | CP1                                 | CP0 <sup>(2)</sup> | CP1     | CP0 <sup>(2)</sup>    |        | BODEN    | CP1     | CP0 <sup>(2)</sup> | PWRTE   | WDTE     | F0SC1 | F0SC0 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------|---------|-----------------------|--------|----------|---------|--------------------|---------|----------|-------|-------|

| bit 13           | ļ                                                                                                                                                                                                                                                                                                                             | <u> </u>                            | ļļ                 |         | ļ                     |        | <u> </u> | <u></u> | <u>I</u>           | <u></u> | <u> </u> | ļ     | bit 0 |

| bit 13-8<br>5-4: |                                                                                                                                                                                                                                                                                                                               |                                     |                    |         |                       |        |          |         |                    |         |          |       |       |

|                  |                                                                                                                                                                                                                                                                                                                               | 0                                   | m memo<br>-01FFh c |         |                       | on off |          |         |                    |         |          |       |       |

| bit 7            |                                                                                                                                                                                                                                                                                                                               |                                     | nted: Re           | -       |                       |        |          |         |                    |         |          |       |       |

| bit 6            | BOI                                                                                                                                                                                                                                                                                                                           | DEN: Br                             | own-out l          | Reset E | nable bit             | (1)    |          |         |                    |         |          |       |       |

|                  |                                                                                                                                                                                                                                                                                                                               | BOR en<br>BOR dis                   |                    |         |                       |        |          |         |                    |         |          |       |       |

| bit 3            | 1 =                                                                                                                                                                                                                                                                                                                           | <b>RTE</b> : Po<br>PWRT o<br>PWRT e |                    | īmer Er | able bit <sup>(</sup> | 1, 3)  |          |         |                    |         |          |       |       |

| bit 2            | 1 =                                                                                                                                                                                                                                                                                                                           | TE: Wat<br>WDT en<br>WDT dis        |                    | mer Ena | able bit              |        |          |         |                    |         |          |       |       |

| bit 1-0          | <ul> <li>11 = RC oscillator</li> <li>10 = HS oscillator</li> <li>01 = XT oscillator</li> <li>00 = LP oscillator</li> <li>Note 1: Enabling Brown-out Reset automatically enables Power-up Timer (PWRT) regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled anytime Brown-out Detect Reset is</li> </ul> |                                     |                    |         |                       |        |          |         |                    |         |          |       |       |

|                  | <ul> <li>enabled.</li> <li>2: All of the CP&lt;1:0&gt; pairs have to be given the same value to enable the code protection scheme listed.</li> <li>3: Unprogrammed parts default the Power-up Timer disabled.</li> </ul>                                                                                                      |                                     |                    |         |                       |        |          |         |                    |         |          |       |       |

| -                | Legend:<br>R = Readable bit                                                                                                                                                                                                                                                                                                   |                                     |                    |         |                       |        |          |         |                    |         |          |       |       |

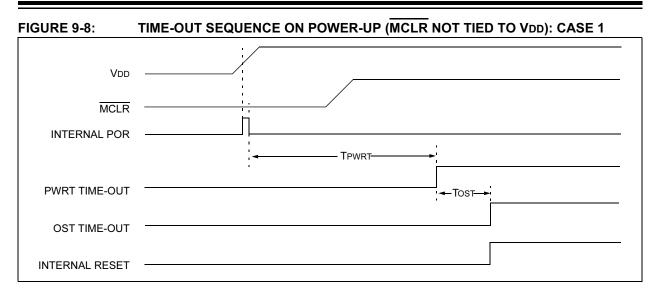

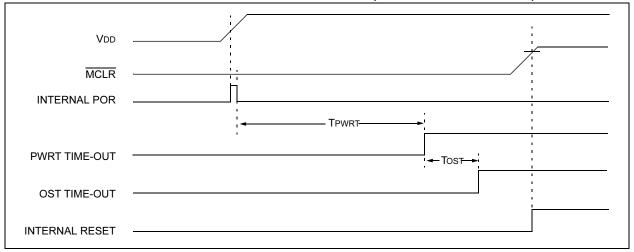

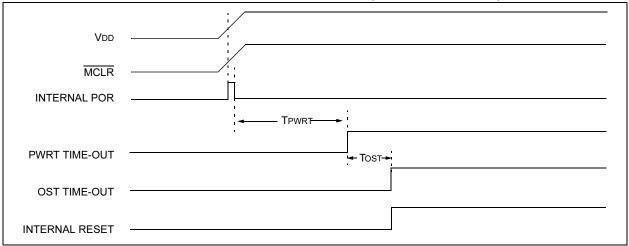

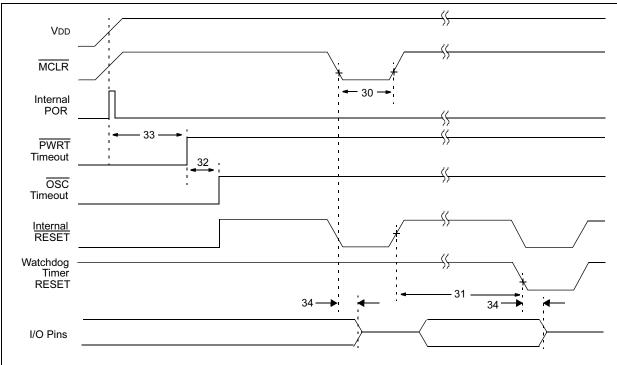

### 9.4.5 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with <u>PWRTE</u> bit erased (<u>PWRT</u> disabled), there will be no time-out at all. Figure 9-8, Figure 9-9 and Figure 9-10 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 9-9). This is useful for testing purposes or to synchronize more than one PIC16C62X device operating in parallel.

Table 9-4 shows the RESET conditions for some special registers, while Table 9-5 shows the RESET conditions for all the registers.

### 9.4.6 POWER CONTROL (PCON)/ STATUS REGISTER

The power control/STATUS register, PCON (address 8Eh), has two bits.

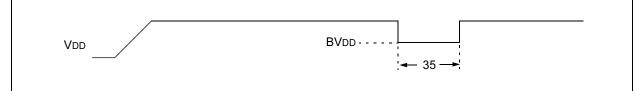

Bit0 is  $\overline{\text{BOR}}$  (Brown-out).  $\overline{\text{BOR}}$  is unknown on Poweron Reset. It must then be set by the user and checked on subsequent RESETS to see if  $\overline{\text{BOR}} = 0$ , indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$  STATUS bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent RESET, if POR is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe              | er-up     | Brown-out Reset   | Wake-up<br>from SLEEP |  |

|--------------------------|-------------------|-----------|-------------------|-----------------------|--|

|                          | PWRTE = 0         | PWRTE = 1 | Brown-out Reset   |                       |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc             |  |

| RC                       | 72 ms             | _         | 72 ms             | _                     |  |

### TABLE 9-1: TIME-OUT IN VARIOUS SITUATIONS

| <b>TABLE 9-2</b> : | STATUS/PCON BITS AND THEIR SIGNIFICANCE |

|--------------------|-----------------------------------------|

|--------------------|-----------------------------------------|

| POR | BOR | то | PD |                                    |

|-----|-----|----|----|------------------------------------|

| 0   | Х   | 1  | 1  | Power-on Reset                     |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR          |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR          |

| 1   | 0   | Х  | Х  | Brown-out Reset                    |

| 1   | 1   | 0  | u  | WDT Reset                          |

| 1   | 1   | 0  | 0  | WDT Wake-up                        |

| 1   | 1   | u  | u  | MCLR Reset during normal operation |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP            |

Legend: u = unchanged, x = unknown

### TABLE 9-3: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 83h     | STATUS |       |       |       | TO    | PD    |       |       |       | 0001 1xxx             | 000q quuu                                      |

| 8Eh     | PCON   | _     | _     |       | _     | _     | _     | POR   | BOR   | 0x                    | uq                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 9-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

### 9.5 Interrupts

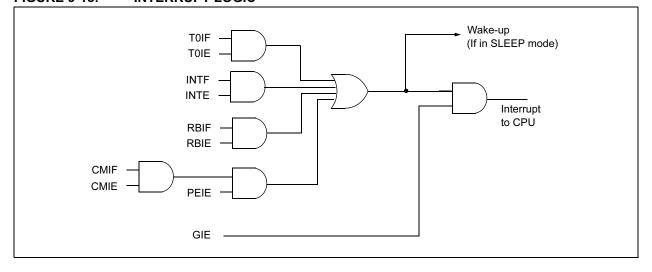

The PIC16C62X has 4 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB<7:4>)

- · Comparator interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which reenable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

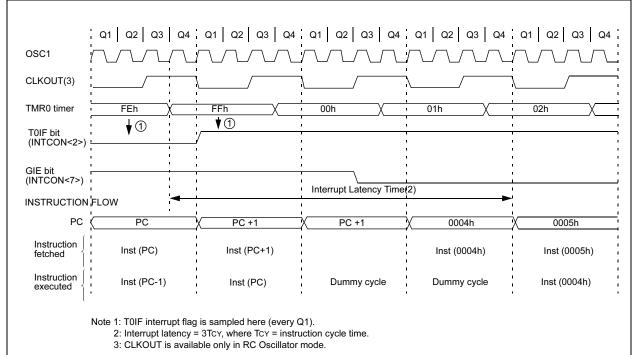

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h.

FIGURE 9-15: INTERRUPT LOGIC

Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/ INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 9-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

| RLF              | Rotate L                                                                        | eft f thro                                               | bugł                    | n Carı                               | ry                             |  |

|------------------|---------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------|--------------------------------------|--------------------------------|--|

| Syntax:          | [ label ]                                                                       | RLF                                                      | f,d                     |                                      |                                |  |

| Operands:        | $0 \le f \le 12$<br>$d \in [0,1]$                                               | 27                                                       |                         |                                      |                                |  |

| Operation:       | See desc                                                                        | cription b                                               | elow                    | /                                    |                                |  |

| Status Affected: | С                                                                               |                                                          |                         |                                      |                                |  |

| Encoding:        | 00                                                                              | 1101                                                     | df                      | ff                                   | ffff                           |  |

| Description:     | The content<br>rotated o<br>the Carry<br>is placed<br>1, the res<br>register 'l | ne bit to<br>Flag. If '<br>in the W<br>sult is sto<br>f. | the l<br>d' is<br>/ reg | left thi<br>0, the<br>ister.<br>back | rough<br>e result<br>If 'd' is |  |

| Words:           |                                                                                 | _                                                        |                         |                                      | -                              |  |

| Cycles:          | 1                                                                               |                                                          |                         |                                      |                                |  |

| Example          | RLF                                                                             | REG1,(                                                   | 1                       |                                      |                                |  |

| zampie           | Before In                                                                       | struction<br>REG1<br>C                                   |                         | 1110<br>0                            | 0110                           |  |

|                  |                                                                                 | REG1<br>W<br>C                                           | =<br>=<br>=             | 1110<br>1100<br>1                    |                                |  |

| RRF              | Rotate R                                                                                                                                                                                                          | ight f th      | nroug       | gh Ca             | irry |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-------------------|------|--|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                         | RRF f          | ,d          |                   |      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 12\\ d\in [0,1] \end{array}$                                                                                                                                                        | 27             |             |                   |      |  |  |  |  |

| Operation:       | See desc                                                                                                                                                                                                          | ription b      | below       | '                 |      |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |                |             |                   |      |  |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                                | 1100           | df          | ff                | ffff |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |                |             |                   |      |  |  |  |  |

|                  | C Register f                                                                                                                                                                                                      |                |             |                   |      |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                 |                |             |                   |      |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                 |                |             |                   |      |  |  |  |  |

| Example          | RRF <b>REG1</b> ,<br>0                                                                                                                                                                                            |                |             |                   |      |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                |                |             |                   |      |  |  |  |  |

|                  | REG1 = 1110 0110<br>C = 0                                                                                                                                                                                         |                |             |                   |      |  |  |  |  |

|                  | After Inst                                                                                                                                                                                                        |                |             |                   |      |  |  |  |  |

|                  |                                                                                                                                                                                                                   | REG1<br>W<br>C | =<br>=<br>= | 1110<br>0111<br>0 |      |  |  |  |  |

SLEEP

| <b>VIII</b>      |                                                                                                                                                            |                                                                                                 |                                                             |                          |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------|--|--|--|--|--|--|

| Syntax:          | [ label<br>]                                                                                                                                               | SLEEF                                                                                           | D                                                           |                          |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                       | None                                                                                            |                                                             |                          |  |  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$ |                                                                                                 |                                                             |                          |  |  |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                     |                                                                                                 |                                                             |                          |  |  |  |  |  |  |

| Encoding:        | 00                                                                                                                                                         | 0000                                                                                            | 0110                                                        | 0011                     |  |  |  |  |  |  |

| Description:     | PD is cle<br>STATUS<br>dog Time<br>cleared.<br>The proc<br>mode wi                                                                                         | ver-down<br>eared. Til<br>bit, TO<br>er and its<br>cessor is<br>th the os<br>. See Se<br>tails. | me-out<br>is set. W<br>s prescal<br>put into s<br>scillator | atch-<br>er are<br>SLEEP |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                          |                                                                                                 |                                                             |                          |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                          |                                                                                                 |                                                             |                          |  |  |  |  |  |  |

| Example:         | SLEEP                                                                                                                                                      |                                                                                                 |                                                             |                          |  |  |  |  |  |  |

NOTES:

### 11.14 PICDEM 1 PICmicro Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include analog input, push button switches and eight LEDs.

### 11.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham

### 11.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessary hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 FLASH microcontrollers.

### 11.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

### 11.18 PICDEM 4 8/14/18-Pin Demonstration Board

The PICDEM 4 can be used to demonstrate the capabilities of the 8-, 14-, and 18-pin PIC16XXXX and PIC18XXXX MCUs, including the PIC16F818/819, PIC16F87/88, PIC16F62XA and the PIC18F1320 family of microcontrollers. PICDEM 4 is intended to showcase the many features of these low pin count parts, including LIN and Motor Control using ECCP. Special provisions are made for low power operation with the supercapacitor circuit, and jumpers allow onboard hardware to be disabled to eliminate current draw in this mode. Included on the demo board are provisions for Crystal, RC or Canned Oscillator modes, a five volt regulator for use with a nine volt wall adapter or battery, DB-9 RS-232 interface, ICD connector for programming via ICSP and development with MPLAB ICD 2, 2x16 liquid crystal display, PCB footprints for H-Bridge motor driver, LIN transceiver and EEPROM. Also included are: header for expansion, eight LEDs, four potentiometers, three push buttons and a prototyping area. Included with the kit is a PIC16F627A and a PIC18F1320. Tutorial firmware is included along with the User's Guide.

### 11.19 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board FLASH memory. A generous prototype area is available for user hardware expansion.

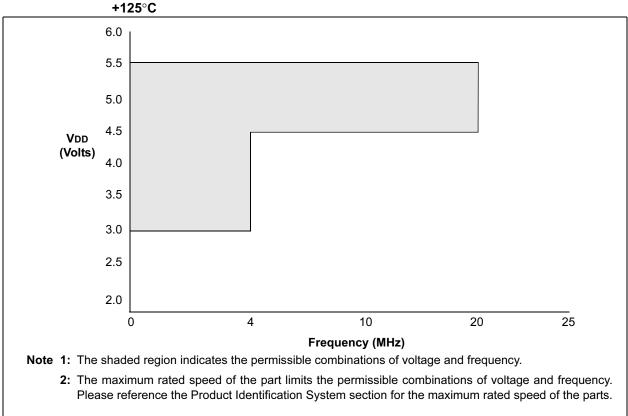

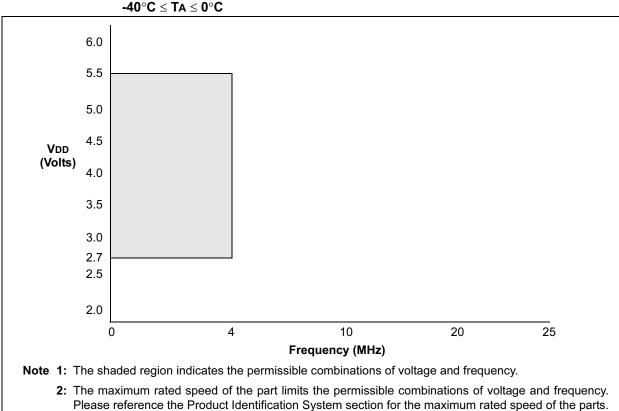

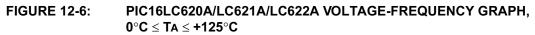

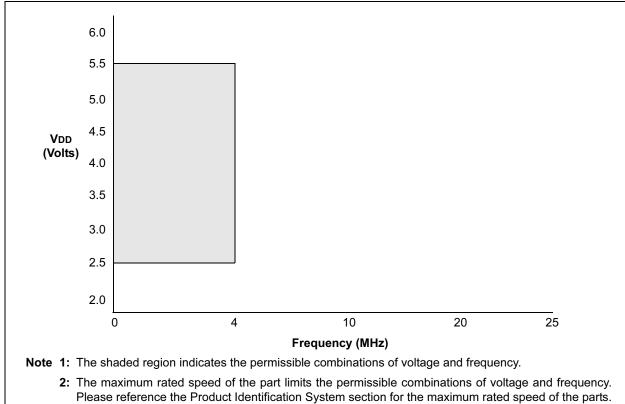

# FIGURE 12-4: PIC16C62XA VOLTAGE-FREQUENCY GRAPH, $-40^{\circ}C \le Ta \le 0^{\circ}C$ , $+70^{\circ}C \le Ta \le +125^{\circ}C$

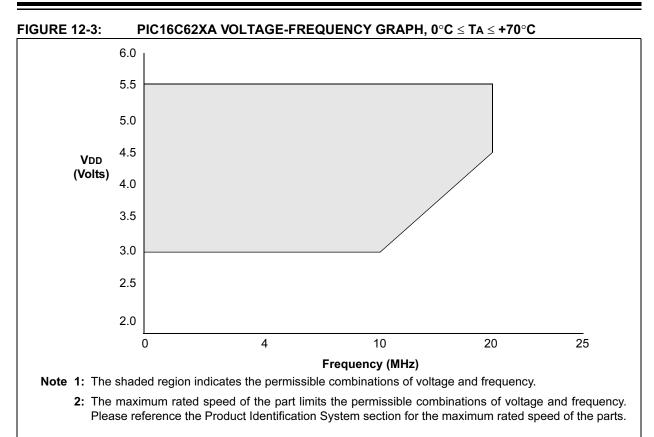

### 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended)

| PIC16C62X       Standard Operating Conditions (unless otherwis<br>Operating temperature -40°C ≤ TA ≤ +85°C for inc<br>0°C ≤ TA ≤ +70°C for co<br>-40°C ≤ TA ≤ +125°C for e         Standard Operating Conditions (unless otherwise)                                                                                                                                                            | dustrial and mmercial and                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                |                                          |

| $\begin{array}{c} \mbox{PIC16LC62X} \\ \mbox{PIC16LC62X} \\ \mbox{Operating temperature} & -40^{\circ}\mbox{C} & \leq \mbox{TA} \leq +85^{\circ}\mbox{C for inc} \\ & 0^{\circ}\mbox{C} & \leq \mbox{TA} \leq +70^{\circ}\mbox{C for co} \\ & -40^{\circ}\mbox{C} & \leq \mbox{TA} \leq +125^{\circ}\mbox{C for e} \\ & \mbox{Operating voltage VDD range is the PIC16C62X range} \end{array}$ | dustrial and<br>mmercial and<br>extended |

| Param.         Sym         Characteristic         Min         Typ†         Max         Units         Conditio           No.                Conditio                                                                                                                                                                                                                                            | ons                                      |

| D001         VDD         Supply Voltage         3.0         —         6.0         V         See Figures 12-1, 12-2, 12-3                                                                                                                                                                                                                                                                       | 3, 12-4, and 12-5                        |

| D001         VDD         Supply Voltage         2.5         —         6.0         V         See Figures 12-1, 12-2, 12-3                                                                                                                                                                                                                                                                       | 3, 12-4, and 12-5                        |

| D002 VDR RAM Data Retention Voltage <sup>(1)</sup> — 1.5* — V Device in SLEEP mode                                                                                                                                                                                                                                                                                                             |                                          |

| D002 VDR RAM Data Retention Voltage <sup>(1)</sup> — 1.5* — V Device in SLEEP mode                                                                                                                                                                                                                                                                                                             |                                          |

| D003         VPOR         VDD start voltage to ensure         —         Vss         —         V         See section on Power-on Report                                                                                                                                                                                                                                                         | eset for details                         |

| D003         VPOR         VDD start voltage to<br>ensure Power-on Reset         —         Vss         —         V         See section on Power-on Reset                                                                                                                                                                                                                                        | eset for details                         |

| D004         SVDD         VDD rise rate to ensure<br>Power-on Reset         0.05*         —         —         V/ms         See section on Power-on Reset                                                                                                                                                                                                                                       | eset for details                         |

| D004     SVDD     VDD rise rate to ensure     0.05*     —     —     V/ms     See section on Power-on Reset                                                                                                                                                                                                                                                                                     | eset for details                         |

| D005 VBOR Brown-out Detect Voltage 3.7 4.0 4.3 V BOREN configuration bit is a                                                                                                                                                                                                                                                                                                                  | cleared                                  |

| D005 VBOR Brown-out Detect Voltage 3.7 4.0 4.3 V BOREN configuration bit is a                                                                                                                                                                                                                                                                                                                  | cleared                                  |

| D010 IDD Supply Current <sup>(2)</sup> - 1.8 3.3 mA Fosc = 4 MHz, VDD = 5.5V, mode, (Note 4)*                                                                                                                                                                                                                                                                                                  |                                          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                        | WD1 disabled, LP                         |

| 9.0 20 mA Fosc = 20 MHz, VDD = 5.5V mode                                                                                                                                                                                                                                                                                                                                                       | , WDT disabled, HS                       |

| D010 IDD Supply Current <sup>(2)</sup> $-$ 1.4 2.5 mA Fosc = 2.0 MHz, VDD = 3.0 V mode (Note 4)                                                                                                                                                                                                                                                                                                | /, WDT disabled, XT                      |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                        | WDT disabled, LP                         |

| D020 IPD Power-down Current <sup>(3)</sup> — 1.0 2.5 $\mu$ A VDD=4.0V, WDT disabled (125°C)                                                                                                                                                                                                                                                                                                    |                                          |

| D020 IPD Power-down Current <sup>(3)</sup> — 0.7 2 $\mu$ A VDD=3.0V, WDT disabled                                                                                                                                                                                                                                                                                                              |                                          |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

$\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

### 12.5 DC CHARACTERISTICS: PIC16C620A/C621A/C622A-40<sup>(7)</sup> (Commercial) PIC16CR620A-40<sup>(7)</sup> (Commercial)

| DC CHARACTERISTICS |                    |                                                                       |           | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |           |          |                                                                            |  |  |  |

|--------------------|--------------------|-----------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|----------------------------------------------------------------------------|--|--|--|

| Param<br>No.       | Sym                | Characteristic                                                        | Min       | Тур†                                                                                                                               | Max       | Units    | Conditions                                                                 |  |  |  |

| D001               | Vdd                | Supply Voltage                                                        | 3.0       | _                                                                                                                                  | 5.5       | V        | Fosc = DC to 20 MHz                                                        |  |  |  |

| D002               | Vdr                | RAM Data Retention Voltage <sup>(1)</sup>                             |           | 1.5*                                                                                                                               | _         | V        | Device in SLEEP mode                                                       |  |  |  |

| D003               | VPOR               | VDD start voltage to ensure<br>Power-on Reset                         | —         | Vss                                                                                                                                | —         | V        | See section on Power-on Reset for details                                  |  |  |  |

| D004               | SVDD               | VDD rise rate to ensure Power-on<br>Reset                             | 0.05<br>* | —                                                                                                                                  | —         | V/ms     | See section on Power-on Reset for details                                  |  |  |  |

| D005               | VBOR               | Brown-out Detect Voltage                                              | 3.65      | 4.0                                                                                                                                | 4.35      | V        | BOREN configuration bit is cleared                                         |  |  |  |

| D010               | IDD                | Supply Current <sup>(2,4)</sup>                                       | —         | 1.2                                                                                                                                | 2.0       | mA       | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT Osc mode, ( <b>Note 4</b> )* |  |  |  |

|                    |                    |                                                                       | —         | 0.4                                                                                                                                | 1.2       | mA       | Fosc = 4 MHz, VDD = 3.0V, WDT disabled,<br>XT Osc mode, (Note 4)           |  |  |  |

|                    |                    |                                                                       | —         | 1.0                                                                                                                                | 2.0       | mA       | Fosc = 10 MHz, VDD = 3.0V, WDT disabled,<br>HS Osc mode, ( <b>Note 6</b> ) |  |  |  |

|                    |                    |                                                                       | —         | 4.0                                                                                                                                | 6.0       | mA       | Fosc = 20 MHz, VDD = 4.5V, WDT disabled,<br>HS Osc mode                    |  |  |  |

|                    |                    |                                                                       | —         | 4.0                                                                                                                                | 7.0       | mA       | Fosc = 20 MHz, VDD = 5.5V, WDT disabled*,<br>HS Osc mode                   |  |  |  |

|                    |                    |                                                                       | —         | 35                                                                                                                                 | 70        | μA       | Fosc = 32 kHz, VDD = 3.0V, WDT disabled,<br>LP Osc mode                    |  |  |  |

| D020               | IPD                | Power Down Current <sup>(3)</sup>                                     |           | _                                                                                                                                  | 2.2       | μA       | VDD = 3.0V                                                                 |  |  |  |

|                    |                    |                                                                       | —         | —                                                                                                                                  | 5.0       | μA       | VDD = 4.5V*                                                                |  |  |  |

|                    |                    |                                                                       | —         | —                                                                                                                                  | 9.0       | μA       | VDD = 5.5V                                                                 |  |  |  |

|                    |                    |                                                                       | —         | —                                                                                                                                  | 15        | μA       | VDD = 5.5V Extended                                                        |  |  |  |

| D022               | $\Delta$ IWDT      | WDT Current <sup>(5)</sup>                                            |           | 6.0                                                                                                                                | 10        | μA       | VDD = 4.0V                                                                 |  |  |  |

| DOODA              |                    |                                                                       |           | 75                                                                                                                                 | 12        | μA       | ( <u>125</u> °C)                                                           |  |  |  |

| D022A<br>D023      | ∆IBOR<br>∆ICOMP    | Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each |           | 75<br>30                                                                                                                           | 125<br>60 | μA<br>μA | BOD enabled, VDD = 5.0V<br>VDD = 4.0V                                      |  |  |  |

| D023               |                    | Comparator Current for each                                           |           | 30                                                                                                                                 | 00        | μA       | VDD - 4.0V                                                                 |  |  |  |

| D023A              |                    | VREF Current <sup>(5)</sup>                                           |           | 80                                                                                                                                 | 135       | μA       | VDD = 4.0V                                                                 |  |  |  |

|                    | $\Delta$ IEE Write | Operating Current                                                     |           |                                                                                                                                    | 3         | mA       | Vcc = 5.5V, SCL = 400 kHz                                                  |  |  |  |