Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 80 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621-20i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Device Differences**

| Device                     | Voltage Range | Oscillator | Process Technology<br>(Microns) |

|----------------------------|---------------|------------|---------------------------------|

| PIC16C620 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C621 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C622 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C620A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

| PIC16CR620A <sup>(2)</sup> | 2.5 - 5.5     | See Note 1 | 0.7                             |

| PIC16C621A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

| PIC16C622A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

2: For ROM parts, operation from 2.5V - 3.0V will require the PIC16LCR62X parts.

**3:** For OTP parts, operation from 2.5V - 3.0V will require the PIC16LC62X parts.

4: For OTP parts, operations from 2.7V - 3.0V will require the PIC16LC62XA parts.

NOTES:

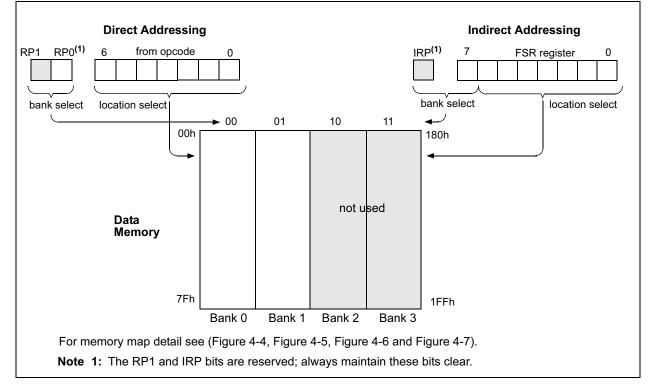

### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-9. However, IRP is not used in the PIC16C62X.

A simple program to clear RAM location 20h-7Fh using indirect addressing is shown in Example 4-1.

| EXAN  | IPLE 4- | 1: INC | DIRECT ADDRESSING    |

|-------|---------|--------|----------------------|

|       | movlw   | 0x20   | ;initialize pointer  |

|       | movwf   | FSR    | ;to RAM              |

| NEXT  | clrf    | INDF   | ;clear INDF register |

|       | incf    | FSR    | ;inc pointer         |

|       | btfss   | FSR,7  | ;all done?           |

|       | goto    | NEXT   | ;no clear next       |

|       |         |        | ;yes continue        |

| CONTI | NUE:    |        |                      |

|       |         |        |                      |

### FIGURE 4-9: DIRECT/INDIRECT ADDRESSING PIC16C62X

### 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading the port register reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}\,,\ {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

|                                                       | = =                   |

|-------------------------------------------------------|-----------------------|

| ; Initial PORT settings:                              | PORTB<7:4> Inputs     |

| ;                                                     | PORTB<3:0> Outputs    |

| ; PORTB<7:6> have external ; connected to other circu |                       |

| ;                                                     |                       |

| ;                                                     | PORT latch PORT pins  |

| ;                                                     |                       |

|                                                       | -                     |

|                                                       |                       |

| BCF PORTB, 7                                          | ; 01pp pppp 11pp pppp |

| BCF PORTB, 6                                          | ; 10pp pppp 11pp pppp |

| BSF STATUS, RPO                                       | ;                     |

| BCF TRISB, 7                                          | ;10pp pppp 11pp pppp  |

| BCF TRISB, 6                                          | ;10pp pppp 10pp pppp  |

| ;                                                     |                       |

| ; Note that the user may h                            | nave expected the pin |

| ; values to be 00pp pppp.                             | The 2nd BCF caused    |

| ; RB7 to be latched as the                            | e pin value (High).   |

|                                                       |                       |

# 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

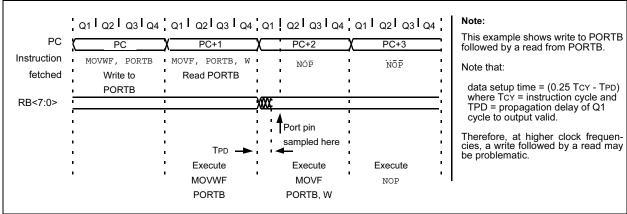

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-7). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 5-7: SUCCESSIVE I/O OPERATION

# 9.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16C62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-Circuit Serial Programming™

The PIC16C62X devices have a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

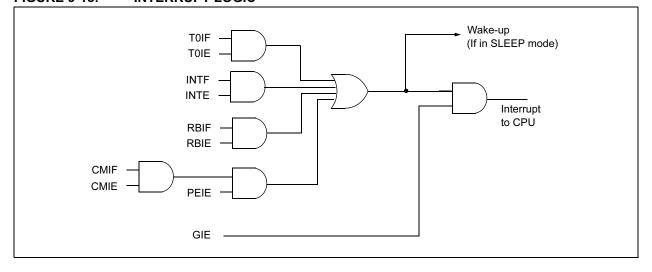

### 9.5 Interrupts

The PIC16C62X has 4 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB<7:4>)

- · Comparator interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which reenable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h.

FIGURE 9-15: INTERRUPT LOGIC

Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/ INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 9-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

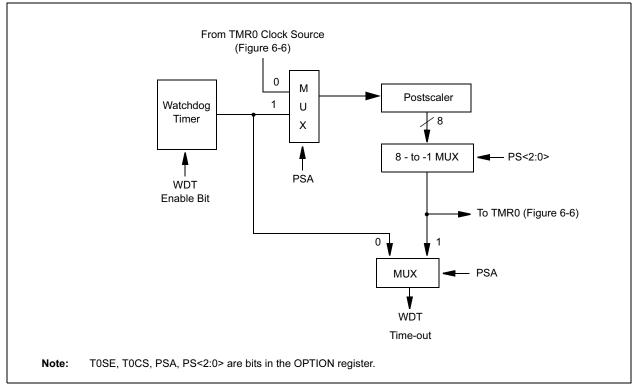

## 9.7 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the CLKIN pin. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET. If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the configuration bit WDTE as clear (Section 9.1).

#### 9.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see

DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

#### 9.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

#### FIGURE 9-17: WATCHDOG TIMER BLOCK DIAGRAM

| TABLE 9-7: SUMMARY OF WATCHDOG TIMER REGISTERS |

|------------------------------------------------|

|------------------------------------------------|

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 2007h   | Config. bits | —     | BODEN  | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 | —                     | —                               |

| 81h     | OPTION       | RBPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111             | 1111 1111                       |

Legend: Shaded cells are not used by the Watchdog Timer.

**Note:** – = Unimplemented location, read as "0"

+ = Reserved for future use

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                 |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                            |

| Operands:        | $0 \le f \le 127$<br>d $\in$ [0,1]                                                                                                                                                                                                                                                                                                     |

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                   |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                                                      |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                      |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                                   |

| Example          | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                     |

|                  | $\begin{array}{rcl} PC &=& address \ {\tt HERE} \\ \mbox{After Instruction} \\ CNT &=& CNT - 1 \\ \mbox{if CNT} &=& 0, \\ PC &=& address \ {\tt CONTINUE} \\ \mbox{if CNT} \neq& 0, \\ PC &=& address \ {\tt HERE} + 1 \\ \end{array}$                                                                                                 |

| GOTO             | Unconditional Branch                                                                                                                                                                                                                                                                                                                   |

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                                                                                                                                                                |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                                                                                                                     |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                   |

| Encoding:        | 10 1kkk kkkk kkkk                                                                                                                                                                                                                                                                                                                      |

| Description:     | GOTO is an unconditional branch.<br>The eleven bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction.                                                                                                                                      |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                      |

| Cycles:          | 2                                                                                                                                                                                                                                                                                                                                      |

| Example          | GOTO THERE                                                                                                                                                                                                                                                                                                                             |

|                  | After Instruction<br>PC = Address THERE                                                                                                                                                                                                                                                                                                |

| INCF             | Increment f                                                                                                                                                            |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                              |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                        |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                           |  |  |  |

| Status Affected: | Z                                                                                                                                                                      |  |  |  |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                      |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |  |  |  |

| Words:           | 1                                                                                                                                                                      |  |  |  |

| Cycles:          | 1                                                                                                                                                                      |  |  |  |

| Example          | INCF CNT, 1                                                                                                                                                            |  |  |  |

|                  | Before Instruction<br>CNT = 0xFF<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                                                  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                    |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                             |

| Status Affected: | Z                                                                                                                                                                                                                                                                                    |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |

| Example          | MOVF FSR, <b>0</b>                                                                                                                                                                                                                                                                   |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |

| MOVWF            | Move W to f                                                                                                                                                                                                                                                                          |

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                    |

| Operation:       | $(W) \rightarrow (f)$                                                                                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                                                                 |

| Encoding:        | 00 0000 1fff ffff                                                                                                                                                                                                                                                                    |

| Description:     | Move data from W register to reg-<br>ister 'f'.                                                                                                                                                                                                                                      |

| Words:           | 1                                                                                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |

| Example          | MOVWF OPTION                                                                                                                                                                                                                                                                         |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F                                                                                                                                                                                                |

|                  | $\begin{array}{rcl} \text{OPTION} &= & 0x4F \\ \text{W} &= & 0x4F \end{array}$                                                                                                                                                                                                       |

| NOP              | No Oper   | ation  |      |      |

|------------------|-----------|--------|------|------|

| Syntax:          | [ label ] | NOP    |      |      |

| Operands:        | None      |        |      |      |

| Operation:       | No opera  | ation  |      |      |

| Status Affected: | None      |        |      |      |

| Encoding:        | 00        | 0000   | 0xx0 | 0000 |

| Description:     | No opera  | ition. |      |      |

| Words:           | 1         |        |      |      |

| Cycles:          | 1         |        |      |      |

| Example          | NOP       |        |      |      |

| OPTION           | Load Op                                                                                     | tion Reg                                                     | gister                                                       |                                     |  |

|------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------|--|

| Syntax:          | [label] OPTION                                                                              |                                                              |                                                              |                                     |  |

| Operands:        | None                                                                                        |                                                              |                                                              |                                     |  |

| Operation:       | $(W) \rightarrow OPTION$                                                                    |                                                              |                                                              |                                     |  |

| Status Affected: | None                                                                                        |                                                              |                                                              |                                     |  |

| Encoding:        | 00                                                                                          | 0000                                                         | 0110                                                         | 0010                                |  |

| Description:     | The control<br>loaded in<br>This instr<br>code con<br>products.<br>able/writa<br>directly a | the OP<br>fuction is<br>apatibility<br>Since C<br>able regis | FION regi<br>supporte<br>with PIC<br>PTION is<br>ster, the u | ster.<br>ed for<br>16C5X<br>a read- |  |

| Words:           | 1                                                                                           |                                                              |                                                              |                                     |  |

| Cycles:          | 1                                                                                           |                                                              |                                                              |                                     |  |

| Example          |                                                                                             |                                                              |                                                              |                                     |  |

|                  | ity with                                                                                    | future P<br>s, do no                                         | vard com<br>PICmicro <sup>©</sup><br>ot use thi              | B                                   |  |

|                  |                                                                                             |                                                              |                                                              |                                     |  |

NOTES:

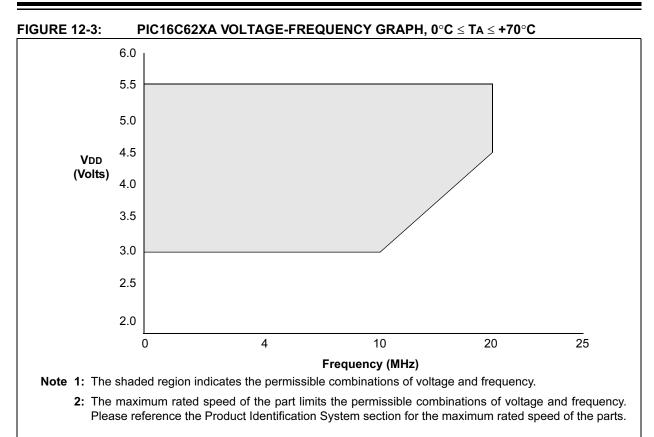

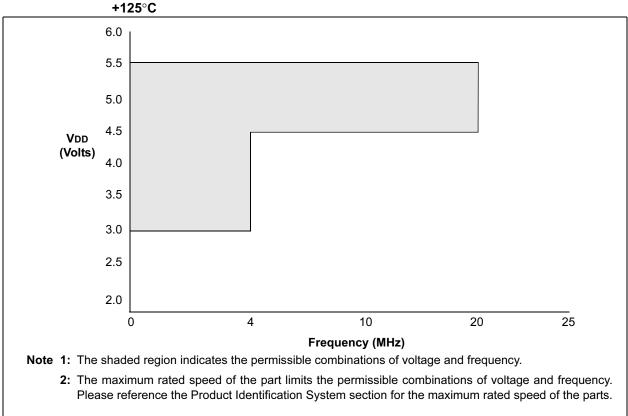

# FIGURE 12-4: PIC16C62XA VOLTAGE-FREQUENCY GRAPH, $-40^{\circ}C \le Ta \le 0^{\circ}C$ , $+70^{\circ}C \le Ta \le +125^{\circ}C$

| PIC16CR62XA-04<br>PIC16CR62XA-20 | $ \begin{array}{ c c c c } \hline \textbf{Standard Operating Conditions (unless otherwise stated)} \\ \hline \textbf{Operating temperature} & -40^{\circ}\text{C} & \leq \text{TA} \leq +85^{\circ}\text{C} \text{ for industrial and} \\ & 0^{\circ}\text{C} & \leq \text{TA} \leq +70^{\circ}\text{C} \text{ for commercial and} \\ & -40^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \end{array} $ |  |  |  |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIC16LCR62XA-04                  | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq TA \leq +85^{\circ}$ C for industrial and $0^{\circ}$ C $\leq TA \leq +70^{\circ}$ C for commercial and $-40^{\circ}$ C $\leq TA \leq +125^{\circ}$ C for extended                                                                                                                                                                               |  |  |  |  |

| Param. Sym Characteristic No.    | Min Typ† Max Units Conditions                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in k $\Omega$ .

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

## 12.5 DC CHARACTERISTICS: PIC16C620A/C621A/C622A-40<sup>(7)</sup> (Commercial) PIC16CR620A-40<sup>(7)</sup> (Commercial)

| DC CHARACTERISTICS |                                   |                                               |           | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |           |          |                                                                            |  |  |  |

|--------------------|-----------------------------------|-----------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|----------------------------------------------------------------------------|--|--|--|

| Param<br>No.       | Sym                               | Characteristic                                |           | Тур†                                                                                                                               | Max       | Units    | Conditions                                                                 |  |  |  |

| D001               | Vdd                               | Supply Voltage                                | 3.0       | _                                                                                                                                  | 5.5       | V        | Fosc = DC to 20 MHz                                                        |  |  |  |

| D002               | Vdr                               | RAM Data Retention Voltage <sup>(1)</sup>     |           | 1.5*                                                                                                                               |           | V        | Device in SLEEP mode                                                       |  |  |  |

| D003               | VPOR                              | VDD start voltage to ensure<br>Power-on Reset | —         | Vss                                                                                                                                | _         | V        | See section on Power-on Reset for details                                  |  |  |  |

| D004               | SVDD                              | VDD rise rate to ensure Power-on<br>Reset     | 0.05<br>* | —                                                                                                                                  | _         | V/ms     | See section on Power-on Reset for details                                  |  |  |  |

| D005               | VBOR                              | Brown-out Detect Voltage                      | 3.65      | 4.0                                                                                                                                | 4.35      | V        | BOREN configuration bit is cleared                                         |  |  |  |

| D010               | IDD                               | Supply Current <sup>(2,4)</sup>               | —         | 1.2                                                                                                                                | 2.0       | mA       | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT Osc mode, ( <b>Note 4</b> )* |  |  |  |

|                    |                                   |                                               | —         | 0.4                                                                                                                                | 1.2       | mA       | Fosc = 4 MHz, VDD = 3.0V, WDT disabled,<br>XT Osc mode, (Note 4)           |  |  |  |

|                    |                                   |                                               | —         | 1.0                                                                                                                                | 2.0       | mA       | Fosc = 10 MHz, VDD = 3.0V, WDT disabled,<br>HS Osc mode, ( <b>Note 6</b> ) |  |  |  |

|                    |                                   |                                               | —         | 4.0                                                                                                                                | 6.0       | mA       | Fosc = 20 MHz, VDD = 4.5V, WDT disabled,<br>HS Osc mode                    |  |  |  |

|                    |                                   |                                               | —         | 4.0                                                                                                                                | 7.0       | mA       | Fosc = 20 MHz, VDD = 5.5V, WDT disabled*,<br>HS Osc mode                   |  |  |  |

|                    |                                   |                                               | —         | 35                                                                                                                                 | 70        | μA       | Fosc = 32 kHz, VDD = 3.0V, WDT disabled,<br>LP Osc mode                    |  |  |  |

| D020               | IPD                               | Power Down Current <sup>(3)</sup>             | _         | _                                                                                                                                  | 2.2       | μA       | VDD = 3.0V                                                                 |  |  |  |

|                    |                                   |                                               | —         | —                                                                                                                                  | 5.0       | μA       | VDD = 4.5V*                                                                |  |  |  |

|                    |                                   |                                               | —         | —                                                                                                                                  | 9.0       | μA       | VDD = 5.5V                                                                 |  |  |  |

|                    |                                   | (5)                                           | —         | —                                                                                                                                  | 15        | μA       | VDD = 5.5V Extended                                                        |  |  |  |

| D022               | $\Delta$ IWDT                     | WDT Current <sup>(5)</sup>                    | —         | 6.0                                                                                                                                | 10        | μA       | VDD = 4.0V                                                                 |  |  |  |

| D022A              |                                   | Brown-out Reset Current <sup>(5)</sup>        |           | 75                                                                                                                                 | 12        | μA       | $(125^{\circ}C)$                                                           |  |  |  |

| D022A<br>D023      | ∆IBOR<br>∆ICOMP                   | Comparator Current for each                   | _         | 75<br>30                                                                                                                           | 125<br>60 | μA<br>μA | BOD enabled, VDD = 5.0V<br>VDD = 4.0V                                      |  |  |  |

|                    |                                   | Comparator <sup>(5)</sup>                     |           |                                                                                                                                    |           |          |                                                                            |  |  |  |

| D023A              | $\Delta$ IVREF                    | VREF Current <sup>(5)</sup>                   | —         | 80                                                                                                                                 | 135       | μA       | VDD = 4.0V                                                                 |  |  |  |

|                    | $\Delta \text{IEE Write}$         | Operating Current                             | —         |                                                                                                                                    | 3         | mA       | Vcc = 5.5V, SCL = 400 kHz                                                  |  |  |  |

|                    | $\Delta \text{IEE} \ \text{Read}$ | Operating Current                             | —         |                                                                                                                                    | 1         | mA       |                                                                            |  |  |  |

|                    | $\Delta IEE$                      | Standby Current                               | —         |                                                                                                                                    | 30        | μA       | Vcc = 3.0V, EE Vdd = Vcc                                                   |  |  |  |

|                    | $\Delta IEE$                      | Standby Current                               | —         |                                                                                                                                    | 100       | μA       | Vcc = 3.0V, EE Vdd = Vcc                                                   |  |  |  |

| 1A                 | Fosc                              | LP Oscillator Operating Frequency             | 0         | —                                                                                                                                  | 200       | kHz      | All temperatures                                                           |  |  |  |

|                    |                                   | RC Oscillator Operating Frequency             | 0         | -                                                                                                                                  | 4         | MHz      | All temperatures                                                           |  |  |  |

|                    |                                   | XT Oscillator Operating Frequency             | 0         | —                                                                                                                                  | 4         | MHz      | All temperatures                                                           |  |  |  |

|                    |                                   | HS Oscillator Operating Frequency             | U         |                                                                                                                                    | 20        | MHz      | All temperatures                                                           |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption. The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD, MCLR = VDD; WDT enabled/disabled as specified.

The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP

mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/ 2REXT (mA) with REXT in kΩ.

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

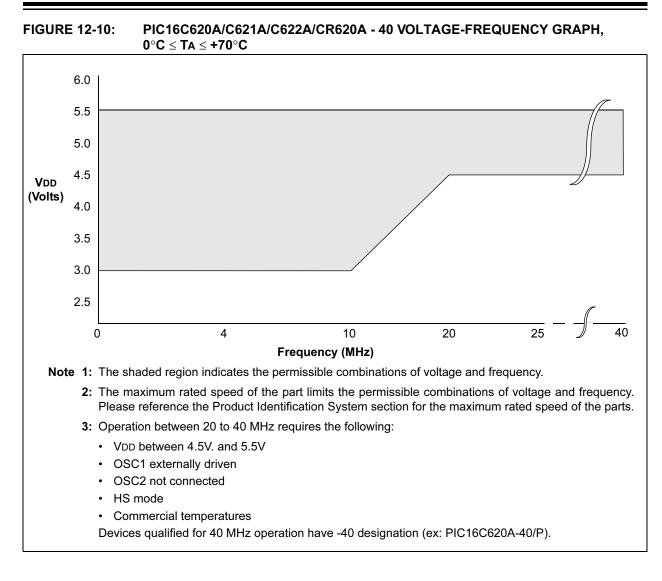

7: See Section 12.1 and Section 12.3 for 16C62X and 16CR62X devices for operation between 20 MHz and 40 MHz for valid modified characteristics.

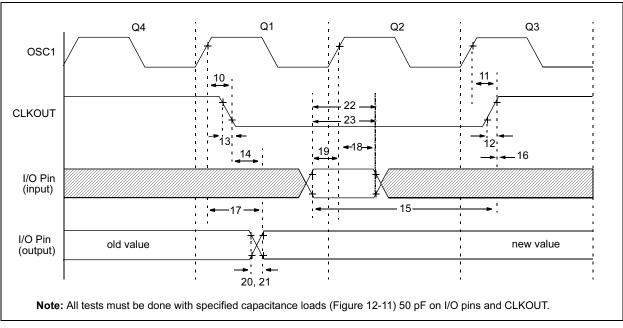

### 12.9 Timing Diagrams and Specifications

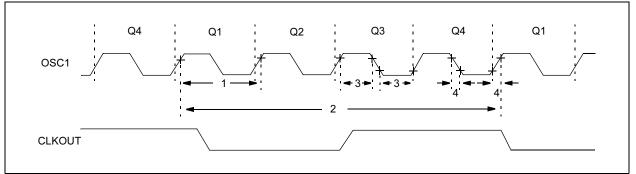

#### FIGURE 12-12: EXTERNAL CLOCK TIMING

#### TABLE 12-3: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym                                             | Characteristic                        | Min  | Тур†   | Max    | Units | Conditions                         |  |

|------------------|-------------------------------------------------|---------------------------------------|------|--------|--------|-------|------------------------------------|--|

| 1A               | 1A Fosc External CLKIN Frequency <sup>(1)</sup> |                                       | DC   | —      | 4      | MHz   | XT and RC Osc mode, VDD=5.0V       |  |

|                  |                                                 |                                       | DC   | _      | 20     | MHz   | HS Osc mode                        |  |

|                  | Oscillator Frequency <sup>(1)</sup>             |                                       | DC   | —      | 200    | kHz   | LP Osc mode                        |  |

|                  |                                                 |                                       | DC   | —      | 4      | MHz   | RC Osc mode, VDD=5.0V              |  |

|                  |                                                 |                                       | 0.1  | —      | 4      | MHz   | XT Osc mode                        |  |

|                  |                                                 |                                       | 1    | —      | 20     | MHz   | HS Osc mode                        |  |

|                  |                                                 |                                       | DC   | —      | 200    | kHz   | LP Osc mode                        |  |

| 1                | Tosc                                            | External CLKIN Period <sup>(1)</sup>  | 250  | —      | _      | ns    | XT and RC Osc mode                 |  |

|                  |                                                 |                                       | 50   | —      | —      | ns    | HS Osc mode                        |  |

|                  |                                                 |                                       | 5    | —      | —      | μs    | LP Osc mode                        |  |

|                  |                                                 | Oscillator Period <sup>(1)</sup>      | 250  | —      | _      | ns    | RC Osc mode                        |  |

|                  |                                                 |                                       | 250  | —      | 10,000 | ns    | XT Osc mode                        |  |

|                  |                                                 |                                       | 50   | —      | 1,000  | ns    | HS Osc mode                        |  |

|                  |                                                 |                                       | 5    | —      | —      | μs    | LP Osc mode                        |  |

| 2                | TCY                                             | Instruction Cycle Time <sup>(1)</sup> | 1.0  | Fosc/4 | DC     | μS    | Tcys=Fosc/4                        |  |

| 3*               | TosL,                                           | ,                                     | 100* | —      | _      | ns    | XT oscillator, Tosc L/H duty cycle |  |

|                  | TosH                                            | Low Time                              | 2*   | —      | —      | μs    | LP oscillator, Tosc L/H duty cycle |  |

|                  |                                                 |                                       | 20*  | _      | —      | ns    | HS oscillator, Tosc L/H duty cycle |  |

| 4*               | TosR,                                           |                                       | 25*  | _      | _      | ns    | XT oscillator                      |  |

|                  | TosF                                            |                                       | 50*  | —      | —      | ns    | LP oscillator                      |  |

|                  |                                                 |                                       | 15*  | —      | —      | ns    | HS oscillator                      |  |

**2:** \* These parameters are characterized but not tested.

3: † Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

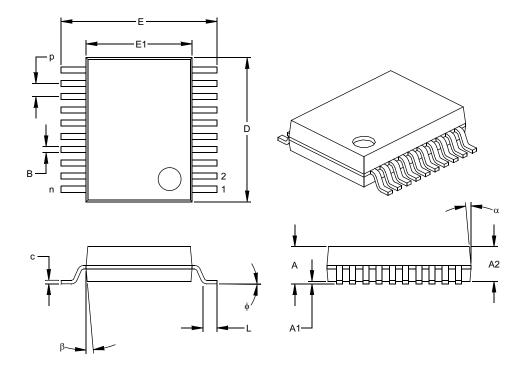

20-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

|                          | Units |      | INCHES* |      | MILLIMETERS |        |        |  |

|--------------------------|-------|------|---------|------|-------------|--------|--------|--|

| Dimensi                  | MIN   | NOM  | MAX     | MIN  | NOM         | MAX    |        |  |

| Number of Pins           | n     |      | 20      |      |             | 20     |        |  |

| Pitch                    | р     |      | .026    |      |             | 0.65   |        |  |

| Overall Height           | Α     | .068 | .073    | .078 | 1.73        | 1.85   | 1.98   |  |

| Molded Package Thickness | A2    | .064 | .068    | .072 | 1.63        | 1.73   | 1.83   |  |

| Standoff §               | A1    | .002 | .006    | .010 | 0.05        | 0.15   | 0.25   |  |

| Overall Width            | Е     | .299 | .309    | .322 | 7.59        | 7.85   | 8.18   |  |

| Molded Package Width     | E1    | .201 | .207    | .212 | 5.11        | 5.25   | 5.38   |  |

| Overall Length           | D     | .278 | .284    | .289 | 7.06        | 7.20   | 7.34   |  |

| Foot Length              | L     | .022 | .030    | .037 | 0.56        | 0.75   | 0.94   |  |

| Lead Thickness           | С     | .004 | .007    | .010 | 0.10        | 0.18   | 0.25   |  |

| Foot Angle               | φ     | 0    | 4       | 8    | 0.00        | 101.60 | 203.20 |  |

| Lead Width               | В     | .010 | .013    | .015 | 0.25        | 0.32   | 0.38   |  |

| Mold Draft Angle Top     | α     | 0    | 5       | 10   | 0           | 5      | 10     |  |

| Mold Draft Angle Bottom  |       | 0    | 5       | 10   | 0           | 5      | 10     |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-150 Drawing No. C04-072

DS30235J-page 116

NOTES: