Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 96 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621a-04-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 PIC16C62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C62X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

## 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the Oscillator modes.

Microchip's PICSTART<sup>®</sup> and PRO MATE<sup>®</sup> programmers both support programming of the PIC16C62X.

Note: Microchip does not recommend code protecting windowed devices.

### 2.2 One-Time-Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

## 2.3 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who chose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices, but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

## 2.4 Serialized Quick-Turnaround-Production<sup>sm</sup> (SQTP<sup>sm</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry-code, password or ID number.

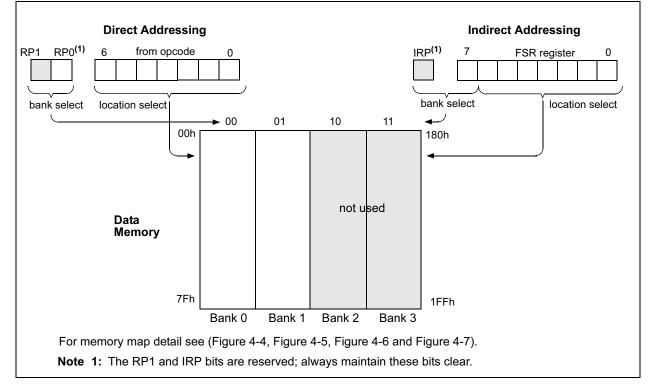

### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-9. However, IRP is not used in the PIC16C62X.

A simple program to clear RAM location 20h-7Fh using indirect addressing is shown in Example 4-1.

| EXAN  | IPLE 4- | 1: INC | DIRECT ADDRESSING    |

|-------|---------|--------|----------------------|

|       | movlw   | 0x20   | ;initialize pointer  |

|       | movwf   | FSR    | ;to RAM              |

| NEXT  | clrf    | INDF   | ;clear INDF register |

|       | incf    | FSR    | ;inc pointer         |

|       | btfss   | FSR,7  | ;all done?           |

|       | goto    | NEXT   | ;no clear next       |

|       |         |        | ;yes continue        |

| CONTI | NUE:    |        |                      |

|       |         |        |                      |

## FIGURE 4-9: DIRECT/INDIRECT ADDRESSING PIC16C62X

# PIC16C62X

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to WDT.)

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

|          |              | ,                                             |

|----------|--------------|-----------------------------------------------|

| 1.BCF    | STATUS, RPO  | ;Skip if already in<br>;Bank 0                |

| 2.CLRWDT |              | ;Clear WDT                                    |

| 3.CLRF   | TMR0         | ;Clear TMR0 & Prescaler                       |

| 4.BSF    | STATUS, RPO  | ;Bank 1                                       |

| 5.MOVLW  | '00101111'b; | ;These 3 lines (5, 6, 7)                      |

| 6.MOVWF  | OPTION       | ;are required only if<br>;desired PS<2:0> are |

| 7.CLRWDT |              | ;000 or 001                                   |

| 8.MOVLW  | '00101xxx'b  | ;Set Postscaler to                            |

| 9.MOVWF  | OPTION       | ;desired WDT rate                             |

| 10.BCF   | STATUS, RPO  | ;Return to Bank 0                             |

|          |              |                                               |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 6-2. This precaution must be taken even if the WDT is disabled.

# EXAMPLE 6-2:

#### CHANGING PRESCALER (WDT→TIMER0)

|        | •           | ,                                        |

|--------|-------------|------------------------------------------|

| CLRWDT |             | ;Clear WDT and                           |

|        |             | ;prescaler                               |

| BSF    | STATUS, RPO |                                          |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new<br>;prescale value and |

|        |             | ;clock source                            |

| MOVWF  | OPTION REG  |                                          |

| BCF    | STATUS, RPO |                                          |

### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6                | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|----------|----------------------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 r | mer0 module register |       |        |        |        |        |        | XXXX XXXX       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE      | PEIE                 | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | RBPU     | INTEDG               | TOCS  | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _        |                      | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

**Note:** Shaded bits are not used by TMR0 module.

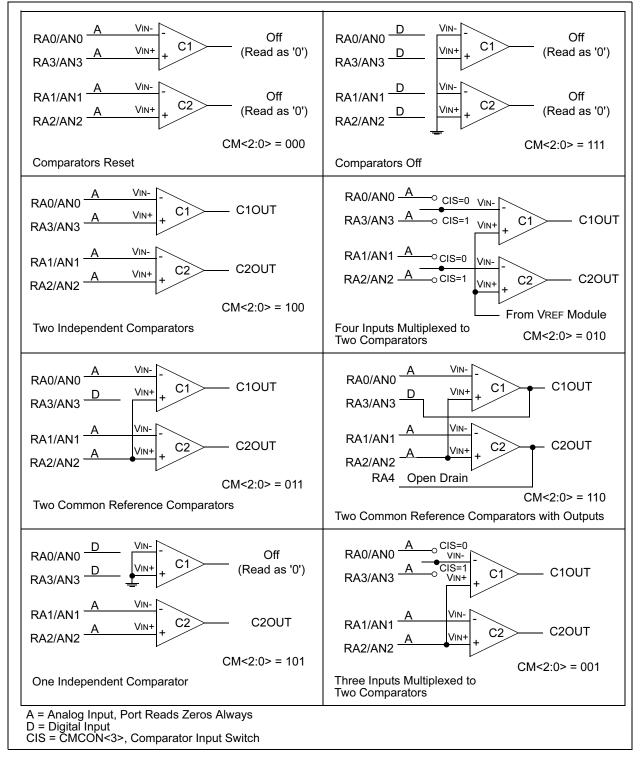

## 7.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 7-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 12-2.

**Note:** Comparator interrupts should be disabled during a Comparator mode change otherwise a false interrupt may occur.

## 7.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise the maximum delay of the comparators should be used (Table 12-2).

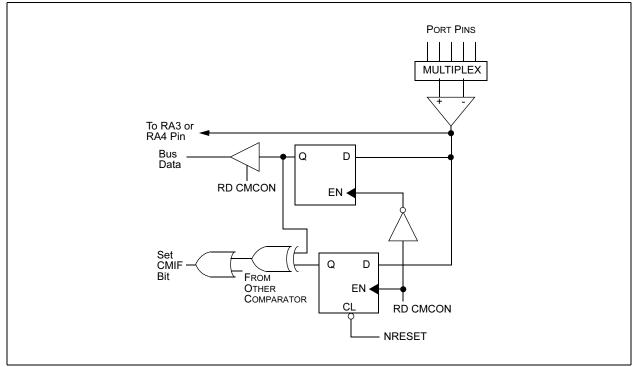

## 7.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 7-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3 and RA4 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

#### FIGURE 7-3: COMPARATOR OUTPUT BLOCK DIAGRAM

## 7.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be RESET by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | If a change in the CMCON register          |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | (C1OUT or C2OUT) should occur when a       |  |  |  |  |  |  |  |  |

|       | read operation is being executed (start of |  |  |  |  |  |  |  |  |

|       | the Q2 cycle), then the CMIF (PIR1<6>)     |  |  |  |  |  |  |  |  |

|       | interrupt flag may not get set.            |  |  |  |  |  |  |  |  |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

# 7.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will

Vdd ∆Vt = 0.6V RIC Rs < 10K Δικ **I**LEAKAGE CPIN VT = 0.6V ±500 nA 5 pF Vss Input Capacitance Legend CPIN = Threshold Voltage Vт = Leakage Current at the pin due to various junctions ILEAKAGE = = Interconnect Resistance RIC Rs = Source Impedance Analog Voltage VA =

FIGURE 7-4: ANALOG INPUT MODEL

wake up the device from SLEEP mode when enabled. While the comparator is powered-up, higher SLEEP currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering SLEEP. If the device wakes up from SLEEP, the contents of the CMCON register are not affected.

## 7.8 Effects of a RESET

A device RESET forces the CMCON register to its RESET state. This forces the comparator module to be in the comparator RESET mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at RESET time. The comparators will be powered-down during the RESET interval.

## 7.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 7-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latchup may occur. A maximum source impedance of  $10 \ k\Omega$ is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

# 9.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16C62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

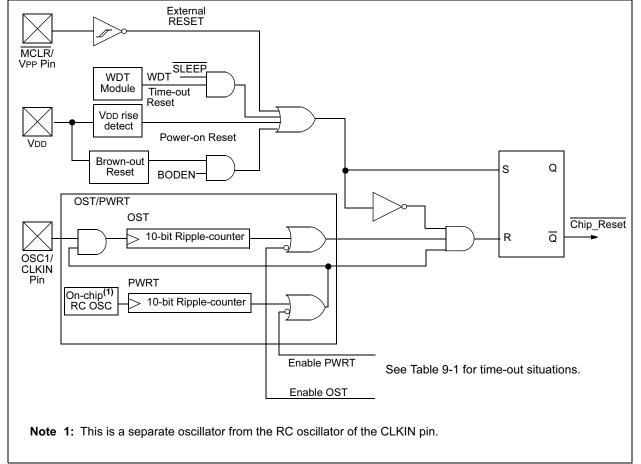

- 8. In-Circuit Serial Programming™

The PIC16C62X devices have a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 9.3 RESET

The PIC16C62X differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) WDT Reset (normal operation)

- e) WDT wake-up (SLEEP)

- f) Brown-out Reset (BOR)

Some registers are not affected in any RESET condition Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset,

MCLR Reset, WDT Reset and MCLR Reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 9-2. These bits are used in software to determine the nature of the RESET. See Table 9-5 for a full description of RESET states of all registers.

A simplified block diagram of the on-chip RESET circuit is shown in Figure 9-6.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 12-5 for pulse width specification.

### TABLE 9-4: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register | Address | Power-on Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during<br/>SLEEP</li> <li>WDT Reset</li> <li>Brown-out Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP<br/>through interrupt</li> <li>Wake-up from SLEEP<br/>through WDT time-out</li> </ul> |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W        | _       | xxxx xxxx      | นนนน นนนน                                                                                                                                                  | <u></u>                                                                                                           |

| INDF     | 00h     |                | _                                                                                                                                                          | _                                                                                                                 |

| TMR0     | 01h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | นนนน นนนน                                                                                                         |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                                                                                  | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                                                                                   | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR      | 04h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                                                                                     | u uuuu                                                                                                            |

| PORTB    | 06h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | uuuu uuuu                                                                                                         |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                                                                                    | uu uuuu                                                                                                           |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                                                                                     | u uuuu                                                                                                            |

| INTCON   | 0Bh     | 0000 000x      | 0000 000u                                                                                                                                                  | uuuu uqqq <sup>(2)</sup>                                                                                          |

| PIR1     | 0Ch     | -0             | -0                                                                                                                                                         | -q (2,5)                                                                                                          |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                                                                                     | u uuuu                                                                                                            |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PIE1     | 8Ch     | -0             | -0                                                                                                                                                         | -u                                                                                                                |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                                                                        | uu                                                                                                                |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                                                                                  | uuu- uuuu                                                                                                         |

### TABLE 9-5: INITIALIZATION CONDITION FOR REGISTERS

$\label{eq:legend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 9-4 for RESET value for specific condition.

5: If wake-up was due to comparator input changing, then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = u.

**6:** If RESET was due to brown-out, then bit 0 = 0. All other RESETS will cause bit 0 = u.

TABLE 9-6: SUMMARY OF INTERRUPT REGISTERS

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on POR<br>Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 0Bh     | INTCON | GIE   | PEIE  | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1   | —     | CMIF  | —     | —     | —     | —     | —     | —     | -0                    | -0                                             |

| 8Ch     | PIE1   | _     | CMIE  | _     | _     | —     | _     | —     | _     | -0                    | -0                                             |

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

## 9.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and STATUS register). This will have to be implemented in software.

Example 9-3 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x20 in Bank 0 and it must also be defined at 0xA0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 9-3:

- · Stores the W register

- Stores the STATUS register in Bank 0

- Executes the ISR code

- Restores the STATUS (and bank select bit register)

- · Restores the W register

#### EXAMPLE 9-3: SAVING THE STATUS AND W REGISTERS IN RAM

| MOVWF | W_TEMP            | ;copy W to temp register,<br>;could be in either bank                       |

|-------|-------------------|-----------------------------------------------------------------------------|

| SWAPF | STATUS,W          | ;swap status to be saved<br>into W                                          |

| BCF   | STATUS, RPO       | ;change to bank 0 regardless<br>;of current bank                            |

| MOVWF | STATUS_TEMP       | ;save status to bank 0<br>;register                                         |

| :     |                   |                                                                             |

| :     | (ISR)             |                                                                             |

| :     |                   |                                                                             |

| SWAPF | STATUS_TEMP,<br>W | ;swap STATUS_TEMP register<br>;into W, sets bank to origi-<br>nal<br>;state |

| MOVWF | STATUS            | ;move W into STATUS register                                                |

| SWAPF | W_TEMP,F          | ;swap W_TEMP                                                                |

| SWAPF | W_TEMP,W          | ;swap W_TEMP into W                                                         |

# **10.0 INSTRUCTION SET SUMMARY**

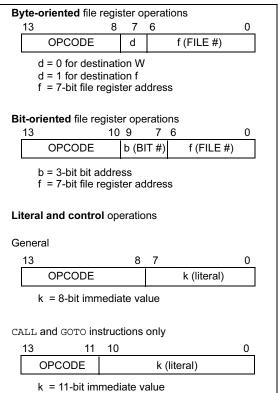

Each PIC16C62X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16C62X instruction set summary in Table 10-2 lists **byte-oriented**, **bitoriented**, and **literal and control** operations. Table 10-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 10-1: OPCODE FIELD DESCRIPTIONS

| DESCRIPTIONS  |                                                                                                                                                                                |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Field         | Description                                                                                                                                                                    |  |  |  |  |  |

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |  |  |  |  |  |

| W             | Working register (accumulator)                                                                                                                                                 |  |  |  |  |  |

| b             | Bit address within an 8-bit file register                                                                                                                                      |  |  |  |  |  |

| k             | Literal field, constant data or label                                                                                                                                          |  |  |  |  |  |

| х             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |  |  |  |  |  |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |  |  |  |  |  |

| label         | Label name                                                                                                                                                                     |  |  |  |  |  |

| TOS           | Top of Stack                                                                                                                                                                   |  |  |  |  |  |

| PC            | Program Counter                                                                                                                                                                |  |  |  |  |  |

| PCLAT<br>H    | Program Counter High Latch                                                                                                                                                     |  |  |  |  |  |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |  |  |  |  |  |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |  |  |  |  |  |

| то            | Time-out bit                                                                                                                                                                   |  |  |  |  |  |

| PD            | Power-down bit                                                                                                                                                                 |  |  |  |  |  |

| dest          | Destination either the W register or the specified regis-<br>ter file location                                                                                                 |  |  |  |  |  |

| []            | Options                                                                                                                                                                        |  |  |  |  |  |

| ()            | Contents                                                                                                                                                                       |  |  |  |  |  |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |  |  |  |  |  |

| < >           | Register bit field                                                                                                                                                             |  |  |  |  |  |

| ∈             | In the set of                                                                                                                                                                  |  |  |  |  |  |

| italics       | User defined term (font is courier)                                                                                                                                            |  |  |  |  |  |

|               |                                                                                                                                                                                |  |  |  |  |  |

The instruction set is highly orthogonal and is grouped into three basic categories:

- · Byte-oriented operations

- **Bit-oriented** operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 10-1 lists the instructions recognized by the MPASM  $^{\rm TM}$  assembler.

Figure 10-1 shows the three general formats that the instructions can have.

| Note: | To maintain upward compatibility with                 |  |  |  |  |  |  |  |

|-------|-------------------------------------------------------|--|--|--|--|--|--|--|

|       | future PICmicro <sup>®</sup> products, do not use the |  |  |  |  |  |  |  |

|       | OPTION and TRIS instructions.                         |  |  |  |  |  |  |  |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

# PIC16C62X

| INCFSZ                       | Increment f, Skip if 0                                                                                                                                                | IORWF            | Inclusive OR W with f                                                                                                                                                 |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                      | [ <i>label</i> ] INCFSZ f,d                                                                                                                                           | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                            |  |  |

| Operands:                    | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                    | Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                    |  |  |

| Operation:                   | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                      | Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                     |  |  |

| Status Affected:             | None                                                                                                                                                                  | Status Affected: | Z                                                                                                                                                                     |  |  |

| Encoding:                    | 00 1111 dfff ffff                                                                                                                                                     | Encoding:        | 00 0100 dfff ffff                                                                                                                                                     |  |  |

| Description:                 | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'. | Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |  |  |

|                              | If the result is 0, the next instruc-<br>tion, which is already fetched, is                                                                                           | Words:           | 1                                                                                                                                                                     |  |  |

|                              | discarded. A NOP is executed                                                                                                                                          | Cycles:          | 1                                                                                                                                                                     |  |  |

|                              | instead making it a two-cycle                                                                                                                                         | Example          | IORWF RESULT, 0                                                                                                                                                       |  |  |

| Words:<br>Cycles:<br>Example | instruction. 1 1(2) HERE INCFSZ CNT, 1 GOTO LOOP CONTINUE • •                                                                                                         |                  | Before InstructionRESULT = $0x13$ W = $0x91$ After InstructionRESULT =RESULT = $0x13$ W = $0x93$ Z =1                                                                 |  |  |

|                              | •<br>Before Instruction                                                                                                                                               | MOVLW            | Move Literal to W                                                                                                                                                     |  |  |

|                              | PC = address HERE<br>After Instruction                                                                                                                                | Syntax:          | [ <i>label</i> ] MOVLW k                                                                                                                                              |  |  |

|                              | CNT = CNT + 1                                                                                                                                                         | Operands:        | $0 \le k \le 255$                                                                                                                                                     |  |  |

|                              | if CNT= 0,<br>PC = address CONTINUE                                                                                                                                   | Operation:       | $k \rightarrow (W)$                                                                                                                                                   |  |  |

|                              | if CNT≠ 0,                                                                                                                                                            | Status Affected: | None                                                                                                                                                                  |  |  |

|                              | PC = address HERE +1                                                                                                                                                  | Encoding:        | 11 00xx kkkk kkkk                                                                                                                                                     |  |  |

| IORLW                        | Inclusive OR Literal with W                                                                                                                                           | Description:     | The eight bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's.                                                                      |  |  |

| Syntax:                      | [ <i>label</i> ] IORLW k                                                                                                                                              | Words:           | 1                                                                                                                                                                     |  |  |

| Operands:                    | $0 \le k \le 255$                                                                                                                                                     | Cycles:          | 1                                                                                                                                                                     |  |  |

| Operation:                   | (W) .OR. $k \rightarrow$ (W)                                                                                                                                          | Example          | MOVLW 0x5A                                                                                                                                                            |  |  |

| Status Affected:             | Z                                                                                                                                                                     | Example          | After Instruction                                                                                                                                                     |  |  |

| Encoding:                    | 11 1000 kkkk kkkk                                                                                                                                                     |                  | W = 0x5A                                                                                                                                                              |  |  |

| Description:                 | The contents of the W register is<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register.                                              |                  |                                                                                                                                                                       |  |  |

| Words:                       | 1                                                                                                                                                                     |                  |                                                                                                                                                                       |  |  |

| Cycles:                      | 1                                                                                                                                                                     |                  |                                                                                                                                                                       |  |  |

| Example                      | IORLW 0x35                                                                                                                                                            |                  |                                                                                                                                                                       |  |  |

|                              | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBE                                                                                                       |                  |                                                                                                                                                                       |  |  |

W = Z =

0xBF 1

## 11.14 PICDEM 1 PICmicro Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include analog input, push button switches and eight LEDs.

## 11.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham

## 11.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessary hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 FLASH microcontrollers.

## 11.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

## 11.18 PICDEM 4 8/14/18-Pin Demonstration Board

The PICDEM 4 can be used to demonstrate the capabilities of the 8-, 14-, and 18-pin PIC16XXXX and PIC18XXXX MCUs, including the PIC16F818/819, PIC16F87/88, PIC16F62XA and the PIC18F1320 family of microcontrollers. PICDEM 4 is intended to showcase the many features of these low pin count parts, including LIN and Motor Control using ECCP. Special provisions are made for low power operation with the supercapacitor circuit, and jumpers allow onboard hardware to be disabled to eliminate current draw in this mode. Included on the demo board are provisions for Crystal, RC or Canned Oscillator modes, a five volt regulator for use with a nine volt wall adapter or battery, DB-9 RS-232 interface, ICD connector for programming via ICSP and development with MPLAB ICD 2, 2x16 liquid crystal display, PCB footprints for H-Bridge motor driver, LIN transceiver and EEPROM. Also included are: header for expansion, eight LEDs, four potentiometers, three push buttons and a prototyping area. Included with the kit is a PIC16F627A and a PIC18F1320. Tutorial firmware is included along with the User's Guide.

# 11.19 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board FLASH memory. A generous prototype area is available for user hardware expansion.

# PIC16C62X

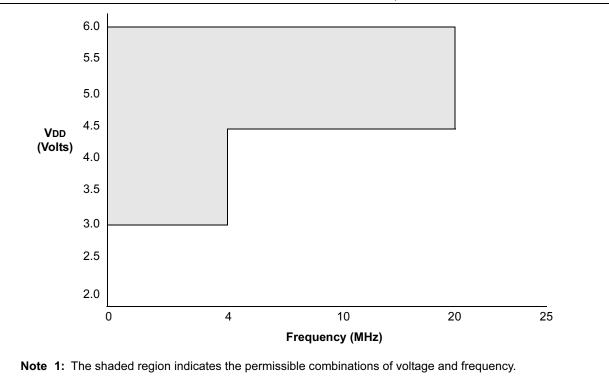

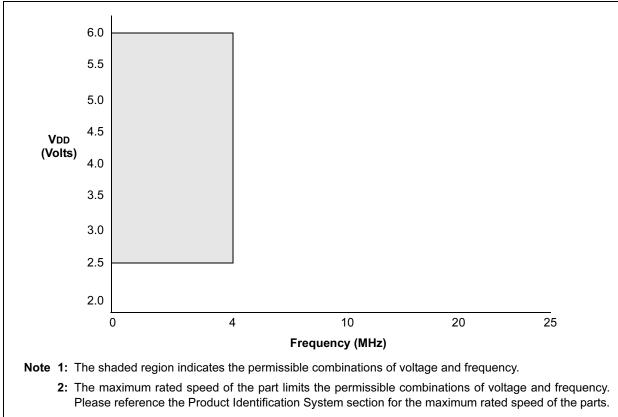

**2**: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

## 12.2 DC Characteristics: PIC16C62XA-04 (Commercial, Industrial, Extended) PIC16C62XA-20 (Commercial, Industrial, Extended) PIC16LC62XA-04 (Commercial, Industrial, Extended) (CONT.)

| PIC16C62XA<br>PIC16LC62XA |     |                                   | Oper<br>Stand<br>Oper | $\begin{array}{l lllllllllllllllllllllllllllllllllll$ |                         |                      |                                                                                                                                                                       |  |  |

|---------------------------|-----|-----------------------------------|-----------------------|-------------------------------------------------------|-------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param.<br>No.             | Sym | Characteristic                    | Min                   | Тур†                                                  | Мах                     | Units                | Conditions                                                                                                                                                            |  |  |

| D010                      | IDD | Supply Current <sup>(2, 4)</sup>  |                       | 1.2<br>0.4<br>1.0                                     | 2.0<br>1.2<br>2.0       | mA<br>mA<br>mA       | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT mode, (Note 4)*<br>Fosc = 4 MHz, VDD = 3.0V, WDT disabled,<br>XT mode, (Note 4)*<br>Fosc = 10 MHz, VDD = 3.0V, WDT dis- |  |  |

|                           |     |                                   | _                     | 4.0                                                   | 6.0<br>7.0              | mA                   | abled, HS mode, (Note 6)<br>Fosc = 20 MHz, VDD = 4.5V, WDT dis-<br>abled, HS mode<br>Fosc = 20 MHz, VDD = 5.5V, WDT dis-                                              |  |  |

|                           |     |                                   | _                     | 35                                                    | 70                      | μA                   | abled*, HS mode<br>Fosc = 32 kHz, VDD = 3.0V, WDT dis-<br>abled, LP mode                                                                                              |  |  |

| D010                      | IDD | Supply Current <sup>(2)</sup>     | _                     | 1.2<br>—<br>35                                        | 2.0<br>1.1<br>70        | mA<br>mA<br>μA       | Fosc = 4 MHz, VDD = 5.5V, WDT disabled<br>XT mode, (Note 4)*<br>Fosc = 4 MHz, VDD = 2.5V, WDT disabled<br>XT mode, (Note 4)                                           |  |  |

| D020                      | IPD | Power-down Current <sup>(3)</sup> |                       |                                                       | 2.2<br>5.0              | μΑ<br>μΑ<br>μΑ       | Fosc = 32 kHz, VDD = 2.5V, WDT dis-<br>abled, LP mode<br>VDD = 3.0V<br>VDD = 4.5V*                                                                                    |  |  |

|                           |     |                                   |                       |                                                       | 9.0<br>15               | μA<br>μA             | VDD = 5.5V<br>VDD = 5.5V Extended Temp.                                                                                                                               |  |  |

| D020                      | IPD | Power-down Current <sup>(3)</sup> |                       | <br> <br>                                             | 2.0<br>2.2<br>9.0<br>15 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 2.5V<br>VDD = 3.0V*<br>VDD = 5.5V<br>VDD = 5.5V Extended Temp.                                                                                                  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

| Parameter<br>No. | Sym          | Characteristic                                               | Min                                | Тур†    | Max        | Units    | Conditions                                                   |

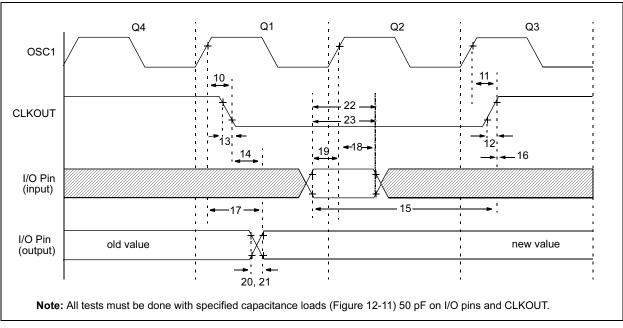

|------------------|--------------|--------------------------------------------------------------|------------------------------------|---------|------------|----------|--------------------------------------------------------------|

| 10*              | TosH2ckL     | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                              |                                    | 75<br>— | 200<br>400 | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 11*              | TosH2ck<br>H | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                              |                                    | 75<br>— | 200<br>400 | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 12*              | TckR         | CLKOUT rise time <sup>(1)</sup>                              |                                    | 35<br>— | 100<br>200 | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 13*              | TckF         | CLKOUT fall time <sup>(1)</sup>                              |                                    | 35<br>— | 100<br>200 | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 14*              | TckL2ioV     | CLKOUT ↓ to Port out valid <sup>(1)</sup>                    | _                                  | —       | 20         | ns       |                                                              |

| 15*              | TioV2ckH     | Port in valid before CLKOUT <sup>↑(1)</sup>                  | Tosc +200<br>ns<br>Tosc +400<br>ns | —       | _          | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 16*              | TckH2iol     | Port in hold after CLKOUT ↑ <sup>(1)</sup>                   | 0                                  | —       |            | ns       |                                                              |

| 17*              | TosH2ioV     | OSC1↑ (Q1 cycle) to Port out valid                           |                                    | 50      | 150<br>300 | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 18*              | TosH2iol     | OSC1↑ (Q2 cycle) to Port input<br>invalid (I/O in hold time) | 100<br>200                         | _       | _          | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 19*              | TioV2osH     | Port input valid to OSC1↑ (I/O in setup time)                | 0                                  | —       | _          | ns       |                                                              |

| 20*              | TioR         | Port output rise time                                        | _                                  | 10<br>— | 40<br>80   | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 21*              | TioF         | Port output fall time                                        | _                                  | 10<br>— | 40<br>80   | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 22*              | Tinp         | RB0/INT pin high or low time                                 | 25<br>40                           | _       | _          | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 23               | Trbp         | RB<7:4> change interrupt high or<br>low time                 | Тсү                                |         |            | ns       |                                                              |

# TABLE 12-4: CLKOUT AND I/O TIMING REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| DeviceFrequency<br>RangeTemperature<br>RangePackageDevicePIC16C62X: VDD range 3.0V to 6.0V<br>PIC16C62XAT: VDD range 3.0V to 6.0V<br>PIC16C62XA: VDD range 3.0V to 5.5V<br>PIC16LC62XA: VDD range 2.5V to 6.0V<br>PIC16LC62XA: VDD range 2.5V to 6.0V<br>PIC16LC62XA: VDD range 2.5V to 5.5V<br>PIC16LC62XA: VDD range 2.5V to 5.5V<br>PIC16LC62XAT: VDD range 2.5V to 5.5V<br>PIC16LC620AT: VDD range 2.0V to 5.5V<br>PIC16LC620AT: VDD range 2.0V to 5.5V<br>PIC16LCR620AT: VDD range 2.0V to 5.5V<br>PIC16LCR6                                                      | PART NO.        | <u>-xx</u>                                                                                                        | ¥                                                                                                                                                                                                                   | <u>/xx</u>                                                                                                                                                                                                                                                                                                                | xxx                                                            | Ex      | amples:                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------|

| PIC16C62XT: VDD range 3.0V to 6.0V<br>PIC16C62XA: VDD range 3.0V to 5.5V<br>PIC16C62XA: VDD range 3.0V to 5.5V<br>PIC16LC62XA: VDD range 2.5V to 6.0V<br>PIC16LC62X: VDD range 2.5V to 5.5V<br>PIC16LC62XA: VDD range 2.5V to 5.5V<br>PIC16LC62XA: VDD range 2.5V to 5.5V<br>PIC16CR620A: VDD range 2.5V to 5.5V<br>PIC16CR620A: VDD range 2.5V to 5.5V<br>PIC16CR620A: VDD range 2.5V to 5.5V<br>PIC16LC622A: VDD range 2.5V to 5.5V<br>PIC16LC622A: VDD range 2.5V to 5.5V<br>PIC16LCR620A: VDD range 2.0V to 5.5V | Device          |                                                                                                                   |                                                                                                                                                                                                                     | Package                                                                                                                                                                                                                                                                                                                   | Pattern                                                        | a)      | PIC16C621A - 04/P 301 = Commercial temp.,<br>PDIP package, 4 MHz, normal VDD limits, QTP<br>pattern #301. |

| $\begin{array}{rcl} 04 & 4 \text{ MHz} (XT \text{ and } \text{RC osc}) \\ 20 & 20 \text{ MHz} (\text{HS osc}) \\ \end{array}$ Temperature Range - = 0°C to +70°C<br>I = -40°C to +85°C<br>E = -40°C to +125°C<br>Package P = PDIP<br>SO = SOIC (Gull Wing, 300 mil bo<br>SS = SSOP (209 mil)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Device          | PIC16C62<br>PIC16C62<br>PIC16LC6<br>PIC16LC6<br>PIC16LC6<br>PIC16LC6<br>PIC16LC6<br>PIC16CR<br>PIC16CR<br>PIC16CR | 2XT: VDD range 3.0<br>2XA: VDD range 3.0<br>2XAT: VDD range 3.6<br>22XT: VDD range 2.5<br>32XT: VDD range 2.5<br>32XA: VDD range 2<br>52XA: VDD range 2<br>620A: VDD range 2<br>620A: VDD range<br>R620A: VDD range | W to 6.0V (Tap           OV to 5.5V           .0V to 5.5V (Ta           5V to 6.0V           .5V to 6.0V (Ta           .5V to 5.5V           .5V to 5.5V           2.5V to 5.5V | pe and Reel)<br>pe and Reel)<br>ape and Reel)<br>ape and Reel) | )<br>b) | PIC16LC622-04I/SO = Industrial temp., SOIC<br>package, 200 kHz, extended VDD limits.                      |

| Package P = PDIP<br>SO = SOIC (Gull Wing, 300 mil bo<br>SS = SSOP (209 mil)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Frequency Rang  | 04 4 MH                                                                                                           | Iz (XT and RC osc                                                                                                                                                                                                   | ;)                                                                                                                                                                                                                                                                                                                        |                                                                |         |                                                                                                           |

| SO = SOIC (Gull Wing, 300 mil bo<br>SS = SSOP (209 mil)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Temperature Rar | = -                                                                                                               | -40°C to +85°C                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                           |                                                                |         |                                                                                                           |