Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 96 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621a-20-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **EPROM-Based 8-Bit CMOS Microcontrollers**

#### Devices included in this data sheet:

Referred to collectively as PIC16C62X.

- PIC16C620 PIC16C620A

- PIC16C621 PIC16C621A

- PIC16C622 PIC16C622A

- PIC16CR620A

#### **High Performance RISC CPU:**

- Only 35 instructions to learn

- All single cycle instructions (200 ns), except for program branches which are two-cycle

- Operating speed:

- DC 40 MHz clock input

- DC 100 ns instruction cycle

| Device      | Program<br>Memory | Data<br>Memory |

|-------------|-------------------|----------------|

| PIC16C620   | 512               | 80             |

| PIC16C620A  | 512               | 96             |

| PIC16CR620A | 512               | 96             |

| PIC16C621   | 1K                | 80             |

| PIC16C621A  | 1K                | 96             |

| PIC16C622   | 2K                | 128            |

| PIC16C622A  | 2K                | 128            |

· Interrupt capability

- 16 special function hardware registers

- 8-level deep hardware stack

- Direct, Indirect and Relative addressing modes

#### **Peripheral Features:**

- 13 I/O pins with individual direction control

- High current sink/source for direct LED drive

- Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VREF) module

- Programmable input multiplexing from device inputs and internal voltage reference

- Comparator outputs can be output signals

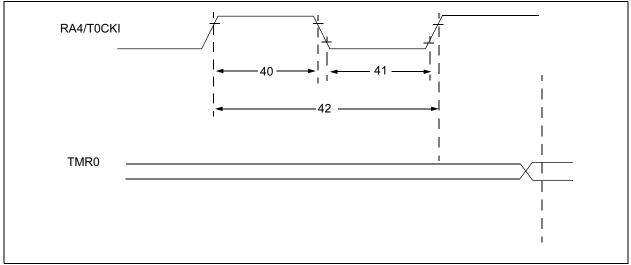

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

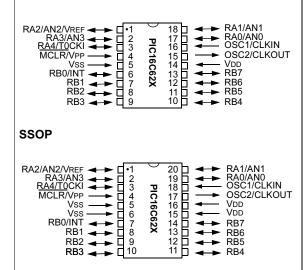

#### Pin Diagrams

#### PDIP, SOIC, Windowed CERDIP

#### **Special Microcontroller Features:**

- · Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- · Programmable code protection

- · Power saving SLEEP mode

- Selectable oscillator options

- Serial in-circuit programming (via two pins)

- Four user programmable ID locations

#### **CMOS Technology:**

- Low power, high speed CMOS EPROM technology

- Fully static design

- · Wide operating range

- 2.5V to 5.5V

- Commercial, industrial and extended temperature range

- Low power consumption

- < 2.0 mA @ 5.0V, 4.0 MHz

- 15 μA typical @ 3.0V, 32 kHz

- < 1.0 μA typical standby current @ 3.0V

NOTES:

### 1.0 GENERAL DESCRIPTION

The PIC16C62X devices are 18 and 20-Pin ROM/ EPROM-based members of the versatile PICmicro<sup>®</sup> family of low cost, high performance, CMOS, fullystatic, 8-bit microcontrollers.

All PICmicro microcontrollers employ an advanced RISC architecture. The PIC16C62X devices have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16C62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC16C620A, PIC16C621A and PIC16CR620A have 96 bytes of RAM. The PIC16C622(A) has 128 bytes of RAM. Each device has 13 I/O pins and an 8-bit timer/counter with an 8-bit programmable prescaler. In addition, the PIC16C62X adds two analog comparators with a programmable on-chip voltage reference module. The comparator module is ideally suited for applications requiring a low cost analog interface (e.g., battery chargers, threshold detectors, white goods controllers, etc).

PIC16C62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (Power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external and internal interrupts and RESET.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock- up.

A UV-erasable CERDIP-packaged version is ideal for code development while the cost effective One-Time-Programmable (OTP) version is suitable for production in any volume.

Table 1-1 shows the features of the PIC16C62X midrange microcontroller families.

A simplified block diagram of the PIC16C62X is shown in Figure 3-1.

The PIC16C62X series fits perfectly in applications ranging from battery chargers to low power remote sensors. The EPROM technology makes

customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C62X very versatile.

#### 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to PIC16C62X family of devices (Appendix B). The PIC16C62X family fills the niche for users wanting to migrate up from the PIC16C5X family and not needing various peripheral features of other members of the PIC16XX mid-range microcontroller family.

#### 1.2 Development Support

The PIC16C62X family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low cost development programmer and a full-featured programmer. Third Party "C" compilers are also available.

| Name         | DIP/SOIC<br>Pin # | SSOP<br>Pin # | I/O/P Type             | Buffer<br>Type        | Description                                                                                                                                                                                                         |

|--------------|-------------------|---------------|------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 16                | 18            | I                      | ST/CMOS               | Oscillator crystal input/external clock source input.                                                                                                                                                               |

| OSC2/CLKOUT  | 15                | 17            | 0                      | _                     | Oscillator crystal output. Connects to crystal or resonator<br>in Crystal Oscillator mode. In RC mode, OSC2 pin out-<br>puts CLKOUT, which has 1/4 the frequency of OSC1<br>and denotes the instruction cycle rate. |

| MCLR/VPP     | 4                 | 4             | I/P                    | ST                    | Master Clear (Reset) input/programming voltage input.<br>This pin is an Active Low Reset to the device.                                                                                                             |

|              |                   |               |                        |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                                 |

| RA0/AN0      | 17                | 19            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |

| RA1/AN1      | 18                | 20            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |

| RA2/AN2/VREF | 1                 | 1             | I/O                    | ST                    | Analog comparator input or VREF output                                                                                                                                                                              |

| RA3/AN3      | 2                 | 2             | I/O                    | ST                    | Analog comparator input /output                                                                                                                                                                                     |

| RA4/T0CKI    | 3                 | 3             | I/O                    | ST                    | Can be selected to be the clock input to the Timer<br>timer/counter or a comparator output. Output is<br>open drain type.                                                                                           |

|              |                   |               |                        |                       | PORTB is a bi-directional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs.                                                                                                 |

| RB0/INT      | 6                 | 7             | I/O                    | TTL/ST <sup>(1)</sup> | RB0/INT can also be selected as an externa interrupt pin.                                                                                                                                                           |

| RB1          | 7                 | 8             | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB2          | 8                 | 9             | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB3          | 9                 | 10            | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB4          | 10                | 11            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |

| RB5          | 11                | 12            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |

| RB6          | 12                | 13            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming clock                                                                                                                                                                   |

| RB7          | 13                | 14            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming data.                                                                                                                                                                   |

| Vss          | 5                 | 5,6           | Р                      |                       | Ground reference for logic and I/O pins.                                                                                                                                                                            |

| Vdd          | 14                | 15,16         | Р                      | _                     | Positive supply for logic and I/O pins.                                                                                                                                                                             |

| Legend:      | O = out<br>— = No | •             | I/O = inp<br>I = Input | ut/output             | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                             |

TTL = TTL input

**Note** 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

### 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-Chip Voltage Reference (Section 8.0) can also be an input to the comparators.

The CMCON register, shown in Register 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-1.

#### REGISTER 7-1: CMCON REGISTER (ADDRESS 1Fh)

|         |                             |                                 | <b>(</b> | ,   |       |       |       |       |

|---------|-----------------------------|---------------------------------|----------|-----|-------|-------|-------|-------|

|         | R-0                         | R-0                             | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|         | C2OUT                       | C10UT                           | —        | —   | CIS   | CM2   | CM1   | CM0   |

|         | bit 7                       |                                 |          |     |       |       |       | bit 0 |

|         |                             |                                 |          |     |       |       |       |       |

| bit 7   | <b>C2OUT</b> : Co           | omparator 2                     | output   |     |       |       |       |       |

|         | 1 = C2 VIN                  | + > C2 VIN-                     |          |     |       |       |       |       |

|         | 0 = C2 VIN                  | + < C2 VIN-                     |          |     |       |       |       |       |

| bit 6   | C10UT: Co                   | omparator 1                     | output   |     |       |       |       |       |

|         | 1 = C1 VIN                  | + > C1 VIN-                     |          |     |       |       |       |       |

|         | 0 = C1  VIN + < C1  VIN -   |                                 |          |     |       |       |       |       |

| bit 5-4 | Unimplem                    | ented: Read                     | d as '0' |     |       |       |       |       |

| bit 3   | CIS: Comp                   | arator Input                    | Switch   |     |       |       |       |       |

|         | When CM<                    | <2:0>: = 001                    | :        |     |       |       |       |       |

|         | 1 = C1 VIN-                 | - connects to                   | o RA3    |     |       |       |       |       |

|         | 0 = C1 VIN                  | - connects to                   | o RA0    |     |       |       |       |       |

|         | When CM<                    | <2:0> = 010:                    |          |     |       |       |       |       |

|         |                             | <ul> <li>connects to</li> </ul> |          |     |       |       |       |       |

|         |                             | I- connects t                   |          |     |       |       |       |       |

|         | 0 = C1 VIN- connects to RA0 |                                 |          |     |       |       |       |       |

|         | C2 VIN                      | I- connects t                   | 0 RA1    |     |       |       |       |       |

| bit 2-0 | CM<2:0>:                    | Comparator                      | mode.    |     |       |       |       |       |

|         |                             |                                 |          |     |       |       |       |       |

|         | Legend:                     |                                 |          |     |       |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 9.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16C62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-Circuit Serial Programming™

The PIC16C62X devices have a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 9.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### REGISTER 9-1: CONFIGURATION WORD (ADDRESS 2007h)

| CP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CP0 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                            | CP1                                                                                                                                                                                                                      | CP0 <sup>(2)</sup> | CP1     | CP0 <sup>(2)</sup> |        | BODEN    | CP1     | CP0 (2)  | PWRTE   | WDTE     | F0SC1 | F0SC0 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|--------------------|--------|----------|---------|----------|---------|----------|-------|-------|

| bit 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ļ                                                                                                                                                                                                                                                                                                                             | <u> </u>                                                                                                                                                                                                                 | ļļ                 |         | ļ                  |        | <u> </u> | <u></u> | <u>I</u> | <u></u> | <u> </u> | ļ     | bit 0 |

| bit 13-8,       CP<1:0>: Code protection bit pairs <sup>(2)</sup> 5-4:       Code protection for 2K program memory         11 = Program memory code protection off       10 = 0400h-07FFh code protected         01 = 0200h-07FFh code protected       00 = 0000h-07FFh code protected         00 = 0000h-07FFh code protected       Code protection for 1K program memory         11 = Program memory code protection off       10 = Program memory code protection off         10 = Program memory code protected       00 = 0000h-03FFh code protected         00 = 0000h-03FFh code protected       00 = 0000h-03FFh code protected         00 = 0000h-03FFh code protected       00 = 0000h-03FFh code protected         00 = 0000h-03FFh code protected       00 = 0000h-03FFh code protected         00 = 0000h-03FFh code protected       00 = 0000h-03FFh code protected         00 = 0000h-03FFh code protected       00 = 0000h-03FFh code protected         00 = 0000h-03FFh code protected       00 = 0000h-03FFh code protected         00 = 0000h-03FFh code protected       00 = 0000h-03FFh code protection off         11 = Program memory code protection off       10 = Program memory code protection off         10 = Program memory code protection off       10 = Program memory code protection off |                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                          |                    |         |                    |        |          |         |          |         |          |       |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                        | m memo<br>-01FFh c |         |                    | on off |          |         |          |         |          |       |       |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                          | nted: Re           | -       |                    |        |          |         |          |         |          |       |       |

| bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BOI                                                                                                                                                                                                                                                                                                                           | DEN: Br                                                                                                                                                                                                                  | own-out l          | Reset E | nable bit          | (1)    |          |         |          |         |          |       |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                               | 1 = BOR enabled<br>0 = BOR disabled                                                                                                                                                                                      |                    |         |                    |        |          |         |          |         |          |       |       |

| bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 =                                                                                                                                                                                                                                                                                                                           | <b>PWRTE</b> : Power-up Timer Enable bit <sup>(1, 3)</sup><br>1 = PWRT disabled<br>0 = PWRT enabled                                                                                                                      |                    |         |                    |        |          |         |          |         |          |       |       |

| bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 =                                                                                                                                                                                                                                                                                                                           | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                                                                                                                                   |                    |         |                    |        |          |         |          |         |          |       |       |

| bit 1-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>11 = RC oscillator</li> <li>10 = HS oscillator</li> <li>01 = XT oscillator</li> <li>00 = LP oscillator</li> <li>Note 1: Enabling Brown-out Reset automatically enables Power-up Timer (PWRT) regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled anytime Brown-out Detect Reset is</li> </ul> |                                                                                                                                                                                                                          |                    |         |                    |        |          |         |          |         |          |       |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                               | <ul> <li>enabled.</li> <li>2: All of the CP&lt;1:0&gt; pairs have to be given the same value to enable the code protection scheme listed.</li> <li>3: Unprogrammed parts default the Power-up Timer disabled.</li> </ul> |                    |         |                    |        |          |         |          |         |          |       |       |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                          |                    |         |                    |        |          |         |          |         |          |       |       |

#### 9.9 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip                    | does | not | recommend | code |  |  |

|-------|------------------------------|------|-----|-----------|------|--|--|

|       | protecting windowed devices. |      |     |           |      |  |  |

#### 9.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify. Only the Least Significant 4 bits of the ID locations are used.

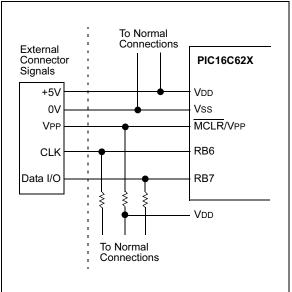

#### 9.11 In-Circuit Serial Programming™

The PIC16C62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X/9XX Programming Specification (DS30228).

A typical In-Circuit Serial Programming connection is shown in Figure 9-19.

# FIGURE 9-19:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| TABLE 10-2: PIC16C62X INSTRUCTION SET |

|---------------------------------------|

|---------------------------------------|

| Mnemonic,<br>Operands |          | Description                  | Cycles |     | 14-Bit | Opcode | Status | Notes    |       |

|-----------------------|----------|------------------------------|--------|-----|--------|--------|--------|----------|-------|

|                       |          |                              |        | MSb |        | LSb    |        | Affected |       |

| BYTE-OR               | IENTED I | FILE REGISTER OPERATIONS     |        |     |        |        |        |          |       |

| ADDWF                 | f, d     | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff   | C,DC,Z   | 1,2   |

| ANDWF                 | f, d     | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff   | Z        | 1,2   |

| CLRF                  | f        | Clear f                      | 1      | 00  | 0001   | lfff   | ffff   | Z        | 2     |

| CLRW                  | -        | Clear W                      | 1      | 00  | 0001   | 0000   | 0011   | Z        |       |

| COMF                  | f, d     | Complement f                 | 1      | 00  | 1001   | dfff   | ffff   | Z        | 1,2   |

| DECF                  | f, d     | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff   | Z        | 1,2   |

| DECFSZ                | f, d     | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff   |          | 1,2,3 |

| INCF                  | f, d     | Increment f                  | 1      | 00  | 1010   | dfff   | ffff   | Z        | 1,2   |

| INCFSZ                | f, d     | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff   |          | 1,2,3 |

| IORWF                 | f, d     | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff   | Z        | 1,2   |

| MOVF                  | f, d     | Move f                       | 1      | 00  | 1000   | dfff   | ffff   | Z        | 1,2   |

| MOVWF                 | f        | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff   |          |       |

| NOP                   | -        | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000   |          |       |

| RLF                   | f, d     | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff   | С        | 1,2   |

| RRF                   | f, d     | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff   | С        | 1,2   |

| SUBWF                 | f, d     | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff   | C,DC,Z   | 1,2   |

| SWAPF                 | f, d     | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff   |          | 1,2   |

| XORWF                 | f, d     | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff   | Z        | 1,2   |

| BIT-ORIEN             | NTED FIL | E REGISTER OPERATIONS        |        |     |        |        |        | •        |       |

| BCF                   | f, b     | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff   |          | 1,2   |

| BSF                   | f, b     | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff   |          | 1,2   |

| BTFSC                 | f, b     | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff   |          | 3     |

| BTFSS                 | f, b     | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff   |          | 3     |

| LITERAL               | AND CO   | NTROL OPERATIONS             |        |     |        |        |        |          |       |

| ADDLW                 | k        | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk   | C,DC,Z   |       |

| ANDLW                 | k        | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk   | Z        |       |

| CALL                  | k        | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk   |          |       |

| CLRWDT                | -        | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100   | TO,PD    |       |

| GOTO                  | k        | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk   |          |       |

| IORLW                 | k        | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk   | Z        |       |

| MOVLW                 | k        | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk   |          |       |

| RETFIE                | -        | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001   |          |       |

| RETLW                 | k        | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk   |          |       |

| RETURN                | -        | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000   |          |       |

| SLEEP                 | -        | Go into Standby mode         | 1      | 00  | 0000   | 0110   | 0011   | TO,PD    |       |

| SUBLW                 | k        | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk   | C,DC,Z   |       |

| XORLW                 | k        | Exclusive OR literal with W  | 1      | 11  | 1010   | kkkk   | kkkk   | Z        |       |

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**2:** If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| SWAPF            | Swap Ni                                                                                                                                                                    | bbles in  | f    |              |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|--------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                 |           |      |              |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                          |           |      |              |  |  |  |

| Operation:       | (f<3:0>) → (dest<7:4>),<br>(f<7:4>) → (dest<3:0>)                                                                                                                          |           |      |              |  |  |  |

| Status Affected: | None                                                                                                                                                                       |           |      |              |  |  |  |

| Encoding:        | 00                                                                                                                                                                         | 1110      | dfff | ffff         |  |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in W<br>register. If 'd' is 1, the result is<br>placed in register 'f'. |           |      |              |  |  |  |

| Words:           | 1                                                                                                                                                                          |           |      |              |  |  |  |

| Cycles:          | 1                                                                                                                                                                          |           |      |              |  |  |  |

| Example          | SWAPF                                                                                                                                                                      | REG,      | 0    |              |  |  |  |

|                  | Before In                                                                                                                                                                  | struction |      |              |  |  |  |

|                  |                                                                                                                                                                            | REG1      | = (  | DxA5         |  |  |  |

|                  | After Inst                                                                                                                                                                 | ruction   |      |              |  |  |  |

|                  |                                                                                                                                                                            | REG1<br>W |      | 0xA5<br>0x5A |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                 |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                                                            |  |  |  |  |  |  |

| Operands:        | $5 \le f \le 7$                                                                                                                                                                    |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow TRIS$ register f;                                                                                                                                                 |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                               |  |  |  |  |  |  |

| Encoding:        | 00 0000 0110 Offf                                                                                                                                                                  |  |  |  |  |  |  |

| Description:     | The instruction is supported for<br>code compatibility with the<br>PIC16C5X products. Since TRIS<br>registers are readable and<br>writable, the user can directly<br>address them. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                  |  |  |  |  |  |  |

| Example          |                                                                                                                                                                                    |  |  |  |  |  |  |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup> prod-<br>ucts, do not use this<br>instruction.                                                             |  |  |  |  |  |  |

| XORLW                                                                                                    | Exclusive OR Literal with W                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                  | [ <i>label</i> XORLW k<br>]                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Operands:                                                                                                | $0 \le k \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Operation:                                                                                               | (W) .XOR. $k \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                                                                                                | 11 1010 kkkk kkkk                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Description:                                                                                             | The contents of the W register<br>are XOR'ed with the eight bit<br>literal 'k'. The result is placed in<br>the W register.                                                                                                                                                                                                                                                                                                                                                              |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example:                                                                                                 | XORLW 0xAF                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                          | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                          | W = 0xB5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                          | After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                          | W = 0x1A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| XORWF                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                          | Exclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Syntax:                                                                                                  | [label] XORWF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Syntax:                                                                                                  | [ <i>label</i> ] XORWF f,d $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Syntax:<br>Operands:                                                                                     | $ \begin{array}{ll} \textit{[label]} & XORWF & f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \end{array} $                                                                                                                                                                                                                                                                                                                                                                                    |

| Syntax:<br>Operands:<br>Operation:                                                                       | $ \begin{array}{ll} \textit{[label]} & \text{XORWF} & \textit{f,d} \\ 0 \leq \textit{f} \leq 127 \\ d \in [0,1] \\ (W) & \text{XOR.} & (\textit{f}) \rightarrow (\textit{dest}) \end{array} $                                                                                                                                                                                                                                                                                           |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] XORWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                                                                                                                                                                                             |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{array}{c c} \textit{[label]} & \text{XORWF} & \textit{f,d} \\ 0 \leq \textit{f} \leq 127 \\ d \in [0,1] \\ (W) . \text{XOR.} (\textit{f}) \rightarrow (\text{dest}) \\ \hline Z \\ \hline \hline 00 & 0110 & \text{dfff} & \text{ffff} \\ \hline \text{Exclusive OR the contents of the} \\ W \text{ register with register 'f'. If 'd' is} \\ 0, \text{ the result is stored in the W} \\ \text{register. If 'd' is 1, the result is} \end{array}$                             |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d$ $0 \le f \le 127$ $d \in [0,1]$ (W) .XOR. (f) $\rightarrow$ (dest) Z $\boxed{00 \qquad 0110 \qquad dfff \qquad ffff}$ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'.                                                                                                                              |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $[label] XORWF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (W) .XOR. (f) $\rightarrow$ (dest) Z $\boxed{00  0110  dfff  ffff}$ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. 1                                                                                                                                                                                   |