Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                |                                                                             |

| RAM Size                   | 96 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | <u>.</u>                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621a-20e-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### 4.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

| E PE<br>Global Internables all un<br>isables all in<br>Peripheral<br>nables all p<br>TMR0 Ove<br>nables the T<br>isables the | N-0     R/W-0       EIE     TOIE       rrupt Enable bit       n-masked interrunts       Interrupts       Interrupt Enable       n-masked periphoreripheral interrupt       erflow Interrupt Entrupt       TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | R/W-0<br>RBIE                                                                                                                                                        | R/W-0<br>T0IF                                                                                                                                                                                                                                | R/W-0<br>INTF                                                                                                                                                                                                            | R/W-x<br>RBIF<br>bit 0                                                                                                                                                                                                                                                                     |  |  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          | bit 0                                                                                                                                                                                                                                                                                      |  |  |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| sables all in<br>Peripheral<br>nables all un<br>sables all p<br>TMR0 Ove<br>nables the T<br>isables the                      | nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                                                          | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the                                                       | n-masked periph<br>peripheral interru<br>rflow Interrupt Er<br>TMR0 interrupt                                                                                                                                            | neral interrupt<br>pts                                                                                                  | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| sables all p<br>TMR0 Ove<br>nables the<br>sables the                                                                         | peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                                                                                                              | pts                                                                                                                     | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| TMR0 Ove<br>nables the<br>sables the                                                                                         | rflow Interrupt Er<br>TMR0 interrupt                                                                                                                                                                                     |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| nables the<br>isables the                                                                                                    | TMR0 interrupt                                                                                                                                                                                                           | nable bit                                                                                                               |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| sables the                                                                                                                   |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

|                                                                                                                              | I MRU interrupt                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

|                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| INTE: RB0/INT External Interrupt Enable bit                                                                                  |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

|                                                                                                                              | RB0/INT externa                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| 0 = Disables the RB0/INT external interrupt                                                                                  |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| <b>RBIE</b> : RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt                                |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

|                                                                                                                              | RB port change                                                                                                                                                                                                           | •                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| TMR0 Ove                                                                                                                     | rflow Interrupt Fl                                                                                                                                                                                                       | ag bit                                                                                                                  |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| 1 = TMR0 register has overflowed (must be cleared in software)                                                               |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| MR0 registe                                                                                                                  | er did not overflov                                                                                                                                                                                                      | W                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| RB0/INT E                                                                                                                    | xternal Interrupt                                                                                                                                                                                                        | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

|                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      | red in softwa                                                                                                                                                                                                                                | are)                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                            |  |  |

| RB Port Cl                                                                                                                   | hange Interrupt F                                                                                                                                                                                                        | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |

| 'hen at leas                                                                                                                 |                                                                                                                                                                                                                          | •                                                                                                                       | -                                                                                                                                                                    | (must be cle                                                                                                                                                                                                                                 | ared in softw                                                                                                                                                                                                            | ware)                                                                                                                                                                                                                                                                                      |  |  |

|                                                                                                                              | ne RB0/INT<br>ne RB0/INT<br>RB Port C<br>hen at leas                                                                                                                                                                     | ne RB0/INT external interrune<br>RB0/INT external interrun<br>RB Port Change Interrupt I<br>hen at least one of the RB< | ne RB0/INT external interrupt did not occ<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins cha<br>one of the RB<7:4> pins have changed s | ne RB0/INT external interrupt occurred (must be clea<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state<br>one of the RB<7:4> pins have changed state | ne RB0/INT external interrupt occurred (must be cleared in softwa<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cle | ne RB0/INT external interrupt occurred (must be cleared in software)<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cleared in softwore)<br>one of the RB<7:4> pins have changed state |  |  |

| REGISTER 4-3: | INTCON REGISTER (ADDRESS 0BH OR 8BH) |

|---------------|--------------------------------------|

|---------------|--------------------------------------|

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Name    | Bit # | Buffer Type           | Function                                                                                                                |  |

|---------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| RB0/INT | bit0  | TTL/ST <sup>(1)</sup> | Input/output or external interrupt input. Internal software programmable weak pull-up.                                  |  |

| RB1     | bit1  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |  |

| RB2     | bit2  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |  |

| RB3     | bit3  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |  |

| RB4     | bit4  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |  |

| RB5     | bit5  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |  |

| RB6     | bit6  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock pin. |  |

| RB7     | bit7  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data pin.  |  |

#### TABLE 5-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h     | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX XXXX       | uuuu uuuu                       |

| 86h     | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h     | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

Legend: u = unchanged, x = unknown

Note 1: Shaded bits are not used by PORTB.

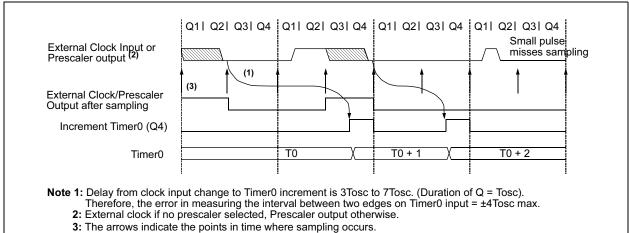

## 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

## 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

#### EXAMPLE 8-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; | 4 Inputs Muxed |

|-------|-------------|---|----------------|

| MOVWF | CMCON       | ; | to 2 comps.    |

| BSF   | STATUS, RPO | ; | go to Bank 1   |

| MOVLW | 0x0F        | ; | RA3-RA0 are    |

| MOVWF | TRISA       | ; | inputs         |

| MOVLW | 0xA6        | ; | enable VREF    |

| MOVWF | VRCON       | ; | low range      |

|       |             | ; | set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; | go to Bank O   |

| CALL  | DELAY10     | ; | 10µs delay     |

## 8.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 8-1) keep VREF from approaching VSS or VDD. The voltage reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the voltage reference can be found in Table 12-2.

## 8.3 Operation During SLEEP

When the device wakes up from SLEEP through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the voltage reference should be disabled.

## 8.4 Effects of a RESET

A device RESET disables the voltage reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

## 8.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the voltage reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the voltage reference output for external connections to VREF. Figure 8-2 shows an example buffering technique.

# FIGURE 8-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 8-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | -      | CIS    | CM2    | CM1    | CM0    | 00 0000         | 00 0000                         |

| 85h     | TRISA | _     |       |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

**Note:** - = Unimplemented, read as "0"

## 9.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16C62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-Circuit Serial Programming™

The PIC16C62X devices have a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 9.9 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip                    | does | not | recommend | code |  |  |

|-------|------------------------------|------|-----|-----------|------|--|--|

|       | protecting windowed devices. |      |     |           |      |  |  |

#### 9.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify. Only the Least Significant 4 bits of the ID locations are used.

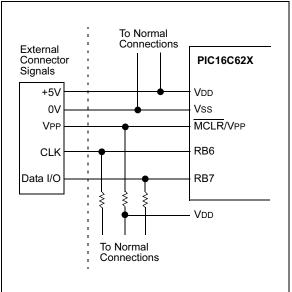

## 9.11 In-Circuit Serial Programming™

The PIC16C62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X/9XX Programming Specification (DS30228).

A typical In-Circuit Serial Programming connection is shown in Figure 9-19.

# FIGURE 9-19:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| BCF              | Bit Clear f                                                         | BTFSC            | Bit Test, Skip if Clear                                                   |

|------------------|---------------------------------------------------------------------|------------------|---------------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      | Syntax:          | [label]BTFSC f,b                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$       |

| Operation:       | $0 \rightarrow (f \le b >)$                                         | Operation:       | skip if (f <b>) = 0</b>                                                   |

| Status Affected: | None                                                                | Status Affected: | None                                                                      |

| Encoding:        | 01 00bb bfff ffff                                                   | Encoding:        | 01 10bb bfff ffff                                                         |

| Description:     | Bit 'b' in register 'f' is cleared.                                 | Description:     | If bit 'b' in register 'f' is '0', then the                               |

| Words:           | 1                                                                   |                  | next instruction is skipped.<br>If bit 'b' is '0', then the next instruc- |

| Cycles:          | 1                                                                   |                  | tion fetched during the current                                           |

| Example          | BCF FLAG_REG, 7                                                     |                  | instruction execution is discarded,                                       |

|                  | Before Instruction<br>FLAG_REG = 0xC7                               |                  | and a NOP is executed instead,<br>making this a two-cycle instruction.    |

|                  | After Instruction                                                   | Words:           | 1                                                                         |

|                  | FLAG_REG = 0x47                                                     | Cycles:          | 1(2)                                                                      |

|                  |                                                                     | Example          | here btfsc <b>FLAG,1</b><br>false goto <b>process co</b>                  |

| BSF              | Bit Set f                                                           |                  | TRUE DE                                                                   |

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |                  | •                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                  | Before Instruction<br>PC = address HERE                                   |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |                  | After Instruction<br>if FLAG<1> = 0.                                      |

| Status Affected: | None                                                                |                  | PC = address TRUE                                                         |

| Encoding:        | 01 01bb bfff ffff                                                   |                  | if FLAG<1>=1,<br>PC = address FALSE                                       |

| Description:     | Bit 'b' in register 'f' is set.                                     |                  | PC = address FALSE                                                        |

| Words:           | 1                                                                   |                  |                                                                           |

| Cycles:          | 1                                                                   |                  |                                                                           |

| Example          | BSF FLAG_REG, 7                                                     |                  |                                                                           |

Before Instruction FLAG\_REG = 0x0A After Instruction

FLAG\_REG = 0x8A

| BTFSS            | Bit Test f, Skip if Set                                                                                                                          | CALL             | Call Subroutine                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                              | Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                    |

| Operands:        | $0 \le f \le 127$                                                                                                                                | Operands:        | $0 \leq k \leq 2047$                                                                                                                                                       |

|                  | $0 \le b < 7$                                                                                                                                    | Operation:       | $(PC)$ + 1 $\rightarrow$ TOS,                                                                                                                                              |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                          |                  | $k \rightarrow PC<10:0>$ ,<br>(PCLATH<4:3>) $\rightarrow PC<12:11>$                                                                                                        |

| Status Affected: | None                                                                                                                                             | Status Affected: | None                                                                                                                                                                       |

| Encoding:        | 01 11bb bfff ffff                                                                                                                                | Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next instruc-                         | Description:     | Call Subroutine. First, return<br>address (PC+1) is pushed onto                                                                                                            |

|                  | tion fetched during the current<br>instruction execution, is discarded<br>and a NOP is executed instead,<br>making this a two-cycle instruction. |                  | the stack. The eleven bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. |

| Words:           | 1                                                                                                                                                | Words:           | 1                                                                                                                                                                          |

| Cycles:          | 1(2)                                                                                                                                             | Cycles:          | 2                                                                                                                                                                          |

| Example          | here btfss <b>FLAG,1</b><br>false goto <b>PROCESS_CO</b>                                                                                         | Example          | HERE CALL                                                                                                                                                                  |

|                  | TRUE DE                                                                                                                                          | Liampio          | THER                                                                                                                                                                       |

|                  | Before Instruction<br>PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,<br>PC = address FALSE<br>if FLAG<1> = 1,                         |                  | Before Instruction<br>PC = Address HERE<br>After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                 |

|                  | PC = address TRUE                                                                                                                                | CLRF             | Clear f                                                                                                                                                                    |

|                  |                                                                                                                                                  | Syntax:          | [label] CLRF f                                                                                                                                                             |

|                  |                                                                                                                                                  | Operands:        | $0 \leq f \leq 127$                                                                                                                                                        |

|                  |                                                                                                                                                  | Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$                                                                                                      |

|                  |                                                                                                                                                  | Status Affected: | Z                                                                                                                                                                          |

|                  |                                                                                                                                                  | Encoding:        | 00 0001 1fff ffff                                                                                                                                                          |

|                  |                                                                                                                                                  | Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.                                                                                                          |

|                  |                                                                                                                                                  | Words:           | 1                                                                                                                                                                          |

|                  |                                                                                                                                                  | Cycles:          | 1                                                                                                                                                                          |

|                  |                                                                                                                                                  | Example          | CLRF FLAG_REG                                                                                                                                                              |

|                  |                                                                                                                                                  |                  | Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction                                                                                                                 |

|                  |                                                                                                                                                  |                  | $FLAG_REG = 0x00$<br>Z = 1                                                                                                                                                 |

| MOVF             | Move f                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                    |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                             |

| Status Affected: | Z                                                                                                                                                                                                                                                                                    |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |

| Example          | MOVF FSR, <b>0</b>                                                                                                                                                                                                                                                                   |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |

| MOVWF            | Move W to f                                                                                                                                                                                                                                                                          |

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                    |

| Operation:       | $(W) \rightarrow (f)$                                                                                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                                                                 |

| Encoding:        | 00 0000 1fff ffff                                                                                                                                                                                                                                                                    |

| Description:     | Move data from W register to reg-<br>ister 'f'.                                                                                                                                                                                                                                      |

| Words:           | 1                                                                                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |

| Example          | MOVWF OPTION                                                                                                                                                                                                                                                                         |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F                                                                                                                                                                                                |

|                  | $\begin{array}{rcl} \text{OPTION} &= & 0x4F \\ \text{W} &= & 0x4F \end{array}$                                                                                                                                                                                                       |

| NOP              | No Operation      |     |  |  |  |  |

|------------------|-------------------|-----|--|--|--|--|

| Syntax:          | [ label ]         | NOP |  |  |  |  |

| Operands:        | None              |     |  |  |  |  |

| Operation:       | No operation      |     |  |  |  |  |

| Status Affected: | None              |     |  |  |  |  |

| Encoding:        | 00 0000 0xx0 0000 |     |  |  |  |  |

| Description:     | No operation.     |     |  |  |  |  |

| Words:           | 1                 |     |  |  |  |  |

| Cycles:          | 1                 |     |  |  |  |  |

| Example          | NOP               |     |  |  |  |  |

| OPTION           | Load Option Register                                                                                                                                                                                                                               |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] OPTION                                                                                                                                                                                                                                   |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                               |  |  |  |  |

| Operation:       | $(W) \rightarrow OPTION$                                                                                                                                                                                                                           |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                               |  |  |  |  |

| Encoding:        | 00 0000 0110 0010                                                                                                                                                                                                                                  |  |  |  |  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register.<br>This instruction is supported for<br>code compatibility with PIC16C5X<br>products. Since OPTION is a read-<br>able/writable register, the user can<br>directly address it. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                  |  |  |  |  |

| Example          |                                                                                                                                                                                                                                                    |  |  |  |  |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup><br>products, do not use this<br>instruction.                                                                                                                               |  |  |  |  |

|                  |                                                                                                                                                                                                                                                    |  |  |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                       |  |  |  |  |