Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 96 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621a-20e-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

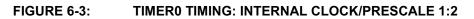

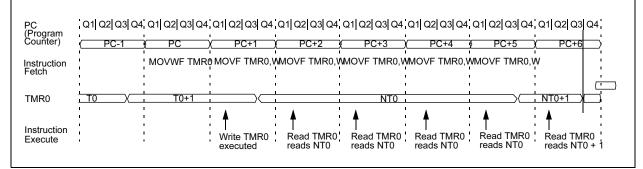

### 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

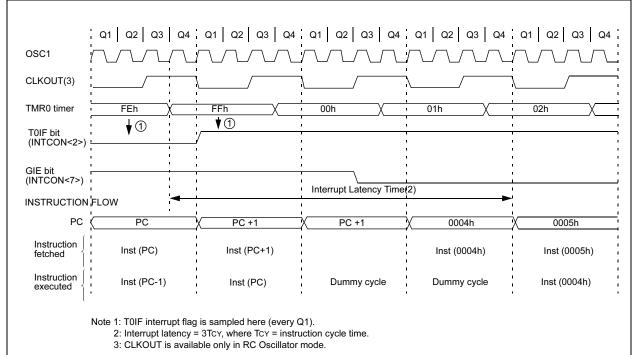

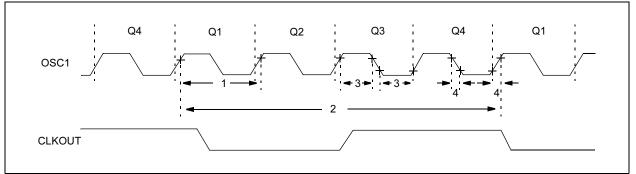

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

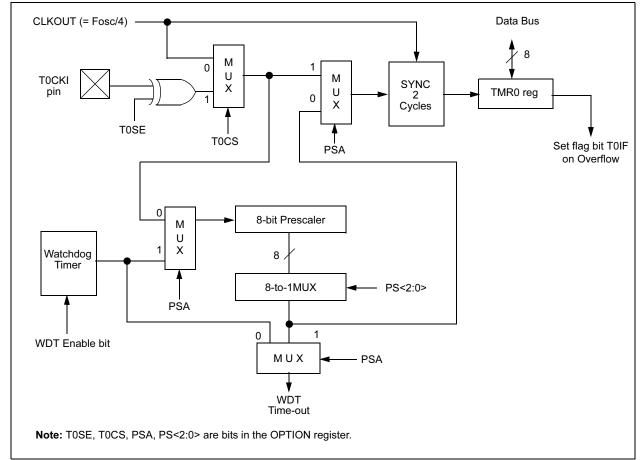

#### 6.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 6-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

#### FIGURE 6-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

NOTES:

The code example in Example 7-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

#### EXAMPLE 7-1: INITIALIZING COMPARATOR MODULE

| MOVLW | 0x03         | ;Init comparator mode             |

|-------|--------------|-----------------------------------|

| MOVWF | CMCON        | ;CM<2:0> = 011                    |

| CLRF  | PORTA        | ;Init PORTA                       |

| BSF   | STATUS, RPO  | ;Select Bank1                     |

| MOVLW | 0x07         | ;Initialize data direction        |

| MOVWF | TRISA        | ;Set RA<2:0> as inputs            |

|       |              | ;RA<4:3> as outputs               |

|       |              | ;TRISA<7:5> always read `0'       |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| CALL  | DELAY 10     | ;10µs delay                       |

| MOVF  | CMCON,F      | ;Read CMCONtoend change condition |

| BCF   | PIR1,CMIF    | ;Clear pending interrupts         |

| BSF   | STATUS, RPO  | ;Select Bank 1                    |

| BSF   | PIE1,CMIE    | ;Enable comparator interrupts     |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| BSF   | INTCON, PEIE | ;Enable peripheral interrupts     |

| BSF   | INTCON, GIE  | ;Global interrupt enable          |

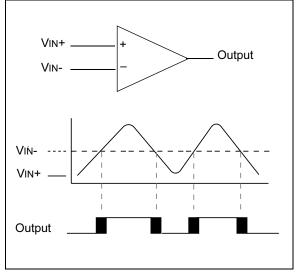

# 7.2 Comparator Operation

A single comparator is shown in Figure 7-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 7-2 represent the uncertainty due to input offsets and response time.

## 7.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator Operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 7-2).

#### 7.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSs and VDD, and can be applied to either pin of the comparator(s).

#### 7.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 10, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 7-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

#### 9.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### REGISTER 9-1: CONFIGURATION WORD (ADDRESS 2007h)

| CP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CP0 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                            | CP1                                 | CP0 <sup>(2)</sup> | CP1     | CP0 <sup>(2)</sup>    |        | BODEN    | CP1     | CP0 <sup>(2)</sup> | PWRTE       | WDTE     | F0SC1 | F0SC0 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------|---------|-----------------------|--------|----------|---------|--------------------|-------------|----------|-------|-------|

| bit 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ļ                                                                                                                                                                                                                                                                                                                             | <u> </u>                            | ļļ                 |         | ļ                     |        | <u> </u> |         | Į                  | <u> </u>    | <u> </u> | ļ     | bit 0 |

| bit 13-8, <b>CP&lt;1:0&gt;:</b> Code protection bit pairs <sup>(2)</sup><br>5-4: Code protection for 2K program memory<br>11 = Program memory code protection off<br>10 = 0400h-07FFh code protected<br>01 = 0200h-07FFh code protected<br>00 = 0000h-07FFh code protected<br>Code protection for 1K program memory<br>11 = Program memory code protection off<br>10 = Program memory code protection off<br>10 = 0200h-03FFh code protected<br>00 = 0000h-03FFh code protected<br>Code protection for 0.5K program memory<br>11 = Program memory code protection off<br>10 = Program memory code protection off |                                                                                                                                                                                                                                                                                                                               |                                     |                    |         |                       |        |          |         |                    |             |          |       |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                               | 0                                   | m memo<br>-01FFh c |         |                       | on off |          |         |                    |             |          |       |       |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                               |                                     | nted: Re           | -       |                       |        |          |         |                    |             |          |       |       |

| bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BO                                                                                                                                                                                                                                                                                                                            | DEN: Br                             | own-out l          | Reset E | nable bit             | (1)    |          |         |                    |             |          |       |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                               | BOR en<br>BOR dis                   |                    |         |                       |        |          |         |                    |             |          |       |       |

| bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 =                                                                                                                                                                                                                                                                                                                           | <b>RTE</b> : Po<br>PWRT o<br>PWRT e |                    | īmer Er | able bit <sup>(</sup> | 1, 3)  |          |         |                    |             |          |       |       |

| bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 =                                                                                                                                                                                                                                                                                                                           | TE: Wat<br>WDT en<br>WDT dis        |                    | mer Ena | able bit              |        |          |         |                    |             |          |       |       |

| bit 1-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>11 = RC oscillator</li> <li>10 = HS oscillator</li> <li>01 = XT oscillator</li> <li>00 = LP oscillator</li> <li>Note 1: Enabling Brown-out Reset automatically enables Power-up Timer (PWRT) regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled anytime Brown-out Detect Reset is</li> </ul> |                                     |                    |         |                       |        |          |         |                    |             |          |       |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>enabled.</li> <li>2: All of the CP&lt;1:0&gt; pairs have to be given the same value to enable the code protection scheme listed.</li> <li>3: Unprogrammed parts default the Power-up Timer disabled.</li> </ul>                                                                                                      |                                     |                    |         |                       |        |          |         |                    |             |          |       |       |

| Legend<br>R = Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | l:<br>adable b                                                                                                                                                                                                                                                                                                                | it                                  |                    | W =     | Writable              | bit    | U =      | Unimple | emented            | bit, read a | s '0'    |       |       |

#### 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC16C62X devices can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

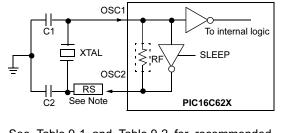

# 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

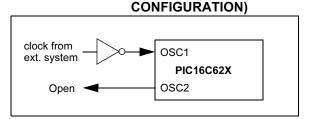

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 9-1). The PIC16C62X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 9-2).

#### FIGURE 9-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

See Table 9-1 and Table 9-2 for recommended values of C1 and C2.

**Note:** A series resistor may be required for AT strip cut crystals.

#### FIGURE 9-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC

# TABLE 9-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| R                                                                                                                                                                                                                                                                                                                 | anges Chara                   | 21                                      |                                         |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|--|--|

| Mode                                                                                                                                                                                                                                                                                                              | Freq                          | <b>0562(C2)</b>                         |                                         |  |  |  |  |  |

| ХТ                                                                                                                                                                                                                                                                                                                | 455 kHz<br>2.0 MHz<br>4.0 MHz | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 82 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |  |  |  |

| HS                                                                                                                                                                                                                                                                                                                | 8.0 MHz<br>16.0 MHz 🔨         | 10-68 pF<br>10-22 pF                    | 10 - 68 pF<br>10 - 22 pF                |  |  |  |  |  |

| Higher capacitance increases the stability of the oscil-<br>lator but also increases the start-up time. These<br>wabes are for design guidance only. Since each<br>resonator has its own characteristics, the user<br>should consult the resonator manufacturer for<br>appropriate values of external components. |                               |                                         |                                         |  |  |  |  |  |

#### TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Freq     | OSC1(C1)    | OSC2(C2)                |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|-------------------------|--|--|--|--|--|

| LP                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32 kHz   | 68 - 100 pF | 68 - 100 pF             |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 200 kHz  | 15 - 30 pF  | 15 - 30 pF              |  |  |  |  |  |

| хт                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 100 kHz  | 68 - 150 pF | 150-300 pF              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2 MHz    | 15 - 30 pF  | 15-30 pF                |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4 MHz    | 15 - 30 pF  | 15-30 pF                |  |  |  |  |  |

| HS                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8 MHz    | 15-30 pF    | <sup>V</sup> 15 - 30 pF |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10 MHz   | 15-30 pF    | 15 - 30 pF              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20 MHz 🔨 | 15-30 pF    | 15 - 30 pF              |  |  |  |  |  |

| 20 MHz 183 30 pF 15 - 30 pF<br>Higher capacitance increases the stability of the<br>oscillator but also increases the start-up time.<br>These values are for design guidance only. Rs may<br>be required in HS mode as well as XT mode to<br>avoid overdriving crystals with low drive level<br>specification. Since each crystal has its own<br>characteristics, the user should consult the crystal<br>manufacturer for appropriate values of external<br>components. |          |             |                         |  |  |  |  |  |

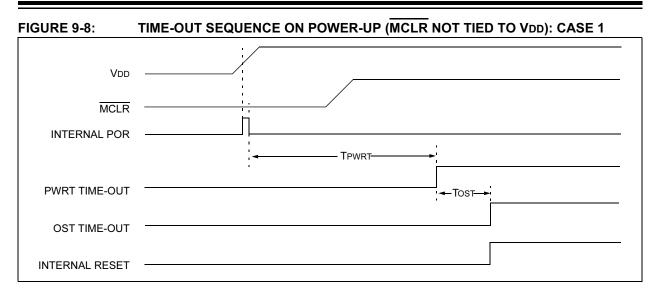

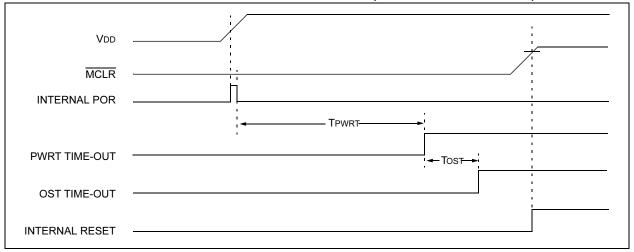

FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

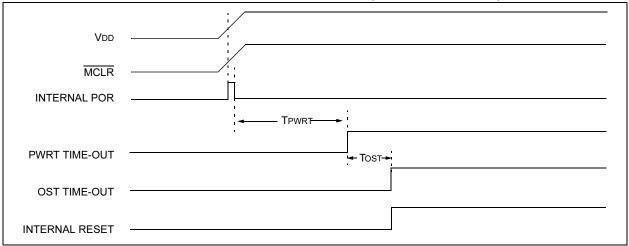

FIGURE 9-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

### 11.9 MPLAB ICE 2000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 2000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers. Software control of the MPLAB ICE 2000 in-circuit emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PICmicro microcontrollers.

The MPLAB ICE 2000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

## 11.10 MPLAB ICE 4000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 4000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for highend PICmicro microcontrollers. Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICD 4000 is a premium emulator system, providing the features of MPLAB ICE 2000, but with increased emulation memory and high speed performance for dsPIC30F and PIC18XXXX devices. Its advanced emulator features include complex triggering and timing, up to 2 Mb of emulation memory, and the ability to view variables in real-time.

The MPLAB ICE 4000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

# 11.11 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low cost, run-time development tool, connecting to the host PC via an RS-232 or high speed USB interface. This tool is based on the FLASH PICmicro MCUs and can be used to develop for these and other PICmicro microcontrollers. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers cost effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single-stepping and watching variables, CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real-time. MPLAB ICD 2 also serves as a development programmer for selected PICmicro devices.

### 11.12 PRO MATE II Universal Device Programmer

The PRO MATE II is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features an LCD display for instructions and error messages and a modular detachable socket assembly to support various package types. In Stand-Alone mode, the PRO MATE II device programmer can read, verify, and program PICmicro devices without a PC connection. It can also set code protection in this mode.

### 11.13 PICSTART Plus Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus development programmer supports most PICmicro devices up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

### 11.14 PICDEM 1 PICmicro Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include analog input, push button switches and eight LEDs.

#### 11.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham

### 11.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessary hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 FLASH microcontrollers.

## 11.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

### 11.18 PICDEM 4 8/14/18-Pin Demonstration Board

The PICDEM 4 can be used to demonstrate the capabilities of the 8-, 14-, and 18-pin PIC16XXXX and PIC18XXXX MCUs, including the PIC16F818/819, PIC16F87/88, PIC16F62XA and the PIC18F1320 family of microcontrollers. PICDEM 4 is intended to showcase the many features of these low pin count parts, including LIN and Motor Control using ECCP. Special provisions are made for low power operation with the supercapacitor circuit, and jumpers allow onboard hardware to be disabled to eliminate current draw in this mode. Included on the demo board are provisions for Crystal, RC or Canned Oscillator modes, a five volt regulator for use with a nine volt wall adapter or battery, DB-9 RS-232 interface, ICD connector for programming via ICSP and development with MPLAB ICD 2, 2x16 liquid crystal display, PCB footprints for H-Bridge motor driver, LIN transceiver and EEPROM. Also included are: header for expansion, eight LEDs, four potentiometers, three push buttons and a prototyping area. Included with the kit is a PIC16F627A and a PIC18F1320. Tutorial firmware is included along with the User's Guide.

# 11.19 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board FLASH memory. A generous prototype area is available for user hardware expansion.

# 12.0 ELECTRICAL SPECIFICATIONS

#### Absolute Maximum Ratings †

| Ambient Temperature under bias                                                                                 | 40° to +125°C                    |

|----------------------------------------------------------------------------------------------------------------|----------------------------------|

| Storage Temperature                                                                                            | 65° to +150°C                    |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                   | 0.6V to VDD +0.6V                |

| Voltage on VDD with respect to Vss                                                                             | 0 to +7.5V                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                   | 0 to +14V                        |

| Voltage on RA4 with respect to Vss                                                                             |                                  |

| Total power Dissipation (Note 1)                                                                               | 1.0W                             |

| Maximum Current out of Vss pin                                                                                 | 300 mA                           |

| Maximum Current into VDD pin                                                                                   | 250 mA                           |

| Input Clamp Current, Iк (Vi <0 or Vi> VDD)                                                                     | ±20 mA                           |

| Output Clamp Current, Iок (Vo <0 or Vo>VDD)                                                                    | ±20 mA                           |

| Maximum Output Current sunk by any I/O pin                                                                     | 25 mA                            |

| Maximum Output Current sourced by any I/O pin                                                                  | 25 mA                            |

| Maximum Current sunk by PORTA and PORTB                                                                        | 200 mA                           |

| Maximum Current sourced by PORTA and PORTB                                                                     | 200 mA                           |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) | ) x IOH} + $\Sigma$ (VOI x IOL). |

2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latchup. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

**† NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

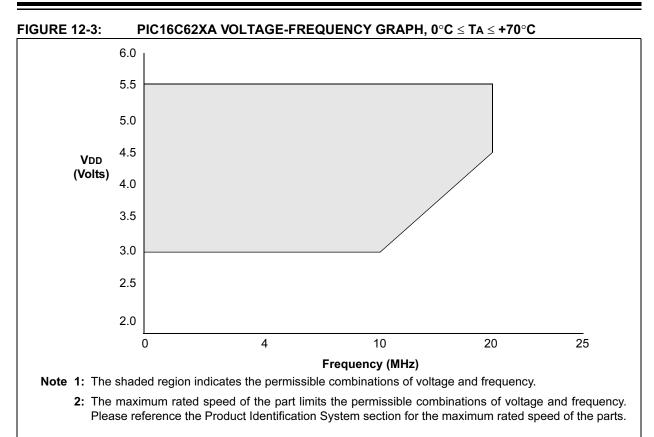

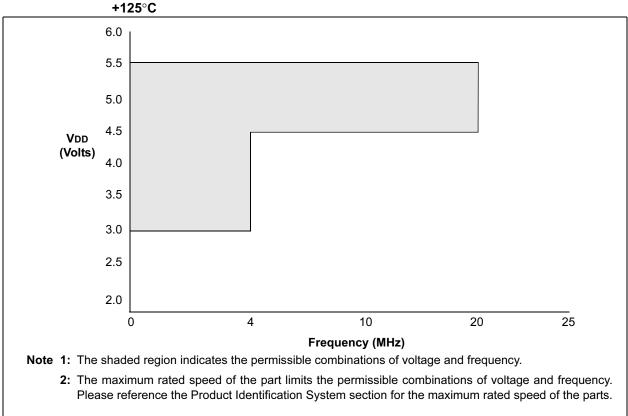

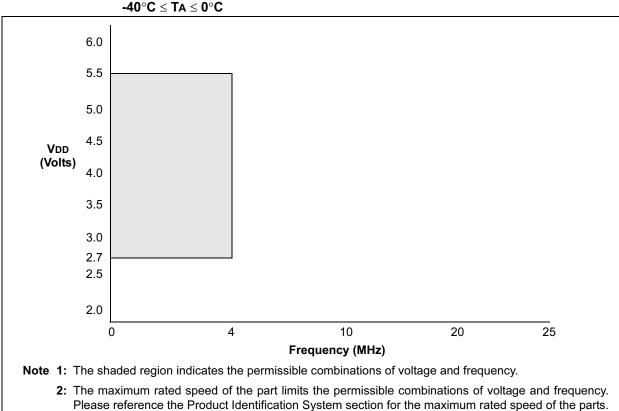

# FIGURE 12-4: PIC16C62XA VOLTAGE-FREQUENCY GRAPH, $-40^{\circ}C \le Ta \le 0^{\circ}C$ , $+70^{\circ}C \le Ta \le +125^{\circ}C$

#### 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended)

| PIC16C62XOperating temperature $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ for incomplete<br>$0^{\circ}C$ $TA \leq +70^{\circ}C$ for complete<br>$-40^{\circ}C$ $TA \leq +70^{\circ}C$ for complete<br>$-40^{\circ}C$ Standard Operating Conditions (unless otherwise)                                                                                                                          | dustrial and mmercial and                  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                | -40°C $\leq$ TA $\leq$ +125°C for extended |  |  |  |  |  |  |

| $\begin{array}{c} \mbox{PIC16LC62X} \\ \mbox{PIC16LC62X} \\ \mbox{Operating temperature} & -40^{\circ}\mbox{C} & \leq \mbox{TA} \leq +85^{\circ}\mbox{C for inc} \\ & 0^{\circ}\mbox{C} & \leq \mbox{TA} \leq +70^{\circ}\mbox{C for co} \\ & -40^{\circ}\mbox{C} & \leq \mbox{TA} \leq +125^{\circ}\mbox{C for e} \\ & \mbox{Operating voltage VDD range is the PIC16C62X range} \end{array}$ | dustrial and<br>mmercial and<br>extended   |  |  |  |  |  |  |

| Param.         Sym         Characteristic         Min         Typ†         Max         Units         Conditio           No.                Conditio                                                                                                                                                                                                                                            | ons                                        |  |  |  |  |  |  |

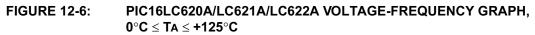

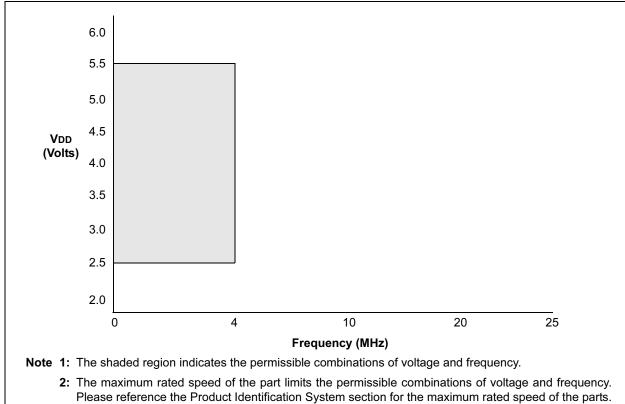

| D001         VDD         Supply Voltage         3.0         —         6.0         V         See Figures 12-1, 12-2, 12-3                                                                                                                                                                                                                                                                       | 3, 12-4, and 12-5                          |  |  |  |  |  |  |

| D001         VDD         Supply Voltage         2.5         —         6.0         V         See Figures 12-1, 12-2, 12-3                                                                                                                                                                                                                                                                       | 3, 12-4, and 12-5                          |  |  |  |  |  |  |

| D002 VDR RAM Data Retention Voltage <sup>(1)</sup> — 1.5* — V Device in SLEEP mode                                                                                                                                                                                                                                                                                                             |                                            |  |  |  |  |  |  |

| D002 VDR RAM Data Retention Voltage <sup>(1)</sup> — 1.5* — V Device in SLEEP mode                                                                                                                                                                                                                                                                                                             |                                            |  |  |  |  |  |  |

| D003         VPOR         VDD start voltage to ensure         —         Vss         —         V         See section on Power-on Report                                                                                                                                                                                                                                                         | eset for details                           |  |  |  |  |  |  |

| D003         VPOR         VDD start voltage to<br>ensure Power-on Reset         —         Vss         —         V         See section on Power-on Reset                                                                                                                                                                                                                                        | eset for details                           |  |  |  |  |  |  |

| D004         SVDD         VDD rise rate to ensure<br>Power-on Reset         0.05*         —         —         V/ms         See section on Power-on Reset                                                                                                                                                                                                                                       | eset for details                           |  |  |  |  |  |  |

| D004     SVDD     VDD rise rate to ensure     0.05*     —     —     V/ms     See section on Power-on Reset                                                                                                                                                                                                                                                                                     | eset for details                           |  |  |  |  |  |  |

| D005 VBOR Brown-out Detect Voltage 3.7 4.0 4.3 V BOREN configuration bit is a                                                                                                                                                                                                                                                                                                                  | cleared                                    |  |  |  |  |  |  |

| D005 VBOR Brown-out Detect Voltage 3.7 4.0 4.3 V BOREN configuration bit is a                                                                                                                                                                                                                                                                                                                  | cleared                                    |  |  |  |  |  |  |

| D010 IDD Supply Current <sup>(2)</sup> - 1.8 3.3 mA Fosc = 4 MHz, VDD = 5.5V, mode, (Note 4)*                                                                                                                                                                                                                                                                                                  |                                            |  |  |  |  |  |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                        | WD1 disabled, LP                           |  |  |  |  |  |  |

| 9.0 20 mA Fosc = 20 MHz, VDD = 5.5V mode                                                                                                                                                                                                                                                                                                                                                       | , WDT disabled, HS                         |  |  |  |  |  |  |

| D010 IDD Supply Current <sup>(2)</sup> $-$ 1.4 2.5 mA Fosc = 2.0 MHz, VDD = 3.0 V mode (Note 4)                                                                                                                                                                                                                                                                                                | /, WDT disabled, XT                        |  |  |  |  |  |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                        | WDT disabled, LP                           |  |  |  |  |  |  |

| D020 IPD Power-down Current <sup>(3)</sup> — 1.0 2.5 $\mu$ A VDD=4.0V, WDT disabled (125°C)                                                                                                                                                                                                                                                                                                    |                                            |  |  |  |  |  |  |

| D020 IPD Power-down Current <sup>(3)</sup> — 0.7 2 $\mu$ A VDD=3.0V, WDT disabled                                                                                                                                                                                                                                                                                                              |                                            |  |  |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

$\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

| PIC16CR62XA-04<br>PIC16CR62XA-20 | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                             |  |  |  |  |  |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| PIC16LCR62XA-04                  | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq$ TA $\leq$ +85°C for industrial and $0^{\circ}$ C $\leq$ TA $\leq$ +70°C for commercial and $-40^{\circ}$ C $<$ TA $\leq$ +125°C for extended |  |  |  |  |  |  |  |

| Param. Sym Characteristic No.    | Min Typ† Max Units Conditions                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in k $\Omega$ .

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

#### 12.4 DC Characteristics: PIC16C62X/C62XA/CR62XA (Commercial, Industrial, Extended) PIC16LC62X/LC62XA/LCR62XA (Commercial, Industrial, Extended)

| PIC16C                    | 62X/C | 62XA/CR62XA                               |                            |      |                  |       | hs (unless otherwise stated)<br>$\leq TA \leq +85^{\circ}C$ for industrial and<br>$\leq TA \leq +70^{\circ}C$ for commercial and                               |

|---------------------------|-------|-------------------------------------------|----------------------------|------|------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           |       |                                           |                            |      |                  | -40°C | $\leq TA \leq +125^{\circ}C$ for extended                                                                                                                      |

| PIC16LC62X/LC62XA/LCR62XA |       |                                           | Operating temperature      |      |                  |       | ns (unless otherwise stated)<br>$\leq$ TA $\leq$ +85°C for industrial and<br>$\leq$ TA $\leq$ +70°C for commercial and<br>$\leq$ TA $\leq$ +125°C for extended |

| Param.<br>No.             | Sym   | Characteristic                            | Min                        | Тур† | Мах              | Units | Conditions                                                                                                                                                     |

|                           | VIL   | Input Low Voltage                         |                            |      |                  |       |                                                                                                                                                                |

|                           |       | I/O ports                                 |                            |      |                  |       |                                                                                                                                                                |

| D030                      |       | with TTL buffer                           | Vss                        | —    | 0.8V<br>0.15 Vdd | V     | VDD = 4.5V to 5.5V<br>otherwise                                                                                                                                |

| D031                      |       | with Schmitt Trigger input                | Vss                        | —    | 0.2 VDD          | V     |                                                                                                                                                                |

| D032                      |       | MCLR, RA4/T0CKI,OSC1 (in RC mode)         | Vss                        | —    | 0.2 VDD          | V     | (Note 1)                                                                                                                                                       |

| D033                      |       | OSC1 (in XT and HS)                       | Vss                        | _    | 0.3 VDD          | V     |                                                                                                                                                                |

|                           |       | OSC1 (in LP)                              | Vss                        | —    | 0.6 Vdd-<br>1.0  | V     |                                                                                                                                                                |

|                           | VIL   | Input Low Voltage                         |                            |      |                  |       |                                                                                                                                                                |

|                           |       | I/O ports                                 |                            |      |                  |       |                                                                                                                                                                |

| D030                      |       | with TTL buffer                           | Vss                        | -    | 0.8V<br>0.15 VDD | V     | VDD = 4.5V to 5.5V<br>otherwise                                                                                                                                |

| D031                      |       | with Schmitt Trigger input                | Vss                        | —    | 0.2 Vdd          | V     |                                                                                                                                                                |

| D032                      |       | MCLR, RA4/T0CKI,OSC1 (in RC mode)         | Vss                        | —    | 0.2 VDD          | V     | (Note 1)                                                                                                                                                       |

| D033                      |       | OSC1 (in XT and HS)                       | Vss                        | —    | 0.3 VDD          | V     |                                                                                                                                                                |

|                           |       | OSC1 (in LP)                              | Vss                        | _    | 0.6 Vdd-<br>1.0  | V     |                                                                                                                                                                |

|                           | VIH   | Input High Voltage                        |                            |      |                  |       |                                                                                                                                                                |

|                           |       | I/O ports                                 |                            |      |                  |       |                                                                                                                                                                |

| D040                      |       | with TTL buffer                           | 2.0V<br>0.25 VDD<br>+ 0.8V | _    | Vdd<br>Vdd       | V     | V <sub>DD</sub> = 4.5V to 5.5V<br>otherwise                                                                                                                    |

| D041                      |       | with Schmitt Trigger input                | 0.8 Vdd                    | _    | VDD              |       |                                                                                                                                                                |

| D042                      |       | MCLR RA4/T0CKI                            | 0.8 VDD                    | _    | VDD              | V     |                                                                                                                                                                |

| D043<br>D043A             |       | OSC1 (XT, HS and LP)<br>OSC1 (in RC mode) | 0.7 Vdd<br>0.9 Vdd         | _    | VDD              | V     | (Note 1)                                                                                                                                                       |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16C62X(A) be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

#### 12.9 Timing Diagrams and Specifications

#### FIGURE 12-12: EXTERNAL CLOCK TIMING

#### TABLE 12-3: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                          | Min  | Тур†   | Max    | Units | Conditions                         |

|------------------|-------|-----------------------------------------|------|--------|--------|-------|------------------------------------|

| 1A               | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC   | —      | 4      | MHz   | XT and RC Osc mode, VDD=5.0V       |

|                  |       |                                         | DC   | _      | 20     | MHz   | HS Osc mode                        |

|                  |       |                                         | DC   | —      | 200    | kHz   | LP Osc mode                        |

|                  |       | Oscillator Frequency <sup>(1)</sup>     | DC   | —      | 4      | MHz   | RC Osc mode, VDD=5.0V              |

|                  |       |                                         | 0.1  | —      | 4      | MHz   | XT Osc mode                        |

|                  |       |                                         | 1    | —      | 20     | MHz   | HS Osc mode                        |

|                  |       |                                         | DC   | —      | 200    | kHz   | LP Osc mode                        |

| 1                | Tosc  | External CLKIN Period <sup>(1)</sup>    | 250  | —      | _      | ns    | XT and RC Osc mode                 |

|                  |       |                                         | 50   | —      | —      | ns    | HS Osc mode                        |

|                  |       |                                         | 5    | —      | —      | μs    | LP Osc mode                        |

|                  |       | Oscillator Period <sup>(1)</sup>        | 250  | —      | _      | ns    | RC Osc mode                        |

|                  |       |                                         | 250  | —      | 10,000 | ns    | XT Osc mode                        |

|                  |       |                                         | 50   | —      | 1,000  | ns    | HS Osc mode                        |

|                  |       |                                         | 5    | —      | —      | μs    | LP Osc mode                        |

| 2                | TCY   | Instruction Cycle Time <sup>(1)</sup>   | 1.0  | Fosc/4 | DC     | μS    | Tcys=Fosc/4                        |

| 3*               | TosL, | External Clock in (OSC1) High or        | 100* | —      | _      | ns    | XT oscillator, Tosc L/H duty cycle |

|                  | TosH  | Low Time                                | 2*   | —      | —      | μs    | LP oscillator, Tosc L/H duty cycle |

|                  |       |                                         | 20*  | _      | —      | ns    | HS oscillator, Tosc L/H duty cycle |

| 4*               | TosR, | External Clock in (OSC1) Rise or        | 25*  | _      | _      | ns    | XT oscillator                      |

|                  | TosF  | Fall Time                               | 50*  | —      | —      | ns    | LP oscillator                      |

|                  |       |                                         | 15*  | —      | —      | ns    | HS oscillator                      |

**2:** \* These parameters are characterized but not tested.

3: † Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

# 13.0 DEVICE CHARACTERIZATION INFORMATION

The graphs and tables provided in this section are for design guidance and are not tested. In some graphs or tables, the data presented is outside specified operating range (e.g., outside specified VDD range). This is for information only and devices will operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution, while "max" or "min" represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation.

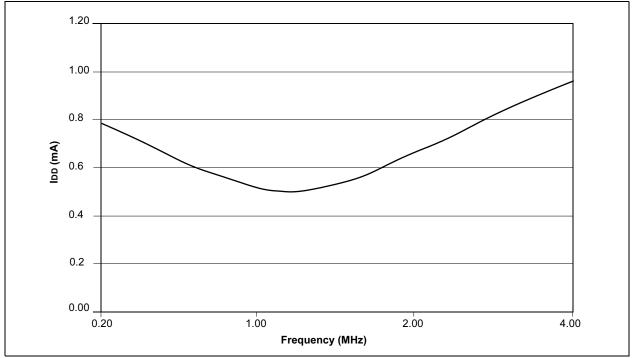

FIGURE 13-1: IDD VS. FREQUENCY (XT MODE, VDD = 5.5V)

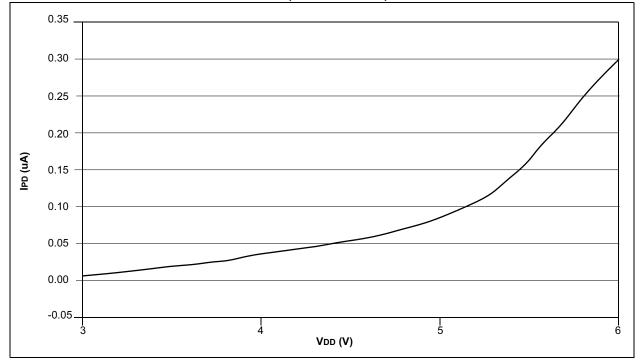

FIGURE 13-2: PIC16C622A IPD VS. VDD (WDT DISABLE)

© 2003 Microchip Technology Inc.

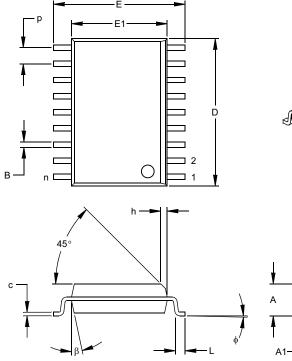

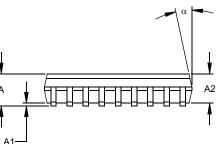

## 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

|                          |        | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|--------|---------|------|-------------|-------|-------|-------|

| Dimension                | Limits | MIN     | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins           | n      |         | 18   |             |       | 18    |       |

| Pitch                    | р      |         | .050 |             |       | 1.27  |       |

| Overall Height           | Α      | .093    | .099 | .104        | 2.36  | 2.50  | 2.64  |

| Molded Package Thickness | A2     | .088    | .091 | .094        | 2.24  | 2.31  | 2.39  |

| Standoff §               | A1     | .004    | .008 | .012        | 0.10  | 0.20  | 0.30  |

| Overall Width            | Е      | .394    | .407 | .420        | 10.01 | 10.34 | 10.67 |

| Molded Package Width     | E1     | .291    | .295 | .299        | 7.39  | 7.49  | 7.59  |

| Overall Length           | D      | .446    | .454 | .462        | 11.33 | 11.53 | 11.73 |

| Chamfer Distance         | h      | .010    | .020 | .029        | 0.25  | 0.50  | 0.74  |

| Foot Length              | L      | .016    | .033 | .050        | 0.41  | 0.84  | 1.27  |

| Foot Angle               | ¢      | 0       | 4    | 8           | 0     | 4     | 8     |

| Lead Thickness           | С      | .009    | .011 | .012        | 0.23  | 0.27  | 0.30  |

| Lead Width               | В      | .014    | .017 | .020        | 0.36  | 0.42  | 0.51  |

| Mold Draft Angle Top     | α      | 0       | 12   | 15          | 0     | 12    | 15    |

| Mold Draft Angle Bottom  | β      | 0       | 12   | 15          | 0     | 12    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-051

NOTES: