Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 96 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

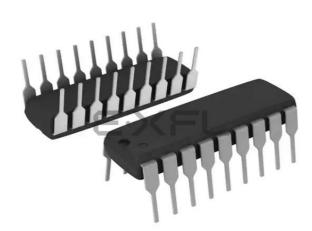

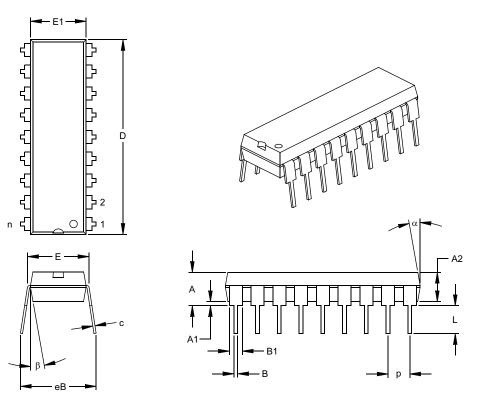

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621a-20i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART, PRO MATE and PowerSmart are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Accuron, Application Maestro, dsPIC, dsPICDEM, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICkit, PICDEM, PICDEM.net, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPIC, Select Mode, SmartSensor, SmartShunt, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

# **PIC16C62X**

### **EPROM-Based 8-Bit CMOS Microcontrollers**

#### Devices included in this data sheet:

Referred to collectively as PIC16C62X.

- PIC16C620 PIC16C620A

- PIC16C621 PIC16C621A

- PIC16C622 PIC16C622A

- PIC16CR620A

#### **High Performance RISC CPU:**

- Only 35 instructions to learn

- All single cycle instructions (200 ns), except for program branches which are two-cycle

- Operating speed:

- DC 40 MHz clock input

- DC 100 ns instruction cycle

| Device      | Program<br>Memory | Data<br>Memory |

|-------------|-------------------|----------------|

| PIC16C620   | 512               | 80             |

| PIC16C620A  | 512               | 96             |

| PIC16CR620A | 512               | 96             |

| PIC16C621   | 1K                | 80             |

| PIC16C621A  | 1K                | 96             |

| PIC16C622   | 2K                | 128            |

| PIC16C622A  | 2K                | 128            |

· Interrupt capability

- 16 special function hardware registers

- 8-level deep hardware stack

- Direct, Indirect and Relative addressing modes

#### **Peripheral Features:**

- 13 I/O pins with individual direction control

- High current sink/source for direct LED drive

- Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VREF) module

- Programmable input multiplexing from device inputs and internal voltage reference

- Comparator outputs can be output signals

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

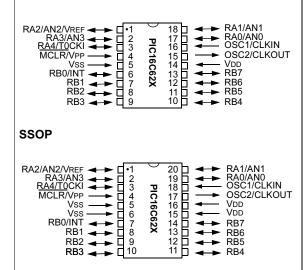

#### Pin Diagrams

#### PDIP, SOIC, Windowed CERDIP

#### **Special Microcontroller Features:**

- · Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- · Programmable code protection

- · Power saving SLEEP mode

- Selectable oscillator options

- Serial in-circuit programming (via two pins)

- Four user programmable ID locations

#### **CMOS Technology:**

- Low power, high speed CMOS EPROM technology

- Fully static design

- · Wide operating range

- 2.5V to 5.5V

- Commercial, industrial and extended temperature range

- Low power consumption

- < 2.0 mA @ 5.0V, 4.0 MHz

- 15 μA typical @ 3.0V, 32 kHz

- < 1.0 μA typical standby current @ 3.0V

#### FIGURE 4-4: DATA MEMORY MAP FOR THE PIC16C620/621

| File     |                                  |                     | File        |  |  |  |

|----------|----------------------------------|---------------------|-------------|--|--|--|

| Address  | 3                                |                     | Address     |  |  |  |

| 00h      | INDF <sup>(1)</sup>              | INDF <sup>(1)</sup> | 80h         |  |  |  |

| 01h      | TMR0                             | OPTION              | 81h         |  |  |  |

| 02h      | PCL                              | PCL                 | 82h         |  |  |  |

| 03h      | STATUS                           | STATUS              | 83h         |  |  |  |

| 04h      | FSR                              | FSR                 | 84h         |  |  |  |

| 05h      | PORTA                            | TRISA               | 85h         |  |  |  |

| 06h      | PORTB                            | TRISB               | 86h         |  |  |  |

| 07h      |                                  |                     | 87h         |  |  |  |

| 08h      |                                  |                     | 88h         |  |  |  |

| 09h      |                                  |                     | 89h         |  |  |  |

| 0Ah      | PCLATH                           | PCLATH              | 8Ah         |  |  |  |

| 0Bh      | INTCON                           | INTCON              | 8Bh         |  |  |  |

| 0Ch      | PIR1                             | PIE1                | 8Ch         |  |  |  |

| 0Dh      |                                  |                     | 8Dh         |  |  |  |

| 0Eh      |                                  | PCON                | 8Eh         |  |  |  |

| 0Fh      |                                  |                     | 8Fh         |  |  |  |

| 10h      |                                  |                     | 90h         |  |  |  |

| 11h      |                                  |                     | 91h         |  |  |  |

| 12h      |                                  |                     | 92h         |  |  |  |

| 13h      |                                  |                     | 93h         |  |  |  |

| 14h      |                                  |                     | 94h         |  |  |  |

| 15h      |                                  |                     | 95h         |  |  |  |

| 16h      |                                  |                     | 96h         |  |  |  |

| 17h      |                                  |                     | 97h         |  |  |  |

| 18h      |                                  |                     | 98h         |  |  |  |

| 19h      |                                  |                     | 99h         |  |  |  |

| 1Ah      |                                  |                     | 9Ah         |  |  |  |

| 1Bh      |                                  |                     | 9Bh         |  |  |  |

| 1Ch      |                                  |                     | 9Ch         |  |  |  |

| 1Dh      |                                  |                     | 9Dh         |  |  |  |

| 1Eh      |                                  |                     | 9Eh         |  |  |  |

| 1Fh      | CMCON                            | VRCON               | 9Fh         |  |  |  |

| 20h      |                                  | _                   | A0h         |  |  |  |

|          | General                          |                     |             |  |  |  |

|          | Purpose<br>Register              |                     |             |  |  |  |

| 6Fh      | 5                                |                     |             |  |  |  |

| 70h      |                                  |                     |             |  |  |  |

|          |                                  |                     |             |  |  |  |

|          |                                  |                     |             |  |  |  |

|          |                                  |                     |             |  |  |  |

| 7Fh      |                                  |                     | FFh         |  |  |  |

|          | Bank 0                           | Bank 1              |             |  |  |  |

| <b>—</b> |                                  | 1 4                 |             |  |  |  |

| Unimp    | plemented data me                | mory locations, r   | ead as '0'. |  |  |  |

| Note 1:  | Note 1: Not a physical register. |                     |             |  |  |  |

|          |                                  |                     |             |  |  |  |

|          |                                  |                     |             |  |  |  |

#### FIGURE 4-5:

#### DATA MEMORY MAP FOR THE PIC16C622

|                 | 1116                |                     |                 |

|-----------------|---------------------|---------------------|-----------------|

| File<br>Address | 8                   |                     | File<br>Address |

| 00h             | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |

| 01h             | TMR0                | OPTION              | 81h             |

| 02h             | PCL                 | PCL                 | 82h             |

| 03h             | STATUS              | STATUS              | 83h             |

| 04h             | FSR                 | FSR                 | 84h             |

| 05h             | PORTA               | TRISA               | 85h             |

| 06h             | PORTB               | TRISB               | 86h             |

| 00h             | TOILID              | TRIOD               | 87h             |

| 07h<br>08h      |                     |                     | 88h             |

| 00h             |                     |                     | 89h             |

| 03h<br>0Ah      | PCLATH              | PCLATH              | 8Ah             |

| 0An<br>0Bh      | INTCON              | INTCON              | 8Bh             |

| 0Dh             | PIR1                | PIE1                | 8Ch             |

| 0Ch<br>0Dh      | PIRI                | PIEI                | 8Dh             |

|                 |                     | PCON                |                 |

| 0Eh<br>0Fh      |                     | PCON                | 8Eh             |

|                 |                     |                     | 8Fh             |

| 10h             |                     |                     | 90h             |

| 11h             |                     |                     | 91h             |

| 12h             |                     |                     | 92h             |

| 13h             |                     |                     | 93h             |

| 14h             |                     |                     | 94h             |

| 15h             |                     |                     | 95h             |

| 16h             |                     |                     | 96h             |

| 17h             |                     |                     | 97h             |

| 18h             |                     |                     | 98h             |

| 19h             |                     |                     | 99h             |

| 1Ah             |                     |                     | 9Ah             |

| 1Bh             |                     |                     | 9Bh             |

| 1Ch             |                     |                     | 9Ch             |

| 1Dh             |                     |                     | 9Dh             |

| 1Eh             |                     |                     | 9Eh             |

| 1Fh             | CMCON               | VRCON               | 9Fh             |

| 20h             |                     |                     | A0h             |

|                 | General<br>Purpose  | General<br>Purpose  |                 |

|                 | Register            | Register            |                 |

|                 | 0                   | 5                   | BFh             |

|                 |                     |                     | C0h             |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

| 7Fh             |                     |                     | FFh             |

| , , , , , ,     | Bank 0              | Bank 1              |                 |

|                 |                     |                     |                 |

| Unim            | plemented data me   | mory locations, re  | ad as '0'.      |

| Note 1:         | Not a physical re   | aister              |                 |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

### FIGURE 4-6: DATA MEMORY MAP FOR THE PIC16C620A/CR620A/621A

|                           | 11010002                       |                     | - 17 (     |  |  |

|---------------------------|--------------------------------|---------------------|------------|--|--|

| File File Address Address |                                |                     |            |  |  |

| 00h                       | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup> | 80h        |  |  |

| 01h                       | TMR0                           | OPTION              | 81h        |  |  |

| 02h                       | PCL                            | PCL                 | 82h        |  |  |

| 03h                       | STATUS                         | STATUS              | 83h        |  |  |

| 04h                       | FSR                            | FSR                 | 84h        |  |  |

| 05h                       | PORTA                          | TRISA               | 85h        |  |  |

| 06h                       | PORTB                          | TRISB               | 86h        |  |  |

| 07h                       |                                |                     | 87h        |  |  |

| 08h                       |                                |                     | 88h        |  |  |

| 09h                       |                                |                     | 89h        |  |  |

| 0Ah                       | PCLATH                         | PCLATH              | 8Ah        |  |  |

| 0Bh                       | INTCON                         | INTCON              | 8Bh        |  |  |

| 0Ch                       | PIR1                           | PIE1                | 8Ch        |  |  |

| 0Dh                       |                                |                     | 8Dh        |  |  |

| 0Eh                       |                                | PCON                | 8Eh        |  |  |

| 0Fh                       |                                |                     | 8Fh        |  |  |

| 10h                       |                                |                     | 90h        |  |  |

| 11h                       |                                |                     | 91h        |  |  |

| 12h                       |                                |                     | 92h        |  |  |

| 13h                       |                                |                     | 93h        |  |  |

| 14h                       |                                |                     | 94h        |  |  |

| 15h                       |                                |                     | 95h        |  |  |

| 16h                       |                                |                     | 96h        |  |  |

| 17h                       |                                |                     | 97h        |  |  |

| 18h                       |                                |                     | 98h        |  |  |

| 19h                       |                                |                     | 99h        |  |  |

| 1Ah                       |                                |                     | 9Ah        |  |  |

| 1Bh                       |                                |                     | 9Bh        |  |  |

| 1Ch                       |                                |                     | 9Ch        |  |  |

| 1Dh                       |                                |                     | 9Dh        |  |  |

| 1Eh                       |                                |                     | 9Eh        |  |  |

| 1Fh                       | CMCON                          | VRCON               | 9Fh        |  |  |

| 20h                       | General<br>Purpose<br>Register |                     | A0h        |  |  |

| 6Fh                       |                                |                     |            |  |  |

| 70h                       | General                        |                     | F0h        |  |  |

|                           | Purpose<br>Register            | Accesses<br>70h-7Fh | FFh        |  |  |

| 7Fh Bank 0 Bank 1         |                                |                     |            |  |  |

| Unimp                     | lemented data mer              | mory locations, rea | ad as '0'. |  |  |

| Note 1:                   | Not a physical re              | gister.             |            |  |  |

|                           |                                |                     |            |  |  |

#### FIGURE 4-7: DATA MEMORY MAP FOR THE PIC16C622A

|                                         | THE PICTOCOZZA      |                     |            |  |  |  |

|-----------------------------------------|---------------------|---------------------|------------|--|--|--|

| File F<br>Address Add                   |                     |                     |            |  |  |  |

| 00h                                     | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h        |  |  |  |

| 01h                                     | TMR0                | OPTION              | 81h        |  |  |  |

| 02h                                     | PCL                 | PCL                 | 82h        |  |  |  |

| 03h                                     | STATUS              | STATUS              | 83h        |  |  |  |

| 04h                                     | FSR                 | FSR                 | 84h        |  |  |  |

| 05h                                     | PORTA               | TRISA               | 85h        |  |  |  |

| 06h                                     | PORTB               | TRISB               | 86h        |  |  |  |

| 07h                                     |                     |                     | 87h        |  |  |  |

| 08h                                     |                     |                     | 88h        |  |  |  |

| 09h                                     |                     |                     | 89h        |  |  |  |

| 0Ah                                     | PCLATH              | PCLATH              | 8Ah        |  |  |  |

| 0Bh                                     | INTCON              | INTCON              | 8Bh        |  |  |  |

| 0Ch                                     | PIR1                | PIE1                | 8Ch        |  |  |  |

| 0Dh                                     |                     |                     | 8Dh        |  |  |  |

| 0Eh                                     |                     | PCON                | 8Eh        |  |  |  |

| 0Fh                                     |                     |                     | 8Fh        |  |  |  |

| 10h                                     |                     |                     | 90h        |  |  |  |

| 11h                                     |                     |                     | 91h        |  |  |  |

| 12h                                     |                     |                     | 92h        |  |  |  |

| 13h                                     |                     |                     | 93h        |  |  |  |

| 14h                                     |                     |                     | 94h        |  |  |  |

| 15h                                     |                     |                     | 95h        |  |  |  |

| 16h                                     |                     |                     | 96h        |  |  |  |

| 17h                                     |                     |                     | 97h        |  |  |  |

| 18h                                     |                     |                     | 98h        |  |  |  |

| 19h                                     |                     |                     | 99h        |  |  |  |

| 1Ah                                     |                     |                     | 9Ah        |  |  |  |

| 1Bh                                     |                     |                     | 9Bh        |  |  |  |

| 1Ch                                     |                     |                     | 9Ch        |  |  |  |

| 1Dh                                     |                     |                     | 9Dh        |  |  |  |

| 1Eh                                     |                     |                     | 9Eh        |  |  |  |

| 1Fh                                     | CMCON               | VRCON               | 9Fh        |  |  |  |

| 20h                                     |                     |                     | A0h        |  |  |  |

|                                         | General             | General             | Aon        |  |  |  |

|                                         | Purpose<br>Register | Purpose<br>Register |            |  |  |  |

|                                         | rtegister           | rtegister           | BFh        |  |  |  |

|                                         |                     |                     | C0h        |  |  |  |

| 0.51                                    |                     |                     |            |  |  |  |

| 6Fh                                     | 0                   |                     | F0h        |  |  |  |

| 70h                                     | General<br>Purpose  | Accesses            |            |  |  |  |

| 754                                     | Register            | 70h-7Fh             | FFh        |  |  |  |

| /rn                                     | 7Fh Bank 0 Bank 1   |                     |            |  |  |  |

|                                         |                     |                     |            |  |  |  |

| Unimp                                   | plemented data me   | mory locations, re  | ad as '0'. |  |  |  |

| <b>Note 1:</b> Not a physical register. |                     |                     |            |  |  |  |

#### **OPTION Register** 4.2.2.2

The OPTION register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|

|       | TMR0, assign the prescaler to the WDT     |  |  |  |  |  |

|       | (PSA = 1).                                |  |  |  |  |  |

|         | R/W-1                    | R/W-1                          | R/W-1                         | R/W-1                        | R/W-1         | R/W-1 | R/W-1 | R/W-1 |

|---------|--------------------------|--------------------------------|-------------------------------|------------------------------|---------------|-------|-------|-------|

|         | RBPU                     | INTEDG                         | TOCS                          | TOSE                         | PSA           | PS2   | PS1   | PS0   |

|         | bit 7                    |                                |                               |                              |               | •     |       | bit 0 |

| bit 7   | RBPU: PO                 | RTB Pull-u                     | p Enable bi                   | it                           |               |       |       |       |

|         |                          | 3 pull-ups ai<br>3 pull-ups ai |                               | y individual                 | port latch va | alues |       |       |

| bit 6   | INTEDG: I                | nterrupt Edg                   | e Select bit                  | -                            |               |       |       |       |

|         |                          |                                | edge of RB0<br>edge of RB0    |                              |               |       |       |       |

| bit 5   | TOCS: TMI                | R0 Clock Sc                    | ource Select                  | bit                          |               |       |       |       |

|         |                          | ion on RA4/<br>Il instruction  | T0CKI pin<br>cycle clock      | (CLKOUT)                     |               |       |       |       |

| bit 4   | TOSE: TM                 | R0 Source E                    | Edge Select                   | bit                          |               |       |       |       |

|         |                          |                                |                               | ition on RA4<br>ition on RA4 |               |       |       |       |

| bit 3   | PSA: Pres                | caler Assigr                   | iment bit                     |                              | -             |       |       |       |

|         |                          |                                | ned to the W<br>ned to the Ti | DT<br>mer0 module            | Э             |       |       |       |

| bit 2-0 | <b>PS&lt;2:0&gt;</b> : F | Prescaler Ra                   | ate Select bi                 | ts                           |               |       |       |       |

|         | E                        | Bit Value T                    | MR0 Rate                      | WDT Rate                     |               |       |       |       |

|         | -                        | 0000001                        | 1:2<br>1:4                    | 1:1<br>1:2                   |               |       |       |       |

|         |                          | 010<br>011                     | 1 : 8<br>1 : 16               | 1:4<br>1:8                   |               |       |       |       |

|         |                          | 100                            | 1:32                          | 1:16                         |               |       |       |       |

|         |                          | 101                            | 1:64                          | 1:32                         |               |       |       |       |

|         |                          | 110                            | 1:128                         | 1:64                         |               |       |       |       |

|         |                          | 111                            | 1:256                         | 1 : 128                      |               |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 4.2.2.6 PCON Register

The PCON register contains flag bits to differentiate between a Power-on Reset, an external MCLR Reset, WDT Reset or a Brown-out Reset.

| Note: | BOR is unknown on Power-on Reset. It        |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|

|       | must then be set by the user and checked    |  |  |  |  |  |  |  |

|       | on subsequent RESETS to see if BOR is       |  |  |  |  |  |  |  |

|       | cleared, indicating a brown-out has         |  |  |  |  |  |  |  |

|       | occurred. The BOR STATUS bit is a "don't    |  |  |  |  |  |  |  |

|       | care" and is not necessarily predictable if |  |  |  |  |  |  |  |

|       | the brown-out circuit is disabled (by       |  |  |  |  |  |  |  |

|       | programming BODEN bit in the                |  |  |  |  |  |  |  |

|       | Configuration word).                        |  |  |  |  |  |  |  |

#### REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

|   | U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|---|-------|-----|-----|-----|-----|-----|-------|-------|

| ſ | _     | —   | —   | —   | —   | —   | POR   | BOR   |

| - | bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR**: Power-on Reset STATUS bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 **BOR**: Brown-out Reset STATUS bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Name    | Bit # | Buffer Type           | Function                                                                                                                |

|---------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0  | TTL/ST <sup>(1)</sup> | Input/output or external interrupt input. Internal software programmable weak pull-up.                                  |

| RB1     | bit1  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB2     | bit2  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB3     | bit3  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB4     | bit4  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB5     | bit5  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB6     | bit6  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock pin. |

| RB7     | bit7  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data pin.  |

#### TABLE 5-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h     | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX XXXX       | uuuu uuuu                       |

| 86h     | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h     | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

Legend: u = unchanged, x = unknown

Note 1: Shaded bits are not used by PORTB.

#### 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-Chip Voltage Reference (Section 8.0) can also be an input to the comparators.

The CMCON register, shown in Register 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-1.

#### REGISTER 7-1: CMCON REGISTER (ADDRESS 1Fh)

|         |                           |                                 | <b>(</b> | ,   |       |       |       |       |

|---------|---------------------------|---------------------------------|----------|-----|-------|-------|-------|-------|

|         | R-0                       | R-0                             | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|         | C2OUT                     | C10UT                           | —        | —   | CIS   | CM2   | CM1   | CM0   |

|         | bit 7                     |                                 |          |     |       |       |       | bit 0 |

|         |                           |                                 |          |     |       |       |       |       |

| bit 7   | <b>C2OUT</b> : Co         | omparator 2                     | output   |     |       |       |       |       |

|         | 1 = C2 VIN                | + > C2 VIN-                     |          |     |       |       |       |       |

|         | 0 = C2 VIN                | + < C2 VIN-                     |          |     |       |       |       |       |

| bit 6   | <b>C1OUT</b> : Co         | omparator 1                     | output   |     |       |       |       |       |

|         | 1 = C1 VIN                | + > C1 VIN-                     |          |     |       |       |       |       |

|         | 0 = C1 VIN                | + < C1 VIN-                     |          |     |       |       |       |       |

| bit 5-4 | Unimplem                  | ented: Read                     | d as '0' |     |       |       |       |       |

| bit 3   | CIS: Comp                 | arator Input                    | Switch   |     |       |       |       |       |

|         | When CM<                  | <2:0>: = 001                    | :        |     |       |       |       |       |

|         | 1 = C1 VIN-               | - connects to                   | o RA3    |     |       |       |       |       |

|         | 0 = C1 VIN                | - connects to                   | o RA0    |     |       |       |       |       |

|         | When CM<                  | <2:0> = 010:                    |          |     |       |       |       |       |

|         |                           | <ul> <li>connects to</li> </ul> |          |     |       |       |       |       |

|         |                           | I- connects t                   |          |     |       |       |       |       |

|         |                           | - connects to                   |          |     |       |       |       |       |

|         | C2 VIN                    | I- connects t                   | 0 RA1    |     |       |       |       |       |

| bit 2-0 | CM<2:0>: Comparator mode. |                                 |          |     |       |       |       |       |

|         |                           |                                 |          |     |       |       |       |       |

|         | Legend:                   |                                 |          |     |       |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

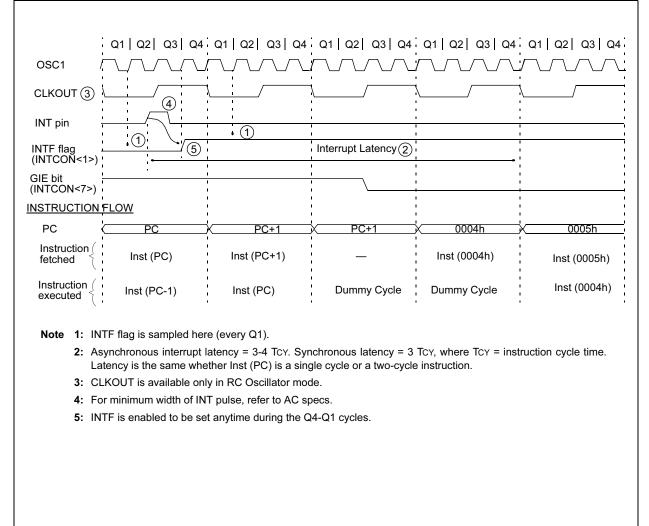

#### 9.5.1 RB0/INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered, either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP and Figure 9-18 for timing of wakeup from SLEEP through RB0/INT interrupt.

#### 9.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 6.0.

#### 9.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

| Note: | If a change on the I/O pin should occur   |

|-------|-------------------------------------------|

|       | when the read operation is being executed |

|       | (start of the Q2 cycle), then the RBIF    |

|       | interrupt flag may not get set.           |

#### 9.5.4 COMPARATOR INTERRUPT

See Section 7.6 for complete description of comparator interrupts.

#### FIGURE 9-16: INT PIN INTERRUPT TIMING

TABLE 9-6: SUMMARY OF INTERRUPT REGISTERS

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on POR<br>Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 0Bh     | INTCON | GIE   | PEIE  | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1   | —     | CMIF  | —     | —     | —     | —     | —     | —     | -0                    | -0                                             |

| 8Ch     | PIE1   | _     | CMIE  | _     | _     | —     | _     | —     | —     | -0                    | -0                                             |

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

#### 9.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and STATUS register). This will have to be implemented in software.

Example 9-3 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x20 in Bank 0 and it must also be defined at 0xA0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 9-3:

- · Stores the W register

- Stores the STATUS register in Bank 0

- Executes the ISR code

- Restores the STATUS (and bank select bit register)

- · Restores the W register

#### EXAMPLE 9-3: SAVING THE STATUS AND W REGISTERS IN RAM

| MOVWF | W_TEMP            | ;copy W to temp register,<br>;could be in either bank                       |

|-------|-------------------|-----------------------------------------------------------------------------|

| SWAPF | STATUS,W          | ;swap status to be saved<br>into W                                          |

| BCF   | STATUS, RPO       | ;change to bank 0 regardless<br>;of current bank                            |

| MOVWF | STATUS_TEMP       | ;save status to bank 0<br>;register                                         |

| :     |                   |                                                                             |

| :     | (ISR)             |                                                                             |

| :     |                   |                                                                             |

| SWAPF | STATUS_TEMP,<br>W | ;swap STATUS_TEMP register<br>;into W, sets bank to origi-<br>nal<br>;state |

| MOVWF | STATUS            | ;move W into STATUS register                                                |

| SWAPF | W_TEMP,F          | ;swap W_TEMP                                                                |

| SWAPF | W_TEMP,W          | ;swap W_TEMP into W                                                         |

## PIC16C62X

| BCF              | Bit Clear f                                                         | BTFSC            | Bit Test, Skip if Clear                                                   |

|------------------|---------------------------------------------------------------------|------------------|---------------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      | Syntax:          | [label]BTFSC f,b                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$       |

| Operation:       | $0 \rightarrow (f \le b >)$                                         | Operation:       | skip if (f <b>) = 0</b>                                                   |

| Status Affected: | None                                                                | Status Affected: | None                                                                      |

| Encoding:        | 01 00bb bfff ffff                                                   | Encoding:        | 01 10bb bfff ffff                                                         |

| Description:     | Bit 'b' in register 'f' is cleared.                                 | Description:     | If bit 'b' in register 'f' is '0', then the                               |

| Words:           | 1                                                                   |                  | next instruction is skipped.<br>If bit 'b' is '0', then the next instruc- |

| Cycles:          | 1                                                                   |                  | tion fetched during the current                                           |

| Example          | BCF FLAG_REG, 7                                                     |                  | instruction execution is discarded,                                       |

|                  | Before Instruction<br>FLAG_REG = 0xC7                               |                  | and a NOP is executed instead,<br>making this a two-cycle instruction.    |

|                  | After Instruction                                                   | Words:           | 1                                                                         |

|                  | FLAG_REG = 0x47                                                     | Cycles:          | 1(2)                                                                      |

|                  |                                                                     | Example          | here btfsc <b>FLAG,1</b><br>false goto <b>process co</b>                  |

| BSF              | Bit Set f                                                           |                  | TRUE DE                                                                   |

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |                  | •                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                  | Before Instruction<br>PC = address HERE                                   |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |                  | After Instruction<br>if FLAG<1> = 0.                                      |

| Status Affected: | None                                                                |                  | PC = address TRUE                                                         |

| Encoding:        | 01 01bb bfff ffff                                                   |                  | if FLAG<1>=1,<br>PC = address FALSE                                       |

| Description:     | Bit 'b' in register 'f' is set.                                     |                  | PC = address FALSE                                                        |

| Words:           | 1                                                                   |                  |                                                                           |

| Cycles:          | 1                                                                   |                  |                                                                           |

| Example          | BSF FLAG_REG, 7                                                     |                  |                                                                           |

Before Instruction FLAG\_REG = 0x0A After Instruction

FLAG\_REG = 0x8A

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                 |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                            |

| Operands:        | $0 \le f \le 127$<br>d $\in$ [0,1]                                                                                                                                                                                                                                                                                                     |

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                   |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                                                      |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                      |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                                   |

| Example          | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                     |

|                  | $\begin{array}{rcl} PC &=& address \ {\tt HERE} \\ \mbox{After Instruction} \\ CNT &=& CNT - 1 \\ \mbox{if CNT} &=& 0, \\ PC &=& address \ {\tt CONTINUE} \\ \mbox{if CNT} \neq& 0, \\ PC &=& address \ {\tt HERE} + 1 \\ \end{array}$                                                                                                 |

| GOTO             | Unconditional Branch                                                                                                                                                                                                                                                                                                                   |

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                                                                                                                                                                |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                                                                                                                     |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                   |

| Encoding:        | 10 1kkk kkkk kkkk                                                                                                                                                                                                                                                                                                                      |

| Description:     | GOTO is an unconditional branch.<br>The eleven bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction.                                                                                                                                      |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                      |

| Cycles:          | 2                                                                                                                                                                                                                                                                                                                                      |

| Example          | GOTO THERE                                                                                                                                                                                                                                                                                                                             |

|                  | After Instruction<br>PC = Address THERE                                                                                                                                                                                                                                                                                                |

| INCF             | Increment f                                                                                                                                                            |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                       |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                      |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                           |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                      |  |  |  |  |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                      |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                                      |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                      |  |  |  |  |

| Example          | INCF CNT, 1                                                                                                                                                            |  |  |  |  |

|                  | Before Instruction<br>CNT = 0xFF<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                                                  |  |  |  |  |

| MOVF                    | Move f                                                                                                                                                                                                                                                                               |  |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                 | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                            |  |  |  |  |

| Operands:               | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                          |  |  |  |  |

| Operation:              | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                             |  |  |  |  |

| Status Affected:        | Z                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Encoding:               | 00 1000 dfff ffff                                                                                                                                                                                                                                                                    |  |  |  |  |

| Description:            | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |  |  |  |  |

| Words:                  | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Cycles:                 | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Example                 | MOVF FSR, <b>0</b>                                                                                                                                                                                                                                                                   |  |  |  |  |

| MOVANE                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |  |  |  |  |

| MOVWF                   | Move W to f                                                                                                                                                                                                                                                                          |  |  |  |  |

| Syntax:                 | [ <i>label</i> ] MOVWF f<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                              |  |  |  |  |

| Operands:<br>Operation: | $0 \le 1 \le 127$<br>(W) $\rightarrow$ (f)                                                                                                                                                                                                                                           |  |  |  |  |

| Status Affected:        | None $(1)$                                                                                                                                                                                                                                                                           |  |  |  |  |

| Encoding:               | 00 0000 1fff ffff                                                                                                                                                                                                                                                                    |  |  |  |  |

| Description:            | Move data from W register to reg-<br>ister 'f'.                                                                                                                                                                                                                                      |  |  |  |  |

| Words:                  | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Cycles:                 | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Example                 | MOVWF OPTION                                                                                                                                                                                                                                                                         |  |  |  |  |

|                         | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F<br>W = 0x4F                                                                                                                                                                                    |  |  |  |  |

|                         | ۷۷ – UX4F                                                                                                                                                                                                                                                                            |  |  |  |  |

| NOP              | No Operation  |      |      |      |  |  |  |  |

|------------------|---------------|------|------|------|--|--|--|--|

| Syntax:          | [ label ]     | NOP  |      |      |  |  |  |  |

| Operands:        | None          |      |      |      |  |  |  |  |

| Operation:       | No operation  |      |      |      |  |  |  |  |

| Status Affected: | None          |      |      |      |  |  |  |  |

| Encoding:        | 00            | 0000 | 0xx0 | 0000 |  |  |  |  |

| Description:     | No operation. |      |      |      |  |  |  |  |

| Words:           | 1             |      |      |      |  |  |  |  |

| Cycles:          | 1             |      |      |      |  |  |  |  |

| Example          | NOP           |      |      |      |  |  |  |  |

| [ lahel ]                                                                                                            |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                           | Load Option Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|