Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | · .                                                                        |

| RAM Size                   | 80 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

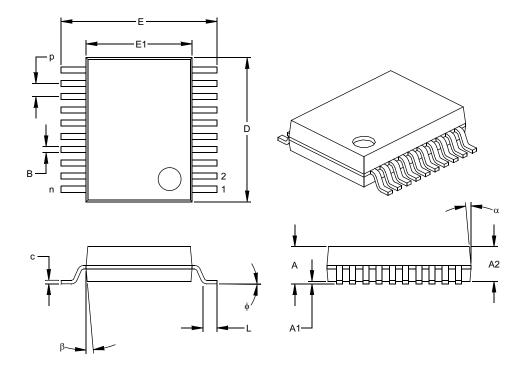

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621t-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

NOTES:

| Name         | DIP/SOIC<br>Pin # | SSOP<br>Pin # | I/O/P Type             | Buffer<br>Type        | Description                                                                                                                                                                                                         |

|--------------|-------------------|---------------|------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 16                | 18            | I                      | ST/CMOS               | Oscillator crystal input/external clock source input.                                                                                                                                                               |

| OSC2/CLKOUT  | 15                | 17            | 0                      | _                     | Oscillator crystal output. Connects to crystal or resonator<br>in Crystal Oscillator mode. In RC mode, OSC2 pin out-<br>puts CLKOUT, which has 1/4 the frequency of OSC1<br>and denotes the instruction cycle rate. |

| MCLR/VPP     | 4                 | 4             | I/P                    | ST                    | Master Clear (Reset) input/programming voltage input.<br>This pin is an Active Low Reset to the device.                                                                                                             |

|              |                   |               |                        |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                                 |

| RA0/AN0      | 17                | 19            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |

| RA1/AN1      | 18                | 20            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |

| RA2/AN2/VREF | 1                 | 1             | I/O                    | ST                    | Analog comparator input or VREF output                                                                                                                                                                              |

| RA3/AN3      | 2                 | 2             | I/O                    | ST                    | Analog comparator input /output                                                                                                                                                                                     |

| RA4/T0CKI    | 3                 | 3             | I/O                    | ST                    | Can be selected to be the clock input to the Timer<br>timer/counter or a comparator output. Output is<br>open drain type.                                                                                           |

|              |                   |               |                        |                       | PORTB is a bi-directional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs.                                                                                                 |

| RB0/INT      | 6                 | 7             | I/O                    | TTL/ST <sup>(1)</sup> | RB0/INT can also be selected as an externa interrupt pin.                                                                                                                                                           |

| RB1          | 7                 | 8             | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB2          | 8                 | 9             | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB3          | 9                 | 10            | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB4          | 10                | 11            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |

| RB5          | 11                | 12            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |

| RB6          | 12                | 13            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming clock                                                                                                                                                                   |

| RB7          | 13                | 14            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming data.                                                                                                                                                                   |

| Vss          | 5                 | 5,6           | Р                      |                       | Ground reference for logic and I/O pins.                                                                                                                                                                            |

| Vdd          | 14                | 15,16         | Р                      | _                     | Positive supply for logic and I/O pins.                                                                                                                                                                             |

| Legend:      | O = out<br>— = No | •             | I/O = inp<br>I = Input | ut/output             | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                             |

TTL = TTL input

**Note** 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

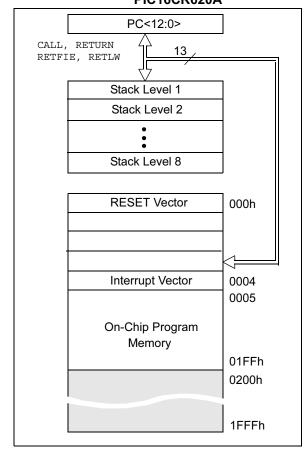

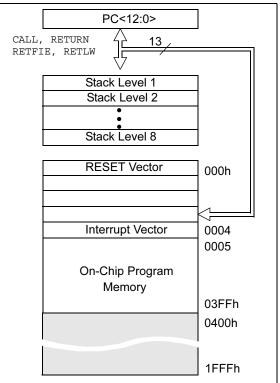

### 4.0 MEMORY ORGANIZATION

### 4.1 Program Memory Organization

The PIC16C62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C620(A) and PIC16CR620, 1K x 14 (0000h - 03FFh) for the PIC16C621(A) and 2K x 14 (0000h - 07FFh) for the PIC16C622(A) are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16C(R)620(A)) or 1K x 14 space (PIC16C621(A)) or 2K x 14 space (PIC16C622(A)). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16C620/PIC16C620A/

PIC16C620/PIC16C620 PIC16CR620A

### FIGURE 4-2:

### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C621/PIC16C621A

FIGURE 4-3:

### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C622/PIC16C622A

### **OPTION Register** 4.2.2.2

The OPTION register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |

|-------|-------------------------------------------|

|       | TMR0, assign the prescaler to the WDT     |

|       | (PSA = 1).                                |

|         | R/W-1                    | R/W-1                          | R/W-1                         | R/W-1                        | R/W-1         | R/W-1 | R/W-1 | R/W-1 |

|---------|--------------------------|--------------------------------|-------------------------------|------------------------------|---------------|-------|-------|-------|

|         | RBPU                     | INTEDG                         | TOCS                          | TOSE                         | PSA           | PS2   | PS1   | PS0   |

|         | bit 7                    |                                |                               |                              |               | •     |       | bit 0 |

| bit 7   | RBPU: PO                 | RTB Pull-u                     | p Enable bi                   | it                           |               |       |       |       |

|         |                          | 3 pull-ups ai<br>3 pull-ups ai |                               | y individual                 | port latch va | alues |       |       |

| bit 6   | INTEDG: I                | nterrupt Edg                   | e Select bit                  | -                            |               |       |       |       |

|         |                          |                                | edge of RB0<br>edge of RB0    |                              |               |       |       |       |

| bit 5   | TOCS: TMI                | R0 Clock Sc                    | ource Select                  | bit                          |               |       |       |       |

|         |                          | ion on RA4/<br>Il instruction  | T0CKI pin<br>cycle clock      | (CLKOUT)                     |               |       |       |       |

| bit 4   | TOSE: TM                 | R0 Source E                    | Edge Select                   | bit                          |               |       |       |       |

|         |                          |                                |                               | ition on RA4<br>ition on RA4 |               |       |       |       |

| bit 3   | PSA: Pres                | caler Assigr                   | iment bit                     |                              | -             |       |       |       |

|         |                          |                                | ned to the W<br>ned to the Ti | DT<br>mer0 module            | Э             |       |       |       |

| bit 2-0 | <b>PS&lt;2:0&gt;</b> : [ | Prescaler Ra                   | ate Select bi                 | ts                           |               |       |       |       |

|         | E                        | Bit Value T                    | MR0 Rate                      | WDT Rate                     |               |       |       |       |

|         | -                        | 000<br>001                     | 1:2<br>1:4                    | 1:1<br>1:2                   |               |       |       |       |

|         |                          | 010<br>011                     | 1 : 8<br>1 : 16               | 1:4<br>1:8                   |               |       |       |       |

|         |                          | 100                            | 1:32                          | 1:16                         |               |       |       |       |

|         |                          | 101                            | 1:64                          | 1:32                         |               |       |       |       |

|         |                          | 110                            | 1:128                         | 1:64                         |               |       |       |       |

|         |                          | 111                            | 1:256                         | 1 : 128                      |               |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

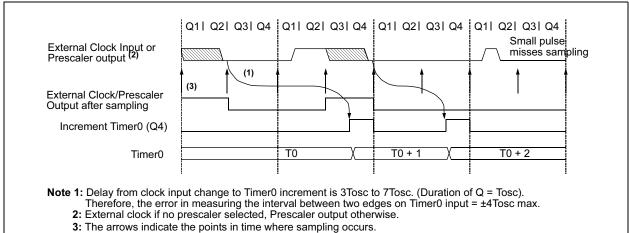

### 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

### 7.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise the maximum delay of the comparators should be used (Table 12-2).

### 7.5 Comparator Outputs

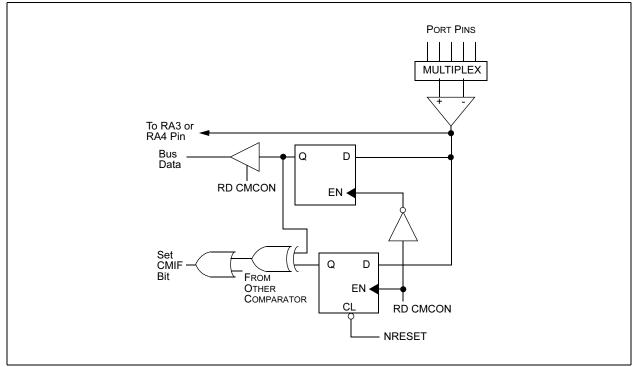

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 7-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3 and RA4 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

### FIGURE 7-3: COMPARATOR OUTPUT BLOCK DIAGRAM

### EXAMPLE 8-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; | 4 Inputs Muxed |

|-------|-------------|---|----------------|

| MOVWF | CMCON       | ; | to 2 comps.    |

| BSF   | STATUS, RPO | ; | go to Bank 1   |

| MOVLW | 0x0F        | ; | RA3-RA0 are    |

| MOVWF | TRISA       | ; | inputs         |

| MOVLW | 0xA6        | ; | enable VREF    |

| MOVWF | VRCON       | ; | low range      |

|       |             | ; | set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; | go to Bank O   |

| CALL  | DELAY10     | ; | 10µs delay     |

### 8.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 8-1) keep VREF from approaching VSS or VDD. The voltage reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the voltage reference can be found in Table 12-2.

### 8.3 Operation During SLEEP

When the device wakes up from SLEEP through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the voltage reference should be disabled.

### 8.4 Effects of a RESET

A device RESET disables the voltage reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

### 8.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the voltage reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the voltage reference output for external connections to VREF. Figure 8-2 shows an example buffering technique.

# FIGURE 8-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

### TABLE 8-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | -      | CIS    | CM2    | CM1    | CM0    | 00 0000         | 00 0000                         |

| 85h     | TRISA | _     |       |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

**Note:** - = Unimplemented, read as "0"

# 9.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16C62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-Circuit Serial Programming™

The PIC16C62X devices have a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

### 9.5 Interrupts

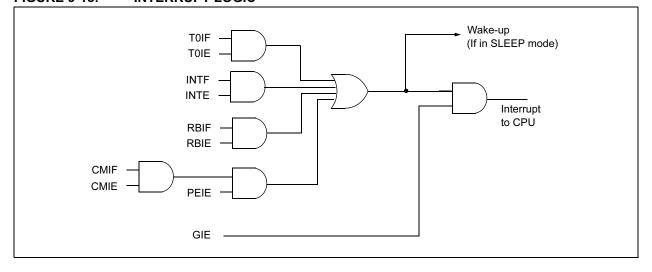

The PIC16C62X has 4 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB<7:4>)

- · Comparator interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which reenable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h.

FIGURE 9-15: INTERRUPT LOGIC

Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/ INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 9-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

### 9.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs with no external circuitry drawing current from the I/O pin and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated      |

|-------|------------------------------------------------|

|       | by a WDT time-out does not drive MCLR pin low. |

|       |                                                |

### 9.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device RESET. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. PD bit, which is set on power-up, is cleared when SLEEP is invoked. TO bit is cleared if WDT wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction after the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

**Note:** If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from SLEEP. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes up from SLEEP, regardless of the source of wake-up.

| Q1 Q2 Q                  | 3 Q4 Q1 Q2 Q3 Q4 Q | Q1                    | Q1 Q2 Q3 Q4      | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 0    | Q1 Q2 Q3 Q4 |

|--------------------------|--------------------|-----------------------|------------------|-------------|------------------|-------------|

| OSC1 /\_/\               |                    | AAAAA                 |                  |             |                  |             |

| CLKOUT(4)                |                    | Tost(2)               | <u> </u>         |             | \ <u>`</u>       |             |

| INT pin                  | 1 I                |                       | 1<br>1           |             | 1                |             |

| NTF flag                 |                    |                       | Interrupt Latend | SV.         |                  |             |

| INTCON<1>)               |                    | <del>≉</del>          | (Note 2)         | ,           |                  |             |

| GIE bit<br>INTCON<7>)    |                    | Processor in<br>SLEEP | 1                |             |                  |             |

| INSTRUCTION FLOW         |                    |                       | 1<br>1<br>1      |             | 1                |             |

| PC X PC                  | <u>Υ PC+1 Χ</u>    | PC+2                  | X PC+2           | PC + 2      | <u>χ 0004h χ</u> | 0005h       |

| Instruction { Inst(PC) = | SLEEP Inst(PC + 1) |                       | Inst(PC + 2)     |             | Inst(0004h)      | Inst(0005h) |

| Instruction Inst(PC      | - 1) SLEEP         |                       | Inst(PC + 1)     | Dummy cycle | Dummy cycle      | Inst(0004h) |

### FIGURE 9-18: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**3:** GIE = '1' assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these Osc modes, but shown here for timing reference.

| SUBLW        | Subtract W from Literal                                                       | SUBWF               | Subtract W from f                                                              |

|--------------|-------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------|

| Syntax:      | [ <i>label</i> ] SUBLW k                                                      | Syntax:             | [ <i>label</i> ] SUBWF f,d                                                     |

| Operands:    | $0 \le k \le 255$                                                             | Operands:           | $0 \le f \le 127$                                                              |

| Operation:   | $k - (W) \to (W)$                                                             |                     | d ∈ [0,1]                                                                      |

| Status       | C, DC, Z                                                                      | Operation:          | (f) - (W) $\rightarrow$ (dest)                                                 |

| Affected:    |                                                                               | Status<br>Affected: | C, DC, Z                                                                       |

| Encoding:    | 11 110x kkkk kkkk                                                             |                     |                                                                                |

| Description: | The W register is subtracted (2's                                             | Encoding:           | 00 0010 dfff ffff                                                              |

|              | complement method) from the eight<br>bit literal 'k'. The result is placed in | Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0, |

|              | the W register.                                                               |                     | the result is stored in the W register.                                        |

| Words:       | 1                                                                             |                     | If 'd' is 1, the result is stored back in                                      |

| Cycles:      | 1                                                                             |                     | register 'f'.                                                                  |

| Example 1:   | SUBLW 0x02                                                                    | Words:              | 1                                                                              |

| ·            | Before Instruction                                                            | Cycles:             | 1                                                                              |

|              | W = 1                                                                         | Example 1:          | SUBWF REG1,1                                                                   |

|              | C = ?                                                                         |                     | Before Instruction                                                             |

|              | After Instruction                                                             |                     | REG1= 3<br>W = 2                                                               |

|              | W = 1<br>C = 1; result is positive                                            |                     | C = ?                                                                          |

| Example 2:   | Before Instruction                                                            |                     | After Instruction                                                              |

| Example 2.   | W = 2                                                                         |                     | REG1= 1                                                                        |

|              | C = ?                                                                         |                     | W = 2<br>C = 1; result is positive                                             |

|              | After Instruction                                                             | Example 2:          | Before Instruction                                                             |

|              | W = 0                                                                         | ·                   | REG1= 2                                                                        |

|              | C = 1; result is zero                                                         |                     | W = 2                                                                          |

| Example 3:   | Before Instruction                                                            |                     | C = ?                                                                          |

|              | W = 3<br>C = ?                                                                |                     | After Instruction                                                              |

|              | After Instruction                                                             |                     | REG1= 0<br>W = 2                                                               |

|              | W = 0 x F F                                                                   |                     | C = 1; result is zero                                                          |

|              | C = 0; result is negative                                                     | Example 3:          | Before Instruction                                                             |

|              |                                                                               |                     | REG1= 1<br>W = 2                                                               |

|              |                                                                               |                     | W = 2<br>C = ?                                                                 |

|              |                                                                               |                     | After Instruction                                                              |

|              |                                                                               |                     | REG1= 0xFF                                                                     |

|              |                                                                               |                     | W = 2                                                                          |

|              |                                                                               |                     | C = 0; result is negative                                                      |

### 11.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 11.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 11.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command-line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities, and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping, and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high level source debugging with the MPLAB IDE.

# 11.6 MPLAB ASM30 Assembler, Linker, and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

### 11.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PICmicro series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break, or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

### 11.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

### 12.2 DC Characteristics: PIC16C62XA-04 (Commercial, Industrial, Extended) PIC16C62XA-20 (Commercial, Industrial, Extended) PIC16LC62XA-04 (Commercial, Industrial, Extended)

| PIC16C62XA<br>PIC16LC62XA |      |                                               |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                          |      |                                              |  |  |  |

|---------------------------|------|-----------------------------------------------|-------|------------------------------------------------------|--------------------------|------|----------------------------------------------|--|--|--|

| Param.<br>No.             | Sym  | Characteristic                                | Min   | Тур†                                                 | /p† Max Units Conditions |      |                                              |  |  |  |

| D001                      | Vdd  | Supply Voltage                                | 3.0   | _                                                    | 5.5                      | V    | See Figures 12-1, 12-2, 12-3, 12-4, and 12-5 |  |  |  |

| D001                      | Vdd  | Supply Voltage                                | 2.5   | _                                                    | 5.5                      | V    | See Figures 12-1, 12-2, 12-3, 12-4, and 12-5 |  |  |  |

| D002                      | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>  |       | 1.5*                                                 |                          | V    | Device in SLEEP mode                         |  |  |  |

| D002                      | Vdr  | RAM Data Retention Voltage <sup>(1)</sup>     |       | 1.5*                                                 | —                        | V    | Device in SLEEP mode                         |  |  |  |

| D003                      | VPOR | VDD start voltage to<br>ensure Power-on Reset |       | Vss                                                  | _                        | V    | See section on Power-on Reset for details    |  |  |  |

| D003                      | VPOR | VDD start voltage to<br>ensure Power-on Reset | —     | Vss                                                  | —                        | V    | See section on Power-on Reset for details    |  |  |  |

| D004                      | SVDD | VDD rise rate to ensure<br>Power-on Reset     | 0.05* | —                                                    | —                        | V/ms | See section on Power-on Reset for details    |  |  |  |

| D004                      | SVDD | VDD rise rate to ensure<br>Power-on Reset     | 0.05* | —                                                    | —                        | V/ms | See section on Power-on Reset for details    |  |  |  |

| D005                      | VBOR | Brown-out Detect Voltage                      | 3.7   | 4.0                                                  | 4.35                     | V    | BOREN configuration bit is cleared           |  |  |  |

| D005                      | VBOR | Brown-out Detect Voltage                      | 3.7   | 4.0                                                  | 4.35                     | V    | BOREN configuration bit is cleared           |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD, MCLR = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

**6:** Commercial temperature range only.

### 12.5 DC CHARACTERISTICS: PIC16C620A/C621A/C622A-40<sup>(7)</sup> (Commercial) PIC16CR620A-40<sup>(7)</sup> (Commercial)

| DC CH         | ARACTER                           | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |           |          |           |          |                                                                            |

|---------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|-----------|----------|----------------------------------------------------------------------------|

| Param<br>No.  | Sym                               | Characteristic                                                                                                                     | Min       | Тур†     | Max       | Units    | Conditions                                                                 |

| D001          | Vdd                               | Supply Voltage                                                                                                                     | 3.0       | _        | 5.5       | V        | Fosc = DC to 20 MHz                                                        |

| D002          | Vdr                               | RAM Data Retention Voltage <sup>(1)</sup>                                                                                          |           | 1.5*     |           | V        | Device in SLEEP mode                                                       |

| D003          | VPOR                              | VDD start voltage to ensure<br>Power-on Reset                                                                                      | —         | Vss      | _         | V        | See section on Power-on Reset for details                                  |

| D004          | SVDD                              | VDD rise rate to ensure Power-on<br>Reset                                                                                          | 0.05<br>* | —        | _         | V/ms     | See section on Power-on Reset for details                                  |

| D005          | VBOR                              | Brown-out Detect Voltage                                                                                                           | 3.65      | 4.0      | 4.35      | V        | BOREN configuration bit is cleared                                         |

| D010          | IDD                               | Supply Current <sup>(2,4)</sup>                                                                                                    | —         | 1.2      | 2.0       | mA       | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT Osc mode, ( <b>Note 4</b> )* |

|               |                                   |                                                                                                                                    | —         | 0.4      | 1.2       | mA       | Fosc = 4 MHz, VDD = 3.0V, WDT disabled,<br>XT Osc mode, (Note 4)           |

|               |                                   |                                                                                                                                    | —         | 1.0      | 2.0       | mA       | Fosc = 10 MHz, VDD = 3.0V, WDT disabled,<br>HS Osc mode, ( <b>Note 6</b> ) |

|               |                                   |                                                                                                                                    | —         | 4.0      | 6.0       | mA       | Fosc = 20 MHz, VDD = 4.5V, WDT disabled,<br>HS Osc mode                    |

|               |                                   |                                                                                                                                    | —         | 4.0      | 7.0       | mA       | Fosc = 20 MHz, VDD = 5.5V, WDT disabled*,<br>HS Osc mode                   |

|               |                                   |                                                                                                                                    | —         | 35       | 70        | μA       | Fosc = 32 kHz, VDD = 3.0V, WDT disabled,<br>LP Osc mode                    |

| D020          | IPD                               | Power Down Current <sup>(3)</sup>                                                                                                  | _         | _        | 2.2       | μA       | VDD = 3.0V                                                                 |

|               |                                   |                                                                                                                                    | —         | —        | 5.0       | μA       | VDD = 4.5V*                                                                |

|               |                                   |                                                                                                                                    | —         | —        | 9.0       | μA       | VDD = 5.5V                                                                 |

|               |                                   | (5)                                                                                                                                | —         | —        | 15        | μA       | VDD = 5.5V Extended                                                        |

| D022          | $\Delta$ IWDT                     | WDT Current <sup>(5)</sup>                                                                                                         |           | 6.0      | 10        | μA       | VDD = 4.0V                                                                 |

| D022A         |                                   | Brown-out Reset Current <sup>(5)</sup>                                                                                             |           | 75       | 12        | μA       | $(125^{\circ}C)$                                                           |

| D022A<br>D023 | ∆IBOR<br>∆ICOMP                   | Comparator Current for each                                                                                                        | _         | 75<br>30 | 125<br>60 | μA<br>μA | BOD enabled, VDD = 5.0V<br>VDD = 4.0V                                      |

|               |                                   | Comparator <sup>(5)</sup>                                                                                                          |           |          |           | 1        |                                                                            |

| D023A         | $\Delta$ IVREF                    | VREF Current <sup>(5)</sup>                                                                                                        | —         | 80       | 135       | μA       | VDD = 4.0V                                                                 |

|               | $\Delta \text{IEE Write}$         | Operating Current                                                                                                                  | —         |          | 3         | mA       | Vcc = 5.5V, SCL = 400 kHz                                                  |

|               | $\Delta \text{IEE} \ \text{Read}$ | Operating Current                                                                                                                  | —         |          | 1         | mA       |                                                                            |

|               | $\Delta IEE$                      | Standby Current                                                                                                                    | —         |          | 30        | μA       | Vcc = 3.0V, EE Vdd = Vcc                                                   |

|               | $\Delta IEE$                      | Standby Current                                                                                                                    | —         |          | 100       | μA       | Vcc = 3.0V, EE Vdd = Vcc                                                   |

| 1A            | Fosc                              | LP Oscillator Operating Frequency                                                                                                  | 0         | —        | 200       | kHz      | All temperatures                                                           |

|               |                                   | RC Oscillator Operating Frequency                                                                                                  | 0         | —        | 4         | MHz      | All temperatures                                                           |

|               |                                   | XT Oscillator Operating Frequency                                                                                                  | 0         | -        | 4         | MHz      | All temperatures                                                           |

|               |                                   | HS Oscillator Operating Frequency                                                                                                  | 0         |          | 20        | MHz      | All temperatures                                                           |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption. The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD, MCLR = VDD; WDT enabled/disabled as specified.

The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP

mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/ 2REXT (mA) with REXT in kΩ.

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

7: See Section 12.1 and Section 12.3 for 16C62X and 16CR62X devices for operation between 20 MHz and 40 MHz for valid modified characteristics.

### 12.5 DC CHARACTERISTICS: PIC16C620A/C621A/C622A-40<sup>(7)</sup> (Commercial) PIC16CR620A-40<sup>(7)</sup> (Commercial)

| DC CH        | IARAC | TERISTICS                                  |                | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |                 |      |                                                                |  |  |  |  |

|--------------|-------|--------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|----------------------------------------------------------------|--|--|--|--|

| Param<br>No. | Sym   | Characteristic                             | Min            | Тур†                                                                                                                               | Мах             | Unit | Conditions                                                     |  |  |  |  |

|              | VIL   | Input Low Voltage                          |                |                                                                                                                                    |                 |      |                                                                |  |  |  |  |

|              |       | I/O ports                                  |                |                                                                                                                                    |                 |      |                                                                |  |  |  |  |

| D030         |       | with TTL buffer                            | Vss            | —                                                                                                                                  | 0.8V<br>0.15Vdd | V    | VDD = 4.5V to 5.5V, otherwise                                  |  |  |  |  |

| D031         |       | with Schmitt Trigger input                 | Vss            |                                                                                                                                    | 0.2VDD          | V    |                                                                |  |  |  |  |

| D032         |       | MCLR, RA4/T0CKI, OSC1<br>(in RC mode)      | Vss            | —                                                                                                                                  | 0.2Vdd          | V    | (Note 1)                                                       |  |  |  |  |

| D033         |       | OSC1 (in XT and HS)                        | Vss            | _                                                                                                                                  | 0.3VDD          | V    |                                                                |  |  |  |  |

|              |       | OSC1 (in LP)                               | Vss            | _                                                                                                                                  | 0.6Vdd - 1.0    | V    |                                                                |  |  |  |  |

|              | Vih   | Input High Voltage                         |                |                                                                                                                                    |                 |      |                                                                |  |  |  |  |

|              |       | I/O ports                                  |                |                                                                                                                                    |                 |      |                                                                |  |  |  |  |

| D040         |       | with TTL buffer                            | 2.0V           | —                                                                                                                                  | Vdd             | V    | VDD = 4.5V to 5.5V, otherwise                                  |  |  |  |  |

|              |       |                                            | 0.25 VDD + 0.8 |                                                                                                                                    | Vdd             |      |                                                                |  |  |  |  |

| D041         |       | with Schmitt Trigger input                 | 0.8 VDD        |                                                                                                                                    | Vdd             |      |                                                                |  |  |  |  |

| D042         |       | MCLR RA4/T0CKI                             | 0.8 VDD        | —                                                                                                                                  | Vdd             | V    |                                                                |  |  |  |  |

| D043         |       | OSC1 (XT, HS and LP)                       | 0.7 VDD        | —                                                                                                                                  | Vdd             | V    |                                                                |  |  |  |  |

| D043A        |       | OSC1 (in RC mode)                          | 0.9 VDD        |                                                                                                                                    |                 |      | (Note 1)                                                       |  |  |  |  |

| D070         | IPURB | PORTB Weak Pull-up Current                 | 50             | 200                                                                                                                                | 400             | μA   | VDD = 5.0V, VPIN = VSS                                         |  |  |  |  |

|              | lı∟   | Input Leakage Current <sup>(2, 3)</sup>    |                |                                                                                                                                    |                 |      |                                                                |  |  |  |  |

|              |       | I/O ports (except PORTA)                   |                |                                                                                                                                    | ±1.0            | μA   | Vss $\leq$ VPIN $\leq$ VDD, pin at hi-impedance                |  |  |  |  |

| D060         |       | PORTA                                      | —              | —                                                                                                                                  | ±0.5            | μA   | Vss $\leq$ VPIN $\leq$ VDD, pin at hi-impedance                |  |  |  |  |

| D061         |       | RA4/T0CKI                                  | —              | —                                                                                                                                  | ±1.0            | μA   | $Vss \leq VPIN \leq VDD$                                       |  |  |  |  |

| D063         |       | OSC1, MCLR                                 | _              | —                                                                                                                                  | ±5.0            | μA   | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration    |  |  |  |  |

|              | Vol   | Output Low Voltage                         |                |                                                                                                                                    |                 |      |                                                                |  |  |  |  |

| D080         |       | I/O ports                                  | _              | —                                                                                                                                  | 0.6             | V    | IOL = 8.5 mA, VDD = 4.5V, -40° to +85°C                        |  |  |  |  |

|              |       |                                            | _              | —                                                                                                                                  | 0.6             | V    | IOL = 7.0 mA, VDD = 4.5V, +125°C                               |  |  |  |  |

| D083         |       | OSC2/CLKOUT (RC only)                      | _              | —                                                                                                                                  | 0.6             | V    | IOL = 1.6 mA, VDD = 4.5V, -40° to +85°C                        |  |  |  |  |

|              |       |                                            |                |                                                                                                                                    | 0.6             | V    | IOL = 1.2 mA, VDD = 4.5V, +125°C                               |  |  |  |  |

|              | Vон   | Output High Voltage <sup>(3)</sup>         |                |                                                                                                                                    |                 |      |                                                                |  |  |  |  |

| D090         |       | I/O ports (except RA4)                     | VDD-0.7        | —                                                                                                                                  | —               | V    | IOH = -3.0 mA, VDD = 4.5V, -40° to +85°C                       |  |  |  |  |

|              |       |                                            | VDD-0.7        | —                                                                                                                                  | —               | V    | ІОН = -2.5 mA, VDD = 4.5V, +125°C                              |  |  |  |  |

| D092         |       | OSC2/CLKOUT (RC only)                      | VDD-0.7        | —                                                                                                                                  | —               | V    | ІОН = -1.3 mA, VDD = 4.5V, -40° to +85°С                       |  |  |  |  |

|              |       |                                            | VDD-0.7        | _                                                                                                                                  | —               | V    | Іон = -1.0 mA, Vdd = 4.5V, +125°С                              |  |  |  |  |

| *D150        | Vod   | Open Drain High Voltage                    |                |                                                                                                                                    | 8.5             | V    | RA4 pin                                                        |  |  |  |  |

|              |       | Capacitive Loading Specs on<br>Output Pins |                |                                                                                                                                    |                 |      |                                                                |  |  |  |  |

| D100         | Cosc2 | OSC2 pin                                   |                |                                                                                                                                    | 15              | pF   | In XT, HS and LP modes when external clock used to drive OSC1. |  |  |  |  |

| D101         | Cio   | All I/O pins/OSC2 (in RC mode)             |                |                                                                                                                                    | 50              | pF   |                                                                |  |  |  |  |

|              |       | parameters are characterized but not       | <u> </u>       | L                                                                                                                                  | ~~              | ۳.   | 1                                                              |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD, MCLR = VDD; WDT enabled/disabled as specified.

The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in bi-impedance state and tied to VDD or VSS.

mode, with all I/O pins in hi-impedance state and tied to VDD or VSs.

For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/ 2REXT (mA) with REXT in kΩ.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

7: See Section 12.1 and Section 12.3 for 16C62X and 16CR62X devices for operation between 20 MHz and 40 MHz for valid modified characteristics.

## 12.6 DC Characteristics:

### PIC16C620A/C621A/C622A-40<sup>(3)</sup> (Commercial) PIC16CR620A-40<sup>(3)</sup> (Commercial)

| DC CHARACTERISTICS<br>Power Supply Pins |      | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |                    |            |                                 |                                                                          |

|-----------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------|---------------------------------|--------------------------------------------------------------------------|

| Characteristic                          | Sym  | Min                                                                                                                                    | Typ <sup>(1)</sup> | Мах        | Units                           | Conditions                                                               |

| Supply Voltage                          | Vdd  | 4.5                                                                                                                                    | —                  | 5.5        | V                               | HS Option from 20 - 40 MHz                                               |

| Supply Current <sup>(2)</sup>           | IDD  | _                                                                                                                                      | 5.5<br>7.7         | 11.5<br>16 | mA<br>mA                        | Fosc = 40 MHz, VDD = 4.5V, HS mode<br>Fosc = 40 MHz, VDD = 5.5V, HS mode |

| HS Oscillator Operating<br>Frequency    | Fosc | 20                                                                                                                                     | _                  | 40         | MHz                             | OSC1 pin is externally driven,<br>OSC2 pin not connected                 |

| Input Low Voltage OSC1                  | VIL  | Vss                                                                                                                                    | —                  | 0.2Vdd     | V                               | HS mode, OSC1 externally driven                                          |

| Input High Voltage OSC1 VIH 0.8VDD      |      |                                                                                                                                        | Vdd                | V          | HS mode, OSC1 externally driven |                                                                          |

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss,

T0CKI = VDD,  $\overline{MCLR}$  = VDD; WDT disabled, HS mode with OSC2 not connected.

**3:** For device operation between DC and 20 MHz. See Table 12-1 and Table 12-2.

# 12.7 AC Characteristics: PIC16C620A/C621A/C622A-40<sup>(2)</sup> (Commercial) PIC16CR620A-40<sup>(2)</sup> (Commercial)

| AC CHARACTERISTICS<br>All Pins Except Power Supply Pir       | IS         |                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |       |            |                                      |  |

|--------------------------------------------------------------|------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|------------|--------------------------------------|--|

| Characteristic                                               | Min        | Typ <sup>(1)</sup> | Max                                                                                                                                | Units | Conditions |                                      |  |

| External CLKIN Frequency                                     | Fosc       | 20                 | —                                                                                                                                  | 40    | MHz        | HS mode, OSC1 externally driven      |  |