Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 80 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                     |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

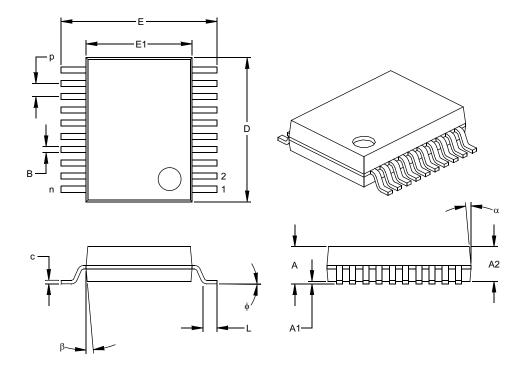

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621t-04i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.0 MEMORY ORGANIZATION

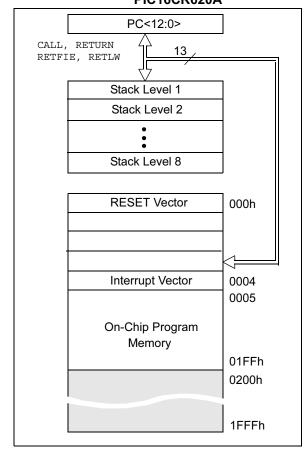

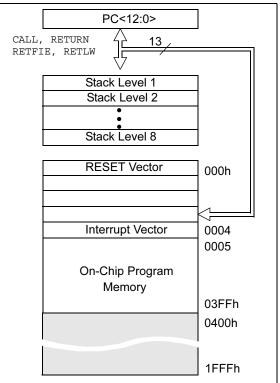

## 4.1 Program Memory Organization

The PIC16C62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C620(A) and PIC16CR620, 1K x 14 (0000h - 03FFh) for the PIC16C621(A) and 2K x 14 (0000h - 07FFh) for the PIC16C622(A) are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16C(R)620(A)) or 1K x 14 space (PIC16C621(A)) or 2K x 14 space (PIC16C622(A)). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16C620/PIC16C620A/

PIC16C620/PIC16C620 PIC16CR620A

## FIGURE 4-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C621/PIC16C621A

FIGURE 4-3:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C622/PIC16C622A

## 4.2.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uuluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any STATUS bit. For other instructions not affecting any STATUS bits, see the "Instruction Set Summary".

- Note 1: The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16C62X and should be programmed as '0'. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The <u>C and DC bits</u> operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

## REGISTER 4-1: STATUS REGISTER (ADDRESS 03H OR 83H)

|         | Reserved            | Reserved                           | R/W-0          | R-1            | R-1            | R/W-x          | R/W-x        | R/W-x          |

|---------|---------------------|------------------------------------|----------------|----------------|----------------|----------------|--------------|----------------|

|         | IRP                 | RP1                                | RP0            | TO             | PD             | Z              | DC           | С              |

|         | bit 7               |                                    |                |                |                |                |              | bit 0          |

|         |                     |                                    |                |                |                |                |              |                |

| bit 7   | -                   | ter Bank Sel                       | -              | d for indirect | addressing     | )              |              |                |

|         |                     | , 3 (100h - 1<br>, 1 (00h - FF     |                |                |                |                |              |                |

|         |                     | t is reserved                      |                | 16C62X; alv    | /ays maintai   | n this bit cle | ar.          |                |

| bit 6-5 |                     | Register Ban                       |                |                | -              |                |              |                |

|         |                     | 1 (80h - FFh                       |                |                |                |                |              |                |

|         |                     | 0 (00h - 7Fh                       |                |                |                |                |              |                |

|         | Each bank<br>clear. | is 128 bytes                       | . The RP1 t    | oit is reserve | ed on the PIC  | C16C62X; a     | lways mainta | ain this bit   |

| bit 4   | TO: Time-c          | out bit                            |                |                |                |                |              |                |

|         |                     | ower-up, CLI                       | RWDT instruc   | ction. or SLE  | EP instruction | on             |              |                |

|         |                     | time-out oc                        |                | ,              |                |                |              |                |

| bit 3   | PD: Power           | -down bit                          |                |                |                |                |              |                |

|         | -                   | ower-up or b<br>cution of the      | -              |                | n              |                |              |                |

| bit 2   | Z: Zero bit         |                                    |                |                |                |                |              |                |

|         |                     | sult of an arit<br>sult of an arit |                |                |                | )              |              |                |

| bit 1   |                     | arry/borrow b                      |                | • •            |                |                | )(for borrow | the polarity   |

|         | is reversed         | -                                  | ζ ,            |                | ·              |                |              |                |

|         |                     | -out from the                      |                |                |                | rred           |              |                |

|         |                     | ry-out from th                     |                |                |                |                |              |                |

| bit 0   | •                   | orrow bit (AD                      |                |                |                |                |              |                |

|         | •                   | -out from the<br>ry-out from th    | -              |                |                |                |              |                |

|         | Note:               | For borrow t                       | he polarity i  | s reversed.    | A subtraction  | on is execut   | ed by addin  | g the two's    |

|         |                     | complement                         |                |                |                |                |              | s, this bit is |

|         |                     | loaded with e                      | either the hig | gh or low or   | der bit of the | source reg     | ister.       |                |

|         | Legend:             | L. L. 14                           |                |                |                |                | hit on all   | 0              |

|         | R = Reada           |                                    |                | ritable bit    |                | •              | bit, read as |                |

|         | - n = Value         | at POR                             | 1′ = Bi        | it is set      | '0' = Bit i    | scleared       | x = Bit is u | nknown         |

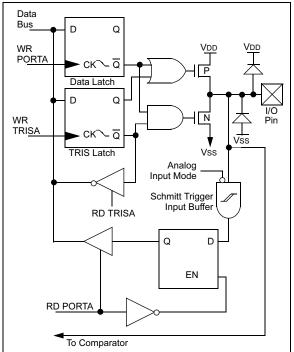

# 5.0 I/O PORTS

The PIC16C62X have two ports, PORTA and PORTB. Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

## 5.1 PORTA and TRISA Registers

PORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. Port RA4 is multiplexed with the T0CKI clock input. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers), which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

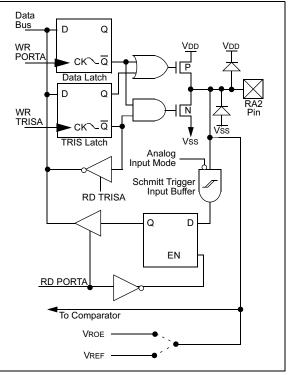

The PORTA pins are multiplexed with comparator and voltage reference functions. The operation of these pins are selected by control bits in the CMCON (comparator control register) register and the VRCON (voltage reference control register) register. When selected as a comparator input, these pins will read as '0's.

#### FIGURE 5-1: BLOCK DIAGRAM OF RA1:RA0 PINS

| Note: | On RESET, the TRISA register is set to all  |

|-------|---------------------------------------------|

|       | inputs. The digital inputs are disabled and |

|       | the comparator inputs are forced to ground  |

|       | to reduce excess current consumption.       |

TRISA controls the direction of the RA pins, even when they are being used as comparator inputs. The user must make sure to keep the pins configured as inputs when using them as comparator inputs.

The RA2 pin will also function as the output for the voltage reference. When in this mode, the VREF pin is a very high impedance output and must be buffered prior to any external load. The user must configure TRISA<2> bit as an input and use high impedance loads.

In one of the Comparator modes defined by the CMCON register, pins RA3 and RA4 become outputs of the comparators. The TRISA<4:3> bits must be cleared to enable outputs to use this function.

#### EXAMPLE 5-1: INITIALIZING PORTA

| CLRF  | PORTA       | ;Initialize PORTA by setting<br>;output data latches |

|-------|-------------|------------------------------------------------------|

| MOVLW | 0X07        | ;Turn comparators off and                            |

| MOVWF | CMCON       | ;enable pins for I/O<br>;functions                   |

| BSF   | STATUS, RPO | ;Select Bank1                                        |

| MOVLW | 0x1F        | ;Value used to initialize                            |

|       |             | ;data direction                                      |

| MOVWF | TRISA       | ;Set RA<4:0> as inputs                               |

|       |             | ;TRISA<7:5> are always                               |

|       |             | ;read as '0'.                                        |

## FIGURE 5-2: BLOCK DIAGRAM OF RA2 PIN

The code example in Example 7-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

#### EXAMPLE 7-1: INITIALIZING COMPARATOR MODULE

| MOVLW | 0x03         | ;Init comparator mode             |

|-------|--------------|-----------------------------------|

| MOVWF | CMCON        | ;CM<2:0> = 011                    |

| CLRF  | PORTA        | ;Init PORTA                       |

| BSF   | STATUS, RPO  | ;Select Bank1                     |

| MOVLW | 0x07         | ;Initialize data direction        |

| MOVWF | TRISA        | ;Set RA<2:0> as inputs            |

|       |              | ;RA<4:3> as outputs               |

|       |              | ;TRISA<7:5> always read `0'       |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| CALL  | DELAY 10     | ;10µs delay                       |

| MOVF  | CMCON,F      | ;Read CMCONtoend change condition |

| BCF   | PIR1,CMIF    | ;Clear pending interrupts         |

| BSF   | STATUS, RPO  | ;Select Bank 1                    |

| BSF   | PIE1,CMIE    | ;Enable comparator interrupts     |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| BSF   | INTCON, PEIE | ;Enable peripheral interrupts     |

| BSF   | INTCON, GIE  | ;Global interrupt enable          |

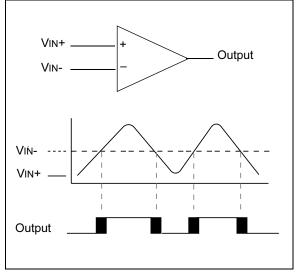

# 7.2 Comparator Operation

A single comparator is shown in Figure 7-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 7-2 represent the uncertainty due to input offsets and response time.

## 7.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator Operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 7-2).

## 7.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSs and VDD, and can be applied to either pin of the comparator(s).

## 7.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 10, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 7-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

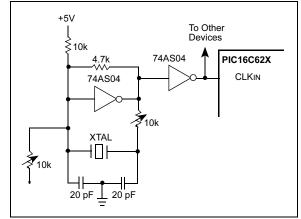

#### 9.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance or one with parallel resonance.

Figure 9-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 9-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

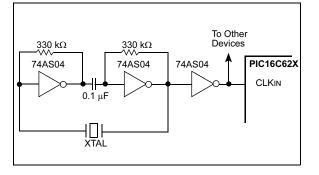

Figure 9-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a  $180^{\circ}$  phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 9-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

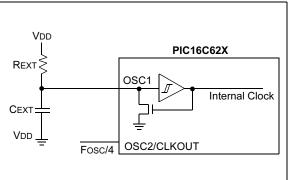

## 9.2.4 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 9-5 shows how the R/C combination is connected to the PIC16C62X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See Section 13.0 for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See Section 13.0 for variation of oscillator frequency due to VDD for given REXT/CEXT values, as well as frequency variation due to operating temperature for given R, C and VDD values.

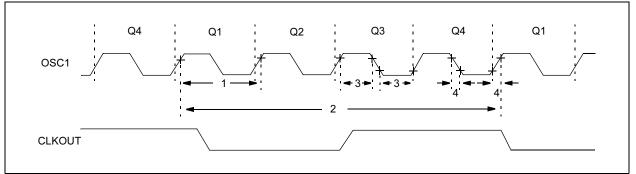

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

## FIGURE 9-5: RC OSCILLATOR MODE

TABLE 9-6: SUMMARY OF INTERRUPT REGISTERS

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on POR<br>Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 0Bh     | INTCON | GIE   | PEIE  | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1   | —     | CMIF  | —     | —     | —     | —     | —     | —     | -0                    | -0                                             |

| 8Ch     | PIE1   | _     | CMIE  | _     | _     | —     | _     | —     | _     | -0                    | -0                                             |

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

## 9.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and STATUS register). This will have to be implemented in software.

Example 9-3 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x20 in Bank 0 and it must also be defined at 0xA0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 9-3:

- · Stores the W register

- Stores the STATUS register in Bank 0

- Executes the ISR code

- Restores the STATUS (and bank select bit register)

- · Restores the W register

#### EXAMPLE 9-3: SAVING THE STATUS AND W REGISTERS IN RAM

| MOVWF | W_TEMP            | ;copy W to temp register,<br>;could be in either bank                       |

|-------|-------------------|-----------------------------------------------------------------------------|

| SWAPF | STATUS,W          | ;swap status to be saved<br>into W                                          |

| BCF   | STATUS, RPO       | ;change to bank 0 regardless<br>;of current bank                            |

| MOVWF | STATUS_TEMP       | ;save status to bank 0<br>;register                                         |

| :     |                   |                                                                             |

| :     | (ISR)             |                                                                             |

| :     |                   |                                                                             |

| SWAPF | STATUS_TEMP,<br>W | ;swap STATUS_TEMP register<br>;into W, sets bank to origi-<br>nal<br>;state |

| MOVWF | STATUS            | ;move W into STATUS register                                                |

| SWAPF | W_TEMP,F          | ;swap W_TEMP                                                                |

| SWAPF | W_TEMP,W          | ;swap W_TEMP into W                                                         |

## 9.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs with no external circuitry drawing current from the I/O pin and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated      |

|-------|------------------------------------------------|

|       | by a WDT time-out does not drive MCLR pin low. |

|       |                                                |

#### 9.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device RESET. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. PD bit, which is set on power-up, is cleared when SLEEP is invoked. TO bit is cleared if WDT wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction after the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

**Note:** If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from SLEEP. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes up from SLEEP, regardless of the source of wake-up.

| Q1 Q2 Q                  | 3 Q4 Q1 Q2 Q3 Q4 Q | Q1                    | Q1 Q2 Q3 Q4      | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 0    | Q1 Q2 Q3 Q4 |

|--------------------------|--------------------|-----------------------|------------------|-------------|------------------|-------------|

| OSC1 //////              |                    | AAAAA                 |                  |             |                  |             |

| CLKOUT(4)                |                    | Tost(2)               | <u> </u>         |             | \ <u>`</u>       |             |

| INT pin                  | 1 I                |                       | 1<br>1           |             | 1                |             |

| NTF flag                 |                    |                       | Interrupt Latend | SV.         |                  |             |

| INTCON<1>)               |                    | <del>≉</del>          | (Note 2)         | ,           |                  |             |

| GIE bit<br>INTCON<7>)    |                    | Processor in<br>SLEEP | 1                |             |                  |             |

| INSTRUCTION FLOW         |                    |                       | 1<br>1<br>1      |             | 1                |             |

| PC X PC                  | <u>Υ PC+1 Χ</u>    | PC+2                  | X PC+2           | PC + 2      | <u>χ 0004h χ</u> | 0005h       |

| Instruction { Inst(PC) = | SLEEP Inst(PC + 1) |                       | Inst(PC + 2)     |             | Inst(0004h)      | Inst(0005h) |

| Instruction Inst(PC      | - 1) SLEEP         |                       | Inst(PC + 1)     | Dummy cycle | Dummy cycle      | Inst(0004h) |

## FIGURE 9-18: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**3:** GIE = '1' assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these Osc modes, but shown here for timing reference.

| INCFSZ                       | Increment f, Skip if 0                                                                                                                                                | IORWF            | Inclusive OR W with f                                                                                                                                                                                        |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                      | [ <i>label</i> ] INCFSZ f,d                                                                                                                                           | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                                                   |

| Operands:                    | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                    | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                           |

| Operation:                   | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                      | Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                                                            |

| Status Affected:             | None                                                                                                                                                                  | Status Affected: | Z                                                                                                                                                                                                            |

| Encoding:                    | 00 1111 dfff ffff                                                                                                                                                     | Encoding:        | 00 0100 dfff ffff                                                                                                                                                                                            |

| Description:                 | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'. | Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.                                        |

|                              | If the result is 0, the next instruc-<br>tion, which is already fetched, is                                                                                           | Words:           | 1                                                                                                                                                                                                            |

|                              | discarded. A NOP is executed                                                                                                                                          | Cycles:          | 1                                                                                                                                                                                                            |

|                              | instead making it a two-cycle                                                                                                                                         | Example          | IORWF RESULT, 0                                                                                                                                                                                              |

| Words:<br>Cycles:<br>Example | instruction.<br>1<br>1(2)<br>HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                       |                  | Before Instruction<br>$\begin{array}{rcl} \text{RESULT} &= & 0x13 \\ W &= & 0x91 \\ \end{array}$ After Instruction<br>$\begin{array}{rcl} \text{RESULT} &= & 0x13 \\ W &= & 0x93 \\ Z &= & 1 \\ \end{array}$ |

|                              | Before Instruction                                                                                                                                                    | MOVLW            | Move Literal to W                                                                                                                                                                                            |

|                              | PC = address HERE<br>After Instruction                                                                                                                                | Syntax:          | [ <i>label</i> ] MOVLW k                                                                                                                                                                                     |

|                              | CNT = CNT + 1                                                                                                                                                         | Operands:        | $0 \le k \le 255$                                                                                                                                                                                            |

|                              | if CNT= 0,<br>PC = address CONTINUE                                                                                                                                   | Operation:       | $k \rightarrow (W)$                                                                                                                                                                                          |

|                              | if CNT≠ 0,                                                                                                                                                            | Status Affected: | None                                                                                                                                                                                                         |

|                              | PC = address HERE +1                                                                                                                                                  | Encoding:        | 11 00xx kkkk kkkk                                                                                                                                                                                            |

| IORLW                        | Inclusive OR Literal with W                                                                                                                                           | Description:     | The eight bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's.                                                                                                             |

| Syntax:                      | [ <i>label</i> ] IORLW k                                                                                                                                              | Words:           | 1                                                                                                                                                                                                            |

| Operands:                    | $0 \le k \le 255$                                                                                                                                                     | Cycles:          | 1                                                                                                                                                                                                            |

| Operation:                   | (W) .OR. $k \rightarrow$ (W)                                                                                                                                          | Example          | MOVLW 0x5A                                                                                                                                                                                                   |

| Status Affected:             | Z                                                                                                                                                                     | Example          | After Instruction                                                                                                                                                                                            |

| Encoding:                    | 11 1000 kkkk kkkk                                                                                                                                                     |                  | W = 0x5A                                                                                                                                                                                                     |

| Description:                 | The contents of the W register is<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register.                                              |                  |                                                                                                                                                                                                              |

| Words:                       | 1                                                                                                                                                                     |                  |                                                                                                                                                                                                              |

| Cycles:                      | 1                                                                                                                                                                     |                  |                                                                                                                                                                                                              |

| Example                      | IORLW 0x35                                                                                                                                                            |                  |                                                                                                                                                                                                              |

|                              |                                                                                                                                                                       |                  |                                                                                                                                                                                                              |

|                              | Before Instruction<br>W = 0x9A<br>After Instruction                                                                                                                   |                  |                                                                                                                                                                                                              |

W = Z =

0xBF 1

| SWAPF            | Swap Ni                                                            | bbles in                                   | f                                        |                   |  |  |

|------------------|--------------------------------------------------------------------|--------------------------------------------|------------------------------------------|-------------------|--|--|

| Syntax:          | [label]                                                            | SWAPF                                      | f,d                                      |                   |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                 |                                            |                                          |                   |  |  |

| Operation:       | (f<3:0>) -<br>(f<7:4>) -                                           |                                            | <i>,</i> .                               |                   |  |  |

| Status Affected: | None                                                               |                                            |                                          |                   |  |  |

| Encoding:        | 00                                                                 | 1110                                       | dfff                                     | ffff              |  |  |

| Description:     | The upper<br>register 'f<br>0, the res<br>register. I<br>placed in | " are excl<br>sult is plac<br>If 'd' is 1, | hanged<br>ced in <sup>v</sup><br>the res | d. If 'd' is<br>W |  |  |

| Words:           | 1                                                                  |                                            |                                          |                   |  |  |

| Cycles:          | 1                                                                  |                                            |                                          |                   |  |  |

| Example          | SWAPF                                                              | REG,                                       | 0                                        |                   |  |  |

|                  | Before In                                                          | struction                                  |                                          |                   |  |  |

|                  |                                                                    | REG1                                       | = (                                      | DxA5              |  |  |

|                  | After Inst                                                         | ruction                                    |                                          |                   |  |  |

|                  |                                                                    | REG1<br>W                                  |                                          | 0xA5<br>0x5A      |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                 |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                                                            |  |  |  |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                                                  |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                                 |  |  |  |  |

| Status Affected: | None                                                                                                                                                                               |  |  |  |  |

| Encoding:        | 00 0000 0110 Offf                                                                                                                                                                  |  |  |  |  |

| Description:     | The instruction is supported for<br>code compatibility with the<br>PIC16C5X products. Since TRIS<br>registers are readable and<br>writable, the user can directly<br>address them. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                  |  |  |  |  |

| Example          |                                                                                                                                                                                    |  |  |  |  |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup> prod-<br>ucts, do not use this<br>instruction.                                                             |  |  |  |  |

| XORLW                                                                                                    | Exclusive OR Literal with W                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                  | [ <i>label</i> XORLW k<br>]                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Operands:                                                                                                | $0 \le k \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Operation:                                                                                               | (W) .XOR. $k \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Encoding:                                                                                                | 11 1010 kkkk kkkk                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Description:                                                                                             | The contents of the W register<br>are XOR'ed with the eight bit<br>literal 'k'. The result is placed in<br>the W register.                                                                                                                                                                                                                                                                                                                                                        |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Example:                                                                                                 | XORLW 0xAF                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                          | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                          | W = 0xB5                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                          | After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                          | W = 0x1A                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| XORWF                                                                                                    | Evolucius OD W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                          | Exclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Syntax:                                                                                                  | [ <i>label</i> ] XORWF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Syntax:                                                                                                  | [ <i>label</i> ] XORWF f,d $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Syntax:<br>Operands:                                                                                     | $ \begin{array}{ll} \textit{[label]} & XORWF & f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \end{array} $                                                                                                                                                                                                                                                                                                                                                                              |

| Syntax:<br>Operands:<br>Operation:                                                                       | $ \begin{array}{ll} \textit{[label]} & \text{XORWF} & \textit{f,d} \\ 0 \leq \textit{f} \leq 127 \\ d \in [0,1] \\ (W) & \text{XOR.} & (\textit{f}) \rightarrow (\textit{dest}) \end{array} $                                                                                                                                                                                                                                                                                     |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] XORWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                                                                                                                                                                                       |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{array}{c c} \textit{[label]} & \text{XORWF} & \textit{f,d} \\ 0 \leq \textit{f} \leq 127 \\ d \in [0,1] \\ (W) . \text{XOR.} (\textit{f}) \rightarrow (\text{dest}) \\ \hline Z \\ \hline \hline 00 & 0110 & \text{dfff} & \text{ffff} \\ \hline \text{Exclusive OR the contents of the} \\ W \text{ register with register 'f'. If 'd' is} \\ 0, \text{ the result is stored in the W} \\ \hline \text{register. If 'd' is 1, the result is} \end{array}$                |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d$ $0 \le f \le 127$ $d \in [0,1]$ $(W) . \text{XOR. } (f) \rightarrow (\text{dest})$ Z $\boxed{00 \qquad 0110  \text{dfff}  \text{ffff}}$ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'.                                                                                                      |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $[label] XORWF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (W) .XOR. (f) $\rightarrow$ (dest) Z $\boxed{00 \qquad 0110 \qquad dfff \qquad ffff}$ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. 1                                                                                                                                                           |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | [ <i>label</i> ] XORWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)<br>Z<br>00 0110 dfff ffff<br>Exclusive OR the contents of the<br>W register with register 'f'. If 'd' is<br>0, the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'.<br>1<br>1                                                                                                                                             |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \\ XORWF REG 1 \\ \end{bmatrix}$                                                                                    |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) . XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \\ XORWF & REG & 1 \\ \hline Before Instruction \\ REG & = 0xAF \\ \end{bmatrix}$                     |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF}  f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \\ XORWF & REG & 1 \\ \hline Before Instruction \\ \hline REG &= 0xAF \\ W &= 0xB5 \\ \end{bmatrix}$ |

# 11.0 DEVELOPMENT SUPPORT

The PICmicro<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB C30 C Compiler

- MPLAB ASM30 Assembler/Linker/Library

- · Simulators

- MPLAB SIM Software Simulator

- MPLAB dsPIC30 Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup> 1 Demonstration Board

- PICDEM.net<sup>™</sup> Demonstration Board

- PICDEM 2 Plus Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 4 Demonstration Board

- PICDEM 17 Demonstration Board

- PICDEM 18R Demonstration Board

- PICDEM LIN Demonstration Board

- PICDEM USB Demonstration Board

- Evaluation Kits

- KEELOQ®

- PICDEM MSC

- microID®

- CAN

- PowerSmart®

- Analog

## 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- · A full-featured editor with color coded context

- · A multiple project manager

- Customizable data windows with direct edit of contents

- · High level source code debugging

- Mouse over variable inspection

- Extensive on-line help

- The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PICmicro emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files (assembly or C)

- absolute listing file (mixed assembly and C)

- machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost effective simulators, through low cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increasing flexibility and power.

## 11.2 MPASM Assembler

The MPASM assembler is a full-featured, universal macro assembler for all PICmicro MCUs.

The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects

- · User defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

# 12.0 ELECTRICAL SPECIFICATIONS

## Absolute Maximum Ratings †

| Ambient Temperature under bias                                                                                 | 40° to +125°C                    |

|----------------------------------------------------------------------------------------------------------------|----------------------------------|

| Storage Temperature                                                                                            | 65° to +150°C                    |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                   | 0.6V to VDD +0.6V                |

| Voltage on VDD with respect to Vss                                                                             | 0 to +7.5V                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                   | 0 to +14V                        |

| Voltage on RA4 with respect to Vss                                                                             |                                  |

| Total power Dissipation (Note 1)                                                                               | 1.0W                             |

| Maximum Current out of Vss pin                                                                                 | 300 mA                           |

| Maximum Current into VDD pin                                                                                   | 250 mA                           |

| Input Clamp Current, Iк (Vi <0 or Vi> VDD)                                                                     | ±20 mA                           |

| Output Clamp Current, Iок (Vo <0 or Vo>VDD)                                                                    | ±20 mA                           |

| Maximum Output Current sunk by any I/O pin                                                                     | 25 mA                            |

| Maximum Output Current sourced by any I/O pin                                                                  | 25 mA                            |

| Maximum Current sunk by PORTA and PORTB                                                                        | 200 mA                           |

| Maximum Current sourced by PORTA and PORTB                                                                     | 200 mA                           |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) | ) x IOH} + $\Sigma$ (VOI x IOL). |

2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latchup. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

**† NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended) (CONT.)

|                                         |                                                  |                                                                                                                                                                                               |                                                                                                   | Standard Operating Conditions (unless otherwise stated) |                               |                            |                                                                                                                                                                                                                                        |  |  |  |  |

|-----------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIC16C                                  | 62X                                              |                                                                                                                                                                                               | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C = 0^{\circ}C \le TA \le +70^{\circ}C$ |                                                         |                               |                            | $\begin{array}{ll} 0^{\circ}C & \leq TA \leq +85^{\circ}C \text{ for industrial and} \\ 0^{\circ}C & \leq TA \leq +70^{\circ}C \text{ for commercial and} \\ 0^{\circ}C & \leq TA \leq +125^{\circ}C \text{ for extended} \end{array}$ |  |  |  |  |

| PIC16LC62X                              |                                                  |                                                                                                                                                                                               |                                                                                                   | $\begin{array}{llllllllllllllllllllllllllllllllllll$    |                               |                            |                                                                                                                                                                                                                                        |  |  |  |  |

| Param<br>. No.                          | Sym                                              | Characteristic                                                                                                                                                                                | Min                                                                                               | Тур†                                                    | Мах                           | Units                      | Conditions                                                                                                                                                                                                                             |  |  |  |  |

| D022<br>D022A<br>D023<br>D023A<br>D0222 | ΔIWDT<br>ΔIBOR<br>ΔICOM<br>P<br>ΔIVREF<br>ΔIVREF | WDT Current <sup>(5)</sup><br>Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each<br>Comparator <sup>(5)</sup><br>VREF Current <sup>(5)</sup><br>WDT Current <sup>(5)</sup> |                                                                                                   | 6.0<br>350<br>—<br>6.0                                  | 20<br>25<br>425<br>100<br>300 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | VDD=4.0V $(125°C)$ BOD enabled, VDD = 5.0V<br>VDD = 4.0V<br>VDD = 4.0V<br>VDD=3.0V                                                                                                                                                     |  |  |  |  |

| D022A<br>D023<br>D023A                  | ΔIBOR<br>ΔICOM<br>P<br>ΔIVREF                    | Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each<br>Comparator <sup>(5)</sup><br>VREF Current <sup>(5)</sup>                                                             |                                                                                                   | 350<br>—                                                | 425<br>100<br>300             | μΑ<br>μΑ<br>μΑ             | BOD enabled, VDD = 5.0V<br>VDD = 3.0V<br>VDD = 3.0V                                                                                                                                                                                    |  |  |  |  |

| 1A                                      | Fosc                                             | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency                                              | 0<br>0<br>0<br>0                                                                                  |                                                         | 200<br>4<br>4<br>20           | kHz<br>MHz<br>MHz<br>MHz   | All temperatures<br>All temperatures<br>All temperatures<br>All temperatures                                                                                                                                                           |  |  |  |  |