Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 80 × 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

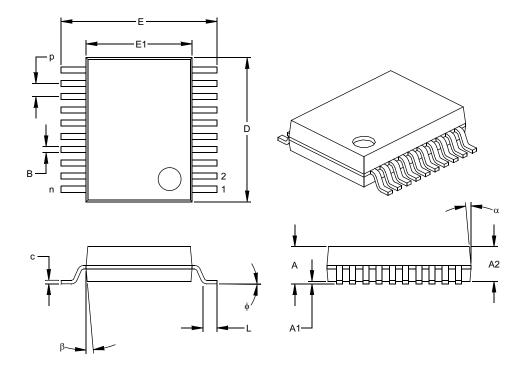

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c621t-20-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART, PRO MATE and PowerSmart are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Accuron, Application Maestro, dsPIC, dsPICDEM, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICkit, PICDEM, PICDEM.net, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPIC, Select Mode, SmartSensor, SmartShunt, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

## 2.0 PIC16C62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C62X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

## 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the Oscillator modes.

Microchip's PICSTART<sup>®</sup> and PRO MATE<sup>®</sup> programmers both support programming of the PIC16C62X.

Note: Microchip does not recommend code protecting windowed devices.

## 2.2 One-Time-Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

## 2.3 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who chose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices, but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

## 2.4 Serialized Quick-Turnaround-Production<sup>sm</sup> (SQTP<sup>sm</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry-code, password or ID number.

| Name         | DIP/SOIC<br>Pin # | SSOP<br>Pin # | I/O/P Type             | Buffer<br>Type        | Description                                                                                                                                                                                                         |

|--------------|-------------------|---------------|------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 16                | 18            | I                      | ST/CMOS               | Oscillator crystal input/external clock source input.                                                                                                                                                               |

| OSC2/CLKOUT  | 15                | 17            | 0                      | _                     | Oscillator crystal output. Connects to crystal or resonator<br>in Crystal Oscillator mode. In RC mode, OSC2 pin out-<br>puts CLKOUT, which has 1/4 the frequency of OSC1<br>and denotes the instruction cycle rate. |

| MCLR/VPP     | 4                 | 4             | I/P                    | ST                    | Master Clear (Reset) input/programming voltage input.<br>This pin is an Active Low Reset to the device.                                                                                                             |

|              |                   |               |                        |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                                 |

| RA0/AN0      | 17                | 19            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |

| RA1/AN1      | 18                | 20            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |

| RA2/AN2/VREF | 1                 | 1             | I/O                    | ST                    | Analog comparator input or VREF output                                                                                                                                                                              |

| RA3/AN3      | 2                 | 2             | I/O                    | ST                    | Analog comparator input /output                                                                                                                                                                                     |

| RA4/T0CKI    | 3                 | 3             | I/O                    | ST                    | Can be selected to be the clock input to the Timer<br>timer/counter or a comparator output. Output is<br>open drain type.                                                                                           |

|              |                   |               |                        |                       | PORTB is a bi-directional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs.                                                                                                 |

| RB0/INT      | 6                 | 7             | I/O                    | TTL/ST <sup>(1)</sup> | RB0/INT can also be selected as an externa interrupt pin.                                                                                                                                                           |

| RB1          | 7                 | 8             | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB2          | 8                 | 9             | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB3          | 9                 | 10            | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB4          | 10                | 11            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |

| RB5          | 11                | 12            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |

| RB6          | 12                | 13            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming clock                                                                                                                                                                   |

| RB7          | 13                | 14            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming data.                                                                                                                                                                   |

| Vss          | 5                 | 5,6           | Р                      |                       | Ground reference for logic and I/O pins.                                                                                                                                                                            |

| Vdd          | 14                | 15,16         | Р                      | _                     | Positive supply for logic and I/O pins.                                                                                                                                                                             |

| Legend:      | O = out<br>— = No | •             | I/O = inp<br>I = Input | ut/output             | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                             |

TTL = TTL input

**Note** 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### **OPTION Register** 4.2.2.2

The OPTION register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |

|-------|-------------------------------------------|

|       | TMR0, assign the prescaler to the WDT     |

|       | (PSA = 1).                                |

|         | R/W-1                                                                                                            | R/W-1                          | R/W-1                      | R/W-1                        | R/W-1         | R/W-1           | R/W-1 | R/W-1 |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------|------------------------------|---------------|-----------------|-------|-------|--|--|--|

|         | RBPU                                                                                                             | INTEDG                         | TOCS                       | TOSE                         | PSA           | PS2             | PS1   | PS0   |  |  |  |

|         | bit 7                                                                                                            |                                |                            |                              |               | •               |       | bit 0 |  |  |  |

| bit 7   | RBPU: PO                                                                                                         | RTB Pull-u                     | p Enable bi                | it                           |               |                 |       |       |  |  |  |

|         |                                                                                                                  | 3 pull-ups ai<br>3 pull-ups ai |                            | y individual                 | port latch va | alues           |       |       |  |  |  |

| bit 6   | INTEDG: I                                                                                                        | nterrupt Edg                   | e Select bit               | -                            |               |                 |       |       |  |  |  |

|         |                                                                                                                  |                                | edge of RB0<br>edge of RB0 |                              |               |                 |       |       |  |  |  |

| bit 5   | TOCS: TMI                                                                                                        | R0 Clock Sc                    | ource Select               | bit                          |               |                 |       |       |  |  |  |

|         |                                                                                                                  | ion on RA4/<br>Il instruction  | T0CKI pin<br>cycle clock   | (CLKOUT)                     |               |                 |       |       |  |  |  |

| bit 4   | TOSE: TM                                                                                                         | R0 Source E                    | Edge Select                | bit                          |               |                 |       |       |  |  |  |

|         |                                                                                                                  |                                |                            | ition on RA4<br>ition on RA4 |               |                 |       |       |  |  |  |

| bit 3   | PSA: Pres                                                                                                        | caler Assigr                   | iment bit                  |                              | -             |                 |       |       |  |  |  |

|         | <ul> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul> |                                |                            |                              |               |                 |       |       |  |  |  |

| bit 2-0 | PS<2:0>: Prescaler Rate Select bits                                                                              |                                |                            |                              |               |                 |       |       |  |  |  |

|         | E                                                                                                                | Bit Value T                    | MR0 Rate                   | WDT Rate                     |               |                 |       |       |  |  |  |

|         | -                                                                                                                | 000<br>001                     | 1:2<br>1:4                 | 1:1<br>1:2                   |               |                 |       |       |  |  |  |

|         |                                                                                                                  | 010<br>011                     | 1 : 8<br>1 : 16            | 1:4<br>1:8                   |               |                 |       |       |  |  |  |

|         |                                                                                                                  | 100                            | 1:32                       | 1:16                         |               |                 |       |       |  |  |  |

|         |                                                                                                                  | 101                            | 1:64                       | 1:32                         |               |                 |       |       |  |  |  |

|         | 110 1:128 1:64                                                                                                   |                                |                            |                              |               |                 |       |       |  |  |  |

|         |                                                                                                                  | 111                            | 1:256                      | 1 : 128                      |               | 111 1.200 1.120 |       |       |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 4.2.2.6 PCON Register

The PCON register contains flag bits to differentiate between a Power-on Reset, an external MCLR Reset, WDT Reset or a Brown-out Reset.

| Note: | BOR is unknown on Power-on Reset. It        |

|-------|---------------------------------------------|

|       | must then be set by the user and checked    |

|       | on subsequent RESETS to see if BOR is       |

|       | cleared, indicating a brown-out has         |

|       | occurred. The BOR STATUS bit is a "don't    |

|       | care" and is not necessarily predictable if |

|       | the brown-out circuit is disabled (by       |

|       | programming BODEN bit in the                |

|       | Configuration word).                        |

### REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

|   | U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|---|-------|-----|-----|-----|-----|-----|-------|-------|

| ſ | —     | —   | —   | —   | —   | —   | POR   | BOR   |

| - | bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR**: Power-on Reset STATUS bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 **BOR**: Brown-out Reset STATUS bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The code example in Example 7-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

### EXAMPLE 7-1: INITIALIZING COMPARATOR MODULE

| MOVLW | 0x03         | ;Init comparator mode             |

|-------|--------------|-----------------------------------|

| MOVWF | CMCON        | ;CM<2:0> = 011                    |

| CLRF  | PORTA        | ;Init PORTA                       |

| BSF   | STATUS, RPO  | ;Select Bank1                     |

| MOVLW | 0x07         | ;Initialize data direction        |

| MOVWF | TRISA        | ;Set RA<2:0> as inputs            |

|       |              | ;RA<4:3> as outputs               |

|       |              | ;TRISA<7:5> always read `0'       |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| CALL  | DELAY 10     | ;10µs delay                       |

| MOVF  | CMCON,F      | ;Read CMCONtoend change condition |

| BCF   | PIR1,CMIF    | ;Clear pending interrupts         |

| BSF   | STATUS, RPO  | ;Select Bank 1                    |

| BSF   | PIE1,CMIE    | ;Enable comparator interrupts     |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| BSF   | INTCON, PEIE | ;Enable peripheral interrupts     |

| BSF   | INTCON, GIE  | ;Global interrupt enable          |

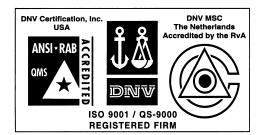

## 7.2 Comparator Operation

A single comparator is shown in Figure 7-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 7-2 represent the uncertainty due to input offsets and response time.

## 7.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator Operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 7-2).

## 7.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSs and VDD, and can be applied to either pin of the comparator(s).

## 7.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 10, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 7-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

## 7.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be RESET by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | If a change in the CMCON register          |

|-------|--------------------------------------------|

|       | (C1OUT or C2OUT) should occur when a       |

|       | read operation is being executed (start of |

|       | the Q2 cycle), then the CMIF (PIR1<6>)     |

|       | interrupt flag may not get set.            |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

## 7.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will

Vdd ∆Vt = 0.6V RIC Rs < 10K Δικ **I**LEAKAGE CPIN VT = 0.6V ±500 nA 5 pF Vss Input Capacitance Legend CPIN = Threshold Voltage Vт = Leakage Current at the pin due to various junctions ILEAKAGE = = Interconnect Resistance RIC Rs = Source Impedance Analog Voltage VA =

FIGURE 7-4: ANALOG INPUT MODEL

wake up the device from SLEEP mode when enabled. While the comparator is powered-up, higher SLEEP currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering SLEEP. If the device wakes up from SLEEP, the contents of the CMCON register are not affected.

## 7.8 Effects of a RESET

A device RESET forces the CMCON register to its RESET state. This forces the comparator module to be in the comparator RESET mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at RESET time. The comparators will be powered-down during the RESET interval.

## 7.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 7-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latchup may occur. A maximum source impedance of  $10 \ k\Omega$ is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

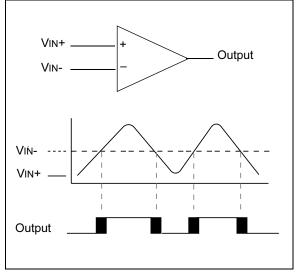

#### 8.0 **VOLTAGE REFERENCE** MODULE

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Register 8-1. The block diagram is given in Figure 8-1.

#### 8.1 **Configuring the Voltage Reference**

The Voltage Reference can output 16 distinct voltage levels for each range. The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 0: VREF = (VDD x 1/4) + (VR<3:0>/32) x VDD

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 12-1). Example 8-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

|                                                                             | R/W-0                                | R/W-0                                                                      | R/W-0                      | U-0                     | R/W-0       | R/W-0      | R/W-0        | R/W-0  |  |  |  |  |  |

|-----------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------|----------------------------|-------------------------|-------------|------------|--------------|--------|--|--|--|--|--|

|                                                                             | VREN                                 | VROE                                                                       | Vrr                        | —                       | VR3         | VR2        | VR1          | VR0    |  |  |  |  |  |

|                                                                             | bit 7                                |                                                                            |                            |                         |             |            |              | bit 0  |  |  |  |  |  |

|                                                                             |                                      |                                                                            |                            |                         |             |            |              |        |  |  |  |  |  |

| bit 7                                                                       | VREN: VREF Enable                    |                                                                            |                            |                         |             |            |              |        |  |  |  |  |  |

|                                                                             |                                      | 1 = VREF circuit powered on<br>0 = VREF circuit powered down, no IDD drain |                            |                         |             |            |              |        |  |  |  |  |  |

| bit 6                                                                       | Vroe: Vref Output Enable             |                                                                            |                            |                         |             |            |              |        |  |  |  |  |  |

|                                                                             |                                      | s output on F                                                              | RA2 pin<br>ed from RA2     | 2 nin                   |             |            |              |        |  |  |  |  |  |

| bit 5                                                                       |                                      | Range sele                                                                 |                            | 2 pm                    |             |            |              |        |  |  |  |  |  |

| bit o                                                                       | 1 = Low Ra                           |                                                                            |                            |                         |             |            |              |        |  |  |  |  |  |

|                                                                             | 0 = High R                           | ange                                                                       |                            |                         |             |            |              |        |  |  |  |  |  |

| bit 4                                                                       | Unimplem                             | ented: Rea                                                                 | d as '0'                   |                         |             |            |              |        |  |  |  |  |  |

| bit 3-0                                                                     |                                      |                                                                            |                            | VR [3:0] ≤ 1            | 5           |            |              |        |  |  |  |  |  |

|                                                                             |                                      |                                                                            | (VR<3:0>/ 2<br>1/4 * Voo + | 4) * VDD<br>(VR<3:0>/ 3 | 2) * \/חח   |            |              |        |  |  |  |  |  |

|                                                                             |                                      | - 0. VILLI -                                                               |                            | (111-0.0-7-0            | 2) 100      |            |              |        |  |  |  |  |  |

|                                                                             | Legend:                              |                                                                            |                            |                         |             |            |              |        |  |  |  |  |  |

|                                                                             | R = Reada                            | ble bit                                                                    | W = W                      | /ritable bit            | U = Unim    | nplemented | bit, read as | '0'    |  |  |  |  |  |

|                                                                             | - n = Value                          | at POR                                                                     | '1' = B                    | it is set               | '0' = Bit i | s cleared  | x = Bit is u | nknown |  |  |  |  |  |

| 8-1:                                                                        | 8-1: VOLTAGE REFERENCE BLOCK DIAGRAM |                                                                            |                            |                         |             |            |              |        |  |  |  |  |  |

|                                                                             |                                      |                                                                            | 16 \$                      | Stages                  |             |            |              |        |  |  |  |  |  |

| $\sim$                                                                      |                                      | _                                                                          |                            |                         | _           | _          |              |        |  |  |  |  |  |

| $-\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | 에드 8R                                | R                                                                          | R                          | R                       | R           |            |              |        |  |  |  |  |  |

|                                                                             |                                      |                                                                            |                            |                         |             |            |              |        |  |  |  |  |  |

#### **REGISTER 8-1:** VRCON REGISTER(ADDRESS 9Fh)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### **FIGURE 8-**

## 9.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16C62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-Circuit Serial Programming™

The PIC16C62X devices have a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 9.4.5 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with <u>PWRTE</u> bit erased (<u>PWRT</u> disabled), there will be no time-out at all. Figure 9-8, Figure 9-9 and Figure 9-10 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 9-9). This is useful for testing purposes or to synchronize more than one PIC16C62X device operating in parallel.

Table 9-4 shows the RESET conditions for some special registers, while Table 9-5 shows the RESET conditions for all the registers.

## 9.4.6 POWER CONTROL (PCON)/ STATUS REGISTER

The power control/STATUS register, PCON (address 8Eh), has two bits.

Bit0 is  $\overline{\text{BOR}}$  (Brown-out).  $\overline{\text{BOR}}$  is unknown on Poweron Reset. It must then be set by the user and checked on subsequent RESETS to see if  $\overline{\text{BOR}} = 0$ , indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$  STATUS bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent RESET, if POR is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe              | er-up     | Brown-out Reset   | Wake-up<br>from SLEEP |  |

|--------------------------|-------------------|-----------|-------------------|-----------------------|--|

|                          | PWRTE = 0         | PWRTE = 1 | Brown-out Reset   |                       |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc             |  |

| RC                       | 72 ms             | _         | 72 ms             | _                     |  |

## TABLE 9-1: TIME-OUT IN VARIOUS SITUATIONS

| <b>TABLE 9-2</b> : | STATUS/PCON BITS AND THEIR SIGNIFICANCE |

|--------------------|-----------------------------------------|

|--------------------|-----------------------------------------|

| POR | BOR | то | PD |                                    |

|-----|-----|----|----|------------------------------------|

| 0   | Х   | 1  | 1  | Power-on Reset                     |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR          |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR          |

| 1   | 0   | Х  | Х  | Brown-out Reset                    |

| 1   | 1   | 0  | u  | WDT Reset                          |

| 1   | 1   | 0  | 0  | WDT Wake-up                        |

| 1   | 1   | u  | u  | MCLR Reset during normal operation |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP            |

Legend: u = unchanged, x = unknown

### TABLE 9-3: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 83h     | STATUS |       |       |       | TO    | PD    |       |       |       | 0001 1xxx             | 000q quuu                                      |

| 8Eh     | PCON   | _     | _     |       | _     | _     | _     | POR   | BOR   | 0x                    | uq                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                          | CALL             | Call Subroutine                                                                                                                                                            |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                              | Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                    |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                | Operands:        | $0 \leq k \leq 2047$                                                                                                                                                       |  |

|                  | $0 \le b < 7$                                                                                                                                    | Operation:       | $(PC)$ + 1 $\rightarrow$ TOS,                                                                                                                                              |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                          |                  | $k \rightarrow PC<10:0>$ ,<br>(PCLATH<4:3>) $\rightarrow PC<12:11>$                                                                                                        |  |

| Status Affected: | None                                                                                                                                             | Status Affected: | None                                                                                                                                                                       |  |

| Encoding:        | 01 11bb bfff ffff                                                                                                                                | Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                          |  |

| Description:     | If bit 'b' in register 'f' is '1', then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next instruc-                         | Description:     | Call Subroutine. First, return<br>address (PC+1) is pushed onto                                                                                                            |  |

|                  | tion fetched during the current<br>instruction execution, is discarded<br>and a NOP is executed instead,<br>making this a two-cycle instruction. |                  | the stack. The eleven bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. |  |

| Words:           | 1                                                                                                                                                | Words:           | 1                                                                                                                                                                          |  |

| Cycles:          | 1(2)                                                                                                                                             | Cycles:          | 2                                                                                                                                                                          |  |

| Example          | HERE BTFSS <b>FLAG,1</b><br>FALSE GOTO <b>PROCESS_CO</b>                                                                                         | Example          | HERE CALL                                                                                                                                                                  |  |

|                  | TRUE DE                                                                                                                                          | Example          | THER                                                                                                                                                                       |  |

|                  | Before Instruction<br>PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,<br>PC = address FALSE<br>if FLAG<1> = 1,                         |                  | Before Instruction<br>PC = Address HERE<br>After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                 |  |

|                  | PC = address TRUE                                                                                                                                | CLRF             | Clear f                                                                                                                                                                    |  |

|                  |                                                                                                                                                  | Syntax:          | [label] CLRF f                                                                                                                                                             |  |

|                  |                                                                                                                                                  | Operands:        | $0 \leq f \leq 127$                                                                                                                                                        |  |

|                  |                                                                                                                                                  | Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$                                                                                                      |  |

|                  |                                                                                                                                                  | Status Affected: | Z                                                                                                                                                                          |  |

|                  |                                                                                                                                                  | Encoding:        | 00 0001 1fff ffff                                                                                                                                                          |  |

|                  |                                                                                                                                                  | Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.                                                                                                          |  |

|                  |                                                                                                                                                  | Words:           | 1                                                                                                                                                                          |  |

|                  |                                                                                                                                                  | Cycles:          | 1                                                                                                                                                                          |  |

|                  |                                                                                                                                                  | Example          | CLRF FLAG_REG                                                                                                                                                              |  |

|                  |                                                                                                                                                  |                  | Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction                                                                                                                 |  |

|                  |                                                                                                                                                  |                  | $FLAG_REG = 0x00$<br>Z = 1                                                                                                                                                 |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                          |           |            |              |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|--------------|--|--|--|--|

| Syntax:          | [label]                                                                                                                                                                    | SWAPF     | f,d        |              |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                          |           |            |              |  |  |  |  |

| Operation:       | (f<3:0>) -<br>(f<7:4>) -                                                                                                                                                   |           | <i>,</i> . |              |  |  |  |  |

| Status Affected: | None                                                                                                                                                                       |           |            |              |  |  |  |  |

| Encoding:        | 00                                                                                                                                                                         | 1110      | dfff       | ffff         |  |  |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in W<br>register. If 'd' is 1, the result is<br>placed in register 'f'. |           |            |              |  |  |  |  |

| Words:           | 1                                                                                                                                                                          |           |            |              |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                          |           |            |              |  |  |  |  |

| Example          | SWAPF                                                                                                                                                                      | REG,      | 0          |              |  |  |  |  |

|                  | Before In                                                                                                                                                                  | struction |            |              |  |  |  |  |

|                  |                                                                                                                                                                            | REG1      | = (        | DxA5         |  |  |  |  |

|                  | After Inst                                                                                                                                                                 | ruction   |            |              |  |  |  |  |

|                  |                                                                                                                                                                            | REG1<br>W |            | 0xA5<br>0x5A |  |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                 |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                                                            |  |  |  |  |  |  |  |

| Operands:        | $5 \le f \le 7$                                                                                                                                                                    |  |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow TRIS$ register f;                                                                                                                                                 |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                               |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 0110 Offf                                                                                                                                                                  |  |  |  |  |  |  |  |

| Description:     | The instruction is supported for<br>code compatibility with the<br>PIC16C5X products. Since TRIS<br>registers are readable and<br>writable, the user can directly<br>address them. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Example          |                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup> prod-<br>ucts, do not use this<br>instruction.                                                             |  |  |  |  |  |  |  |

| XORLW                                                                                         | Exclusive OR Literal with W                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                                                       | [ <i>label</i> XORLW k<br>]                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Operands:                                                                                     | $0 \le k \le 255$                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Operation:                                                                                    | (W) .XOR. $k \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Status Affected:                                                                              | Z                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Encoding:                                                                                     | 11 1010 kkkk kkkk                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Description:                                                                                  | The contents of the W register<br>are XOR'ed with the eight bit<br>literal 'k'. The result is placed in<br>the W register.                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Words:                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Cycles:                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Example:                                                                                      | XORLW 0xAF                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                                                                                               | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                                                                                               | W = 0xB5                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                                                                                               | After Instruction                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                                                                                               | W = 0x1A                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| XORWF                                                                                         | Exclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Syntax:                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                                                                                               | [ <i>label</i> ] XORWF f,d                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Operands:                                                                                     | $ \begin{array}{l} \left[ \begin{array}{c} \textit{label} \end{array} \right]  \text{XORWF}  f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \end{array} $                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| -                                                                                             | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Operands:                                                                                     | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Operands:<br>Operation:                                                                       | $0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Operands:<br>Operation:<br>Status Affected:                                                   | $0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) . XOR. (f) \rightarrow (dest) \\ \hline Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W \\ register. If 'd' is 1, the result is \\ \end{array}$                                                                                                       |  |  |  |  |  |  |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) . XOR. (f) \rightarrow (dest) \\ \hline Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W \\ register. If 'd' is 1, the result is \\ stored back in register 'f'. \end{array}$                                                                          |  |  |  |  |  |  |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) . XOR. (f) \rightarrow (dest) \\ \hline Z \\ \hline \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W \\ register. If 'd' is 1, the result is \\ stored back in register 'f'. \\ 1 \end{array}$                                                              |  |  |  |  |  |  |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) . XOR. (f) \rightarrow (dest) \\ \hline Z \\ \hline \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W \\ register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \end{array}$                                                            |  |  |  |  |  |  |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) . XOR. (f) \rightarrow (dest) \\ \hline Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W \\ register. If 'd' is 1, the result is \\ stored back in register 'f'. \\ 1 \\ 1 \\ XORWF & REG & 1 \\ \end{array}$                                          |  |  |  |  |  |  |