Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c622-04i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

NOTES:

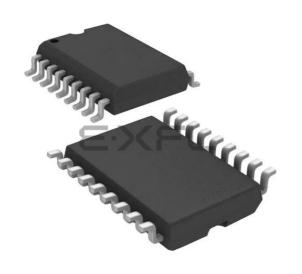

## FIGURE 3-1: BLOCK DIAGRAM

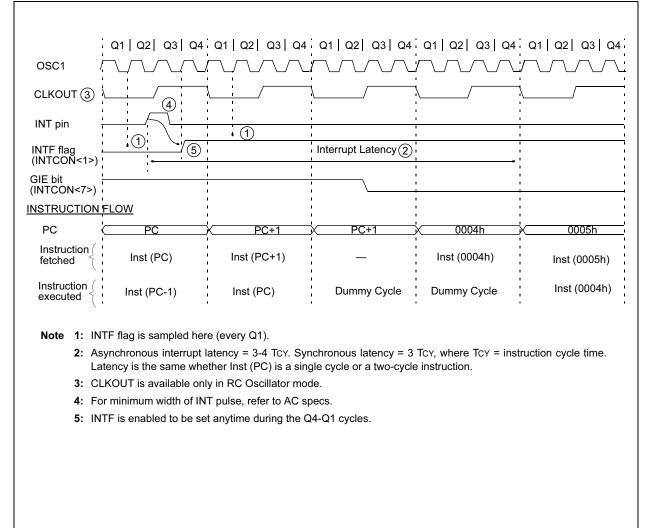

## 3.1 Clocking Scheme/Instruction Cycle

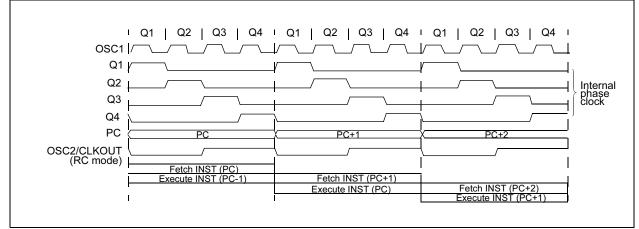

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

## 3.2 Instruction Flow/Pipelining

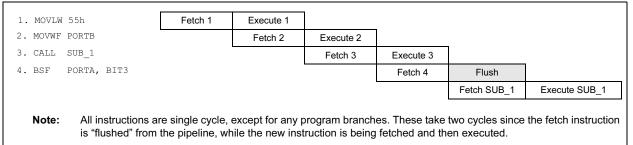

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

## 4.0 MEMORY ORGANIZATION

## 4.1 Program Memory Organization

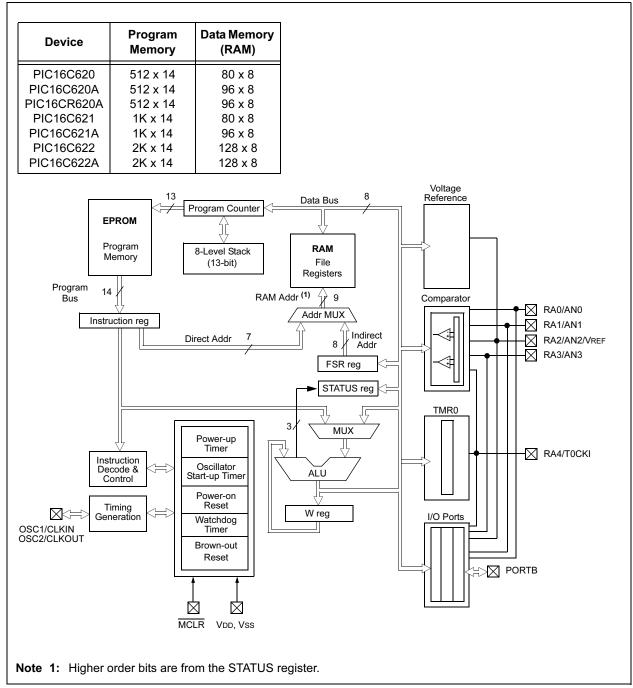

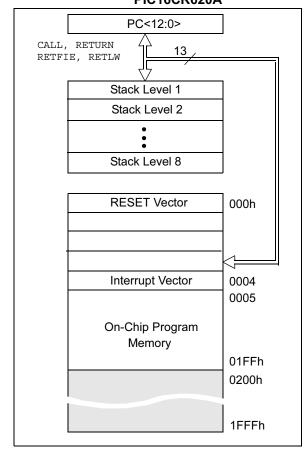

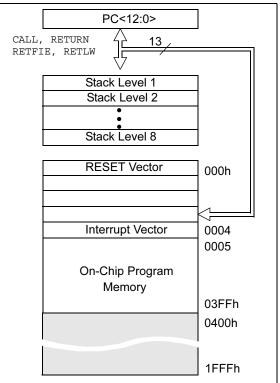

The PIC16C62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C620(A) and PIC16CR620, 1K x 14 (0000h - 03FFh) for the PIC16C621(A) and 2K x 14 (0000h - 07FFh) for the PIC16C622(A) are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16C(R)620(A)) or 1K x 14 space (PIC16C621(A)) or 2K x 14 space (PIC16C622(A)). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16C620/PIC16C620A/

PIC16C620/PIC16C620 PIC16CR620A

## FIGURE 4-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C621/PIC16C621A

FIGURE 4-3:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C622/PIC16C622A

## 4.2 Data Memory Organization

The data memory (Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7) is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20-7Fh (Bank0) on the PIC16C620A/CR620A/621A and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16C622 and PIC16C622A are General Purpose Registers implemented as static RAM. Some Special Purpose Registers are mapped in Bank 1.

Addresses F0h-FFh of bank1 are implemented as common ram and mapped back to addresses 70h-7Fh in bank0 on the PIC16C620A/621A/622A/CR620A.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 80 x 8 in the PIC16C620/621, 96 x 8 in the PIC16C620A/621A/CR620A and 128 x 8 in the PIC16C622(A). Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

### TABLE 5-1:PORTA FUNCTIONS

| Name         | Bit # | Buffer<br>Type | Function                                                                                          |

|--------------|-------|----------------|---------------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0  | ST             | Input/output or comparator input                                                                  |

| RA1/AN1      | bit1  | ST             | Input/output or comparator input                                                                  |

| RA2/AN2/VREF | bit2  | ST             | Input/output or comparator input or VREF output                                                   |

| RA3/AN3      | bit3  | ST             | Input/output or comparator input/output                                                           |

| RA4/T0CKI    | bit4  | ST             | Input/output or external clock input for TMR0 or comparator output.<br>Output is open drain type. |

Legend: ST = Schmitt Trigger input

## TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|------------|------------|------------|------------|------------|-----------------|---------------------------------|

| 05h     | PORTA |       |       |       | RA4        | RA3        | RA2        | RA1        | RA0        | x 0000          | u 0000                          |

| 85h     | TRISA |       |       | _     | TRISA<br>4 | TRISA<br>3 | TRISA<br>2 | TRISA<br>1 | TRISA<br>0 | 1 1111          | 1 1111                          |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | _          | CIS        | CM2        | CM1        | CM0        | 00 0000         | 00 0000                         |

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _          | VR3        | VR2        | VR1        | VR0        | 000- 0000       | 000- 0000                       |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

Note: Shaded bits are not used by PORTA.

| Name    | Bit # | Buffer Type           | Function                                                                                                                |

|---------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0  | TTL/ST <sup>(1)</sup> | Input/output or external interrupt input. Internal software programmable weak pull-up.                                  |

| RB1     | bit1  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB2     | bit2  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB3     | bit3  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB4     | bit4  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB5     | bit5  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB6     | bit6  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock pin. |

| RB7     | bit7  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data pin.  |

## TABLE 5-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h     | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX XXXX       | uuuu uuuu                       |

| 86h     | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h     | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

Legend: u = unchanged, x = unknown

Note 1: Shaded bits are not used by PORTB.

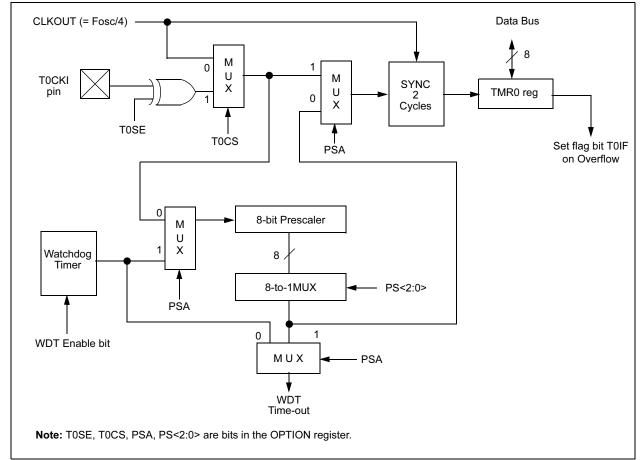

## 6.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 6-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

#### FIGURE 6-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

## 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-Chip Voltage Reference (Section 8.0) can also be an input to the comparators.

The CMCON register, shown in Register 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-1.

## REGISTER 7-1: CMCON REGISTER (ADDRESS 1Fh)

|         |                   |                                 | <b>(</b> | ,   |       |       |       |       |  |

|---------|-------------------|---------------------------------|----------|-----|-------|-------|-------|-------|--|

|         | R-0               | R-0                             | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|         | C2OUT             | C10UT                           | —        | —   | CIS   | CM2   | CM1   | CM0   |  |

|         | bit 7             |                                 |          |     |       |       |       | bit 0 |  |

|         |                   |                                 |          |     |       |       |       |       |  |

| bit 7   | <b>C2OUT</b> : Co | omparator 2                     | output   |     |       |       |       |       |  |

|         | 1 = C2 VIN        | + > C2 VIN-                     |          |     |       |       |       |       |  |

|         | 0 = C2 VIN        | + < C2 VIN-                     |          |     |       |       |       |       |  |

| bit 6   | <b>C1OUT</b> : Co | omparator 1                     | output   |     |       |       |       |       |  |

|         | 1 = C1 VIN        | + > C1 VIN-                     |          |     |       |       |       |       |  |

|         | 0 = C1 VIN        | + < C1 VIN-                     |          |     |       |       |       |       |  |

| bit 5-4 | Unimplem          | ented: Read                     | d as '0' |     |       |       |       |       |  |

| bit 3   | CIS: Comp         | arator Input                    | Switch   |     |       |       |       |       |  |

|         | When CM<          | <2:0>: = 001                    | :        |     |       |       |       |       |  |

|         | 1 = C1 VIN-       | - connects to                   | o RA3    |     |       |       |       |       |  |

|         | 0 = C1 VIN        | - connects to                   | o RA0    |     |       |       |       |       |  |

|         | When CM<          | <2:0> = 010:                    |          |     |       |       |       |       |  |

|         |                   | <ul> <li>connects to</li> </ul> |          |     |       |       |       |       |  |

|         |                   | I- connects t                   |          |     |       |       |       |       |  |

|         |                   | 0 = C1 VIN- connects to RA0     |          |     |       |       |       |       |  |

|         | C2 VIN            | C2 VIN- connects to RA1         |          |     |       |       |       |       |  |

| bit 2-0 | CM<2:0>:          | Comparator                      | mode.    |     |       |       |       |       |  |

|         |                   |                                 |          |     |       |       |       |       |  |

|         | Legend:           |                                 |          |     |       |       |       |       |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The code example in Example 7-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

#### EXAMPLE 7-1: INITIALIZING COMPARATOR MODULE

| MOVLW | 0x03         | ;Init comparator mode             |

|-------|--------------|-----------------------------------|

| MOVWF | CMCON        | ;CM<2:0> = 011                    |

| CLRF  | PORTA        | ;Init PORTA                       |

| BSF   | STATUS, RPO  | ;Select Bank1                     |

| MOVLW | 0x07         | ;Initialize data direction        |

| MOVWF | TRISA        | ;Set RA<2:0> as inputs            |

|       |              | ;RA<4:3> as outputs               |

|       |              | ;TRISA<7:5> always read `0'       |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| CALL  | DELAY 10     | ;10µs delay                       |

| MOVF  | CMCON,F      | ;Read CMCONtoend change condition |

| BCF   | PIR1,CMIF    | ;Clear pending interrupts         |

| BSF   | STATUS, RPO  | ;Select Bank 1                    |

| BSF   | PIE1,CMIE    | ;Enable comparator interrupts     |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| BSF   | INTCON, PEIE | ;Enable peripheral interrupts     |

| BSF   | INTCON, GIE  | ;Global interrupt enable          |

## 7.2 Comparator Operation

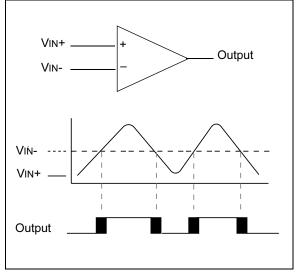

A single comparator is shown in Figure 7-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 7-2 represent the uncertainty due to input offsets and response time.

## 7.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator Operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 7-2).

## 7.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSs and VDD, and can be applied to either pin of the comparator(s).

## 7.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 10, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 7-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

## 9.5.1 RB0/INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered, either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP and Figure 9-18 for timing of wakeup from SLEEP through RB0/INT interrupt.

## 9.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 6.0.

#### 9.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

| Note: | If a change on the I/O pin should occur   |

|-------|-------------------------------------------|

|       | when the read operation is being executed |

|       | (start of the Q2 cycle), then the RBIF    |

|       | interrupt flag may not get set.           |

#### 9.5.4 COMPARATOR INTERRUPT

See Section 7.6 for complete description of comparator interrupts.

#### FIGURE 9-16: INT PIN INTERRUPT TIMING

TABLE 9-6: SUMMARY OF INTERRUPT REGISTERS

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on POR<br>Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 0Bh     | INTCON | GIE   | PEIE  | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1   | —     | CMIF  | —     | —     | —     | —     | —     | —     | -0                    | -0                                             |

| 8Ch     | PIE1   | _     | CMIE  | _     | _     | —     | _     | —     | _     | -0                    | -0                                             |

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

## 9.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and STATUS register). This will have to be implemented in software.

Example 9-3 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x20 in Bank 0 and it must also be defined at 0xA0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 9-3:

- · Stores the W register

- Stores the STATUS register in Bank 0

- Executes the ISR code

- Restores the STATUS (and bank select bit register)

- · Restores the W register

#### EXAMPLE 9-3: SAVING THE STATUS AND W REGISTERS IN RAM

| MOVWF | W_TEMP            | ;copy W to temp register,<br>;could be in either bank                       |

|-------|-------------------|-----------------------------------------------------------------------------|

| SWAPF | STATUS,W          | ;swap status to be saved<br>into W                                          |

| BCF   | STATUS, RPO       | ;change to bank 0 regardless<br>;of current bank                            |

| MOVWF | STATUS_TEMP       | ;save status to bank 0<br>;register                                         |

| :     |                   |                                                                             |

| :     | (ISR)             |                                                                             |

| :     |                   |                                                                             |

| SWAPF | STATUS_TEMP,<br>W | ;swap STATUS_TEMP register<br>;into W, sets bank to origi-<br>nal<br>;state |

| MOVWF | STATUS            | ;move W into STATUS register                                                |

| SWAPF | W_TEMP,F          | ;swap W_TEMP                                                                |

| SWAPF | W_TEMP,W          | ;swap W_TEMP into W                                                         |

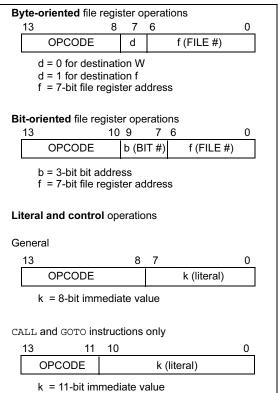

## **10.0 INSTRUCTION SET SUMMARY**

Each PIC16C62X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16C62X instruction set summary in Table 10-2 lists **byte-oriented**, **bitoriented**, and **literal and control** operations. Table 10-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 10-1: OPCODE FIELD DESCRIPTIONS

|               | DESCRIPTIONS                                                                                                                                                                   |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field         | Description                                                                                                                                                                    |

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| х             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLAT<br>H    | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| то            | Time-out bit                                                                                                                                                                   |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified regis-<br>ter file location                                                                                                 |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| < >           | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

|               |                                                                                                                                                                                |

The instruction set is highly orthogonal and is grouped into three basic categories:

- · Byte-oriented operations

- **Bit-oriented** operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 10-1 lists the instructions recognized by the MPASM  $^{\rm TM}$  assembler.

Figure 10-1 shows the three general formats that the instructions can have.

| Note: | To maintain upward compatibility with                 |

|-------|-------------------------------------------------------|

|       | future PICmicro <sup>®</sup> products, do not use the |

|       | OPTION and TRIS instructions.                         |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

## FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

| TABLE 10-2. FICTOCO2A INSTRUCTION SET | TABLE 10-2: | PIC16C62X INSTRUCTION SET |

|---------------------------------------|-------------|---------------------------|

|---------------------------------------|-------------|---------------------------|

| Mnemonic, |          | Description                  | Cycles | 14-Bit Opcode |      |      |      | Status   | Notes |

|-----------|----------|------------------------------|--------|---------------|------|------|------|----------|-------|

| Operands  |          |                              |        | MSb           | )    |      | LSb  | Affected |       |

| BYTE-ORI  | ENTED I  | FILE REGISTER OPERATIONS     |        |               |      |      |      |          |       |

| ADDWF     | f, d     | Add W and f                  | 1      | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |

| ANDWF     | f, d     | AND W with f                 | 1      | 00            | 0101 | dfff | ffff | Z        | 1,2   |

| CLRF      | f        | Clear f                      | 1      | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW      | -        | Clear W                      | 1      | 00            | 0001 | 0000 | 0011 | Z        |       |

| COMF      | f, d     | Complement f                 | 1      | 00            | 1001 | dfff | ffff | Z        | 1,2   |

| DECF      | f, d     | Decrement f                  | 1      | 00            | 0011 | dfff | ffff | Z        | 1,2   |

| DECFSZ    | f, d     | Decrement f, Skip if 0       | 1(2)   | 00            | 1011 | dfff | ffff |          | 1,2,3 |

| INCF      | f, d     | Increment f                  | 1      | 00            | 1010 | dfff | ffff | Z        | 1,2   |

| INCFSZ    | f, d     | Increment f, Skip if 0       | 1(2)   | 00            | 1111 | dfff | ffff |          | 1,2,3 |

| IORWF     | f, d     | Inclusive OR W with f        | 1      | 00            | 0100 | dfff | ffff | Z        | 1,2   |

| MOVF      | f, d     | Move f                       | 1      | 00            | 1000 | dfff | ffff | Z        | 1,2   |

| MOVWF     | f        | Move W to f                  | 1      | 00            | 0000 | lfff | ffff |          |       |

| NOP       | -        | No Operation                 | 1      | 00            | 0000 | 0xx0 | 0000 |          |       |

| RLF       | f, d     | Rotate Left f through Carry  | 1      | 00            | 1101 | dfff | ffff | С        | 1,2   |

| RRF       | f, d     | Rotate Right f through Carry | 1      | 00            | 1100 | dfff | ffff | С        | 1,2   |

| SUBWF     | f, d     | Subtract W from f            | 1      | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |

| SWAPF     | f, d     | Swap nibbles in f            | 1      | 00            | 1110 | dfff | ffff |          | 1,2   |

| XORWF     | f, d     | Exclusive OR W with f        | 1      | 00            | 0110 | dfff | ffff | Z        | 1,2   |

| BIT-ORIEN | NTED FIL | E REGISTER OPERATIONS        |        |               |      |      |      |          |       |

| BCF       | f, b     | Bit Clear f                  | 1      | 01            | 00bb | bfff | ffff |          | 1,2   |

| BSF       | f, b     | Bit Set f                    | 1      | 01            | 01bb | bfff | ffff |          | 1,2   |

| BTFSC     | f, b     | Bit Test f, Skip if Clear    | 1 (2)  | 01            | 10bb | bfff | ffff |          | 3     |

| BTFSS     | f, b     | Bit Test f, Skip if Set      | 1 (2)  | 01            | 11bb | bfff | ffff |          | 3     |

| LITERAL / | AND COI  | NTROL OPERATIONS             |        |               |      |      |      |          |       |

| ADDLW     | k        | Add literal and W            | 1      | 11            | 111x | kkkk | kkkk | C,DC,Z   |       |

| ANDLW     | k        | AND literal with W           | 1      | 11            | 1001 | kkkk | kkkk | Z        |       |

| CALL      | k        | Call subroutine              | 2      | 10            | 0kkk | kkkk | kkkk |          |       |

| CLRWDT    | -        | Clear Watchdog Timer         | 1      | 00            | 0000 | 0110 | 0100 | TO,PD    |       |

| GOTO      | k        | Go to address                | 2      | 10            | 1kkk | kkkk | kkkk |          |       |

| IORLW     | k        | Inclusive OR literal with W  | 1      | 11            | 1000 | kkkk | kkkk | Z        |       |

| MOVLW     | k        | Move literal to W            | 1      | 11            | 00xx | kkkk | kkkk |          |       |

| RETFIE    | -        | Return from interrupt        | 2      | 00            | 0000 | 0000 | 1001 |          |       |

| RETLW     | k        | Return with literal in W     | 2      | 11            | 01xx | kkkk | kkkk |          |       |

| RETURN    | -        | Return from Subroutine       | 2      | 00            | 0000 | 0000 | 1000 |          |       |

| SLEEP     | -        | Go into Standby mode         | 1      | 00            | 0000 | 0110 | 0011 | TO,PD    |       |

| SUBLW     | k        | Subtract W from literal      | 1      | 11            | 110x | kkkk | kkkk | C,DC,Z   |       |

| XORLW     | k        | Exclusive OR literal with W  | 1      | 11            | 1010 | kkkk | kkkk | Z        |       |

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**2:** If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| MOVF                    | Move f                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:                 | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| Operands:               | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| Operation:              | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| Status Affected:        | Z                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Encoding:               | 00 1000 dfff ffff                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Description:            | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |  |  |  |  |  |  |  |  |

| Words:                  | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Cycles:                 | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Example                 | MOVF FSR, <b>0</b>                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| MOVANE                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| MOVWF                   | Move W to f                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| Syntax:                 | [ <i>label</i> ] MOVWF f<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| Operands:<br>Operation: | $0 \le 1 \le 127$<br>(W) $\rightarrow$ (f)                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| Status Affected:        | None $(1)$                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| Encoding:               | 00 0000 1fff ffff                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Description:            | Move data from W register to reg-<br>ister 'f'.                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Words:                  | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Cycles:                 | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Example                 | MOVWF OPTION                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

|                         | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F<br>W = 0x4F                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|                         | W = 0x4F                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| NOP              | No Operation      |     |  |  |  |  |  |

|------------------|-------------------|-----|--|--|--|--|--|

| Syntax:          | [ label ]         | NOP |  |  |  |  |  |

| Operands:        | None              |     |  |  |  |  |  |

| Operation:       | No operation      |     |  |  |  |  |  |

| Status Affected: | None              |     |  |  |  |  |  |

| Encoding:        | 00 0000 0xx0 0000 |     |  |  |  |  |  |

| Description:     | No operation.     |     |  |  |  |  |  |

| Words:           | 1                 |     |  |  |  |  |  |

| Cycles:          | 1                 |     |  |  |  |  |  |

| Example          | NOP               |     |  |  |  |  |  |

| [ lahel ]                                                                                                                                                                            |                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| [label] OPTION                                                                                                                                                                       |                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| None                                                                                                                                                                                 |                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| $(W) \rightarrow OPTION$                                                                                                                                                             |                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| None                                                                                                                                                                                 |                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 00                                                                                                                                                                                   | 0000                                                                                                                                                                                   | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |