Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c622-20e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C62X uses a Harvard architecture, in which, program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture, where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C620(A) and PIC16CR620A address 512 x 14 on-chip program memory. The PIC16C621(A) addresses 1K x 14 program memory. The PIC16C622(A) addresses 2K x 14 program memory. All program memory is internal.

The PIC16C62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16C62X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

#### **OPTION Register** 4.2.2.2

The OPTION register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |

|-------|-------------------------------------------|

|       | TMR0, assign the prescaler to the WDT     |

|       | (PSA = 1).                                |

|         | R/W-1                                                                                                            | R/W-1                          | R/W-1                      | R/W-1                        | R/W-1         | R/W-1 | R/W-1 | R/W-1 |

|---------|------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------|------------------------------|---------------|-------|-------|-------|

|         | RBPU                                                                                                             | INTEDG                         | TOCS                       | TOSE                         | PSA           | PS2   | PS1   | PS0   |

|         | bit 7                                                                                                            |                                |                            |                              |               | •     |       | bit 0 |

| bit 7   | RBPU: PO                                                                                                         | RTB Pull-u                     | p Enable bi                | it                           |               |       |       |       |

|         |                                                                                                                  | 3 pull-ups ai<br>3 pull-ups ai |                            | y individual                 | port latch va | alues |       |       |

| bit 6   | INTEDG: I                                                                                                        | nterrupt Edg                   | e Select bit               | -                            |               |       |       |       |

|         |                                                                                                                  |                                | edge of RB0<br>edge of RB0 |                              |               |       |       |       |

| bit 5   | TOCS: TMI                                                                                                        | R0 Clock Sc                    | ource Select               | bit                          |               |       |       |       |

|         |                                                                                                                  | ion on RA4/<br>Il instruction  | T0CKI pin<br>cycle clock   | (CLKOUT)                     |               |       |       |       |

| bit 4   | TOSE: TM                                                                                                         | R0 Source E                    | Edge Select                | bit                          |               |       |       |       |

|         |                                                                                                                  |                                |                            | ition on RA4<br>ition on RA4 |               |       |       |       |

| bit 3   | <b>PSA</b> : Prescaler Assignment bit                                                                            |                                |                            |                              |               |       |       |       |

|         | <ul> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul> |                                |                            |                              |               |       |       |       |

| bit 2-0 | PS<2:0>: Prescaler Rate Select bits                                                                              |                                |                            |                              |               |       |       |       |

|         | E                                                                                                                | Bit Value T                    | MR0 Rate                   | WDT Rate                     |               |       |       |       |

|         | -                                                                                                                | 000<br>001                     | 1:2<br>1:4                 | 1:1<br>1:2                   |               |       |       |       |

|         |                                                                                                                  | 010<br>011                     | 1 : 8<br>1 : 16            | 1:4<br>1:8                   |               |       |       |       |

|         |                                                                                                                  | 100                            | 1:32                       | 1:16                         |               |       |       |       |

|         |                                                                                                                  | 101                            | 1:64                       | 1:32                         |               |       |       |       |

|         |                                                                                                                  | 110                            | 1:128                      | 1:64                         |               |       |       |       |

|         | 111 1 : 256 1 : 128                                                                                              |                                |                            |                              |               |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 4.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

| E PE<br>Global Internables all un<br>isables all in<br>Peripheral<br>nables all p<br>TMR0 Ove<br>nables the T<br>isables the | N-0     R/W-0       EIE     TOIE       rrupt Enable bit       n-masked interrunts       Interrupts       Interrupt Enable       n-masked periphoreripheral interrupt       erflow Interrupt Entrupt       TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | R/W-0<br>RBIE                                                                                                                                                        | R/W-0<br>T0IF                                                                                                                                                                                                                                | R/W-0<br>INTF                                                                                                                                                                                                            | R/W-x<br>RBIF<br>bit 0                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          | bit 0                                                                                                                                                                                                                                                                                      |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| sables all in<br>Peripheral<br>nables all un<br>sables all p<br>TMR0 Ove<br>nables the T<br>isables the                      | nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                                                          | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the                                                       | n-masked periph<br>peripheral interru<br>rflow Interrupt Er<br>TMR0 interrupt                                                                                                                                            | neral interrupt<br>pts                                                                                                  | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| sables all p<br>TMR0 Ove<br>nables the<br>sables the                                                                         | peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                                                                                                              | pts                                                                                                                     | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| TMR0 Ove<br>nables the<br>sables the                                                                                         | rflow Interrupt Er<br>TMR0 interrupt                                                                                                                                                                                     |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| nables the<br>isables the                                                                                                    | TMR0 interrupt                                                                                                                                                                                                           | nable bit                                                                                                               |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| sables the                                                                                                                   |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | I MRU interrupt                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | External Interrupt                                                                                                                                                                                                       |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | RB0/INT externa<br>RB0/INT externa                                                                                                                                                                                       |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | hange Interrupt E                                                                                                                                                                                                        |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | RB port change i                                                                                                                                                                                                         |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | RB port change                                                                                                                                                                                                           | •                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| TMR0 Ove                                                                                                                     | rflow Interrupt Fl                                                                                                                                                                                                       | ag bit                                                                                                                  |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| MR0 registe                                                                                                                  | er has overflowed                                                                                                                                                                                                        | d (must be cle                                                                                                          | eared in soft                                                                                                                                                        | ware)                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| MR0 registe                                                                                                                  | er did not overflov                                                                                                                                                                                                      | W                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| RB0/INT E                                                                                                                    | xternal Interrupt                                                                                                                                                                                                        | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      | red in softwa                                                                                                                                                                                                                                | are)                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                            |

| RB Port Cl                                                                                                                   | hange Interrupt F                                                                                                                                                                                                        | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| 'hen at leas                                                                                                                 |                                                                                                                                                                                                                          | •                                                                                                                       | -                                                                                                                                                                    | (must be cle                                                                                                                                                                                                                                 | ared in softw                                                                                                                                                                                                            | ware)                                                                                                                                                                                                                                                                                      |

|                                                                                                                              | ne RB0/INT<br>ne RB0/INT<br>RB Port C<br>hen at leas                                                                                                                                                                     | ne RB0/INT external interrune<br>RB0/INT external interrun<br>RB Port Change Interrupt I<br>hen at least one of the RB< | ne RB0/INT external interrupt did not occ<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins cha<br>one of the RB<7:4> pins have changed s | ne RB0/INT external interrupt occurred (must be clea<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state<br>one of the RB<7:4> pins have changed state | ne RB0/INT external interrupt occurred (must be cleared in softwa<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cle | ne RB0/INT external interrupt occurred (must be cleared in software)<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cleared in softwore)<br>one of the RB<7:4> pins have changed state |

| REGISTER 4-3: | INTCON REGISTER (ADDRESS 0BH OR 8BH) |

|---------------|--------------------------------------|

|---------------|--------------------------------------|

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 4.2.2.4 PIE1 Register

This register contains the individual enable bit for the comparator interrupt.

| <b>REGISTER 4-4:</b> | PIE1 REGISTER (ADDRESS 8CH)                                                                                                                           |       |     |     |     |     |     |       |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|-----|-----|-----|-------|

|                      | U-0                                                                                                                                                   | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|                      |                                                                                                                                                       | CMIE  | _   |     |     | —   | _   | —     |

|                      | bit 7 bit 0                                                                                                                                           |       |     |     |     |     |     | bit 0 |

| bit 7                | Unimplemented: Read as '0'                                                                                                                            |       |     |     |     |     |     |       |

| bit 6                | <b>CMIE</b> : Comparator Interrupt Enable bit<br>1 = Enables the Comparator interrupt<br>0 = Disables the Comparator interrupt                        |       |     |     |     |     |     |       |

| bit 5-0              | Unimplemented: Read as '0'                                                                                                                            |       |     |     |     |     |     |       |

|                      | Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0- n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unitable bit |       |     |     |     |     |     |       |

#### 4.2.2.5 PIR1 Register

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of |  |  |  |

|-------|--------------------------------------------------------------------------------------------|--|--|--|

|       | its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User               |  |  |  |

|       | software should ensure the appropriate                                                     |  |  |  |

|       | interrupt flag bits are clear prior to enabling                                            |  |  |  |

|       | an interrupt.                                                                              |  |  |  |

### REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

| ER 4-5: | PIRT REGISTER (ADDRESS UCH)          |         |         |              |              |                                    |              |        |  |

|---------|--------------------------------------|---------|---------|--------------|--------------|------------------------------------|--------------|--------|--|

|         | U-0                                  | R/W-0   | U-0     | U-0          | U-0          | U-0                                | U-0          | U-0    |  |

|         |                                      | CMIF    |         | —            | _            |                                    |              |        |  |

|         | bit 7                                |         |         |              |              |                                    |              | bit 0  |  |

|         |                                      |         |         |              |              |                                    |              |        |  |

| bit 7   | Unimplemented: Read as '0'           |         |         |              |              |                                    |              |        |  |

| bit 6   | CMIF: Comparator Interrupt Flag bit  |         |         |              |              |                                    |              |        |  |

|         | 1 = Comparator input has changed     |         |         |              |              |                                    |              |        |  |

|         | 0 = Comparator input has not changed |         |         |              |              |                                    |              |        |  |

| bit 5-0 | Unimplemented: Read as '0'           |         |         |              |              |                                    |              |        |  |

|         |                                      |         |         |              |              |                                    |              |        |  |

|         | Legend:                              |         |         |              |              |                                    |              |        |  |

|         | R = Readab                           | ole bit | W = W   | /ritable bit | U = Unim     | U = Unimplemented bit, read as '0' |              |        |  |

|         | - n = Value                          | at POR  | '1' = B | it is set    | '0' = Bit is | s cleared                          | x = Bit is u | nknown |  |

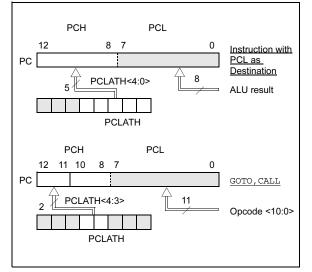

## 4.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any RESET, the PC is cleared. Figure 4-8 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-8: LOADING OF PC IN DIFFERENT SITUATIONS

## 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

### 4.3.2 STACK

The PIC16C62X family has an 8-level deep x 13-bit wide hardware stack (Figure 4-2 and Figure 4-3). The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no STATUS bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to WDT.)

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

|          |              | ,                                             |

|----------|--------------|-----------------------------------------------|

| 1.BCF    | STATUS, RPO  | ;Skip if already in<br>;Bank 0                |

| 2.CLRWDT |              | ;Clear WDT                                    |

| 3.CLRF   | TMR0         | ;Clear TMR0 & Prescaler                       |

| 4.BSF    | STATUS, RPO  | ;Bank 1                                       |

| 5.MOVLW  | '00101111'b; | ;These 3 lines (5, 6, 7)                      |

| 6.MOVWF  | OPTION       | ;are required only if<br>;desired PS<2:0> are |

| 7.CLRWDT |              | ;000 or 001                                   |

| 8.MOVLW  | '00101xxx'b  | ;Set Postscaler to                            |

| 9.MOVWF  | OPTION       | ;desired WDT rate                             |

| 10.BCF   | STATUS, RPO  | ;Return to Bank 0                             |

|          |              |                                               |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 6-2. This precaution must be taken even if the WDT is disabled.

## EXAMPLE 6-2:

#### CHANGING PRESCALER (WDT→TIMER0)

|        | •           | ,                                        |

|--------|-------------|------------------------------------------|

| CLRWDT |             | ;Clear WDT and                           |

|        |             | ;prescaler                               |

| BSF    | STATUS, RPO |                                          |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new<br>;prescale value and |

|        |             | ;clock source                            |

| MOVWF  | OPTION REG  |                                          |

| BCF    | STATUS, RPO |                                          |

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6       | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|----------|-------------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 r | nodule regi | ster  |        |        |        |        |        | XXXX XXXX       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE      | PEIE        | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | RBPU     | INTEDG      | TOCS  | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _        |             | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

**Note:** Shaded bits are not used by TMR0 module.

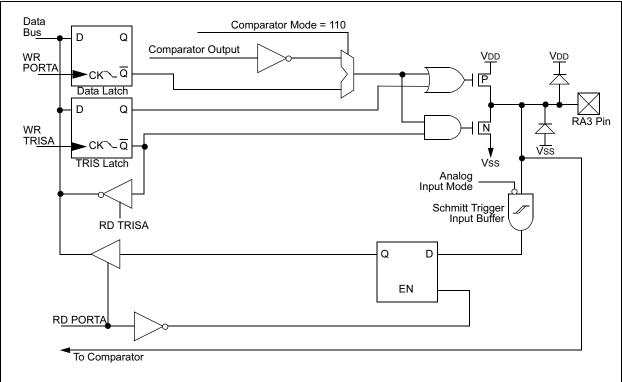

## 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-Chip Voltage Reference (Section 8.0) can also be an input to the comparators.

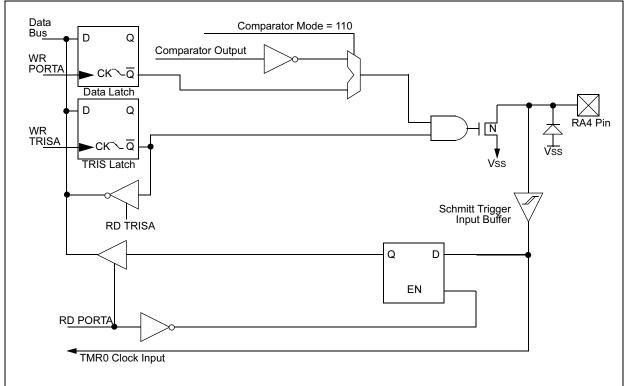

The CMCON register, shown in Register 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-1.

### REGISTER 7-1: CMCON REGISTER (ADDRESS 1Fh)

|         |                   |                                 | <b>(</b> | ,   |       |       |       |       |

|---------|-------------------|---------------------------------|----------|-----|-------|-------|-------|-------|

|         | R-0               | R-0                             | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|         | C2OUT             | C10UT                           | —        | —   | CIS   | CM2   | CM1   | CM0   |

|         | bit 7             |                                 |          |     |       |       |       | bit 0 |

|         |                   |                                 |          |     |       |       |       |       |

| bit 7   | <b>C2OUT</b> : Co | omparator 2                     | output   |     |       |       |       |       |

|         | 1 = C2 VIN        | + > C2 VIN-                     |          |     |       |       |       |       |

|         | 0 = C2 VIN        | + < C2 VIN-                     |          |     |       |       |       |       |

| bit 6   | <b>C1OUT</b> : Co | omparator 1                     | output   |     |       |       |       |       |

|         | 1 = C1 VIN        | + > C1 VIN-                     |          |     |       |       |       |       |

|         | 0 = C1 VIN        | + < C1 VIN-                     |          |     |       |       |       |       |

| bit 5-4 | Unimplem          | ented: Read                     | d as '0' |     |       |       |       |       |

| bit 3   | CIS: Comp         | arator Input                    | Switch   |     |       |       |       |       |

|         | When CM<          | <2:0>: = 001                    | :        |     |       |       |       |       |

|         | 1 = C1 VIN-       | - connects to                   | o RA3    |     |       |       |       |       |

|         | 0 = C1 VIN        | - connects to                   | o RA0    |     |       |       |       |       |

|         | When CM<          | <2:0> = 010:                    |          |     |       |       |       |       |

|         |                   | <ul> <li>connects to</li> </ul> |          |     |       |       |       |       |

|         |                   | I- connects t                   |          |     |       |       |       |       |

|         |                   | - connects to                   |          |     |       |       |       |       |

|         | C2 VIN            | I- connects t                   | 0 RA1    |     |       |       |       |       |

| bit 2-0 | CM<2:0>:          | Comparator                      | mode.    |     |       |       |       |       |

|         |                   |                                 |          |     |       |       |       |       |

|         | Legend:           |                                 |          |     |       |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

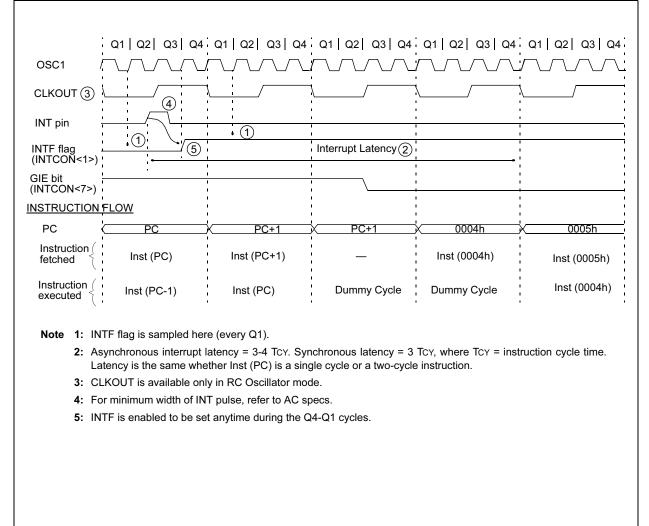

#### 9.5.1 RB0/INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered, either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP and Figure 9-18 for timing of wakeup from SLEEP through RB0/INT interrupt.

#### 9.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 6.0.

#### 9.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

| Note: | If a change on the I/O pin should occur   |

|-------|-------------------------------------------|

|       | when the read operation is being executed |

|       | (start of the Q2 cycle), then the RBIF    |

|       | interrupt flag may not get set.           |

#### 9.5.4 COMPARATOR INTERRUPT

See Section 7.6 for complete description of comparator interrupts.

#### FIGURE 9-16: INT PIN INTERRUPT TIMING

#### 9.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs with no external circuitry drawing current from the I/O pin and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated      |

|-------|------------------------------------------------|

|       | by a WDT time-out does not drive MCLR pin low. |

|       |                                                |

#### 9.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device RESET. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. PD bit, which is set on power-up, is cleared when SLEEP is invoked. TO bit is cleared if WDT wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction after the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

**Note:** If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from SLEEP. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes up from SLEEP, regardless of the source of wake-up.

| Q1 Q2 Q                  | 3 Q4 Q1 Q2 Q3 Q4 Q | Q1                    | Q1 Q2 Q3 Q4      | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 0    | Q1 Q2 Q3 Q4 |

|--------------------------|--------------------|-----------------------|------------------|-------------|------------------|-------------|

| OSC1 //////              |                    |                       |                  |             |                  |             |

| CLKOUT(4)                |                    | Tost(2)               | <u> </u>         |             | \ <u>`</u>       |             |

| INT pin                  | 1 I                |                       | 1<br>1           |             | 1                |             |

| NTF flag                 |                    |                       | Interrupt Latend | SV.         |                  |             |

| INTCON<1>)               |                    | <del>≉</del>          | (Note 2)         | ,           |                  |             |

| GIE bit<br>INTCON<7>)    |                    | Processor in<br>SLEEP | 1                |             |                  |             |

| INSTRUCTION FLOW         |                    |                       | 1<br>1<br>1      |             | 1                |             |

| PC X PC                  | <u>Υ PC+1 Χ</u>    | PC+2                  | X PC+2           | PC + 2      | <u>χ 0004h χ</u> | 0005h       |

| Instruction { Inst(PC) = | SLEEP Inst(PC + 1) |                       | Inst(PC + 2)     |             | Inst(0004h)      | Inst(0005h) |

| Instruction Inst(PC      | - 1) SLEEP         |                       | Inst(PC + 1)     | Dummy cycle | Dummy cycle      | Inst(0004h) |

#### FIGURE 9-18: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**3:** GIE = '1' assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these Osc modes, but shown here for timing reference.

# PIC16C62X

| RETFIE           | Return from Interrupt                                                                                                                                                                                                |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                       |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$ ,<br>1 $\rightarrow GIE$                                                                                                                                                                        |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                    |  |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top of Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two-cycle<br>instruction. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                               |  |  |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                               |  |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                                                                  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                                       |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                      |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                                                         |

| Description:     | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction.                                       |

| Words:           | 1                                                                                                                                                                                                                         |

| Cycles:          | 2                                                                                                                                                                                                                         |

| Example          | CALL TABLE;W contains table                                                                                                                                                                                               |

| TABLE            | ;offset value<br>;W now has table value<br>ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>RETLW k2 ;<br>RETLW kn ; End of table<br>Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8 |

| RETURN           | Return from Subroutine                                                                                                                                                                                                    |

| Syntax:          | [label] RETURN                                                                                                                                                                                                            |

| Operands:        | None                                                                                                                                                                                                                      |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                      |

| Encoding:        | 00 0000 0000 1000                                                                                                                                                                                                         |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction.                                                                |

| Words:           | 1                                                                                                                                                                                                                         |

| Cycles:          | 2                                                                                                                                                                                                                         |