Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

|                            |                                                                             |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            |                                                                             |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c622a-04e-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

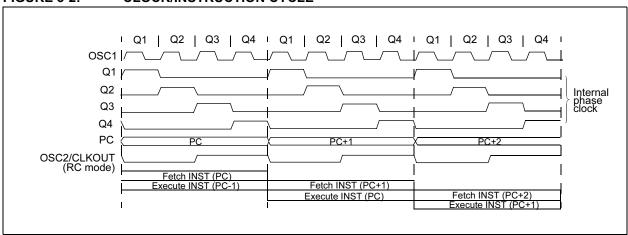

# 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

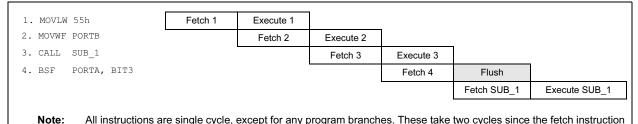

### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### **EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW**

is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

### 4.0 MEMORY ORGANIZATION

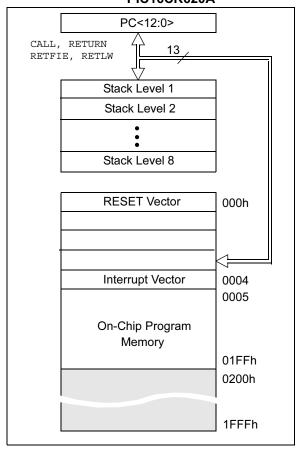

### 4.1 Program Memory Organization

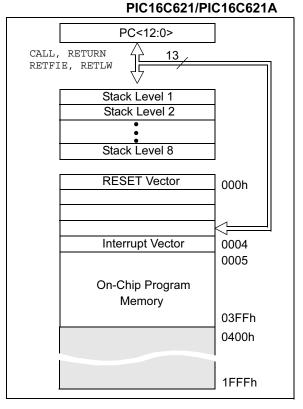

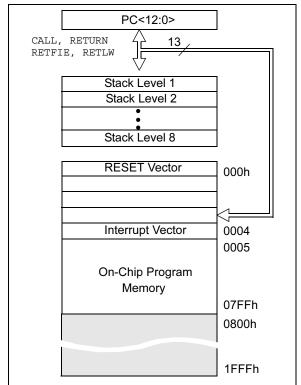

The PIC16C62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C620(A) and PIC16CR620, 1K x 14 (0000h - 03FFh) for the PIC16C621(A) and 2K x 14 (0000h - 07FFh) for the PIC16C622(A) are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16C(R)620(A)) or 1K x 14 space (PIC16C621(A)) or 2K x 14 space (PIC16C622(A)). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16C620/PIC16C620A/ PIC16CR620A

FIGURE 4-2: PROGRAM MEMORY MAP

AND STACK FOR THE

FIGURE 4-3: PROGRAM MEMORY MAP

AND STACK FOR THE

PIC16C622/PIC16C622A

FIGURE 4-4: DATA MEMORY MAP FOR THE PIC16C620/621

| File<br>Address |                                                   |                     | File<br>Address |  |  |  |  |  |  |

|-----------------|---------------------------------------------------|---------------------|-----------------|--|--|--|--|--|--|

| 00h             | INDF <sup>(1)</sup>                               | INDF <sup>(1)</sup> | 80h             |  |  |  |  |  |  |

| 01h             | TMR0                                              | OPTION              | 81h             |  |  |  |  |  |  |

| 02h             | PCL                                               | PCL                 | 82h             |  |  |  |  |  |  |

| 03h             | STATUS                                            | STATUS              | 83h             |  |  |  |  |  |  |

| 04h             | FSR                                               | FSR                 | 84h             |  |  |  |  |  |  |

| 05h             | PORTA                                             | TRISA               | 85h             |  |  |  |  |  |  |

| 06h             | PORTB                                             | TRISB               | 86h             |  |  |  |  |  |  |

| 07h             |                                                   |                     | 87h             |  |  |  |  |  |  |

| 08h             |                                                   |                     | 88h             |  |  |  |  |  |  |

| 09h             |                                                   |                     | 89h             |  |  |  |  |  |  |

| 0Ah             | PCLATH                                            | PCLATH              | 8Ah             |  |  |  |  |  |  |

| 0Bh             | INTCON                                            | INTCON              | 8Bh             |  |  |  |  |  |  |

| 0Ch             | PIR1                                              | PIE1                | 8Ch             |  |  |  |  |  |  |

| 0Dh             |                                                   |                     | 8Dh             |  |  |  |  |  |  |

| 0Eh             |                                                   | PCON                | 8Eh             |  |  |  |  |  |  |

| 0Fh             |                                                   |                     | 8Fh             |  |  |  |  |  |  |

| 10h             |                                                   |                     | 90h             |  |  |  |  |  |  |

| 11h             |                                                   |                     | 91h             |  |  |  |  |  |  |

| 12h             |                                                   |                     | 92h             |  |  |  |  |  |  |

| 13h             |                                                   |                     | 93h             |  |  |  |  |  |  |

| 14h             |                                                   |                     | 94h             |  |  |  |  |  |  |

| 15h             |                                                   |                     | 95h             |  |  |  |  |  |  |

| 16h             |                                                   |                     | 96h             |  |  |  |  |  |  |

| 17h             |                                                   |                     | 97h             |  |  |  |  |  |  |

| 18h             |                                                   |                     | 98h             |  |  |  |  |  |  |

| 19h             |                                                   |                     | 99h             |  |  |  |  |  |  |

| 1Ah             |                                                   |                     | 9Ah             |  |  |  |  |  |  |

| 1Bh             |                                                   |                     | 9Bh             |  |  |  |  |  |  |

| 1Ch             |                                                   |                     | 9Ch             |  |  |  |  |  |  |

| 1Dh             |                                                   |                     | 9Dh             |  |  |  |  |  |  |

| 1Eh             |                                                   |                     | 9Eh             |  |  |  |  |  |  |

| 1Fh             | CMCON                                             | VRCON               | 9Fh             |  |  |  |  |  |  |

| 20h             | Comercia                                          |                     | A0h             |  |  |  |  |  |  |

|                 | General<br>Purpose                                |                     |                 |  |  |  |  |  |  |

| 6Fh             | Register                                          |                     |                 |  |  |  |  |  |  |

| 70h             |                                                   |                     |                 |  |  |  |  |  |  |

| /un             |                                                   |                     |                 |  |  |  |  |  |  |

|                 |                                                   |                     |                 |  |  |  |  |  |  |

|                 |                                                   |                     | _               |  |  |  |  |  |  |

|                 |                                                   |                     |                 |  |  |  |  |  |  |

| 7Fh             | Donl: 0                                           | Don't 4             | ☐ FFh           |  |  |  |  |  |  |

|                 | Bank 0                                            | Bank 1              |                 |  |  |  |  |  |  |

| Unimp           | Unimplemented data memory locations, read as '0'. |                     |                 |  |  |  |  |  |  |

| Note 1:         |                                                   |                     |                 |  |  |  |  |  |  |

| 1               |                                                   |                     |                 |  |  |  |  |  |  |

FIGURE 4-5: DATA MEMORY MAP FOR THE PIC16C622

| File<br>Address                                   | 3                   |                     | File<br>Address |  |  |  |  |  |

|---------------------------------------------------|---------------------|---------------------|-----------------|--|--|--|--|--|

| 00h                                               | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |  |  |  |  |  |

| 01h                                               | TMR0                | OPTION              | 81h             |  |  |  |  |  |

| 02h                                               | PCL                 | PCL                 | 82h             |  |  |  |  |  |

| 03h                                               | STATUS              | STATUS              | 83h             |  |  |  |  |  |

| 04h                                               | FSR                 | FSR                 | 84h             |  |  |  |  |  |

| 05h                                               | PORTA               | TRISA               | 85h             |  |  |  |  |  |

| 06h                                               | PORTB               | TRISB               | 86h             |  |  |  |  |  |

| 07h                                               |                     |                     | 87h             |  |  |  |  |  |

| 08h                                               |                     |                     | 88h             |  |  |  |  |  |

| 09h                                               |                     |                     | 89h             |  |  |  |  |  |

| 0Ah                                               | PCLATH              | PCLATH              | 8Ah             |  |  |  |  |  |

| 0Bh                                               | INTCON              | INTCON              | 8Bh             |  |  |  |  |  |

| 0Ch                                               | PIR1                | PIE1                | 8Ch             |  |  |  |  |  |

| 0Dh                                               |                     |                     | 8Dh             |  |  |  |  |  |

| 0Eh                                               |                     | PCON                | 8Eh             |  |  |  |  |  |

| 0Fh                                               |                     |                     | 8Fh             |  |  |  |  |  |

| 10h                                               |                     |                     | 90h             |  |  |  |  |  |

| 11h                                               |                     |                     | 91h             |  |  |  |  |  |

| 12h                                               |                     |                     | 92h             |  |  |  |  |  |

| 13h                                               |                     |                     | 93h             |  |  |  |  |  |

| 14h                                               |                     |                     | 94h             |  |  |  |  |  |

| 15h                                               |                     |                     | 95h             |  |  |  |  |  |

| 16h                                               |                     |                     | 96h             |  |  |  |  |  |

| 17h                                               |                     |                     | 97h             |  |  |  |  |  |

| 18h                                               |                     |                     | 98h             |  |  |  |  |  |

| 19h                                               |                     |                     | 99h             |  |  |  |  |  |

| 1Ah                                               |                     |                     | 9Ah             |  |  |  |  |  |

| 1Bh                                               |                     |                     | 9Bh             |  |  |  |  |  |

| 1Ch                                               |                     |                     | 9Ch             |  |  |  |  |  |

| 1Dh                                               |                     |                     | 9Dh             |  |  |  |  |  |

| 1Eh                                               |                     |                     | 9Eh             |  |  |  |  |  |

| 1Fh                                               | CMCON               | VRCON               | 9Fh             |  |  |  |  |  |

| 20h                                               |                     |                     | A0h             |  |  |  |  |  |

|                                                   | General             | General             | 7 (011          |  |  |  |  |  |

|                                                   | Purpose<br>Register | Purpose<br>Register |                 |  |  |  |  |  |

|                                                   | . tog.oto.          | . tog.oto.          | BFh             |  |  |  |  |  |

|                                                   |                     |                     | C0h             |  |  |  |  |  |

|                                                   |                     |                     |                 |  |  |  |  |  |

| ſ                                                 |                     |                     | 7 /             |  |  |  |  |  |

|                                                   |                     |                     |                 |  |  |  |  |  |

| 7Fh                                               |                     |                     | FFh             |  |  |  |  |  |

| 7111                                              | Bank 0              | Bank 1              |                 |  |  |  |  |  |

|                                                   |                     |                     |                 |  |  |  |  |  |

| Unimplemented data memory locations, read as '0'. |                     |                     |                 |  |  |  |  |  |

| Note 1:                                           | Not a physical re   | egister.            |                 |  |  |  |  |  |

|                                                   |                     |                     |                 |  |  |  |  |  |

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM. The Special Function Registers can be classified into two sets (core and peripheral). The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16C62X

| Address | Name          | Bit 7               | Bit 6              | Bit 5       | Bit 4        | Bit 3        | Bit 2        | Bit 1       | Bit 0    | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|---------------|---------------------|--------------------|-------------|--------------|--------------|--------------|-------------|----------|-----------------------|------------------------------------------------|

| Bank 0  |               |                     |                    |             |              |              |              |             |          |                       |                                                |

| 00h     | INDF          | Addressin register) | g this locati      | on uses co  | ntents of FS | SR to addre  | ss data me   | mory (not a | physical | xxxx xxxx             | xxxx xxxx                                      |

| 01h     | TMR0          | Timer0 Mo           | odule's Reg        | ister       |              |              |              |             |          | xxxx xxxx             | uuuu uuuu                                      |

| 02h     | PCL           | Program C           | Counter's (F       | PC) Least S | ignificant B | yte          |              |             |          | 0000 0000             | 0000 0000                                      |

| 03h     | STATUS        | IRP <sup>(2)</sup>  | RP1 <sup>(2)</sup> | RP0         | TO           | PD           | Z            | DC          | С        | 0001 1xxx             | 000q quuu                                      |

| 04h     | FSR           | Indirect da         | ata memory         | address po  | ointer       |              |              |             |          | xxxx xxxx             | uuuu uuuu                                      |

| 05h     | PORTA         | _                   | _                  | _           | RA4          | RA3          | RA2          | RA1         | RA0      | x 0000                | u 0000                                         |

| 06h     | PORTB         | RB7                 | RB6                | RB5         | RB4          | RB3          | RB2          | RB1         | RB0      | xxxx xxxx             | uuuu uuuu                                      |

| 07h-09h | Unimplemented |                     |                    |             |              |              |              |             |          | _                     | _                                              |

| 0Ah     | PCLATH        | _                   | _                  | _           | Write buffe  | er for upper | 5 bits of pr | ogram cour  | nter     | 0 0000                | 0 0000                                         |

| 0Bh     | INTCON        | GIE                 | PEIE               | TOIE        | INTE         | RBIE         | TOIF         | INTF        | RBIF     | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1          | _                   | CMIF               | _           | _            | _            | _            | _           | _        | -0                    | -0                                             |

| 0Dh-1Eh | Unimplemented |                     |                    |             |              |              |              |             |          | _                     | _                                              |

| 1Fh     | CMCON         | C2OUT               | C10UT              | _           | _            | CIS          | CM2          | CM1         | CM0      | 00 0000               | 00 0000                                        |

| Bank 1  |               |                     |                    |             |              |              |              |             |          |                       |                                                |

| 80h     | INDF          | Addressin register) | g this locati      | on uses co  | ntents of FS | SR to addre  | ss data me   | mory (not a | physical | xxxx xxxx             | xxxx xxxx                                      |

| 81h     | OPTION        | RBPU                | INTEDG             | T0CS        | T0SE         | PSA          | PS2          | PS1         | PS0      | 1111 1111             | 1111 1111                                      |

| 82h     | PCL           | Program C           | Counter's (F       | PC) Least S | ignificant B | yte          |              |             |          | 0000 0000             | 0000 0000                                      |

| 83h     | STATUS        | IRP <sup>(2)</sup>  | RP1 <sup>(2)</sup> | RP0         | TO           | PD           | Z            | DC          | С        | 0001 1xxx             | 000q quuu                                      |

| 84h     | FSR           | Indirect da         | ata memory         | address po  | ointer       | •            | •            | •           |          | xxxx xxxx             | uuuu uuuu                                      |

| 85h     | TRISA         | _                   | _                  | _           | TRISA4       | TRISA3       | TRISA2       | TRISA1      | TRISA0   | 1 1111                | 1 1111                                         |

| 86h     | TRISB         | TRISB7              | TRISB6             | TRISB5      | TRISB4       | TRISB3       | TRISB2       | TRISB1      | TRISB0   | 1111 1111             | 1111 1111                                      |

| 87h-89h | Unimplemented |                     |                    |             |              |              |              |             |          | _                     | _                                              |

| 8Ah     | PCLATH        | _                   | _                  | _           | Write buffe  | er for upper | 5 bits of pr | ogram cour  | nter     | 0 0000                | 0 0000                                         |

| 8Bh     | INTCON        | GIE                 | PEIE               | TOIE        | INTE         | RBIE         | T0IF         | INTF        | RBIF     | 0000 000x             | 0000 000u                                      |

| 8Ch     | PIE1          | _                   | CMIE               | _           | _            | _            | _            | _           | _        | -0                    | -0                                             |

| 8Dh     | Unimplemented |                     |                    |             |              |              |              |             |          | _                     | _                                              |

| 8Eh     | PCON          | _                   | _                  | _           | _            | _            | _            | POR         | BOR      | 0x                    | uq                                             |

| 8Fh-9Eh | Unimplemented |                     |                    |             |              |              |              |             |          | _                     |                                                |

| 9Fh     | VRCON         | VREN                | VROE               | VRR         | _            | VR3          | VR2          | VR1         | VR0      | 000- 0000             | 000- 0000                                      |

Legend: — = Unimplemented locations read as '0',  ${\tt u}$  = unchanged,  ${\tt x}$  = unknown,

q = value depends on condition, shaded = unimplemented

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

<sup>2:</sup> IRP & RP1 bits are reserved; always maintain these bits clear.

### 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

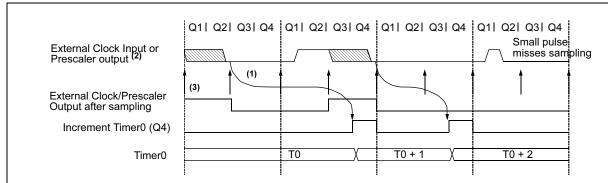

### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.2.2 TIMERO INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

FIGURE 6-5: TIMERO TIMING WITH EXTERNAL CLOCK

- Note 1: Delay from clock input change to Timer0 increment is 3Tosc to 7Tosc. (Duration of Q = Tosc).

Therefore, the error in measuring the interval between two edges on Timer0 input = ±4Tosc max.

- 2: External clock if no prescaler selected, Prescaler output otherwise.

- 3: The arrows indicate the points in time where sampling occurs.

#### 7.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be RESET by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

Note: If a change in the CMCON register (C1OUT or C2OUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<6>) interrupt flag may not get set.

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

### 7.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake up the device from SLEEP mode when enabled. While the comparator is powered-up, higher SLEEP currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering SLEEP. If the device wakes up from SLEEP, the contents of the CMCON register are not affected.

#### 7.8 Effects of a RESET

A device RESET forces the CMCON register to its RESET state. This forces the comparator module to be in the comparator RESET mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at RESET time. The comparators will be powered-down during the RESET interval.

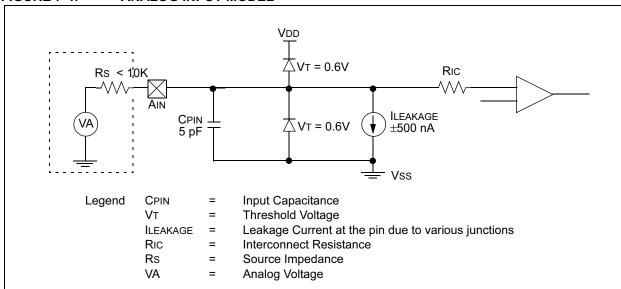

### 7.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 7-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latchup may occur. A impedance maximum source of 10 k $\Omega$ recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

FIGURE 7-4: ANALOG INPUT MODEL

# **PIC16C62X**

TABLE 7-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on POR | Value on<br>All Other<br>RESETS |

|---------|--------|-------|-------|-------|--------|--------|--------|--------|--------|--------------|---------------------------------|

| 1Fh     | CMCON  | C2OUT | C1OUT | _     |        | CIS    | CM2    | CM1    | CM0    | 00 0000      | 00 0000                         |

| 9Fh     | VRCON  | VREN  | VROE  | VRR   | 1      | VR3    | VR2    | VR1    | VR0    | 000- 0000    | 000- 0000                       |

| 0Bh     | INTCON | GIE   | PEIE  | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x    | 0000 000u                       |

| 0Ch     | PIR1   | _     | CMIF  | _     | _      | _      |        | _      | _      | -0           | -0                              |

| 8Ch     | PIE1   | 1     | CMIE  | _     |        | _      |        |        |        | -0           | -0                              |

| 85h     | TRISA  | 1     |       | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111       | 1 1111                          |

Legend: x = unknown, u = unchanged, - = unimplemented, read as "0"

### EXAMPLE 8-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; | 4 Inputs Muxed |

|-------|-------------|---|----------------|

| MOVWF | CMCON       | ; | to 2 comps.    |

| BSF   | STATUS, RPO | ; | go to Bank 1   |

| MOVLW | 0x0F        | ; | RA3-RA0 are    |

| MOVWF | TRISA       | ; | inputs         |

| MOVLW | 0xA6        | ; | enable VREF    |

| MOVWF | VRCON       | ; | low range      |

|       |             | ; | set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; | go to Bank 0   |

| CALL  | DELAY10     | ; | 10μs delay     |

### 8.2 Voltage Reference Accuracy/Error

The full range of Vss to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 8-1) keep VREF from approaching Vss or VDD. The voltage reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the voltage reference can be found in Table 12-2.

### 8.3 Operation During SLEEP

When the device wakes up from SLEEP through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the voltage reference should be disabled.

#### 8.4 Effects of a RESET

A device RESET disables the voltage reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

#### 8.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the voltage reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

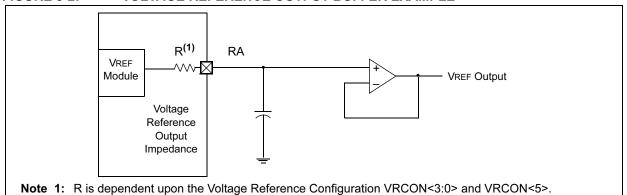

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the voltage reference output for external connections to VREF. Figure 8-2 shows an example buffering technique.

#### FIGURE 8-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

TABLE 8-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C10UT | _     | _      | CIS    | CM2    | CM1    | CM0    | 00 0000         | 00 0000                         |

| 85h     | TRISA | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Note: - = Unimplemented, read as "0"

# 9.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16C62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

#### These are:

- OSC selection

- 2. RESET

Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-Circuit Serial Programming™

The PIC16C62X devices have a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 9.4.5 TIME-OUT SEQUENCE

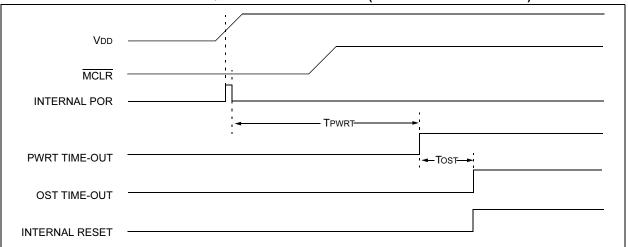

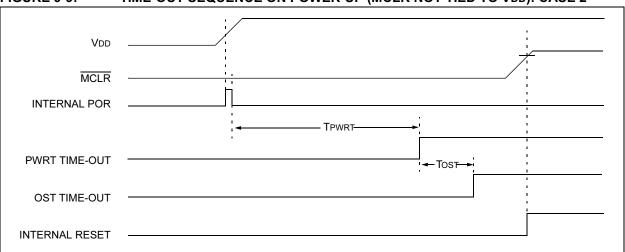

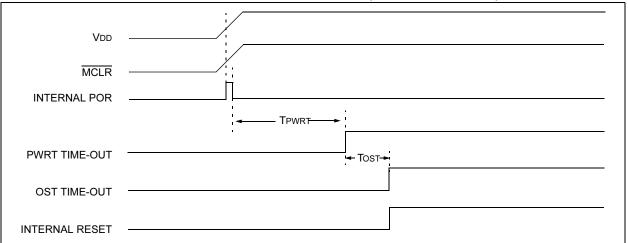

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and PWRTE bit status. For example, in RC mode with PWRTE bit erased (PWRT disabled), there will be no time-out at all. Figure 9-8, Figure 9-9 and Figure 9-10 depict time-out sequences.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then bringing MCLR high will begin execution immediately (see Figure 9-9). This is useful for testing purposes or to synchronize more than one PIC16C62X device operating in parallel.

Table 9-4 shows the RESET conditions for some special registers, while Table 9-5 shows the RESET conditions for all the registers.

#### 9.4.6 POWER CONTROL (PCON)/ STATUS REGISTER

The power control/STATUS register, PCON (address 8Eh), has two bits.

Bit0 is  $\overline{BOR}$  (Brown-out).  $\overline{BOR}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if  $\overline{BOR}$  = 0, indicating that a brown-out has occurred. The  $\overline{BOR}$  STATUS bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is  $\overline{\mathsf{POR}}$  (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent RESET, if  $\overline{\mathsf{POR}}$  is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

TABLE 9-1: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Powe              | er-up     | Brown-out Reset   | Wake-up<br>from SLEEP |  |

|--------------------------|-------------------|-----------|-------------------|-----------------------|--|

| Oscillator Configuration | PWRTE = 0         | PWRTE = 1 | Brown-out Neset   |                       |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc             |  |

| RC                       | 72 ms             | _         | 72 ms             | _                     |  |

TABLE 9-2: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD |                                    |  |  |  |

|-----|-----|----|----|------------------------------------|--|--|--|

| 0   | X   | 1  | 1  | Power-on Reset                     |  |  |  |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR          |  |  |  |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR          |  |  |  |

| 1   | 0   | Х  | Х  | Brown-out Reset                    |  |  |  |

| 1   | 1   | 0  | u  | WDT Reset                          |  |  |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                        |  |  |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation |  |  |  |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP            |  |  |  |

Legend: u = unchanged, x = unknown

TABLE 9-3: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 83h     | STATUS |       |       |       | TO    | PD    |       |       |       | 0001 1xxx             | 000q quuu                                      |

| 8Eh     | PCON   | _     |       | _     | _     |       | _     | POR   | BOR   | 0x                    | uq                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

FIGURE 9-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 9-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

# **PIC16C62X**

| BCF              | Bit Clear                             | f          |             |      |  |  |  |

|------------------|---------------------------------------|------------|-------------|------|--|--|--|

| Syntax:          | [ label ] BCF f,b                     |            |             |      |  |  |  |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$     |            |             |      |  |  |  |

| Operation:       | $0 \rightarrow (f < b)$               | >)         |             |      |  |  |  |

| Status Affected: | None                                  |            |             |      |  |  |  |

| Encoding:        | 01                                    | 00bb       | bfff        | ffff |  |  |  |

| Description:     | Bit 'b' in r                          | egister 'f | ' is cleare | ed.  |  |  |  |

| Words:           | 1                                     |            |             |      |  |  |  |

| Cycles:          | 1                                     |            |             |      |  |  |  |

| Example          | BCF                                   | FLAG_F     | REG, 7      |      |  |  |  |

|                  | Before Instruction<br>FLAG_REG = 0xC7 |            |             |      |  |  |  |

|                  | After Instruction                     |            |             |      |  |  |  |

|                  |                                       | FLAG_RE    | EG = 0x47   |      |  |  |  |

| BSF              | Bit Set f                                              |                                   |           |      |  |  |  |  |

|------------------|--------------------------------------------------------|-----------------------------------|-----------|------|--|--|--|--|

| Syntax:          | [ label ] B                                            | [ label ] BSF f,b                 |           |      |  |  |  |  |

| Operands:        | $0 \le f \le 12$ $0 \le b \le 7$                       | $0 \le f \le 127$ $0 \le b \le 7$ |           |      |  |  |  |  |

| Operation:       | 1 → (f <b< td=""><td>&gt;)</td><td></td><td></td></b<> | >)                                |           |      |  |  |  |  |

| Status Affected: | None                                                   |                                   |           |      |  |  |  |  |

| Encoding:        | 01                                                     | 01 01bb bfff                      |           | ffff |  |  |  |  |

| Description:     | Bit 'b' in r                                           | egister 'f                        | ' is set. |      |  |  |  |  |

| Words:           | 1                                                      |                                   |           |      |  |  |  |  |

| Cycles:          | 1                                                      |                                   |           |      |  |  |  |  |

| Example          | BSF                                                    | FLAG_F                            | REG, 7    |      |  |  |  |  |

|                  | Before Instruction<br>FLAG_REG = 0x0A                  |                                   |           |      |  |  |  |  |

|                  | After Inst                                             | ruction                           |           |      |  |  |  |  |

|                  |                                                        | FLAG RE                           | EG = 0x8A | ۸    |  |  |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Encoding:        | 01 10bb bfff ffff                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0', then the next instruction is skipped.  If bit 'b' is '0', then the next instruction fetched during the current instruction execution is discarded, and a NOP is executed instead, making this a two-cycle instruction. |  |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Example          | HERE BTFSC FLAG,1 FALSE GOTO PROCESS_CO TRUE • DE •                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

|                  | PC = address HERE                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|                  | After Instruction  if FLAG<1> = 0,  PC = address TRUE  if FLAG<1>=1,  PC = address FALSE                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

# **PIC16C62X**

NOTES:

#### 11.0 DEVELOPMENT SUPPORT

The PICmicro<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- · Integrated Development Environment

- MPLAB® IDE Software

- · Assemblers/Compilers/Linkers

- MPASM™ Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB C30 C Compiler

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- MPLAB dsPIC30 Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- · In-Circuit Debugger

- MPLAB ICD 2

- · Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART® Plus Development Programmer

- · Low Cost Demonstration Boards

- PICDEM™ 1 Demonstration Board

- PICDEM.net™ Demonstration Board

- PICDEM 2 Plus Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 4 Demonstration Board

- PICDEM 17 Demonstration Board

- PICDEM 18R Demonstration Board

- PICDEM LIN Demonstration Board

- PICDEM USB Demonstration Board

- Evaluation Kits

- KEELOQ®

- PICDEM MSC

- microID®

- CAN

- PowerSmart®

- Analog

### 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows® based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- · A full-featured editor with color coded context

- · A multiple project manager

- Customizable data windows with direct edit of contents

- · High level source code debugging

- · Mouse over variable inspection

- · Extensive on-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PICmicro emulator and simulator tools (automatically updates all project information)

- · Debug using:

- source files (assembly or C)

- absolute listing file (mixed assembly and C)

- machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost effective simulators, through low cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increasing flexibility and power.

#### 11.2 MPASM Assembler

The MPASM assembler is a full-featured, universal macro assembler for all PICmicro MCUs.

The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects

- · User defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

### 11.14 PICDEM 1 PICmicro Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs.

### 11.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM "TCP/IP Lean, Web Servers for Embedded Systems," by Jeremy Bentham

### 11.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessary hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 FLASH microcontrollers.

# 11.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

### 11.18 PICDEM 4 8/14/18-Pin Demonstration Board

The PICDEM 4 can be used to demonstrate the capabilities of the 8-, 14-, and 18-pin PIC16XXXX and PIC18XXXX MCUs, including the PIC16F818/819, PIC16F87/88, PIC16F62XA and the PIC18F1320 family of microcontrollers. PICDEM 4 is intended to showcase the many features of these low pin count parts, including LIN and Motor Control using ECCP. Special provisions are made for low power operation with the supercapacitor circuit, and jumpers allow onboard hardware to be disabled to eliminate current draw in this mode. Included on the demo board are provisions for Crystal, RC or Canned Oscillator modes, a five volt regulator for use with a nine volt wall adapter or battery, DB-9 RS-232 interface, ICD connector for programming via ICSP and development with MPLAB ICD 2, 2x16 liquid crystal display, PCB footprints for H-Bridge motor driver, LIN transceiver and EEPROM. Also included are: header for expansion, eight LEDs, four potentiometers, three push buttons and a prototyping area. Included with the kit is a PIC16F627A and a PIC18F1320. Tutorial firmware is included along with the User's Guide.

#### 11.19 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board FLASH memory. A generous prototype area is available for user hardware expansion.

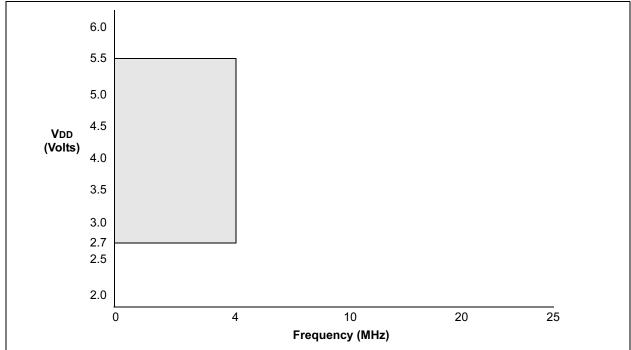

FIGURE 12-5: PIC16LC620A/LC621A/LC622A VOLTAGE-FREQUENCY GRAPH,  $-40^{\circ}\text{C} \leq \text{Ta} \leq 0^{\circ}\text{C}$

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

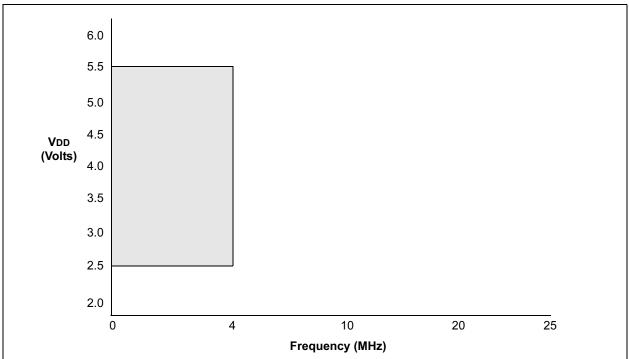

FIGURE 12-6: PIC16LC620A/LC621A/LC622A VOLTAGE-FREQUENCY GRAPH,  $0^{\circ}C \le TA \le +125^{\circ}C$

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

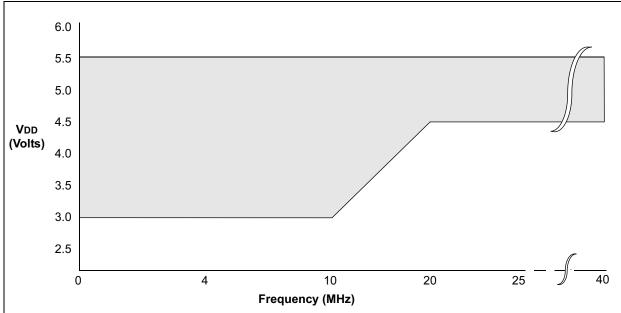

FIGURE 12-10: PIC16C620A/C621A/C622A/CR620A - 40 VOLTAGE-FREQUENCY GRAPH,  $0^{\circ}C \leq TA \leq +70^{\circ}C$

- Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

- 2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

- 3: Operation between 20 to 40 MHz requires the following:

- VDD between 4.5V. and 5.5V

- · OSC1 externally driven

- OSC2 not connected

- · HS mode

- Commercial temperatures

Devices qualified for 40 MHz operation have -40 designation (ex: PIC16C620A-40/P).

12.2 DC Characteristics: PIC16C62XA-04 (Commercial, Industrial, Extended)

PIC16C62XA-20 (Commercial, Industrial, Extended)

PIC16LC62XA-04 (Commercial, Industrial, Extended (CONT.)

| PIC16C62XA    |                 |                                                                                                                                                  |                  |                  |                     |                          |                                                                                      |  |  |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|---------------------|--------------------------|--------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Sym             | Characteristic                                                                                                                                   | Min              | Тур†             | Max                 | Units                    | Conditions                                                                           |  |  |

| D022          | Δlwdt           | WDT Current <sup>(5)</sup>                                                                                                                       | _                | 6.0              | 10<br>12            | μ <b>Α</b><br>μ <b>Α</b> | VDD = 4.0V<br>(125°C)                                                                |  |  |

| D022A<br>D023 | ΔIBOR<br>ΔICOMP | Brown-out Reset Current <sup>(5)</sup> Comparator Current for each Comparator <sup>(5)</sup>                                                     | _<br>_           | 75<br>30         | 125<br>60           | μA<br>μA                 | BOD enabled, VDD = 5.0V<br>VDD = 4.0V<br>VDD = 4.0V                                  |  |  |

| D023A         | $\Delta$ IVREF  | VREF Current <sup>(5)</sup>                                                                                                                      | _                | 80               | 135                 | μΑ                       |                                                                                      |  |  |

| D022          | ΔIWDT           | WDT Current <sup>(5)</sup>                                                                                                                       | _                | 6.0              | 10<br>12            | μ <b>Α</b><br>μ <b>Α</b> | VDD=4.0V<br>(125°C)                                                                  |  |  |

| D022A<br>D023 | ΔIBOR<br>ΔICOMP | Brown-out Reset Current <sup>(5)</sup> Comparator Current for each Comparator <sup>(5)</sup>                                                     | _                | 75<br>30         | 125<br>60           | μA<br>μA                 | BOD enabled, VDD = 5.0V<br>VDD = 4.0V                                                |  |  |

| D023A         | ΔIVREF          | VREF Current <sup>(5)</sup>                                                                                                                      | _                | 80               | 135                 | μΑ                       | VDD = 4.0V                                                                           |  |  |

| 1A            | Fosc            | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0<br>0<br>0<br>0 | —<br>—<br>—      | 200<br>4<br>4<br>20 | kHz<br>MHz<br>MHz<br>MHz | All temperatures All temperatures All temperatures All temperatures All temperatures |  |  |

| 1A            | Fosc            | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0<br>0<br>0<br>0 | _<br>_<br>_<br>_ | 200<br>4<br>4<br>20 | kHz<br>MHz<br>MHz<br>MHz | All temperatures All temperatures All temperatures All temperatures                  |  |  |

- These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

- 5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 6: Commercial temperature range only.

# 12.5 DC CHARACTERISTICS: PIC16C620A/C621A/C622A-40<sup>(7)</sup> (Commercial) PIC16CR620A-40<sup>(7)</sup> (Commercial)

| I/           | Characteristic                             | Min            |      |                 |      |                                                                                        |

|--------------|--------------------------------------------|----------------|------|-----------------|------|----------------------------------------------------------------------------------------|

| I/           | nput Low Voltage                           |                | Тур† | Max             | Unit | Conditions                                                                             |

|              |                                            |                |      |                 |      |                                                                                        |

| D030         | /O ports                                   |                |      |                 |      |                                                                                        |

| D030 w       | vith TTL buffer                            | Vss            | _    | 0.8V<br>0.15VDD | V    | VDD = 4.5V to 5.5V, otherwise                                                          |

| D031 w       | vith Schmitt Trigger input                 | Vss            |      | 0.2VDD          | V    |                                                                                        |

|              | MCLR, RA4/T0CKI, OSC1 in RC mode)          | Vss            | _    | 0.2VDD          | V    | (Note 1)                                                                               |

| D033         | OSC1 (in XT and HS)                        | Vss            | _    | 0.3VDD          | V    |                                                                                        |

| c            | OSC1 (in LP)                               | Vss            | _    | 0.6VDD - 1.0    | V    |                                                                                        |

|              | nput High Voltage<br>/O ports              |                |      |                 |      |                                                                                        |

|              | vith TTL buffer                            | 2.0V           | _    | VDD             | V    | VDD = 4.5V to 5.5V, otherwise                                                          |

|              |                                            | 0.25 VDD + 0.8 |      | VDD             |      | , , , , , , , , , , , , , , , , , , , ,                                                |

| D041 w       | vith Schmitt Trigger input                 | 0.8 VDD        |      | VDD             |      |                                                                                        |

| D042 N       | MCLR RA4/T0CKI                             | 0.8 VDD        | _    | VDD             | V    |                                                                                        |

| D043         | OSC1 (XT, HS and LP)                       | 0.7 VDD        | _    | VDD             | V    |                                                                                        |

|              | OSC1 (in RC mode)                          | 0.9 VDD        |      |                 |      | (Note 1)                                                                               |

|              | PORTB Weak Pull-up Current                 | 50             | 200  | 400             | μΑ   | VDD = 5.0V, VPIN = VSS                                                                 |

|              | nput Leakage Current <sup>(2, 3)</sup>     |                |      |                 |      |                                                                                        |

|              | O ports (except PORTA)                     |                |      | ±1.0            | μΑ   | Vss ≤ Vpin ≤ Vdd, pin at hi-impedance                                                  |

|              | PORTA                                      | _              | _    | ±0.5            | μΑ   | Vss ≤ VPIN ≤ VDD, pin at hi-impedance                                                  |

|              | RA4/T0CKI                                  | _              | _    | ±1.0            | μΑ   | Vss ≤ Vpin ≤ Vdd                                                                       |

| D063         | OSC1, MCLR                                 | _              | _    | ±5.0            | μА   | $Vss \leq VPIN \leq VDD, \ XT, \ HS \ and \ LP \ osc \ configuration$                  |

| Vol. C       | Output Low Voltage                         |                |      |                 |      |                                                                                        |

| D080 I/      | /O ports                                   | _              | _    | 0.6             | V    | IOL = $8.5 \text{ mA}$ , VDD = $4.5 \text{V}$ , $-40^{\circ}$ to $+85^{\circ}\text{C}$ |

|              |                                            | _              | _    | 0.6             | V    | IOL = 7.0 mA, VDD = 4.5V, +125°C                                                       |

| D083         | OSC2/CLKOUT (RC only)                      | _              | _    | 0.6             | V    | IOL = 1.6 mA, $VDD = 4.5V$ , $-40^{\circ}$ to $+85^{\circ}C$                           |

|              |                                            | _              | _    | 0.6             | >    | IOL = 1.2 mA, VDD = 4.5V, +125°C                                                       |

| Voh C        | Output High Voltage <sup>(3)</sup>         |                |      |                 |      |                                                                                        |

| D090 I/      | /O ports (except RA4)                      | VDD-0.7        | _    | _               | V    | IOH = $-3.0$ mA, VDD = $4.5$ V, $-40$ ° to $+85$ °C                                    |

|              |                                            | VDD-0.7        | _    | _               | V    | IOH = -2.5 mA, VDD = 4.5V, +125°C                                                      |

| D092 C       | OSC2/CLKOUT (RC only)                      | VDD-0.7        | _    | _               | V    | IOH = $-1.3$ mA, VDD = $4.5$ V, $-40$ ° to $+85$ °C                                    |

|              |                                            | VDD-0.7        | _    | _               | V    | IOH = -1.0 mA, VDD = 4.5V, +125°C                                                      |

|              | Open Drain High Voltage                    |                |      | 8.5             | V    | RA4 pin                                                                                |

|              | Capacitive Loading Specs on<br>Output Pins |                |      |                 |      |                                                                                        |

| D100 Cosc2 C | OSC2 pin                                   |                |      | 15              | pF   | In XT, HS and LP modes when external clock used to drive OSC1.                         |

| D101 Cio A   | All I/O pins/OSC2 (in RC mode)             |                |      | 50              | pF   |                                                                                        |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in Active Operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD, MCLR = VDD; WDT enabled/disabled as specified.

The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP

- mode, with all I/O pins in hi-impedance state and tied to VDD or VSs.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- 5: The Δ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 6: Commercial temperature range only.

- 7: See Section 12.1 and Section 12.3 for 16C62X and 16CR62X devices for operation between 20 MHz and 40 MHz for valid modified characteristics.

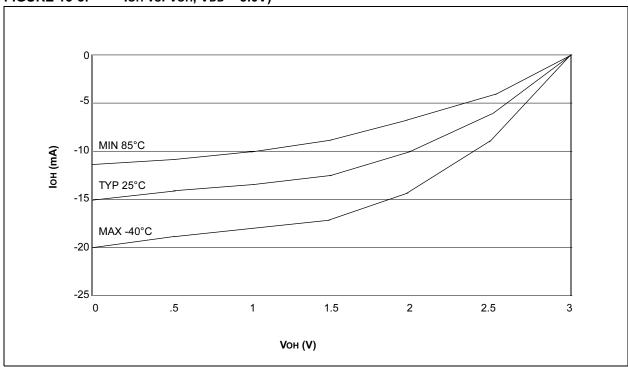

FIGURE 13-5: IOH VS. VOH, VDD = 3.0V)

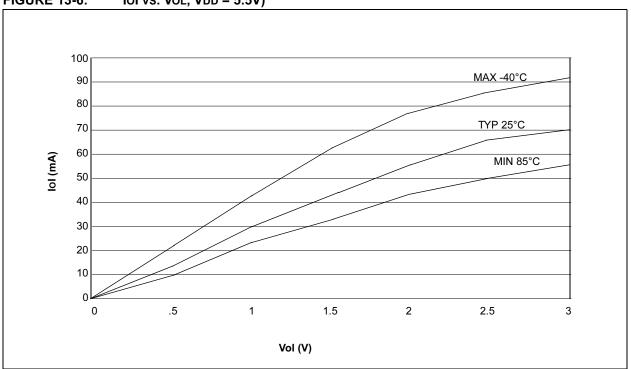

FIGURE 13-6: IOI vs. Vol., VDD = 5.5V)