Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c622a-20-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

# FIGURE 4-6: DATA MEMORY MAP FOR THE PIC16C620A/CR620A/621A

|                 | 11010002                       |                     | - 17 (          |  |  |  |  |  |  |  |

|-----------------|--------------------------------|---------------------|-----------------|--|--|--|--|--|--|--|

| File<br>Address | 3                              |                     | File<br>Address |  |  |  |  |  |  |  |

| 00h             | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup> | 80h             |  |  |  |  |  |  |  |

| 01h             | TMR0                           | OPTION              | 81h             |  |  |  |  |  |  |  |

| 02h             | PCL                            | PCL                 | 82h             |  |  |  |  |  |  |  |

| 03h             | STATUS                         | STATUS              | 83h             |  |  |  |  |  |  |  |

| 04h             | FSR                            | FSR                 | 84h             |  |  |  |  |  |  |  |

| 05h             | PORTA                          | TRISA               | 85h             |  |  |  |  |  |  |  |

| 06h             | PORTB                          | TRISB               | 86h             |  |  |  |  |  |  |  |

| 07h             |                                |                     | 87h             |  |  |  |  |  |  |  |

| 08h             |                                |                     | 88h             |  |  |  |  |  |  |  |

| 09h             |                                |                     | 89h             |  |  |  |  |  |  |  |

| 0Ah             | PCLATH                         | PCLATH              | 8Ah             |  |  |  |  |  |  |  |

| 0Bh             | INTCON                         | INTCON              | 8Bh             |  |  |  |  |  |  |  |

| 0Ch             | PIR1                           | PIE1                | 8Ch             |  |  |  |  |  |  |  |

| 0Dh             |                                |                     | 8Dh             |  |  |  |  |  |  |  |

| 0Eh             |                                | PCON                | 8Eh             |  |  |  |  |  |  |  |

| 0Fh             |                                |                     | 8Fh             |  |  |  |  |  |  |  |

| 10h             |                                |                     | 90h             |  |  |  |  |  |  |  |

| 11h             |                                |                     | 91h             |  |  |  |  |  |  |  |

| 12h             |                                |                     | 92h             |  |  |  |  |  |  |  |

| 13h             |                                |                     | 93h             |  |  |  |  |  |  |  |

| 14h             |                                |                     | 94h             |  |  |  |  |  |  |  |

| 15h             |                                |                     | 95h             |  |  |  |  |  |  |  |

| 16h             |                                |                     | 96h             |  |  |  |  |  |  |  |

| 17h             |                                |                     | 97h             |  |  |  |  |  |  |  |

| 18h             |                                |                     | 98h             |  |  |  |  |  |  |  |

| 19h             |                                |                     | 99h             |  |  |  |  |  |  |  |

| 1Ah             |                                |                     | 9Ah             |  |  |  |  |  |  |  |

| 1Bh             |                                |                     | 9Bh             |  |  |  |  |  |  |  |

| 1Ch             |                                |                     | 9Ch             |  |  |  |  |  |  |  |

| 1Dh             |                                |                     | 9Dh             |  |  |  |  |  |  |  |

| 1Eh             |                                |                     | 9Eh             |  |  |  |  |  |  |  |

| 1Fh             | CMCON                          | VRCON               | 9Fh             |  |  |  |  |  |  |  |

| 20h             | General<br>Purpose<br>Register |                     | A0h             |  |  |  |  |  |  |  |

| 6Fh             |                                |                     |                 |  |  |  |  |  |  |  |

| 70h             | General                        |                     | F0h             |  |  |  |  |  |  |  |

|                 | Purpose<br>Register            | Accesses<br>70h-7Fh |                 |  |  |  |  |  |  |  |

| 7Fh             | Bank 0                         | Bank 1              | 」 FFh           |  |  |  |  |  |  |  |

| Unimp           | lemented data mer              | mory locations, rea | ad as '0'.      |  |  |  |  |  |  |  |

| Note 1:         | Not a physical re              | gister.             |                 |  |  |  |  |  |  |  |

|                 |                                |                     |                 |  |  |  |  |  |  |  |

#### FIGURE 4-7: DATA MEMORY MAP FOR THE PIC16C622A

|                 |                                                                                           | C10C022A            |                 |  |  |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------|---------------------|-----------------|--|--|--|--|--|--|--|

| File<br>Address | 3                                                                                         |                     | File<br>Address |  |  |  |  |  |  |  |

| 00h             | INDF <sup>(1)</sup>                                                                       | INDF <sup>(1)</sup> | 80h             |  |  |  |  |  |  |  |

| 01h             | TMR0                                                                                      | OPTION              | 81h             |  |  |  |  |  |  |  |

| 02h             | PCL                                                                                       | PCL                 | 82h             |  |  |  |  |  |  |  |

| 03h             | STATUS                                                                                    | STATUS              | 83h             |  |  |  |  |  |  |  |

| 04h             | FSR                                                                                       | FSR                 | 84h             |  |  |  |  |  |  |  |

| 05h             | PORTA                                                                                     | TRISA               | 85h             |  |  |  |  |  |  |  |

| 06h             | PORTB                                                                                     | TRISB               | 86h             |  |  |  |  |  |  |  |

| 07h             |                                                                                           |                     | 87h             |  |  |  |  |  |  |  |

| 08h             |                                                                                           |                     | 88h             |  |  |  |  |  |  |  |

| 09h             |                                                                                           |                     | 89h             |  |  |  |  |  |  |  |

| 0Ah             | PCLATH                                                                                    | PCLATH              | 8Ah             |  |  |  |  |  |  |  |

| 0Bh             | INTCON                                                                                    | INTCON              | 8Bh             |  |  |  |  |  |  |  |

| 0Ch             | PIR1                                                                                      | PIE1                | 8Ch             |  |  |  |  |  |  |  |

| 0Dh             |                                                                                           |                     | 8Dh             |  |  |  |  |  |  |  |

| 0Eh             |                                                                                           | PCON                | 8Eh             |  |  |  |  |  |  |  |

| 0Fh             |                                                                                           |                     | 8Fh             |  |  |  |  |  |  |  |

| 10h             |                                                                                           |                     | 90h             |  |  |  |  |  |  |  |

| 11h             |                                                                                           |                     | 91h             |  |  |  |  |  |  |  |

| 12h             |                                                                                           |                     | 92h             |  |  |  |  |  |  |  |

| 13h             |                                                                                           |                     | 93h             |  |  |  |  |  |  |  |

| 14h             |                                                                                           |                     | 94h             |  |  |  |  |  |  |  |

| 15h             |                                                                                           |                     | 95h             |  |  |  |  |  |  |  |

| 16h             |                                                                                           |                     | 96h             |  |  |  |  |  |  |  |

| 17h             |                                                                                           |                     | 97h             |  |  |  |  |  |  |  |

| 18h             |                                                                                           |                     | 98h             |  |  |  |  |  |  |  |

| 19h             |                                                                                           |                     | 99h             |  |  |  |  |  |  |  |

| 1Ah             |                                                                                           |                     | 9Ah             |  |  |  |  |  |  |  |

| 1Bh             |                                                                                           |                     | 9Bh             |  |  |  |  |  |  |  |

| 1Ch             |                                                                                           |                     | 9Ch             |  |  |  |  |  |  |  |

| 1Dh             |                                                                                           |                     | 9Dh             |  |  |  |  |  |  |  |

| 1Eh             |                                                                                           |                     | 9Eh             |  |  |  |  |  |  |  |

| 1Fh             | CMCON                                                                                     | VRCON               | 9Fh             |  |  |  |  |  |  |  |

| 20h             |                                                                                           |                     | A0h             |  |  |  |  |  |  |  |

|                 | General                                                                                   | General             | Aon             |  |  |  |  |  |  |  |

|                 | Purpose<br>Register                                                                       | Purpose<br>Register |                 |  |  |  |  |  |  |  |

|                 | rtegister                                                                                 | rtegister           | BFh             |  |  |  |  |  |  |  |

|                 |                                                                                           |                     | C0h             |  |  |  |  |  |  |  |

| 0.51            |                                                                                           |                     |                 |  |  |  |  |  |  |  |

| 6Fh             | 0                                                                                         |                     | F0h             |  |  |  |  |  |  |  |

| 70h             | General<br>Purpose                                                                        | Accesses            |                 |  |  |  |  |  |  |  |

| 754             | Register                                                                                  | 70h-7Fh             | FFh             |  |  |  |  |  |  |  |

| 7Fh             | Bank 0                                                                                    | Bank 1              | → FF11          |  |  |  |  |  |  |  |

|                 |                                                                                           |                     |                 |  |  |  |  |  |  |  |

| Unimp           | plemented data me                                                                         | mory locations, re  | ad as '0'.      |  |  |  |  |  |  |  |

| Note 1:         | Unimplemented data memory locations, read as '0'. <b>Note 1:</b> Not a physical register. |                     |                 |  |  |  |  |  |  |  |

#### 4.2.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uuluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any STATUS bit. For other instructions not affecting any STATUS bits, see the "Instruction Set Summary".

- Note 1: The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16C62X and should be programmed as '0'. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The <u>C and DC bits</u> operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

#### REGISTER 4-1: STATUS REGISTER (ADDRESS 03H OR 83H)

|         | Reserved                                                                                                                                                 | Reserved                           | R/W-0          | R-1            | R-1            | R/W-x          | R/W-x        | R/W-x          |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|----------------|----------------|--------------|----------------|--|--|

|         | IRP                                                                                                                                                      | RP1                                | RP0            | TO             | PD             | Z              | DC           | С              |  |  |

|         | bit 7                                                                                                                                                    |                                    |                |                |                |                |              | bit 0          |  |  |

|         |                                                                                                                                                          |                                    |                |                |                |                |              |                |  |  |

| bit 7   | -                                                                                                                                                        | ter Bank Sel                       | -              | d for indirect | addressing     | )              |              |                |  |  |

|         |                                                                                                                                                          | , 3 (100h - 1<br>, 1 (00h - FF     |                |                |                |                |              |                |  |  |

|         |                                                                                                                                                          | t is reserved                      |                | 16C62X; alv    | /ays maintai   | n this bit cle | ar.          |                |  |  |

| bit 6-5 |                                                                                                                                                          | Register Ban                       |                |                | -              |                |              |                |  |  |

|         |                                                                                                                                                          | 1 (80h - FFh                       |                |                |                |                |              |                |  |  |

|         |                                                                                                                                                          | 0 (00h - 7Fh                       |                |                |                |                |              |                |  |  |

|         | Each bank<br>clear.                                                                                                                                      | is 128 bytes                       | . The RP1 t    | oit is reserve | ed on the PIC  | C16C62X; a     | lways mainta | ain this bit   |  |  |

| bit 4   | TO: Time-c                                                                                                                                               | out bit                            |                |                |                |                |              |                |  |  |

|         |                                                                                                                                                          | ower-up, CLI                       | RWDT instruc   | ction. or SLE  | EP instruction | on             |              |                |  |  |

|         |                                                                                                                                                          | time-out oc                        |                | ,              |                |                |              |                |  |  |

| bit 3   | PD: Power                                                                                                                                                | -down bit                          |                |                |                |                |              |                |  |  |

|         | -                                                                                                                                                        | ower-up or b<br>cution of the      | -              |                | n              |                |              |                |  |  |

| bit 2   | Z: Zero bit                                                                                                                                              |                                    |                |                |                |                |              |                |  |  |

|         |                                                                                                                                                          | sult of an arit<br>sult of an arit |                |                |                | )              |              |                |  |  |

| bit 1   |                                                                                                                                                          |                                    |                | • •            |                |                | )(for borrow | the polarity   |  |  |

|         | <b>DC</b> : Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)(for borrow the polarity is reversed)                                        |                                    |                |                |                |                |              |                |  |  |

|         | <ul> <li>1 = A carry-out from the 4th low order bit of the result occurred</li> <li>0 = No carry-out from the 4th low order bit of the result</li> </ul> |                                    |                |                |                |                |              |                |  |  |

|         |                                                                                                                                                          | -                                  |                |                |                |                |              |                |  |  |

| bit 0   | •                                                                                                                                                        | orrow bit (AD                      |                |                |                |                |              |                |  |  |

|         | •                                                                                                                                                        | -out from the<br>ry-out from th    | -              |                |                |                |              |                |  |  |

|         | Note:                                                                                                                                                    | For borrow t                       | he polarity i  | s reversed.    | A subtraction  | on is execut   | ed by addin  | g the two's    |  |  |

|         |                                                                                                                                                          | complement                         |                |                |                |                |              | s, this bit is |  |  |

|         |                                                                                                                                                          | loaded with e                      | either the hig | gh or low or   | der bit of the | source reg     | ister.       |                |  |  |

|         | Legend:                                                                                                                                                  | L. L. 14                           |                |                |                |                | hit as a d   | 0              |  |  |

|         | R = Reada                                                                                                                                                |                                    |                | ritable bit    |                | •              | bit, read as |                |  |  |

|         | - n = Value                                                                                                                                              | at POR                             | 1′ = Bi        | it is set      | '0' = Bit i    | scleared       | x = Bit is u | nknown         |  |  |

#### 4.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

| E PE<br>Global Internables all un<br>isables all in<br>Peripheral<br>nables all p<br>TMR0 Ove<br>nables the T<br>isables the | N-0     R/W-0       EIE     TOIE       rrupt Enable bit       n-masked interrunts       Interrupts       Interrupt Enable       n-masked periphoreripheral interrupt       erflow Interrupt Entrupt       TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | R/W-0<br>RBIE                                                                                                                                                        | R/W-0<br>T0IF                                                                                                                                                                                                                                | R/W-0<br>INTF                                                                                                                                                                                                            | R/W-x<br>RBIF<br>bit 0                                                                                                                                                                                                                                                                     |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          | bit 0                                                                                                                                                                                                                                                                                      |  |  |  |  |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| sables all in<br>Peripheral<br>nables all un<br>sables all p<br>TMR0 Ove<br>nables the T<br>isables the                      | nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                                                          | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the                                                       | n-masked periph<br>peripheral interru<br>rflow Interrupt Er<br>TMR0 interrupt                                                                                                                                            | neral interrupt<br>pts                                                                                                  | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| sables all p<br>TMR0 Ove<br>nables the<br>sables the                                                                         | peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                                                                                                              | pts                                                                                                                     | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| TMR0 Ove<br>nables the<br>sables the                                                                                         | rflow Interrupt Er<br>TMR0 interrupt                                                                                                                                                                                     |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| nables the<br>isables the                                                                                                    | TMR0 interrupt                                                                                                                                                                                                           | nable bit                                                                                                               |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| sables the                                                                                                                   |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                              | I MRU interrupt                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                              | External Interrupt                                                                                                                                                                                                       |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| <ul> <li>1 = Enables the RB0/INT external interrupt</li> <li>0 = Disables the RB0/INT external interrupt</li> </ul>          |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                              | hange Interrupt E                                                                                                                                                                                                        |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                              | RB port change i                                                                                                                                                                                                         |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                              | RB port change                                                                                                                                                                                                           | •                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| TMR0 Ove                                                                                                                     | rflow Interrupt Fl                                                                                                                                                                                                       | ag bit                                                                                                                  |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| MR0 registe                                                                                                                  | er has overflowed                                                                                                                                                                                                        | d (must be cle                                                                                                          | eared in soft                                                                                                                                                        | ware)                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| MR0 registe                                                                                                                  | er did not overflov                                                                                                                                                                                                      | W                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| RB0/INT E                                                                                                                    | xternal Interrupt                                                                                                                                                                                                        | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      | red in softwa                                                                                                                                                                                                                                | are)                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| RB Port Cl                                                                                                                   | hange Interrupt F                                                                                                                                                                                                        | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 'hen at leas                                                                                                                 |                                                                                                                                                                                                                          | •                                                                                                                       | -                                                                                                                                                                    | (must be cle                                                                                                                                                                                                                                 | ared in softw                                                                                                                                                                                                            | ware)                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                                                                                                              | ne RB0/INT<br>ne RB0/INT<br>RB Port C<br>hen at leas                                                                                                                                                                     | ne RB0/INT external interrune<br>RB0/INT external interrun<br>RB Port Change Interrupt I<br>hen at least one of the RB< | ne RB0/INT external interrupt did not occ<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins cha<br>one of the RB<7:4> pins have changed s | ne RB0/INT external interrupt occurred (must be clea<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state<br>one of the RB<7:4> pins have changed state | ne RB0/INT external interrupt occurred (must be cleared in softwa<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cle | ne RB0/INT external interrupt occurred (must be cleared in software)<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cleared in softwore)<br>one of the RB<7:4> pins have changed state |  |  |  |  |

| REGISTER 4-3: | INTCON REGISTER (ADDRESS 0BH OR 8BH) |

|---------------|--------------------------------------|

|---------------|--------------------------------------|

| Legend:            |                  |                      |                                  |  |  |  |

|--------------------|------------------|----------------------|----------------------------------|--|--|--|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | = Unimplemented bit, read as '0' |  |  |  |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown               |  |  |  |

#### 4.2.2.4 PIE1 Register

This register contains the individual enable bit for the comparator interrupt.

| <b>REGISTER 4-4:</b>                                                                                                                                         | PIE1 REGISTER (ADDRESS 8CH)                                                                                                    |                            |          |     |     |     |     |       |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------|-----|-----|-----|-----|-------|--|--|--|

|                                                                                                                                                              | U-0                                                                                                                            | R/W-0                      | U-0      | U-0 | U-0 | U-0 | U-0 | U-0   |  |  |  |

|                                                                                                                                                              |                                                                                                                                | CMIE                       | _        |     |     | —   | _   | —     |  |  |  |

|                                                                                                                                                              | bit 7                                                                                                                          |                            |          |     |     |     |     | bit 0 |  |  |  |

| bit 7                                                                                                                                                        | Unimpleme                                                                                                                      | Unimplemented: Read as '0' |          |     |     |     |     |       |  |  |  |

| bit 6                                                                                                                                                        | <b>CMIE</b> : Comparator Interrupt Enable bit<br>1 = Enables the Comparator interrupt<br>0 = Disables the Comparator interrupt |                            |          |     |     |     |     |       |  |  |  |

| bit 5-0                                                                                                                                                      | Unimpleme                                                                                                                      | nted: Read                 | d as '0' |     |     |     |     |       |  |  |  |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkno |                                                                                                                                |                            |          |     |     |     |     |       |  |  |  |

### 4.2.2.5 PIR1 Register

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of |  |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User               |  |  |  |  |  |  |  |

|       | software should ensure the appropriate                                                     |  |  |  |  |  |  |  |

|       | interrupt flag bits are clear prior to enabling                                            |  |  |  |  |  |  |  |

|       | an interrupt.                                                                              |  |  |  |  |  |  |  |

# REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

| ER 4-5: | PIRT REGI                                                                  | SIER (AL      | DRESS 0     |              |          |           |                |       |  |  |  |  |

|---------|----------------------------------------------------------------------------|---------------|-------------|--------------|----------|-----------|----------------|-------|--|--|--|--|

|         | U-0                                                                        | R/W-0         | U-0         | U-0          | U-0      | U-0       | U-0            | U-0   |  |  |  |  |

|         |                                                                            | CMIF          |             | —            | _        |           |                |       |  |  |  |  |

|         | bit 7                                                                      |               |             |              |          |           |                | bit 0 |  |  |  |  |

|         |                                                                            |               |             |              |          |           |                |       |  |  |  |  |

| bit 7   | Unimplemented: Read as '0'                                                 |               |             |              |          |           |                |       |  |  |  |  |

| bit 6   | CMIF: Comparator Interrupt Flag bit                                        |               |             |              |          |           |                |       |  |  |  |  |

|         | 1 = Compai                                                                 | rator input h | nas changed | l            |          |           |                |       |  |  |  |  |

|         | 0 = Comparator input has not changed                                       |               |             |              |          |           |                |       |  |  |  |  |

| bit 5-0 | Unimpleme                                                                  | ented: Rea    | d as '0'    |              |          |           |                |       |  |  |  |  |

|         |                                                                            |               |             |              |          |           |                |       |  |  |  |  |

|         | Legend:                                                                    |               |             |              |          |           |                |       |  |  |  |  |

|         | R = Readab                                                                 | ole bit       | W = W       | /ritable bit | U = Unim | plemented | bit, read as ' | 0'    |  |  |  |  |

|         | - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow |               |             |              |          |           |                |       |  |  |  |  |

#### TABLE 5-1:PORTA FUNCTIONS

| Name         | Bit # | Buffer<br>Type | Function                                                                                          |

|--------------|-------|----------------|---------------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0  | ST             | Input/output or comparator input                                                                  |

| RA1/AN1      | bit1  | ST             | Input/output or comparator input                                                                  |

| RA2/AN2/VREF | bit2  | ST             | Input/output or comparator input or VREF output                                                   |

| RA3/AN3      | bit3  | ST             | Input/output or comparator input/output                                                           |

| RA4/T0CKI    | bit4  | ST             | Input/output or external clock input for TMR0 or comparator output.<br>Output is open drain type. |

Legend: ST = Schmitt Trigger input

### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|------------|------------|------------|------------|------------|-----------------|---------------------------------|

| 05h     | PORTA |       |       |       | RA4        | RA3        | RA2        | RA1        | RA0        | x 0000          | u 0000                          |

| 85h     | TRISA |       |       | _     | TRISA<br>4 | TRISA<br>3 | TRISA<br>2 | TRISA<br>1 | TRISA<br>0 | 1 1111          | 1 1111                          |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | _          | CIS        | CM2        | CM1        | CM0        | 00 0000         | 00 0000                         |

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _          | VR3        | VR2        | VR1        | VR0        | 000- 0000       | 000- 0000                       |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

Note: Shaded bits are not used by PORTA.

# 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- · Edge select for external clock

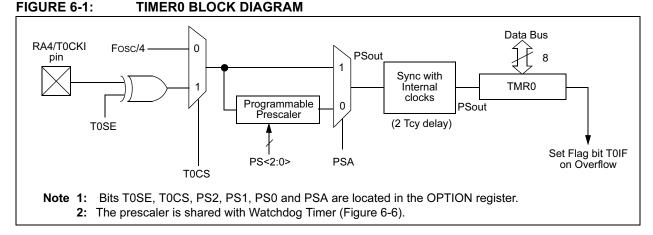

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

### 6.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP, since the timer is shut off during SLEEP. See Figure 6-4 for Timer0 interrupt timing.

#### FIGURE 6-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

| (Program<br>Counter) | ( PC-1      | ) PC        | ( <u>PC+1</u> )        | PC+2                   | <u>PC+3</u> χ          | PC+4                   | PC+5 χ                     | PC+6                     |

|----------------------|-------------|-------------|------------------------|------------------------|------------------------|------------------------|----------------------------|--------------------------|

| Instruction<br>Fetch |             | MOVWF TMR   | 0MOVF TMR0,V           | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W                | 1                        |

|                      | i.          | 1           |                        |                        | i                      |                        | i                          |                          |

| TMR0                 | то х        | T0+1 )(     | T0+2 X                 | 1                      | NT0                    |                        | NT0+1 \                    | NT0+2 )                  |

| Instruction          | 1<br>1<br>1 | 1<br>1<br>1 | <b></b>                | <b>≜</b>               | <b>≜</b>               | <b>†</b>               | <b>†</b>                   | <b>≜</b>                 |

| Executed             | 1           | 1           | Write TMR0<br>executed | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1 | Read TMR0<br>reads NT0 + |

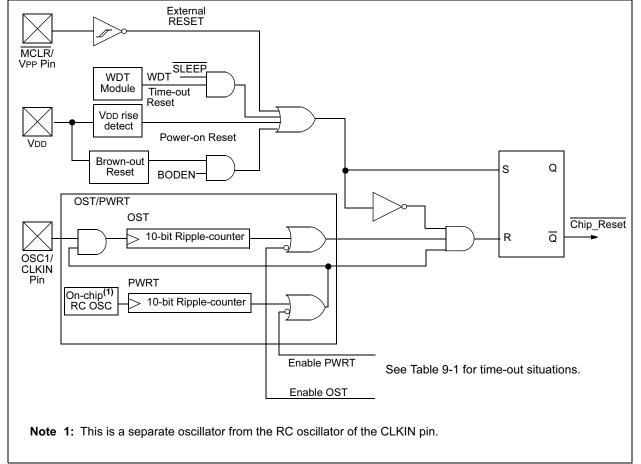

# 9.3 RESET

The PIC16C62X differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) WDT Reset (normal operation)

- e) WDT wake-up (SLEEP)

- f) Brown-out Reset (BOR)

Some registers are not affected in any RESET condition Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset,