Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

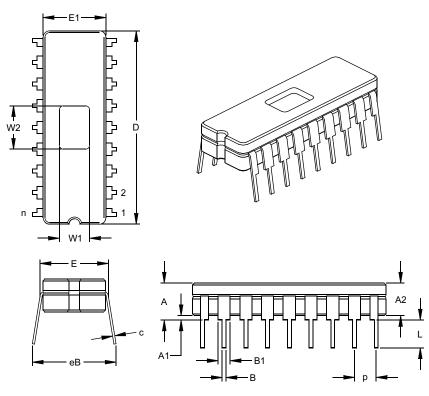

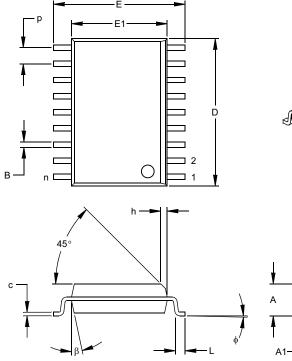

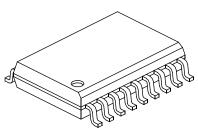

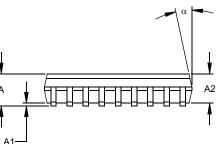

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c622a-20e-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| Name         | DIP/SOIC<br>Pin # | SSOP<br>Pin # | I/O/P Type             | Buffer<br>Type        | Description                                                                                                                                                                                                         |

|--------------|-------------------|---------------|------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 16                | 18            | I                      | ST/CMOS               | Oscillator crystal input/external clock source input.                                                                                                                                                               |

| OSC2/CLKOUT  | 15                | 17            | 0                      | _                     | Oscillator crystal output. Connects to crystal or resonator<br>in Crystal Oscillator mode. In RC mode, OSC2 pin out-<br>puts CLKOUT, which has 1/4 the frequency of OSC1<br>and denotes the instruction cycle rate. |

| MCLR/VPP     | 4                 | 4             | I/P                    | ST                    | Master Clear (Reset) input/programming voltage input.<br>This pin is an Active Low Reset to the device.                                                                                                             |

|              |                   |               |                        |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                                 |

| RA0/AN0      | 17                | 19            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |

| RA1/AN1      | 18                | 20            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |

| RA2/AN2/VREF | 1                 | 1             | I/O                    | ST                    | Analog comparator input or VREF output                                                                                                                                                                              |

| RA3/AN3      | 2                 | 2             | I/O                    | ST                    | Analog comparator input /output                                                                                                                                                                                     |

| RA4/T0CKI    | 3                 | 3             | I/O                    | ST                    | Can be selected to be the clock input to the Timer<br>timer/counter or a comparator output. Output is<br>open drain type.                                                                                           |

|              |                   |               |                        |                       | PORTB is a bi-directional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs.                                                                                                 |

| RB0/INT      | 6                 | 7             | I/O                    | TTL/ST <sup>(1)</sup> | RB0/INT can also be selected as an externa interrupt pin.                                                                                                                                                           |

| RB1          | 7                 | 8             | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB2          | 8                 | 9             | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB3          | 9                 | 10            | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB4          | 10                | 11            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |

| RB5          | 11                | 12            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |

| RB6          | 12                | 13            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming clock                                                                                                                                                                   |

| RB7          | 13                | 14            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming data.                                                                                                                                                                   |

| Vss          | 5                 | 5,6           | Р                      |                       | Ground reference for logic and I/O pins.                                                                                                                                                                            |

| Vdd          | 14                | 15,16         | Р                      | _                     | Positive supply for logic and I/O pins.                                                                                                                                                                             |

| Legend:      | O = out<br>— = No | •             | I/O = inp<br>I = Input | ut/output             | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                             |

TTL = TTL input

**Note** 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

### 4.2.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uuluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any STATUS bit. For other instructions not affecting any STATUS bits, see the "Instruction Set Summary".

- Note 1: The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16C62X and should be programmed as '0'. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The <u>C and DC bits</u> operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

### REGISTER 4-1: STATUS REGISTER (ADDRESS 03H OR 83H)

|                                                                                          | Reserved                                                                                                                                                                | Reserved                                                      | R/W-0          | R-1            | R-1            | R/W-x          | R/W-x        | R/W-x          |  |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------|----------------|----------------|----------------|--------------|----------------|--|

|                                                                                          | IRP                                                                                                                                                                     | RP1                                                           | RP0            | TO             | PD             | Z              | DC           | С              |  |

|                                                                                          | bit 7                                                                                                                                                                   |                                                               |                |                |                |                |              | bit 0          |  |

|                                                                                          |                                                                                                                                                                         |                                                               |                |                |                |                |              |                |  |

| bit 7                                                                                    | -                                                                                                                                                                       | ter Bank Sel                                                  | -              | d for indirect | addressing     | )              |              |                |  |

|                                                                                          |                                                                                                                                                                         | , 3 (100h - 1<br>, 1 (00h - FF                                |                |                |                |                |              |                |  |

|                                                                                          |                                                                                                                                                                         | t is reserved                                                 |                | 16C62X; alv    | /ays maintai   | n this bit cle | ar.          |                |  |

| bit 6-5                                                                                  |                                                                                                                                                                         | Register Ban                                                  |                |                | -              |                |              |                |  |

|                                                                                          |                                                                                                                                                                         | 1 (80h - FFh                                                  |                |                |                |                |              |                |  |

|                                                                                          |                                                                                                                                                                         | 0 (00h - 7Fh                                                  |                |                |                |                |              |                |  |

|                                                                                          | Each bank<br>clear.                                                                                                                                                     | is 128 bytes                                                  | . The RP1 t    | oit is reserve | ed on the PIC  | C16C62X; a     | lways mainta | ain this bit   |  |

| bit 4                                                                                    | TO: Time-c                                                                                                                                                              | out bit                                                       |                |                |                |                |              |                |  |

|                                                                                          |                                                                                                                                                                         |                                                               | RWDT instruc   | ction. or SLE  | EP instruction | on             |              |                |  |

| 1 = After power-up, CLRWDT instruction, or SLEEP instruction 0 = A WDT time-out occurred |                                                                                                                                                                         |                                                               |                |                |                |                |              |                |  |

| bit 3                                                                                    | PD: Power                                                                                                                                                               | -down bit                                                     |                |                |                |                |              |                |  |

|                                                                                          | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                  |                                                               |                |                |                |                |              |                |  |

| bit 2                                                                                    | Z: Zero bit                                                                                                                                                             |                                                               |                |                |                |                |              |                |  |

|                                                                                          |                                                                                                                                                                         | sult of an arit<br>sult of an arit                            |                |                |                | )              |              |                |  |

| bit 1                                                                                    |                                                                                                                                                                         | arry/borrow b                                                 |                | • •            |                |                | )(for borrow | the polarity   |  |

|                                                                                          | is reversed                                                                                                                                                             | -                                                             | ζ ,            |                | ·              |                |              |                |  |

|                                                                                          |                                                                                                                                                                         | -out from the                                                 |                |                |                | rred           |              |                |  |

|                                                                                          |                                                                                                                                                                         | ry-out from th                                                |                |                |                |                |              |                |  |

| bit 0                                                                                    | •                                                                                                                                                                       | C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) |                |                |                |                |              |                |  |

|                                                                                          | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |                                                               |                |                |                |                |              |                |  |

|                                                                                          | Note:                                                                                                                                                                   | For borrow t                                                  | he polarity i  | s reversed.    | A subtraction  | on is execut   | ed by addin  | g the two's    |  |

|                                                                                          |                                                                                                                                                                         | complement                                                    |                |                |                |                |              | s, this bit is |  |

|                                                                                          |                                                                                                                                                                         | loaded with e                                                 | either the hig | gh or low or   | der bit of the | source reg     | ister.       |                |  |

|                                                                                          | Legend:                                                                                                                                                                 | L. L. 14                                                      |                |                |                |                | hit as a d   | 0              |  |

|                                                                                          | R = Reada                                                                                                                                                               |                                                               |                | ritable bit    |                | •              | bit, read as |                |  |

|                                                                                          | - n = Value                                                                                                                                                             | at POR                                                        | 1′ = Bi        | it is set      | '0' = Bit i    | scleared       | x = Bit is u | nknown         |  |

### **OPTION Register** 4.2.2.2

The OPTION register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |

|-------|-------------------------------------------|

|       | TMR0, assign the prescaler to the WDT     |

|       | (PSA = 1).                                |

|         | R/W-1                                                                                                            | R/W-1                          | R/W-1                      | R/W-1                        | R/W-1         | R/W-1 | R/W-1 | R/W-1 |

|---------|------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------|------------------------------|---------------|-------|-------|-------|

|         | RBPU                                                                                                             | INTEDG                         | TOCS                       | TOSE                         | PSA           | PS2   | PS1   | PS0   |

|         | bit 7                                                                                                            |                                |                            |                              |               | •     |       | bit 0 |

| bit 7   | RBPU: PO                                                                                                         | RTB Pull-u                     | p Enable bi                | it                           |               |       |       |       |

|         |                                                                                                                  | 3 pull-ups ai<br>3 pull-ups ai |                            | y individual                 | port latch va | alues |       |       |

| bit 6   | INTEDG: I                                                                                                        | nterrupt Edg                   | e Select bit               | -                            |               |       |       |       |

|         |                                                                                                                  |                                | edge of RB0<br>edge of RB0 |                              |               |       |       |       |

| bit 5   | TOCS: TMI                                                                                                        | R0 Clock Sc                    | ource Select               | bit                          |               |       |       |       |

|         |                                                                                                                  | ion on RA4/<br>Il instruction  | T0CKI pin<br>cycle clock   | (CLKOUT)                     |               |       |       |       |

| bit 4   | TOSE: TM                                                                                                         | R0 Source E                    | Edge Select                | bit                          |               |       |       |       |

|         |                                                                                                                  |                                |                            | ition on RA4<br>ition on RA4 |               |       |       |       |

| bit 3   | PSA: Pres                                                                                                        | caler Assigr                   | iment bit                  |                              | -             |       |       |       |

|         | <ul> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul> |                                |                            |                              |               |       |       |       |

| bit 2-0 | PS<2:0>: Prescaler Rate Select bits                                                                              |                                |                            |                              |               |       |       |       |

|         | E                                                                                                                | Bit Value T                    | MR0 Rate                   | WDT Rate                     |               |       |       |       |

|         | -                                                                                                                | 000<br>001                     | 1:2<br>1:4                 | 1:1<br>1:2                   |               |       |       |       |

|         |                                                                                                                  | 010<br>011                     | 1 : 8<br>1 : 16            | 1:4<br>1:8                   |               |       |       |       |

|         |                                                                                                                  |                                |                            |                              |               |       |       |       |

|         |                                                                                                                  | 101                            | 1:64                       | 1:32                         |               |       |       |       |

|         |                                                                                                                  | 110<br>111                     | 1 : 128<br>1 : 256         | 1 : 64<br>1 : 128            |               |       |       |       |

|         |                                                                                                                  |                                |                            |                              |               |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 4.2.2.6 PCON Register

The PCON register contains flag bits to differentiate between a Power-on Reset, an external MCLR Reset, WDT Reset or a Brown-out Reset.

| Note: | BOR is unknown on Power-on Reset. It        |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | must then be set by the user and checked    |  |  |  |  |  |

|       | on subsequent RESETS to see if BOR is       |  |  |  |  |  |

|       | cleared, indicating a brown-out has         |  |  |  |  |  |

|       | occurred. The BOR STATUS bit is a "don't    |  |  |  |  |  |

|       | care" and is not necessarily predictable if |  |  |  |  |  |

|       | the brown-out circuit is disabled (by       |  |  |  |  |  |

|       | programming BODEN bit in the                |  |  |  |  |  |

|       | Configuration word).                        |  |  |  |  |  |

### REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

|   | U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|---|-------|-----|-----|-----|-----|-----|-------|-------|

| ſ | _     | —   | —   | —   | —   | —   | POR   | BOR   |

| - | bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR**: Power-on Reset STATUS bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 **BOR**: Brown-out Reset STATUS bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

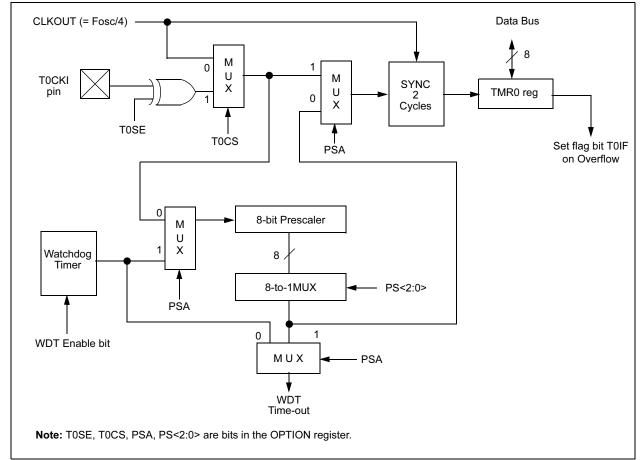

### 6.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 6-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

### FIGURE 6-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

The code example in Example 7-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

### EXAMPLE 7-1: INITIALIZING COMPARATOR MODULE

| MOVLW | 0x03         | ;Init comparator mode             |

|-------|--------------|-----------------------------------|

| MOVWF | CMCON        | ;CM<2:0> = 011                    |

| CLRF  | PORTA        | ;Init PORTA                       |

| BSF   | STATUS, RPO  | ;Select Bank1                     |

| MOVLW | 0x07         | ;Initialize data direction        |

| MOVWF | TRISA        | ;Set RA<2:0> as inputs            |

|       |              | ;RA<4:3> as outputs               |

|       |              | ;TRISA<7:5> always read `0'       |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| CALL  | DELAY 10     | ;10µs delay                       |

| MOVF  | CMCON,F      | ;Read CMCONtoend change condition |

| BCF   | PIR1,CMIF    | ;Clear pending interrupts         |

| BSF   | STATUS, RPO  | ;Select Bank 1                    |

| BSF   | PIE1,CMIE    | ;Enable comparator interrupts     |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| BSF   | INTCON, PEIE | ;Enable peripheral interrupts     |

| BSF   | INTCON, GIE  | ;Global interrupt enable          |

### 7.2 Comparator Operation

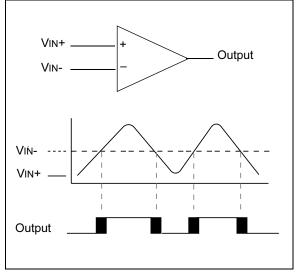

A single comparator is shown in Figure 7-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 7-2 represent the uncertainty due to input offsets and response time.

### 7.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator Operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 7-2).

### 7.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSs and VDD, and can be applied to either pin of the comparator(s).

### 7.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 10, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 7-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

### 7.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise the maximum delay of the comparators should be used (Table 12-2).

### 7.5 Comparator Outputs

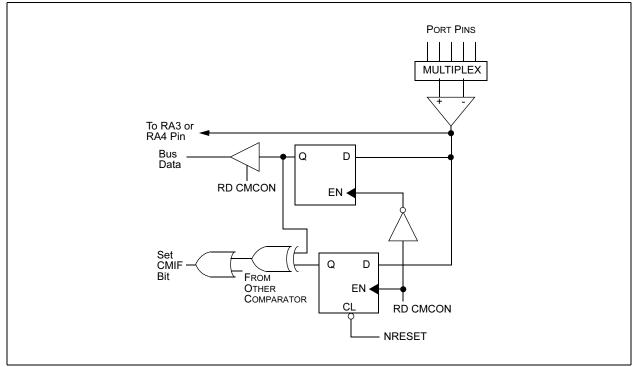

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 7-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3 and RA4 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

### FIGURE 7-3: COMPARATOR OUTPUT BLOCK DIAGRAM

### EXAMPLE 8-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; | 4 Inputs Muxed |

|-------|-------------|---|----------------|

| MOVWF | CMCON       | ; | to 2 comps.    |

| BSF   | STATUS, RPO | ; | go to Bank 1   |

| MOVLW | 0x0F        | ; | RA3-RA0 are    |

| MOVWF | TRISA       | ; | inputs         |

| MOVLW | 0xA6        | ; | enable VREF    |

| MOVWF | VRCON       | ; | low range      |

|       |             | ; | set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; | go to Bank O   |

| CALL  | DELAY10     | ; | 10µs delay     |

### 8.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 8-1) keep VREF from approaching VSS or VDD. The voltage reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the voltage reference can be found in Table 12-2.

### 8.3 Operation During SLEEP

When the device wakes up from SLEEP through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the voltage reference should be disabled.

### 8.4 Effects of a RESET

A device RESET disables the voltage reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

### 8.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the voltage reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the voltage reference output for external connections to VREF. Figure 8-2 shows an example buffering technique.

# FIGURE 8-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

### TABLE 8-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | -      | CIS    | CM2    | CM1    | CM0    | 00 0000         | 00 0000                         |

| 85h     | TRISA | _     |       |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

**Note:** - = Unimplemented, read as "0"

# 9.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16C62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-Circuit Serial Programming™

The PIC16C62X devices have a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

### 9.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

### 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

The Power-up Time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters for details.

### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

### 9.4.4 BROWN-OUT RESET (BOR)

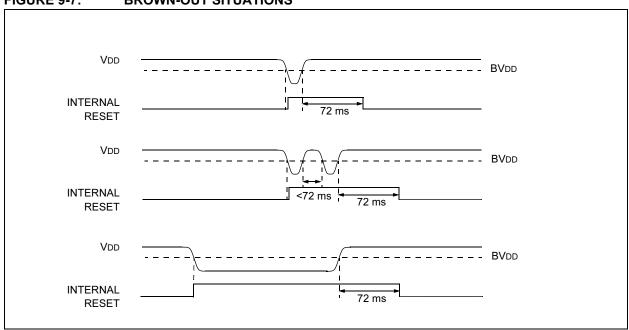

The PIC16C62X members have on-chip Brown-out Reset circuitry. A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V refer to VBOR parameter D005 (VBOR) for greater than parameter (TBOR) in Table 12-5. The brown-out situation will RESET the chip. A RESET won't occur if VDD falls below 4.0V for less than parameter (TBOR).

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 9-7 shows typical Brown-out situations.

### FIGURE 9-7: BROWN-OUT SITUATIONS

# PIC16C62X

### **FIGURE 9-11: EXTERNAL POWER-ON RESET CIRCUIT (FOR** SLOW VDD POWER-UP) Vdd Vdd D R R1 MCLR PIC16C62X С Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down. **2:** < 40 k $\Omega$ is recommended to make sure that voltage drop across R does not violate the device's electrical specification. **3:** R1 = $100\Omega$ to 1 k $\Omega$ will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin

breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

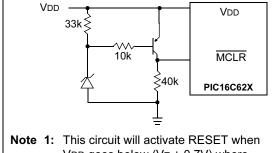

### FIGURE 9-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate RESET when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- **2:** Internal Brown-out Reset circuitry should be disabled when using this circuit.

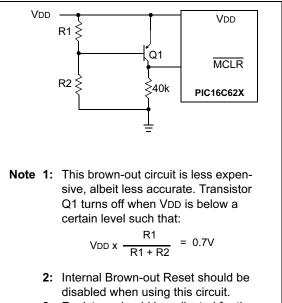

### FIGURE 9-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

**3:** Resistors should be adjusted for the characteristics of the transistor.

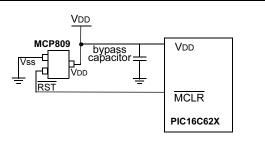

### FIGURE 9-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active RESET pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

## **10.1** Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |  |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |  |  |  |

| Encoding:        | 11 111x kkkk kkkk                                                                                                          |  |  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and<br>the result is placed in the W<br>register. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                          |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                          |  |  |  |  |  |  |  |

| Example          | ADDLW 0x15                                                                                                                 |  |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25                                                            |  |  |  |  |  |  |  |

| ANDLW            | AND Literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |

| Operands:        | $0 \le k \le 255$                                                                                                      |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register. |

| Words:           | 1                                                                                                                      |

| Cycles:          | 1                                                                                                                      |

| Example          | ANDLW 0x5F                                                                                                             |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                        |

| ANDWF            | AND W with f                                                                                                           |

| ADDWF            | Add W and f                                                                                                                                                                    |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in[0,1] \end{array}$                                                                                                                     |  |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (dest)                                                                                                                                                 |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |  |  |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                              |  |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                              |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                              |  |  |  |  |  |  |

| Example          | ADDWF FSR, <b>O</b>                                                                                                                                                            |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                    |  |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |  |  |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                          |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |  |  |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                           |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                           |  |  |  |  |  |  |  |

| Example          | ANDWF FSR, <b>1</b>                                                                                                                                         |  |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                                 |  |  |  |  |  |  |  |

| RLF              | Rotate L                                                                  | eft f thro                                                | bugł                    | n Carı                               | ry                             |  |

|------------------|---------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------|--------------------------------------|--------------------------------|--|

| Syntax:          | [ label ]                                                                 | RLF                                                       | f,d                     |                                      |                                |  |

| Operands:        | $0 \le f \le 12$<br>$d \in [0,1]$                                         | 27                                                        |                         |                                      |                                |  |

| Operation:       | See desc                                                                  | cription b                                                | elow                    | v                                    |                                |  |

| Status Affected: | С                                                                         |                                                           |                         |                                      |                                |  |

| Encoding:        | 00                                                                        | 1101                                                      | df                      | ff                                   | ffff                           |  |

| Description:     | The cont<br>rotated o<br>the Carry<br>is placed<br>1, the res<br>register | ne bit to<br>Flag. If '<br>in the W<br>sult is sto<br>f'. | the l<br>d' is<br>/ reg | left thi<br>0, the<br>ister.<br>back | rough<br>e result<br>If 'd' is |  |

| Words:           | 1                                                                         |                                                           |                         |                                      | -                              |  |

| Cycles:          | 1                                                                         |                                                           |                         |                                      |                                |  |

| Example          | RLF                                                                       | REG1,(                                                    | h                       |                                      |                                |  |

| лапро            | Before In                                                                 | struction<br>REG1<br>C                                    |                         | 1110<br>0                            | 0110                           |  |

|                  |                                                                           | REG1<br>W<br>C                                            | =<br>=<br>=             | 1110<br>1100<br>1                    |                                |  |

| RRF              | Rotate R                                                                                                                                                                                                          | ight f th      | nroug       | gh Ca             | arry     |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-------------------|----------|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                         | RRF f          | ,d          |                   |          |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                       |                |             |                   |          |  |  |  |

| Operation:       | See desc                                                                                                                                                                                                          | ription b      | elow        | '                 |          |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |                |             |                   |          |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                                | 1100           | df          | ff                | ffff     |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |                |             |                   |          |  |  |  |

|                  |                                                                                                                                                                                                                   |                | Regis       | ter f             | <b>}</b> |  |  |  |

| Words:           | 1                                                                                                                                                                                                                 |                |             |                   |          |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                 |                |             |                   |          |  |  |  |

| Example          | RRF                                                                                                                                                                                                               |                | REG<br>0    | 61,               |          |  |  |  |

|                  | Before In                                                                                                                                                                                                         | structior      | ı           |                   |          |  |  |  |

|                  |                                                                                                                                                                                                                   | REG1<br>C      | =<br>=      | 1110<br>0         | 0110     |  |  |  |

|                  | After Inst                                                                                                                                                                                                        |                |             |                   |          |  |  |  |

|                  | 1                                                                                                                                                                                                                 | REG1<br>W<br>C | =<br>=<br>= | 1110<br>0111<br>0 |          |  |  |  |

SLEEP

| <b>VIII</b>      |                                                                                                                                                 |                                                                                                   |                                                             |                          |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------|--|--|--|--|

| Syntax:          | [ label<br>]                                                                                                                                    | SLEEF                                                                                             | D                                                           |                          |  |  |  |  |

| Operands:        | None                                                                                                                                            |                                                                                                   |                                                             |                          |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow PD \end{array}$ |                                                                                                   |                                                             |                          |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                          |                                                                                                   |                                                             |                          |  |  |  |  |

| Encoding:        | 00                                                                                                                                              | 0000                                                                                              | 0110                                                        | 0011                     |  |  |  |  |

| Description:     | PD is cle<br>STATUS<br>dog Time<br>cleared.<br>The proc<br>mode wi                                                                              | ver-down<br>eared. Tin<br>bit, TO i<br>er and its<br>cessor is<br>th the os<br>. See Se<br>tails. | me-out<br>is set. W<br>s prescal<br>put into s<br>scillator | atch-<br>er are<br>SLEEP |  |  |  |  |

| Words:           | 1                                                                                                                                               |                                                                                                   |                                                             |                          |  |  |  |  |

| Cycles:          | 1                                                                                                                                               |                                                                                                   |                                                             |                          |  |  |  |  |

| Example:         | SLEEP                                                                                                                                           |                                                                                                   |                                                             |                          |  |  |  |  |

NOTES:

### 12.2 DC Characteristics: PIC16C62XA-04 (Commercial, Industrial, Extended) PIC16C62XA-20 (Commercial, Industrial, Extended) PIC16LC62XA-04 (Commercial, Industrial, Extended)

| PIC16C        | C62XA |                                               | Opera<br>Stand | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq TA \leq +85^{\circ}$ C for industrial and $0^{\circ}$ C $\leq TA \leq +70^{\circ}$ C for commercial and $-40^{\circ}$ C $\leq TA \leq +125^{\circ}$ C for extendedStandard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $= TA \leq +85^{\circ}$ C for industrial and $0^{\circ}$ C $\leq TA \leq +85^{\circ}$ C for industrial and $0^{\circ}$ C $\leq TA \leq +70^{\circ}$ C for commercial and $-40^{\circ}$ C $\leq TA \leq +70^{\circ}$ C for extended |      |       |                                              |  |  |  |

|---------------|-------|-----------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------------------|--|--|--|

| Param.<br>No. | Sym   | Characteristic                                | Min            | Тур†                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Мах  | Units | Conditions                                   |  |  |  |

| D001          | Vdd   | Supply Voltage                                | 3.0            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.5  | V     | See Figures 12-1, 12-2, 12-3, 12-4, and 12-5 |  |  |  |

| D001          | Vdd   | Supply Voltage                                | 2.5            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.5  | V     | See Figures 12-1, 12-2, 12-3, 12-4, and 12-5 |  |  |  |

| D002          | Vdr   | RAM Data Retention<br>Voltage <sup>(1)</sup>  |                | 1.5*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | V     | Device in SLEEP mode                         |  |  |  |

| D002          | Vdr   | RAM Data Retention Voltage <sup>(1)</sup>     |                | 1.5*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | —    | V     | Device in SLEEP mode                         |  |  |  |

| D003          | VPOR  | VDD start voltage to<br>ensure Power-on Reset |                | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _    | V     | See section on Power-on Reset for details    |  |  |  |

| D003          | VPOR  | VDD start voltage to<br>ensure Power-on Reset |                | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —    | V     | See section on Power-on Reset for details    |  |  |  |

| D004          | SVDD  | VDD rise rate to ensure<br>Power-on Reset     | 0.05*          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —    | V/ms  | See section on Power-on Reset for details    |  |  |  |