# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

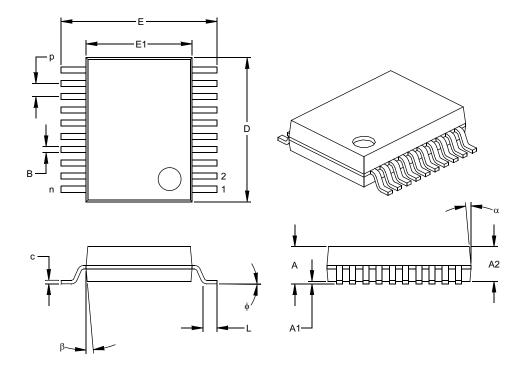

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c622at-04i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART, PRO MATE and PowerSmart are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Accuron, Application Maestro, dsPIC, dsPICDEM, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICkit, PICDEM, PICDEM.net, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPIC, Select Mode, SmartSensor, SmartShunt, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C62X uses a Harvard architecture, in which, program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture, where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C620(A) and PIC16CR620A address 512 x 14 on-chip program memory. The PIC16C621(A) addresses 1K x 14 program memory. The PIC16C622(A) addresses 2K x 14 program memory. All program memory is internal.

The PIC16C62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16C62X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

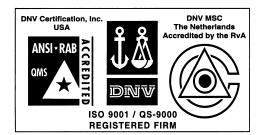

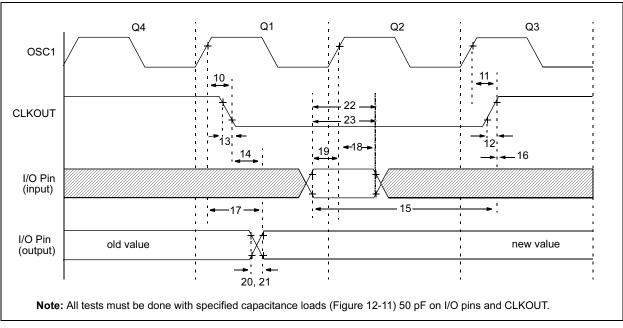

# 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

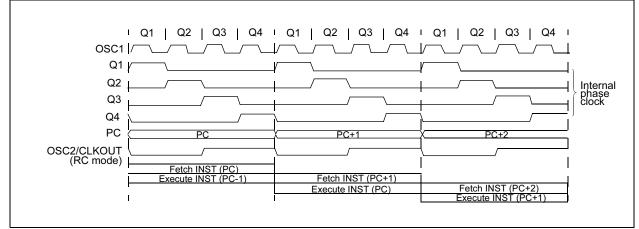

## 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

## 4.2 Data Memory Organization

The data memory (Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7) is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20-7Fh (Bank0) on the PIC16C620A/CR620A/621A and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16C622 and PIC16C622A are General Purpose Registers implemented as static RAM. Some Special Purpose Registers are mapped in Bank 1.

Addresses F0h-FFh of bank1 are implemented as common ram and mapped back to addresses 70h-7Fh in bank0 on the PIC16C620A/621A/622A/CR620A.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 80 x 8 in the PIC16C620/621, 96 x 8 in the PIC16C620A/621A/CR620A and 128 x 8 in the PIC16C622(A). Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

### FIGURE 4-4: DATA MEMORY MAP FOR THE PIC16C620/621

| File     |                     |                     | File        |

|----------|---------------------|---------------------|-------------|

| Address  | 3                   |                     | Address     |

| 00h      | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h         |

| 01h      | TMR0                | OPTION              | 81h         |

| 02h      | PCL                 | PCL                 | 82h         |

| 03h      | STATUS              | STATUS              | 83h         |

| 04h      | FSR                 | FSR                 | 84h         |

| 05h      | PORTA               | TRISA               | 85h         |

| 06h      | PORTB               | TRISB               | 86h         |

| 07h      |                     |                     | 87h         |

| 08h      |                     |                     | 88h         |

| 09h      |                     |                     | 89h         |

| 0Ah      | PCLATH              | PCLATH              | 8Ah         |

| 0Bh      | INTCON              | INTCON              | 8Bh         |

| 0Ch      | PIR1                | PIE1                | 8Ch         |

| 0Dh      |                     |                     | 8Dh         |

| 0Eh      |                     | PCON                | 8Eh         |

| 0Fh      |                     |                     | 8Fh         |

| 10h      |                     |                     | 90h         |

| 11h      |                     |                     | 91h         |

| 12h      |                     |                     | 92h         |

| 13h      |                     |                     | 93h         |

| 14h      |                     |                     | 94h         |

| 15h      |                     |                     | 95h         |

| 16h      |                     |                     | 96h         |

| 17h      |                     |                     | 97h         |

| 18h      |                     |                     | 98h         |

| 19h      |                     |                     | 99h         |

| 1Ah      |                     |                     | 9Ah         |

| 1Bh      |                     |                     | 9Bh         |

| 1Ch      |                     |                     | 9Ch         |

| 1Dh      |                     |                     | 9Dh         |

| 1Eh      |                     |                     | 9Eh         |

| 1Fh      | CMCON               | VRCON               | 9Fh         |

| 20h      |                     | _                   | A0h         |

|          | General             |                     |             |

|          | Purpose<br>Register |                     |             |

| 6Fh      | 5                   |                     |             |

| 70h      |                     |                     |             |

|          |                     |                     |             |

|          |                     |                     |             |

|          |                     |                     |             |

| 7Fh      |                     |                     | FFh         |

|          | Bank 0              | Bank 1              |             |

| <b>—</b> |                     | 1 4                 |             |

| Unimp    | plemented data me   | mory locations, r   | ead as '0'. |

| Note 1:  | Not a physical re   | egister.            |             |

|          |                     |                     |             |

|          |                     |                     |             |

# FIGURE 4-5:

### DATA MEMORY MAP FOR THE PIC16C622

|                 | 1116                |                     |                 |

|-----------------|---------------------|---------------------|-----------------|

| File<br>Address | 8                   |                     | File<br>Address |

| 00h             | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |

| 01h             | TMR0                | OPTION              | 81h             |

| 02h             | PCL                 | PCL                 | 82h             |

| 03h             | STATUS              | STATUS              | 83h             |

| 04h             | FSR                 | FSR                 | 84h             |

| 05h             | PORTA               | TRISA               | 85h             |

| 06h             | PORTB               | TRISB               | 86h             |

| 00h             | TOILID              | TRIOD               | 87h             |

| 07h<br>08h      |                     |                     | 88h             |

| 00h             |                     |                     | 89h             |

| 03h<br>0Ah      | PCLATH              | PCLATH              | 8Ah             |

| 0An<br>0Bh      | INTCON              | INTCON              | 8Bh             |

| 0Dh             | PIR1                | PIE1                | 8Ch             |

| 0Ch<br>0Dh      | PIRI                | PIEI                | 8Dh             |

|                 |                     | PCON                |                 |

| 0Eh<br>0Fh      |                     | PCON                | 8Eh             |

|                 |                     |                     | 8Fh             |

| 10h             |                     |                     | 90h             |

| 11h             |                     |                     | 91h             |

| 12h             |                     |                     | 92h             |

| 13h             |                     |                     | 93h             |

| 14h             |                     |                     | 94h             |

| 15h             |                     |                     | 95h             |

| 16h             |                     |                     | 96h             |

| 17h             |                     |                     | 97h             |

| 18h             |                     |                     | 98h             |

| 19h             |                     |                     | 99h             |

| 1Ah             |                     |                     | 9Ah             |

| 1Bh             |                     |                     | 9Bh             |

| 1Ch             |                     |                     | 9Ch             |

| 1Dh             |                     |                     | 9Dh             |

| 1Eh             |                     |                     | 9Eh             |

| 1Fh             | CMCON               | VRCON               | 9Fh             |

| 20h             |                     |                     | A0h             |

|                 | General<br>Purpose  | General<br>Purpose  |                 |

|                 | Register            | Register            |                 |

|                 | 0                   | 5                   | BFh             |

|                 |                     |                     | C0h             |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

| 7Fh             |                     |                     | FFh             |

| , , , , , ,     | Bank 0              | Bank 1              |                 |

|                 |                     |                     |                 |

| Unim            | plemented data me   | mory locations, re  | ad as '0'.      |

| Note 1:         | Not a physical re   | aister              |                 |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM. The Special Function Registers can be classified into two sets (core and peripheral). The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name          | Bit 7               | Bit 6              | Bit 5       | Bit 4        | Bit 3        | Bit 2        | Bit 1       | Bit 0      | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|---------------|---------------------|--------------------|-------------|--------------|--------------|--------------|-------------|------------|-----------------------|------------------------------------------------|

| Bank 0  |               |                     |                    |             |              |              |              |             |            |                       |                                                |

| 00h     | INDF          | Addressin register) | g this locati      | ion uses co | ntents of FS | SR to addre  | ess data me  | mory (not a | n physical | XXXX XXXX             | XXXX XXXX                                      |

| 01h     | TMR0          | Timer0 Mo           | odule's Reg        | ister       |              |              |              |             |            | xxxx xxxx             | uuuu uuuu                                      |

| 02h     | PCL           | Program 0           | Counter's (F       | PC) Least S | ignificant B | yte          |              |             |            | 0000 0000             | 0000 0000                                      |

| 03h     | STATUS        | IRP <sup>(2)</sup>  | RP1 <sup>(2)</sup> | RP0         | TO           | PD           | Z            | DC          | С          | 0001 1xxx             | 000q quuu                                      |

| 04h     | FSR           | Indirect da         | ata memory         | address po  | ointer       |              |              |             |            | xxxx xxxx             | uuuu uuuu                                      |

| 05h     | PORTA         | —                   | _                  | _           | RA4          | RA3          | RA2          | RA1         | RA0        | x 0000                | u 0000                                         |

| 06h     | PORTB         | RB7                 | RB6                | RB5         | RB4          | RB3          | RB2          | RB1         | RB0        | xxxx xxxx             | uuuu uuuu                                      |

| 07h-09h | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 0Ah     | PCLATH        | _                   | _                  | —           | Write buffe  | er for upper | 5 bits of pr | ogram coui  | nter       | 0 0000                | 0 0000                                         |

| 0Bh     | INTCON        | GIE                 | PEIE               | TOIE        | INTE         | RBIE         | T0IF         | INTF        | RBIF       | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1          | _                   | CMIF               | —           | _            | —            | _            | —           | —          | -0                    | -0                                             |

| 0Dh-1Eh | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 1Fh     | CMCON         | C2OUT               | C1OUT              | —           | _            | CIS          | CM2          | CM1         | CM0        | 00 0000               | 00 0000                                        |

| Bank 1  |               |                     |                    |             |              |              |              |             |            |                       |                                                |

| 80h     | INDF          | Addressin register) | g this locati      | on uses co  | ntents of FS | SR to addre  | ess data me  | mory (not a | ı physical | xxxx xxxx             | xxxx xxxx                                      |

| 81h     | OPTION        | RBPU                | INTEDG             | TOCS        | TOSE         | PSA          | PS2          | PS1         | PS0        | 1111 1111             | 1111 1111                                      |

| 82h     | PCL           | Program 0           | Counter's (F       | PC) Least S | ignificant B | yte          |              |             |            | 0000 0000             | 0000 0000                                      |

| 83h     | STATUS        | IRP <sup>(2)</sup>  | RP1 <sup>(2)</sup> | RP0         | TO           | PD           | Z            | DC          | С          | 0001 1xxx             | 000q quuu                                      |

| 84h     | FSR           | Indirect da         | ata memory         | address po  | ointer       |              |              |             |            | xxxx xxxx             | uuuu uuuu                                      |

| 85h     | TRISA         | —                   | _                  | _           | TRISA4       | TRISA3       | TRISA2       | TRISA1      | TRISA0     | 1 1111                | 1 1111                                         |

| 86h     | TRISB         | TRISB7              | TRISB6             | TRISB5      | TRISB4       | TRISB3       | TRISB2       | TRISB1      | TRISB0     | 1111 1111             | 1111 1111                                      |

| 87h-89h | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 8Ah     | PCLATH        | —                   | _                  | _           | Write buffe  | er for upper | 5 bits of pr | ogram coui  | nter       | 0 0000                | 0 0000                                         |

| 8Bh     | INTCON        | GIE                 | PEIE               | T0IE        | INTE         | RBIE         | T0IF         | INTF        | RBIF       | 0000 000x             | 0000 000u                                      |

| 8Ch     | PIE1          | —                   | CMIE               | —           | —            | —            | —            | —           | —          | -0                    | -0                                             |

| 8Dh     | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 8Eh     | PCON          | —                   |                    | _           |              | _            |              | POR         | BOR        | 0x                    | uq                                             |

| 8Fh-9Eh | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 9Fh     | VRCON         | VREN                | VROE               | VRR         | —            | VR3          | VR2          | VR1         | VR0        | 000- 0000             | 000- 0000                                      |

TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16C62X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown,

${\rm q}$  = value depends on condition, shaded = unimplemented

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

2: IRP & RP1 bits are reserved; always maintain these bits clear.

### 4.2.2.4 PIE1 Register

This register contains the individual enable bit for the comparator interrupt.

| <b>REGISTER 4-4:</b> | PIE1 REGIS                             | PIE1 REGISTER (ADDRESS 8CH)                                                                                                    |          |                           |  |                         |                                |   |  |  |  |  |  |

|----------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------|--|-------------------------|--------------------------------|---|--|--|--|--|--|

|                      | U-0                                    | U-0 R/W-0 U-0 U-0 U-0 U-0 U-0 U-0                                                                                              |          |                           |  |                         |                                |   |  |  |  |  |  |

|                      |                                        | CMIE                                                                                                                           | _        |                           |  | —                       | _                              | — |  |  |  |  |  |

|                      | bit 7 bit 0                            |                                                                                                                                |          |                           |  |                         |                                |   |  |  |  |  |  |

| bit 7                | Unimpleme                              | Jnimplemented: Read as '0'                                                                                                     |          |                           |  |                         |                                |   |  |  |  |  |  |

| bit 6                | 1 = Enables                            | <b>CMIE</b> : Comparator Interrupt Enable bit<br>1 = Enables the Comparator interrupt<br>0 = Disables the Comparator interrupt |          |                           |  |                         |                                |   |  |  |  |  |  |

| bit 5-0              | Unimpleme                              | nted: Read                                                                                                                     | d as '0' |                           |  |                         |                                |   |  |  |  |  |  |

|                      | Legend:<br>R = Readab<br>- n = Value a |                                                                                                                                |          | /ritable bit<br>it is set |  | nplemented<br>s cleared | bit, read as '<br>x = Bit is u |   |  |  |  |  |  |

## 4.2.2.5 PIR1 Register

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of |  |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User               |  |  |  |  |  |  |  |

|       | software should ensure the appropriate                                                     |  |  |  |  |  |  |  |

|       | interrupt flag bits are clear prior to enabling                                            |  |  |  |  |  |  |  |

|       | an interrupt.                                                                              |  |  |  |  |  |  |  |

## REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

| ER 4-5: | PIRT REGI                           | SIER (AL      | DRESS 0      | СН)          |              |           |                |        |  |  |  |  |  |

|---------|-------------------------------------|---------------|--------------|--------------|--------------|-----------|----------------|--------|--|--|--|--|--|

|         | U-0                                 | R/W-0         | U-0          | U-0          | U-0          | U-0       | U-0            | U-0    |  |  |  |  |  |

|         |                                     | CMIF          |              | —            | _            |           |                |        |  |  |  |  |  |

|         | bit 7                               |               |              |              |              |           |                | bit 0  |  |  |  |  |  |

|         |                                     |               |              |              |              |           |                |        |  |  |  |  |  |

| bit 7   | Unimpleme                           | ented: Rea    | d as '0'     |              |              |           |                |        |  |  |  |  |  |

| bit 6   | CMIF: Comparator Interrupt Flag bit |               |              |              |              |           |                |        |  |  |  |  |  |

|         | 1 = Comparator input has changed    |               |              |              |              |           |                |        |  |  |  |  |  |

|         | 0 = Compai                          | rator input h | nas not chan | iged         |              |           |                |        |  |  |  |  |  |

| bit 5-0 | Unimpleme                           | ented: Rea    | d as '0'     |              |              |           |                |        |  |  |  |  |  |

|         |                                     |               |              |              |              |           |                |        |  |  |  |  |  |

|         | Legend:                             |               |              |              |              |           |                |        |  |  |  |  |  |

|         | R = Readab                          | ole bit       | W = W        | /ritable bit | U = Unim     | plemented | bit, read as ' | 0'     |  |  |  |  |  |

|         | - n = Value                         | at POR        | '1' = B      | it is set    | '0' = Bit is | s cleared | x = Bit is u   | nknown |  |  |  |  |  |

# 9.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16C62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-Circuit Serial Programming™

The PIC16C62X devices have a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

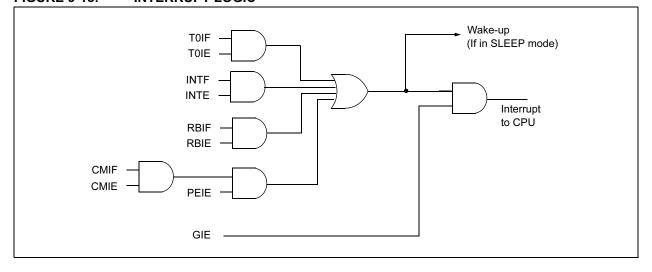

## 9.5 Interrupts

The PIC16C62X has 4 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB<7:4>)

- · Comparator interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which reenable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h.

FIGURE 9-15: INTERRUPT LOGIC

Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/ INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 9-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

## 11.9 MPLAB ICE 2000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 2000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers. Software control of the MPLAB ICE 2000 in-circuit emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PICmicro microcontrollers.

The MPLAB ICE 2000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

## 11.10 MPLAB ICE 4000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 4000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for highend PICmicro microcontrollers. Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICD 4000 is a premium emulator system, providing the features of MPLAB ICE 2000, but with increased emulation memory and high speed performance for dsPIC30F and PIC18XXXX devices. Its advanced emulator features include complex triggering and timing, up to 2 Mb of emulation memory, and the ability to view variables in real-time.

The MPLAB ICE 4000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

# 11.11 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low cost, run-time development tool, connecting to the host PC via an RS-232 or high speed USB interface. This tool is based on the FLASH PICmicro MCUs and can be used to develop for these and other PICmicro microcontrollers. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers cost effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single-stepping and watching variables, CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real-time. MPLAB ICD 2 also serves as a development programmer for selected PICmicro devices.

## 11.12 PRO MATE II Universal Device Programmer

The PRO MATE II is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features an LCD display for instructions and error messages and a modular detachable socket assembly to support various package types. In Stand-Alone mode, the PRO MATE II device programmer can read, verify, and program PICmicro devices without a PC connection. It can also set code protection in this mode.

## 11.13 PICSTART Plus Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus development programmer supports most PICmicro devices up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

## 11.14 PICDEM 1 PICmicro Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include analog input, push button switches and eight LEDs.

## 11.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham

## 11.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessary hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 FLASH microcontrollers.

## 11.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

## 11.18 PICDEM 4 8/14/18-Pin Demonstration Board

The PICDEM 4 can be used to demonstrate the capabilities of the 8-, 14-, and 18-pin PIC16XXXX and PIC18XXXX MCUs, including the PIC16F818/819, PIC16F87/88, PIC16F62XA and the PIC18F1320 family of microcontrollers. PICDEM 4 is intended to showcase the many features of these low pin count parts, including LIN and Motor Control using ECCP. Special provisions are made for low power operation with the supercapacitor circuit, and jumpers allow onboard hardware to be disabled to eliminate current draw in this mode. Included on the demo board are provisions for Crystal, RC or Canned Oscillator modes, a five volt regulator for use with a nine volt wall adapter or battery, DB-9 RS-232 interface, ICD connector for programming via ICSP and development with MPLAB ICD 2, 2x16 liquid crystal display, PCB footprints for H-Bridge motor driver, LIN transceiver and EEPROM. Also included are: header for expansion, eight LEDs, four potentiometers, three push buttons and a prototyping area. Included with the kit is a PIC16F627A and a PIC18F1320. Tutorial firmware is included along with the User's Guide.

# 11.19 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board FLASH memory. A generous prototype area is available for user hardware expansion.

## 11.20 PICDEM 18R PIC18C601/801 Demonstration Board

The PICDEM 18R demonstration board serves to assist development of the PIC18C601/801 family of Microchip microcontrollers. It provides hardware implementation of both 8-bit Multiplexed/De-multiplexed and 16-bit Memory modes. The board includes 2 Mb external FLASH memory and 128 Kb SRAM memory, as well as serial EEPROM, allowing access to the wide range of memory types supported by the PIC18C601/801.

## 11.21 PICDEM LIN PIC16C43X Demonstration Board

The powerful LIN hardware and software kit includes a series of boards and three PICmicro microcontrollers. The small footprint PIC16C432 and PIC16C433 are used as slaves in the LIN communication and feature on-board LIN transceivers. A PIC16F874 FLASH microcontroller serves as the master. All three micro-controllers are programmed with firmware to provide LIN bus communication.

# 11.22 PICkit<sup>™</sup> 1 FLASH Starter Kit

A complete "development system in a box", the PICkit FLASH Starter Kit includes a convenient multi-section board for programming, evaluation, and development of 8/14-pin FLASH PIC<sup>®</sup> microcontrollers. Powered via USB, the board operates under a simple Windows GUI. The PICkit 1 Starter Kit includes the user's guide (on CD ROM), PICkit 1 tutorial software and code for various applications. Also included are MPLAB<sup>®</sup> IDE (Integrated Development Environment) software, software and hardware "Tips 'n Tricks for 8-pin FLASH PIC<sup>®</sup> Microcontrollers" Handbook and a USB Interface Cable. Supports all current 8/14-pin FLASH PIC microcontrollers, as well as many future planned devices.

# 11.23 PICDEM USB PIC16C7X5 Demonstration Board

The PICDEM USB Demonstration Board shows off the capabilities of the PIC16C745 and PIC16C765 USB microcontrollers. This board provides the basis for future USB products.

## 11.24 Evaluation and Programming Tools

In addition to the PICDEM series of circuits, Microchip has a line of evaluation kits and demonstration software for these products.

- KEELOQ evaluation and programming tools for Microchip's HCS Secure Data Products

- CAN developers kit for automotive network applications

- Analog design boards and filter design software

- PowerSmart battery charging evaluation/ calibration kits

- IrDA<sup>®</sup> development kit

- microID development and rfLab<sup>™</sup> development software

- SEEVAL<sup>®</sup> designer kit for memory evaluation and endurance calculations

- PICDEM MSC demo boards for Switching mode power supply, high power IR driver, delta sigma ADC, and flow rate sensor

Check the Microchip web page and the latest Product Line Card for the complete list of demonstration and evaluation kits.

# PIC16C62X

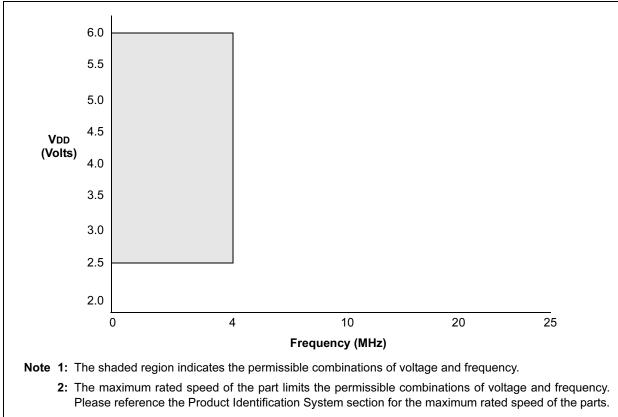

**2**: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

## 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended)

| $\begin{array}{c} 0^{\circ}C &\leq TA \leq +70^{\circ}C \text{ for col}\\ -40^{\circ}C &\leq TA \leq +125^{\circ}C \text{ for expansion}\\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dustrial and mmercial and                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\begin{array}{rll} \mbox{Operating temperature} & -40^\circ C & \leq TA \leq +85^\circ C \mbox{ for industrial and} \\ & 0^\circ C & \leq TA \leq +70^\circ C \mbox{ for commercial and} \\ & -40^\circ C & \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |  |  |  |  |  |  |

| $\begin{array}{c} \mbox{PIC16LC62X} \\ \mbox{PIC16LC62X} \\ \mbox{Operating temperature} & -40^{\circ} C & \leq TA \leq +85^{\circ} C \mbox{ for ind} \\ & 0^{\circ} C & \leq TA \leq +70^{\circ} C \mbox{ for out} \\ & -40^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & \leq TA \leq +125^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & = 0^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & = 0^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & = 0^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C & = 0^{\circ} C \mbox{ for expansion} \\ & 0^{\circ} C \mbo$ | dustrial and<br>mmercial and<br>extended                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Param.         Sym         Characteristic         Min         Typ†         Max         Units         Conditio           No.                Conditio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

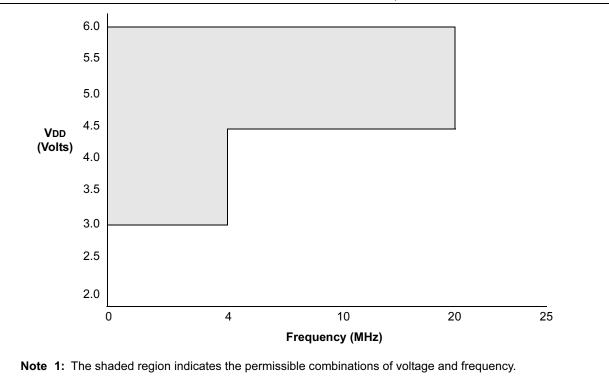

| D001         VDD         Supply Voltage         3.0         —         6.0         V         See Figures 12-1, 12-2, 12-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3, 12-4, and 12-5                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| D001         VDD         Supply Voltage         2.5         —         6.0         V         See Figures 12-1, 12-2, 12-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3, 12-4, and 12-5                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| D002 VDR RAM Data Retention Voltage <sup>(1)</sup> — 1.5* — V Device in SLEEP mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| D002 VDR RAM Data Retention Voltage <sup>(1)</sup> — 1.5* — V Device in SLEEP mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |