Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 20MHz                                                                        |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c622at-20e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART, PRO MATE and PowerSmart are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Accuron, Application Maestro, dsPIC, dsPICDEM, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICkit, PICDEM, PICDEM.net, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPIC, Select Mode, SmartSensor, SmartShunt, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

# **PIC16C62X**

### **EPROM-Based 8-Bit CMOS Microcontrollers**

#### Devices included in this data sheet:

Referred to collectively as PIC16C62X.

- PIC16C620 PIC16C620A

- PIC16C621 PIC16C621A

- PIC16C622 PIC16C622A

- PIC16CR620A

#### **High Performance RISC CPU:**

- Only 35 instructions to learn

- All single cycle instructions (200 ns), except for program branches which are two-cycle

- Operating speed:

- DC 40 MHz clock input

- DC 100 ns instruction cycle

| Device      | Program<br>Memory | Data<br>Memory |

|-------------|-------------------|----------------|

| PIC16C620   | 512               | 80             |

| PIC16C620A  | 512               | 96             |

| PIC16CR620A | 512               | 96             |

| PIC16C621   | 1K                | 80             |

| PIC16C621A  | 1K                | 96             |

| PIC16C622   | 2K                | 128            |

| PIC16C622A  | 2K                | 128            |

· Interrupt capability

- 16 special function hardware registers

- 8-level deep hardware stack

- Direct, Indirect and Relative addressing modes

#### **Peripheral Features:**

- 13 I/O pins with individual direction control

- High current sink/source for direct LED drive

- Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VREF) module

- Programmable input multiplexing from device inputs and internal voltage reference

- Comparator outputs can be output signals

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

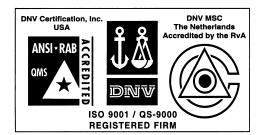

#### Pin Diagrams

#### PDIP, SOIC, Windowed CERDIP

#### **Special Microcontroller Features:**

- · Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- · Programmable code protection

- · Power saving SLEEP mode

- Selectable oscillator options

- Serial in-circuit programming (via two pins)

- Four user programmable ID locations

#### **CMOS Technology:**

- Low power, high speed CMOS EPROM technology

- Fully static design

- · Wide operating range

- 2.5V to 5.5V

- Commercial, industrial and extended temperature range

- Low power consumption

- < 2.0 mA @ 5.0V, 4.0 MHz

- 15 μA typical @ 3.0V, 32 kHz

- < 1.0 μA typical standby current @ 3.0V

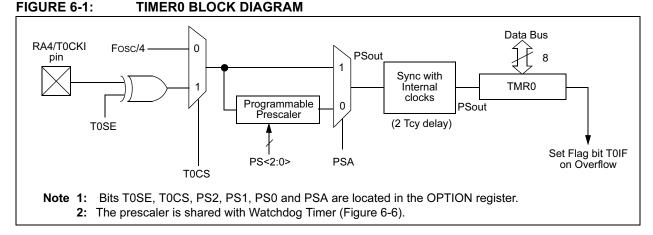

#### 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- · Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

#### 6.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP, since the timer is shut off during SLEEP. See Figure 6-4 for Timer0 interrupt timing.

#### FIGURE 6-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

| (Program<br>Counter) | ( PC-1      | ) PC        | ( <u>PC+1</u> )        | PC+2                   | <u>PC+3</u> χ          | PC+4                   | PC+5 χ                     | PC+6                     |

|----------------------|-------------|-------------|------------------------|------------------------|------------------------|------------------------|----------------------------|--------------------------|

| Instruction<br>Fetch |             | MOVWF TMR   | 0MOVF TMR0,V           | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W                | 1                        |

|                      | i.          | 1           |                        |                        | i                      |                        | i                          |                          |

| TMR0                 | то х        | T0+1 )(     | T0+2 X                 | 1                      | NT0                    |                        | NT0+1 \                    | NT0+2 )                  |

| Instruction          | 1<br>1<br>1 | 1<br>1<br>1 | <b></b>                | <b>≜</b>               | <b>≜</b>               | <b>†</b>               | <b>†</b>                   | <b>≜</b>                 |

| Executed             | 1           | 1           | Write TMR0<br>executed | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1 | Read TMR0<br>reads NT0 + |

#### 6.2 Using Timer0 with External Clock

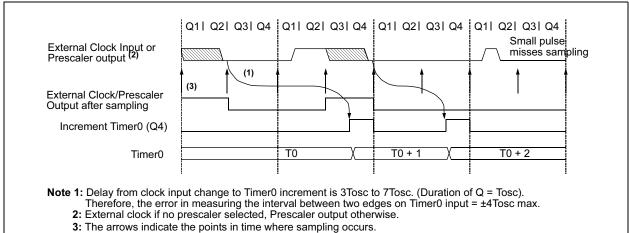

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

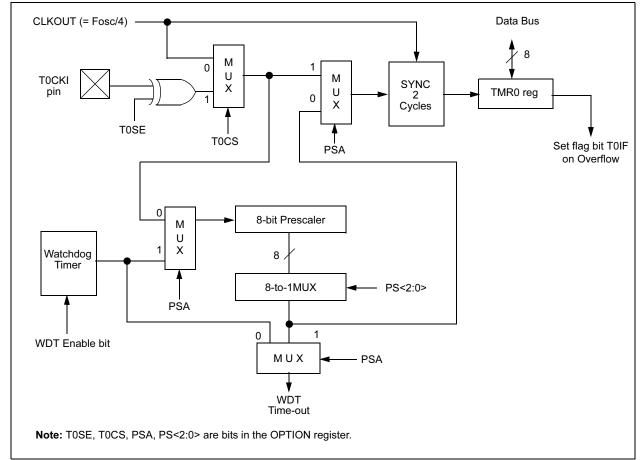

#### 6.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 6-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

#### FIGURE 6-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to WDT.)

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

|          |              | ,                                             |

|----------|--------------|-----------------------------------------------|

| 1.BCF    | STATUS, RPO  | ;Skip if already in<br>;Bank 0                |

| 2.CLRWDT |              | ;Clear WDT                                    |

| 3.CLRF   | TMR0         | ;Clear TMR0 & Prescaler                       |

| 4.BSF    | STATUS, RPO  | ;Bank 1                                       |

| 5.MOVLW  | '00101111'b; | ;These 3 lines (5, 6, 7)                      |

| 6.MOVWF  | OPTION       | ;are required only if<br>;desired PS<2:0> are |

| 7.CLRWDT |              | ;000 or 001                                   |

| 8.MOVLW  | '00101xxx'b  | ;Set Postscaler to                            |

| 9.MOVWF  | OPTION       | ;desired WDT rate                             |

| 10.BCF   | STATUS, RPO  | ;Return to Bank 0                             |

|          |              |                                               |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 6-2. This precaution must be taken even if the WDT is disabled.

#### EXAMPLE 6-2:

#### CHANGING PRESCALER (WDT→TIMER0)

|        | •           | ,                                        |

|--------|-------------|------------------------------------------|

| CLRWDT |             | ;Clear WDT and                           |

|        |             | ;prescaler                               |

| BSF    | STATUS, RPO |                                          |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new<br>;prescale value and |

|        |             | ;clock source                            |

| MOVWF  | OPTION REG  |                                          |

| BCF    | STATUS, RPO |                                          |

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6       | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|----------|-------------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 r | nodule regi | ster  |        |        |        |        |        | XXXX XXXX       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE      | PEIE        | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | RBPU     | INTEDG      | TOCS  | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _        |             | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

**Note:** Shaded bits are not used by TMR0 module.

# 9.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16C62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-Circuit Serial Programming™

The PIC16C62X devices have a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

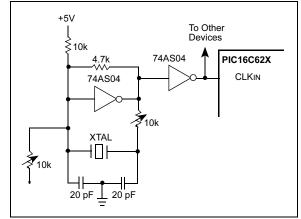

#### 9.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance or one with parallel resonance.

Figure 9-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 9-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

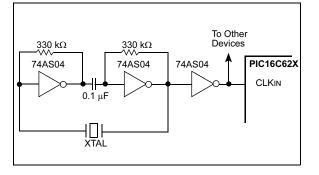

Figure 9-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a  $180^{\circ}$  phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 9-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

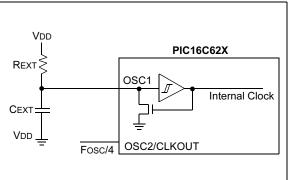

#### 9.2.4 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 9-5 shows how the R/C combination is connected to the PIC16C62X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See Section 13.0 for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See Section 13.0 for variation of oscillator frequency due to VDD for given REXT/CEXT values, as well as frequency variation due to operating temperature for given R, C and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

#### FIGURE 9-5: RC OSCILLATOR MODE

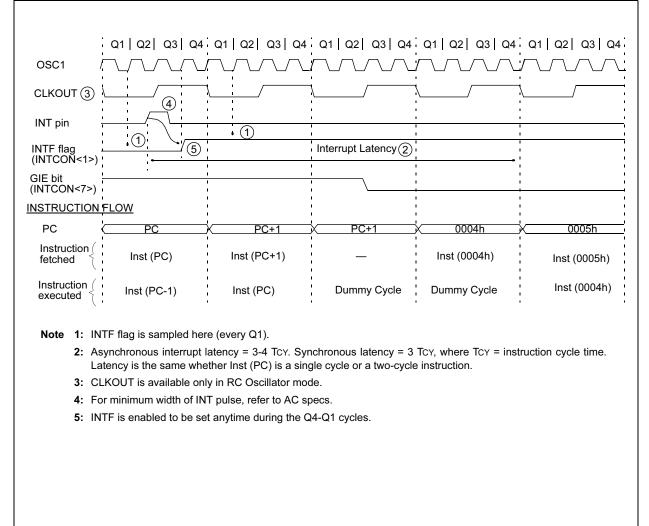

#### 9.5.1 RB0/INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered, either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP and Figure 9-18 for timing of wakeup from SLEEP through RB0/INT interrupt.

#### 9.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 6.0.

#### 9.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

| Note: | If a change on the I/O pin should occur   |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|

|       | when the read operation is being executed |  |  |  |  |

|       | (start of the Q2 cycle), then the RBIF    |  |  |  |  |

|       | interrupt flag may not get set.           |  |  |  |  |

#### 9.5.4 COMPARATOR INTERRUPT

See Section 7.6 for complete description of comparator interrupts.

#### FIGURE 9-16: INT PIN INTERRUPT TIMING

#### 9.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs with no external circuitry drawing current from the I/O pin and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated      |

|-------|------------------------------------------------|

|       | by a WDT time-out does not drive MCLR pin low. |

|       |                                                |

#### 9.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device RESET. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. PD bit, which is set on power-up, is cleared when SLEEP is invoked. TO bit is cleared if WDT wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction after the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

**Note:** If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from SLEEP. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes up from SLEEP, regardless of the source of wake-up.

| Q1 Q2 Q                  | 3 Q4 Q1 Q2 Q3 Q4 Q | Q1                    | Q1 Q2 Q3 Q4      | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 0    | Q1 Q2 Q3 Q4 |

|--------------------------|--------------------|-----------------------|------------------|-------------|------------------|-------------|

| OSC1 //////              |                    | AAAAA                 |                  |             |                  |             |

| CLKOUT(4)                |                    | Tost(2)               | <u> </u>         |             | \ <u>`</u>       |             |

| INT pin                  | 1 I                |                       | 1<br>1           |             | 1                |             |

| NTF flag                 |                    |                       | Interrupt Latend | SV.         |                  |             |

| INTCON<1>)               |                    | <del>≉</del>          | (Note 2)         | ,           |                  |             |

| GIE bit<br>INTCON<7>)    |                    | Processor in<br>SLEEP | 1                |             |                  |             |

| INSTRUCTION FLOW         |                    |                       | 1<br>1<br>1      |             | 1                |             |

| PC X PC                  | <u>Υ PC+1 Χ</u>    | PC+2                  | X PC+2           | PC + 2      | <u>χ 0004h χ</u> | 0005h       |

| Instruction { Inst(PC) = | SLEEP Inst(PC + 1) |                       | Inst(PC + 2)     |             | Inst(0004h)      | Inst(0005h) |

| Instruction Inst(PC      | - 1) SLEEP         |                       | Inst(PC + 1)     | Dummy cycle | Dummy cycle      | Inst(0004h) |

#### FIGURE 9-18: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**3:** GIE = '1' assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these Osc modes, but shown here for timing reference.

#### 11.9 MPLAB ICE 2000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 2000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers. Software control of the MPLAB ICE 2000 in-circuit emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PICmicro microcontrollers.

The MPLAB ICE 2000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

#### 11.10 MPLAB ICE 4000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 4000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for highend PICmicro microcontrollers. Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICD 4000 is a premium emulator system, providing the features of MPLAB ICE 2000, but with increased emulation memory and high speed performance for dsPIC30F and PIC18XXXX devices. Its advanced emulator features include complex triggering and timing, up to 2 Mb of emulation memory, and the ability to view variables in real-time.

The MPLAB ICE 4000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

#### 11.11 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low cost, run-time development tool, connecting to the host PC via an RS-232 or high speed USB interface. This tool is based on the FLASH PICmicro MCUs and can be used to develop for these and other PICmicro microcontrollers. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers cost effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single-stepping and watching variables, CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real-time. MPLAB ICD 2 also serves as a development programmer for selected PICmicro devices.

#### 11.12 PRO MATE II Universal Device Programmer

The PRO MATE II is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features an LCD display for instructions and error messages and a modular detachable socket assembly to support various package types. In Stand-Alone mode, the PRO MATE II device programmer can read, verify, and program PICmicro devices without a PC connection. It can also set code protection in this mode.

#### 11.13 PICSTART Plus Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus development programmer supports most PICmicro devices up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

#### 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended) (CONT.)

|                                                                   |                                                                   |                                                                                                                                                                                                                                                                        | Stand            | dard O                             | perati                                            | ng Con                                 | ditions (unless otherwise stated)                                                                                                                                                                                                                 |

|-------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------|---------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIC16C                                                            | 62X                                                               |                                                                                                                                                                                                                                                                        | Opera            | ating te                           | empera                                            |                                        | $\begin{array}{ll} 0^{\circ}C & \leq TA \leq +85^{\circ}C \text{ for industrial and} \\ 0^{\circ}C & \leq TA \leq +70^{\circ}C \text{ for commercial and} \\ 0^{\circ}C & \leq TA \leq +125^{\circ}C \text{ for extended} \end{array}$            |

|                                                                   | PIC16LC62X Param Sym Characteristic                               |                                                                                                                                                                                                                                                                        |                  |                                    | empera                                            | ture -4<br>-4<br>VDD ran               | ditions (unless otherwise stated)<br>$0^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and<br>$0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial and<br>$0^{\circ}C \leq TA \leq +125^{\circ}C$ for extended<br>ge is the PIC16C62X range. |

| Param<br>. No.                                                    | Sym                                                               | Characteristic                                                                                                                                                                                                                                                         | Min              | Тур†                               | Мах                                               | Units                                  | Conditions                                                                                                                                                                                                                                        |

| D022<br>D022A<br>D023<br>D023A<br>D022A<br>D022A<br>D022A<br>D023 | ΔIWDT<br>ΔIBOR<br>ΔICOM<br>P<br>ΔIVREF<br>ΔIWDT<br>ΔIBOR<br>ΔICOM | WDT Current <sup>(5)</sup><br>Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each<br>Comparator <sup>(5)</sup><br>VREF Current <sup>(5)</sup><br>WDT Current <sup>(5)</sup><br>Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each |                  | 6.0<br>350<br>—<br>6.0<br>350<br>— | 20<br>25<br>425<br>100<br>300<br>15<br>425<br>100 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | VDD=4.0V $(125°C)$ $BOD enabled, VDD = 5.0V$ $VDD = 4.0V$ $VDD = 4.0V$ $VDD = 3.0V$ $BOD enabled, VDD = 5.0V$ $VDD = 3.0V$                                                                                                                        |

| D023A                                                             | P<br>∆IVREF                                                       | Comparator <sup>(5)</sup><br>VREF Current <sup>(5)</sup>                                                                                                                                                                                                               | —                | —                                  | 300                                               | μA                                     | VDD = 3.0V                                                                                                                                                                                                                                        |

| 1A                                                                | Fosc                                                              | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency                                                                                                                       | 0<br>0<br>0<br>0 | <br> <br>                          | 200<br>4<br>4<br>20                               | kHz<br>MHz<br>MHz<br>MHz               | All temperatures<br>All temperatures<br>All temperatures<br>All temperatures                                                                                                                                                                      |

| 1A                                                                | Fosc                                                              | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency                                                                                                                       | 0<br>0<br>0<br>0 |                                    | 200<br>4<br>4<br>20                               | kHz<br>MHz<br>MHz<br>MHz               | All temperatures<br>All temperatures<br>All temperatures<br>All temperatures                                                                                                                                                                      |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in kΩ.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

#### 12.3 DC CHARACTERISTICS: PIC16CR62XA-04 (Commercial, Industrial, Extended) PIC16CR62XA-20 (Commercial, Industrial, Extended) PIC16LCR62XA-04 (Commercial, Industrial, Extended)

| PIC16CR62XA-04<br>PIC16CR62XA-20 |       |                                               |       | $\begin{array}{l lllllllllllllllllllllllllllllllllll$ |            |          |                                                                                                                   |  |  |  |  |

|----------------------------------|-------|-----------------------------------------------|-------|-------------------------------------------------------|------------|----------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIC16L0                          | CR62X | <b>Q-04</b>                                   |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$  |            |          |                                                                                                                   |  |  |  |  |

| Param.<br>No.                    | Sym   | Characteristic                                | Min   | Тур†                                                  | Мах        | Units    | Conditions                                                                                                        |  |  |  |  |

| D001                             | Vdd   | Supply Voltage                                | 3.0   | —                                                     | 5.5        | V        | See Figures 12-7, 12-8, 12-9                                                                                      |  |  |  |  |

| D001                             | Vdd   | Supply Voltage                                | 2.5   | _                                                     | 5.5        | V        | See Figures 12-7, 12-8, 12-9                                                                                      |  |  |  |  |

| D002                             | Vdr   | RAM Data Retention<br>Voltage <sup>(1)</sup>  |       | 1.5*                                                  |            | V        | Device in SLEEP mode                                                                                              |  |  |  |  |

| D002                             | Vdr   | RAM Data Retention<br>Voltage <sup>(1)</sup>  | _     | 1.5*                                                  | —          | V        | Device in SLEEP mode                                                                                              |  |  |  |  |

| D003                             | VPOR  | VDD start voltage to<br>ensure Power-on Reset |       | Vss                                                   | _          | V        | See section on Power-on Reset for details                                                                         |  |  |  |  |

| D003                             | VPOR  | VDD start voltage to<br>ensure Power-on Reset | —     | Vss                                                   | —          | V        | See section on Power-on Reset for details                                                                         |  |  |  |  |

| D004                             | SVDD  | VDD rise rate to ensure<br>Power-on Reset     | 0.05* | —                                                     | —          | V/ms     | See section on Power-on Reset for details                                                                         |  |  |  |  |

| D004                             | SVDD  | VDD rise rate to ensure<br>Power-on Reset     | 0.05* | —                                                     | —          | V/ms     | See section on Power-on Reset for details                                                                         |  |  |  |  |

| D005                             | VBOR  | Brown-out Detect Voltage                      | 3.7   | 4.0                                                   | 4.35       | V        | BOREN configuration bit is cleared                                                                                |  |  |  |  |

| D005                             | VBOR  | Brown-out Detect Voltage                      | 3.7   | 4.0                                                   | 4.35       | V        | BOREN configuration bit is cleared                                                                                |  |  |  |  |

| D010                             | Idd   | Supply Current <sup>(2)</sup>                 | _     | 1.2<br>500                                            | 1.7<br>900 | mA<br>μA | Fosc = 4 MHz, VDD = 5.5V, WDT disabled, XT mode,<br>(Note 4)*<br>Fosc = 4 MHz, VDD = 3.0V, WDT disabled, XT mode, |  |  |  |  |

|                                  |       |                                               | _     | 1.0                                                   | 2.0        | mA       | (Note 4)<br>Fosc = 10 MHz, VDD = 3.0V, WDT disabled, HS mode,<br>(Note 6)                                         |  |  |  |  |

|                                  |       |                                               | —     | 4.0                                                   | 7.0        | mA       | Fosc = 20 MHz, VDD = 5.5V, WDT disabled*, HS                                                                      |  |  |  |  |

|                                  |       |                                               | —     | 3.0                                                   | 6.0        | mA       | mode                                                                                                              |  |  |  |  |

|                                  |       |                                               |       | 35                                                    | 70         | μA       | Fosc = 20 MHz, VDD = 4.5V, WDT disabled, HS mode<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled, LP mode              |  |  |  |  |

| D010                             | IDD   | Supply Current <sup>(2)</sup>                 | —     | 1.2                                                   | 1.7        | mA       | Fosc = 4.0 MHz, VDD = 5.5V, WDT disabled, XT<br>mode, ( <b>Note 4</b> )*                                          |  |  |  |  |

|                                  |       |                                               | —     | 400                                                   | 800        | μA       | Fosc = 4.0 MHz, VDD = 2.5V, WDT disabled, XT mode (Note 4)                                                        |  |  |  |  |

|                                  |       |                                               | —     | 35                                                    | 70         | μA       | Fosc = 32 kHz, VDD = 2.5V, WDT disabled, LP mode                                                                  |  |  |  |  |

| PIC16CR62XA-04<br>PIC16CR62XA-20 | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                |  |  |  |  |  |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| PIC16LCR62XA-04                  | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq$ TA $\leq$ +85°C for industrial and $0^{\circ}$ C $\leq$ TA $\leq$ +70°C for commercial and $-40^{\circ}$ C $\leq$ TA $\leq$ +125°C for extended |  |  |  |  |  |  |

| Param. Sym Characteristic No.    | Min Typ† Max Units Conditions                                                                                                                                                                                                                       |  |  |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula: Ir = VDD/2REXT (mA) with REXT in k $\Omega$ .

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

### 12.6 DC Characteristics:

### PIC16C620A/C621A/C622A-40<sup>(3)</sup> (Commercial) PIC16CR620A-40<sup>(3)</sup> (Commercial)

| DC CHARACTERISTICS<br>Power Supply Pins |      |        |                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |          |                                                                          |  |  |

|-----------------------------------------|------|--------|--------------------|------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------|--|--|

| Characteristic                          | Sym  | Min    | Typ <sup>(1)</sup> | Мах                                                                                                                                | Units    | Conditions                                                               |  |  |

| Supply Voltage                          | Vdd  | 4.5    | —                  | 5.5                                                                                                                                | V        | HS Option from 20 - 40 MHz                                               |  |  |

| Supply Current <sup>(2)</sup>           | IDD  | _      | 5.5<br>7.7         | 11.5<br>16                                                                                                                         | mA<br>mA | Fosc = 40 MHz, VDD = 4.5V, HS mode<br>Fosc = 40 MHz, VDD = 5.5V, HS mode |  |  |

| HS Oscillator Operating<br>Frequency    | Fosc | 20     | _                  | 40                                                                                                                                 | MHz      | OSC1 pin is externally driven,<br>OSC2 pin not connected                 |  |  |

| Input Low Voltage OSC1                  | VIL  | Vss    | —                  | 0.2Vdd                                                                                                                             | V        | HS mode, OSC1 externally driven                                          |  |  |

| Input High Voltage OSC1                 | Vih  | 0.8Vdd |                    | Vdd                                                                                                                                | V        | HS mode, OSC1 externally driven                                          |  |  |

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss,

T0CKI = VDD,  $\overline{MCLR}$  = VDD; WDT disabled, HS mode with OSC2 not connected.

**3:** For device operation between DC and 20 MHz. See Table 12-1 and Table 12-2.

# 12.7 AC Characteristics: PIC16C620A/C621A/C622A-40<sup>(2)</sup> (Commercial) PIC16CR620A-40<sup>(2)</sup> (Commercial)

| AC CHARACTERISTICS<br>All Pins Except Power Supply Pir       | IS         |                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |       |            |                                      |  |

|--------------------------------------------------------------|------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|------------|--------------------------------------|--|

| Characteristic                                               | Min        | Тур <sup>(1)</sup> | Max                                                                                                                                | Units | Conditions |                                      |  |

| External CLKIN Frequency                                     | Fosc       | 20                 | —                                                                                                                                  | 40    | MHz        | HS mode, OSC1 externally driven      |  |

| External CLKIN Period                                        | Tosc       | 25                 | _                                                                                                                                  | 50    | ns         | HS mode (40), OSC1 externally driven |  |

| Clock in (OSC1) Low or High Time                             | TosL, TosH | 6                  | —                                                                                                                                  |       | ns         | HS mode, OSC1 externally driven      |  |

| Clock in (OSC1) Rise or Fall Time                            | TosR, TosF |                    | _                                                                                                                                  | 6.5   | ns         | HS mode, OSC1 externally driven      |  |

| OSC1↑ (Q1 cycle) to Port out valid                           | TosH2ıoV   |                    | —                                                                                                                                  | 100   | ns         | _                                    |  |

| OSC1↑ (Q2 cycle) to Port input<br>invalid (I/O in hold time) | TosH2iol   | 50                 | —                                                                                                                                  | _     | ns         | —                                    |  |

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: For device operation between DC and 20 MHz. See Table 12-1 and Table 12-2.

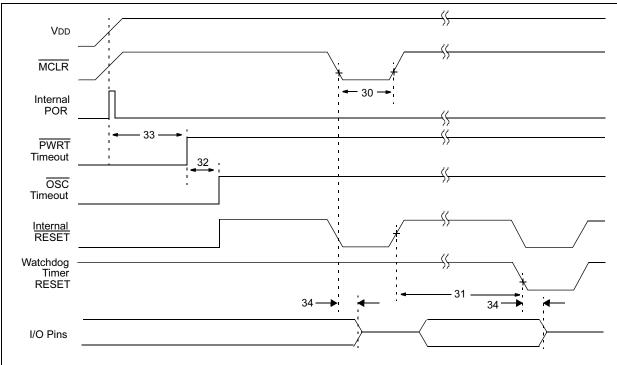

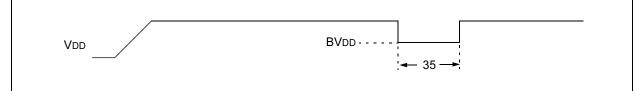

### FIGURE 12-14: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

#### FIGURE 12-15: BROWN-OUT RESET TIMING

### TABLE 12-5:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                | Min  | Тур†      | Max  | Units | Conditions                       |

|------------------|-------|-----------------------------------------------|------|-----------|------|-------|----------------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                        | 2000 | —         | _    | ns    | -40° to +85°C                    |

| 31               | Twdt  | Watchdog Timer Time-out Period (No Prescaler) | 7*   | 18        | 33*  | ms    | VDD = 5.0V, -40° to +85°C        |

| 32               | Tost  | Oscillation Start-up Timer Period             | _    | 1024 Tosc | _    |       | Tosc = OSC1 period               |

| 33               | Tpwrt | Power-up Timer Period                         | 28*  | 72        | 132* | ms    | VDD = 5.0V, -40° to +85°C        |

| 34               | Tioz  | I/O hi-impedance from MCLR low                |      | —         | 2.0  | μS    |                                  |

| 35               | TBOR  | Brown-out Reset Pulse Width                   | 100* | _         |      | μS    | $3.7V \leq V\text{DD} \leq 4.3V$ |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

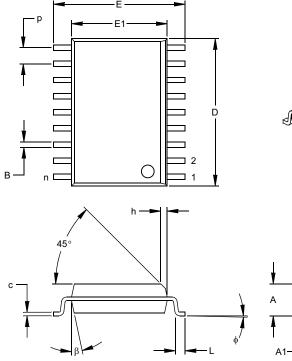

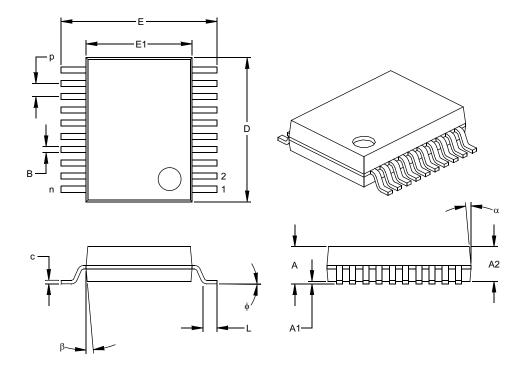

#### 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

|                          |        | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|--------|---------|------|-------------|-------|-------|-------|

| Dimension                | Limits | MIN     | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins           | n      |         | 18   |             |       | 18    |       |

| Pitch                    | р      |         | .050 |             |       | 1.27  |       |

| Overall Height           | Α      | .093    | .099 | .104        | 2.36  | 2.50  | 2.64  |

| Molded Package Thickness | A2     | .088    | .091 | .094        | 2.24  | 2.31  | 2.39  |

| Standoff §               | A1     | .004    | .008 | .012        | 0.10  | 0.20  | 0.30  |

| Overall Width            | Е      | .394    | .407 | .420        | 10.01 | 10.34 | 10.67 |

| Molded Package Width     | E1     | .291    | .295 | .299        | 7.39  | 7.49  | 7.59  |

| Overall Length           | D      | .446    | .454 | .462        | 11.33 | 11.53 | 11.73 |

| Chamfer Distance         | h      | .010    | .020 | .029        | 0.25  | 0.50  | 0.74  |

| Foot Length              | L      | .016    | .033 | .050        | 0.41  | 0.84  | 1.27  |

| Foot Angle               | ¢      | 0       | 4    | 8           | 0     | 4     | 8     |

| Lead Thickness           | С      | .009    | .011 | .012        | 0.23  | 0.27  | 0.30  |

| Lead Width               | В      | .014    | .017 | .020        | 0.36  | 0.42  | 0.51  |

| Mold Draft Angle Top     | α      | 0       | 12   | 15          | 0     | 12    | 15    |

| Mold Draft Angle Bottom  | β      | 0       | 12   | 15          | 0     | 12    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-051

# **PIC16C62X**

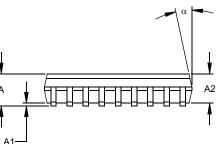

20-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

|                          | Units     |      |      |      | MILLIMETERS |        |        |

|--------------------------|-----------|------|------|------|-------------|--------|--------|

| Dimensi                  | on Limits | MIN  | NOM  | MAX  | MIN         | NOM    | MAX    |

| Number of Pins           | n         |      | 20   |      |             | 20     |        |

| Pitch                    | р         |      | .026 |      |             | 0.65   |        |

| Overall Height           | Α         | .068 | .073 | .078 | 1.73        | 1.85   | 1.98   |

| Molded Package Thickness | A2        | .064 | .068 | .072 | 1.63        | 1.73   | 1.83   |

| Standoff §               | A1        | .002 | .006 | .010 | 0.05        | 0.15   | 0.25   |

| Overall Width            | Е         | .299 | .309 | .322 | 7.59        | 7.85   | 8.18   |

| Molded Package Width     | E1        | .201 | .207 | .212 | 5.11        | 5.25   | 5.38   |

| Overall Length           | D         | .278 | .284 | .289 | 7.06        | 7.20   | 7.34   |

| Foot Length              | L         | .022 | .030 | .037 | 0.56        | 0.75   | 0.94   |

| Lead Thickness           | С         | .004 | .007 | .010 | 0.10        | 0.18   | 0.25   |

| Foot Angle               | φ         | 0    | 4    | 8    | 0.00        | 101.60 | 203.20 |

| Lead Width               | В         | .010 | .013 | .015 | 0.25        | 0.32   | 0.38   |

| Mold Draft Angle Top     | α         | 0    | 5    | 10   | 0           | 5      | 10     |

| Mold Draft Angle Bottom  | β         | 0    | 5    | 10   | 0           | 5      | 10     |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-150 Drawing No. C04-072

DS30235J-page 116

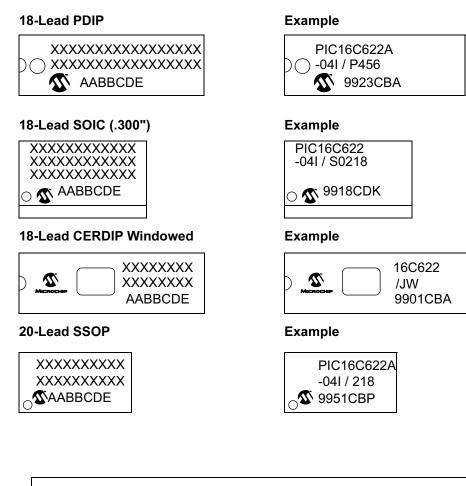

#### 14.1 Package Marking Information

| Legend | d: XXX<br>Y<br>YY<br>WW<br>NNN | Customer specific information*<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code |  |  |  |  |  |  |

|--------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Note:  | be carried                     | nt the full Microchip part number cannot be marked on one line, it will<br>over to the next line thus limiting the number of available characters<br>her specific information.                          |  |  |  |  |  |  |

\* Standard PICmicro device marking consists of Microchip part number, year code, week code, and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

#### **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:      | Technical Publications Manag        | er Total Pages Sent                                       |

|----------|-------------------------------------|-----------------------------------------------------------|

| RE:      | Reader Response                     |                                                           |

| From     | n: Name                             |                                                           |

|          | Company                             |                                                           |

|          | Address                             |                                                           |

|          |                                     |                                                           |

|          | Telephone: ()                       | FAX: ()                                                   |

| Appl     | ication (optional):                 |                                                           |

| Wou      | ld you like a reply?YN              |                                                           |

| Devi     | ce: PIC16C62X                       | _iterature Number: DS30235J                               |

| Que      | stions:                             |                                                           |

| 1. \     | What are the best features of this  | document?                                                 |

| -        |                                     |                                                           |

| <u>-</u> |                                     |                                                           |

| 2. I     | How does this document meet yo      | ur hardware and software development needs?               |

| -        |                                     |                                                           |

| 3. [     | Do you find the organization of thi | s document easy to follow? If not, why?                   |

| _        |                                     |                                                           |

| _        |                                     |                                                           |

| 4. \     | What additions to the document d    | o you think would enhance the structure and subject?      |

| -        |                                     |                                                           |

| -        |                                     |                                                           |

| 5. \     | What deletions from the documen     | t could be made without affecting the overall usefulness? |

| -        |                                     |                                                           |

| -<br>6 I | s there any incorrect or misleadir  | a information (what and where)?                           |

| 0. 1     |                                     |                                                           |

| -        |                                     |                                                           |

| 7. H     | How would you improve this docu     | ment?                                                     |

| _        |                                     |                                                           |

| -        |                                     |                                                           |

|          |                                     |                                                           |